# **CMOS** Technologies for HV applications

## Microelectronics Users eXchange MUX-2011

Rainer Minixhofer – Senior Manager R&D CERN, June 10<sup>th</sup>, 2011

a leap altead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

a leap altead in analog

#### Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

a leap altead in analog

- Let's scale down first

- **Introduction & Company Overview**

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

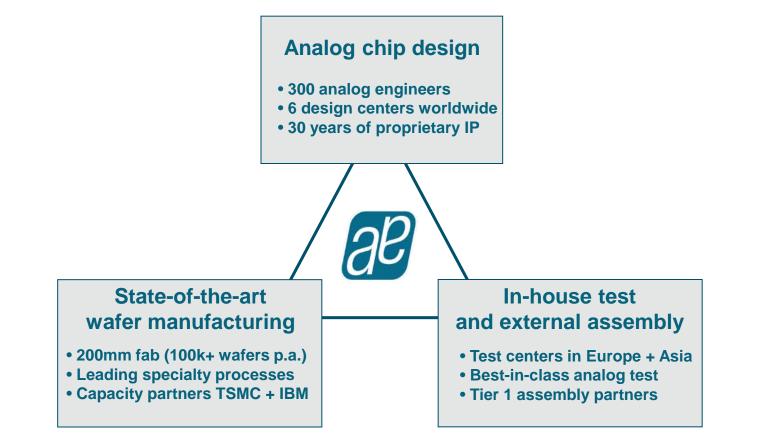

# Full control over design and manufacturing

a lean ahead in analim

a leap ahead in analog

## Figures of Merit in High Voltage Technology

#### **BVdss**

a leap ahead in analog

- Initial Specification for LDMOS devices and defines usable voltage for circuit design

- Allows for adequate voltage margin to account for device hot-e degradation (reliability) and ESD robustness

- For H18, full device reliability lifetime is evaluated during technology qualification

- Statistical in line process control to avoid escapes below minimum value

- SOAC tool checking during design simulation alerts circuit designer to any inappropriate voltage use

#### Ron

- Minimum value is key for setting device size and overall circuit complexity

- For H18, device layout is optimized by device type to obtain a minimum Ron after meeting BVdss window as specified above

#### **Process complexity**

- Modularity to industry standard CMOS: H18 FET electrical specifications/models are identical to those of C18 technology for 1.8 and 5V LV FETs: easy porting of IP

- Minimal mask additions for HV devices: add of 2 masks compared with C18

- Maintain a rich HV device set: variety of BVdss and Vgs of HV LDMOS devices and specific HV devices include NPN, PNP, JFET, HV resistors and HV capacitors

#### Process flexibility and extendibility

- The single H18 process supports multiple BVdss specifications with scaled devices

- H18 is extendable without process changes to BVdss values as low as 10V and high as 120V

- Thus, designs completed now can be enhanced by addition of these extended voltage range devices in the future

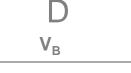

## Si-Limit: On-Resistance vs. Blocking Voltage Tradeoff

$W = \sqrt{\frac{2 \cdot \varepsilon_{Si} \cdot V_{B}}{q \cdot N_{drift}}}$

$V_B = \frac{W \cdot E_{crit}}{2} = \frac{W^2 \cdot q \cdot N_{drift}}{2\varepsilon}$

#### A simple model for HV Transistors:

For a one sided junction the depletion layer width at breakdown is:

and the breakdown voltage is:

Specific on-resistance is given by:

Breakdown occurs when the depletion layer reaches a certain thickness which is almost proportional to the breakdown  $W = 2.58 \cdot 10^{-6} \cdot (V_B)^{\frac{1}{6}}$ voltage (avalanche effect):

Which finally yields:

$$R_{on,sp} \propto V_B^{2.5}$$

S:

$$W = \sqrt{\frac{2 \cdot \varepsilon_{Si} \cdot V_{B}}{q \cdot N_{drift}}}$$

$$V_{B} = \frac{W \cdot E_{crit}}{2} = \frac{W^{2} \cdot q \cdot N_{drift}}{2\varepsilon_{si}}$$

$$R_{on,sp} = \rho \cdot W = \frac{W}{q\mu N_{drift}} = \frac{W^{3}}{2\mu V_{B}\varepsilon_{si}}$$

$$V_{B} = \frac{W}{V_{B}}$$

a leap abead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

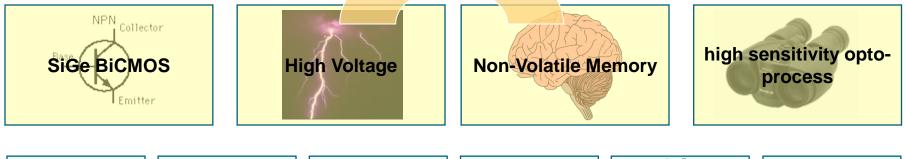

# Process modularity on 0.35µm node

# High flexibility through modularity:

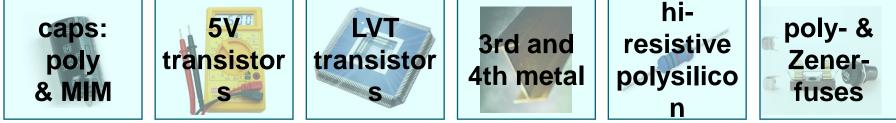

## MOS transistor naming H35

## High Voltage Technology Process Flow

| deep N-well   |                                                                                                                                   | a leap alread in analog                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|               | shallow trench isolation                                                                                                          |                                                                       |

| HV well       | well implants for 1.8V and 5V                                                                                                     |                                                                       |

| HV Gate oxide | Gate oxidation for 5V                                                                                                             | Net:                                                                  |

|               | Gate oxidation for 1.8V<br>Gate formation<br>FET extension implants for 1.8V<br>FET extension implants for 5V<br>spacer formation | •Triple gate process<br>(1.8, 5 and 20V), but<br>1.8 and 20V optional |

|               | pFET S/D/G implants<br>nFET S/D/G implants                                                                                        | •2 additional HV<br>masks to base CMOS                                |

|               | final RTA anneal salicide formation                                                                                               | •Additional resistor                                                  |

|               | contact formation<br>Cu/AI interconnect<br>metal-insulator metal capacitor<br>thick last metal                                    | masks optional •3LM-7LM options                                       |

| HVCMOS ADDS   | <b>CMOS PROCESS</b>                                                                                                               |                                                                       |

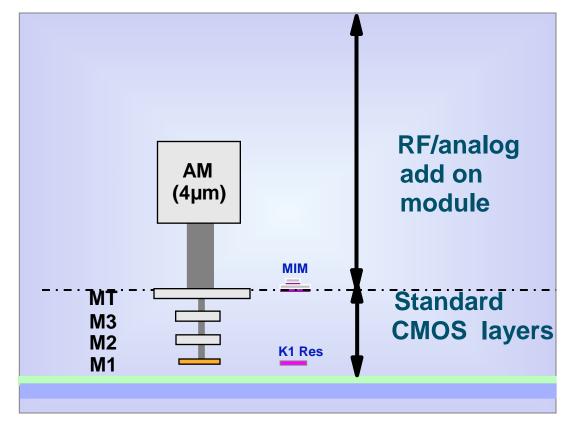

### H18 metal stack options

a lean ahead in analon

|                                 | AM Last Metal Option |           |    |    |    |  |  |  |  |  |

|---------------------------------|----------------------|-----------|----|----|----|--|--|--|--|--|

| # Levels                        | 3                    | 3 4 5 6 7 |    |    |    |  |  |  |  |  |

|                                 |                      |           |    |    | MT |  |  |  |  |  |

|                                 |                      |           |    | MT | M5 |  |  |  |  |  |

|                                 |                      |           | MT | M4 | M4 |  |  |  |  |  |

| Standard<br>Al wiring<br>Levels |                      | MT        | M3 | M3 | M3 |  |  |  |  |  |

|                                 | MT                   | M2        | M2 | M2 | M2 |  |  |  |  |  |

|                                 | M1                   | M1        | M1 | M1 | M1 |  |  |  |  |  |

#### H18 Process Information

. .

r leap altead in analog .

#### 0.18µm HV CMOS - Key Technology Features

Currently available voltages RON (20V & 50V) NMOS Operating Voltages Blocking Voltages Layout scalable devices 1.8 V / 5 V / 20 V / 25 V / 50 V 15 & 105 mΩ mm<sup>2</sup> 20 V / 25 V / 50 V 30 V / 40 V / 70 V 20 - 120 V (120 V demonstrated)

#### 0.18µm HV CMOS - Process Modules

Back end process modules

3 - 7 metal

Power metal (4 µm thick) Poly resistor High resistive poly MIM (metal insulator metal) capacitance

Front end process modules

1.8 V Gates

5.0 V Gates 20 V Gates Isolated low voltage NMOS and PMOS (1.8 V / 5.0 V)

#### Process modularity of H18

High flexibility through modularity:

15

High Voltage

Non-Volatile

Memor

a leap ahead in analog

*austriamicro*systems

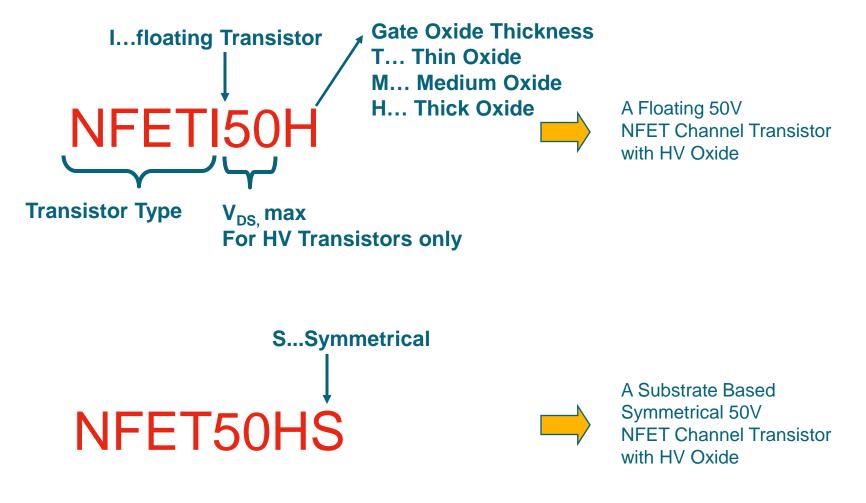

## HV MOS Transistor Naming Convention Cheat Sheet

a leap abead in analog

### H18 device list

a leap ahead in analog

#### Existing C18 Devices

Thin oxide NFET/PFET 1.8V Medium oxide NFET/PFET 5V High Vt NFET/PFET 1.8V N+ diffusion resistor P+ diffusion resistor N+ poly resistor P+ poly resistor **K1 BEOL resistor** High resistivity poly resistor precision poly resistor Single Nitride MIM **Dual Nitride MIM** HighK MIM PCDCAP thin ox Vertical parallel plate capacitor (VNcap) Schottky Barrier Diode Ffuse Bondpad

#### Modifications to existing devices for HV process:

Thin oxide NFETi/PFETi 1.8V in HV wells Medium oxide NFETi/PFETi 5V in HV wells High Vt NFETi/PFETi 1.8V in HV wells N+ diffusion resistor in HV well P+ diffusion resistor in HV well

#### New Devices:

Thin oxide NFETi/PFET 20V Thick oxide NFETi/PFET 20V Thick oxide NFETi/PFET symmetric 20V Medium oxide NFETi 20V Medium oxide NFETi/PFET 25V Thin oxide NFETi/PFET 50V Medium oxide NFETi/PFET 50V Thick NFETi/PFET 50V Thick NFETi/PFET symmetric 50V 3 terminal JFET Parasitic VPNP (high V) Parasitic VNPN (isolated) NWell resistor in HV well PWell resistor in HV well High Voltage VNcap

t leap ahead in analog

- Suite of FETs with three gate oxide thicknesses

- Low Voltage (LV) fets for standard 1.8 and 5V CMOS

- LV fets in HV well for high voltage isolation to substrate

- HV asymmetric fets for High Voltage applications

- 3 gate oxide thicknesses, 2 maximum drain bias choices

- HV symmetric fets for specialty applications (transmission gate)

|                 | LV fets                              |                | LV fets i                                | LV fets in HV well |                                 | HV asymmetric fets in HV<br>wells |                      | netric fets<br>Substrate) |

|-----------------|--------------------------------------|----------------|------------------------------------------|--------------------|---------------------------------|-----------------------------------|----------------------|---------------------------|

| Vds<br>Vgs      | 1.8V                                 | 5.0V           | 1.8V                                     | 5.0V               | 20V**                           | 50V                               | 20V                  | 50V                       |

| 1.8V<br>(3.5nm) | nfet*<br>pfet*<br>nfethvt<br>pfethvt |                | nfeti*<br>pfeti*<br>nfetihvt<br>pfetihvt |                    | nfeti20t<br>pfet20t             | nfeti50t<br>pfet50t               |                      |                           |

| 5.0V<br>(12nm)  |                                      | nfetm<br>pfetm |                                          | nfetim<br>pfetim   | nfet20mh<br>nfeti25m<br>pfet25m | nfeti50m<br>pfet50m               |                      |                           |

| 20V<br>(52nm)   |                                      |                |                                          |                    | nfeti20h<br>pfet20h             | nfeti50h<br>pfet50h               | nfet20hs<br>pfet20hs | nfet50hs<br>pfet50hs      |

\* RF layout available \*\* 25V Vds for nfeti25m,pfeti25m

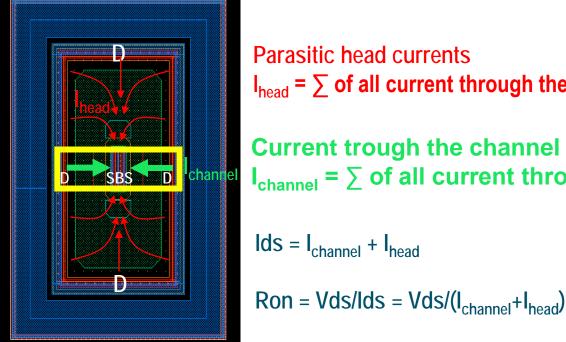

## Wide vs. Small Devices: The Transistor Head effect

Parasitic head currents can't be 100% eliminated (up to 20uA)

Parasitic head currents  $I_{head} = \sum$  of all current through the head

Current trough the channel  $I_{channel} = \sum$  of all current through the channels

Parasitic head currents can't be neglected for low channel Currents (narrow devices) If channel currents are high (wide devices), parasitic head current can be neglected For simple calculation there are two different Ron [Ohm um] values for narrow and wide transistors

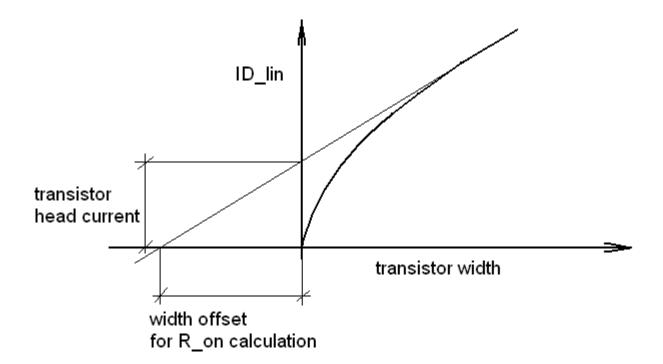

## Ron Calculation

a leap altead in analog

## Transistor head current

#### For small W devices the transistor current increases faster than for a large W device.

a leap abead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- **High Voltage Device Description**

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

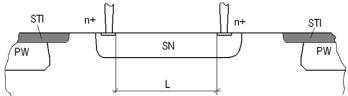

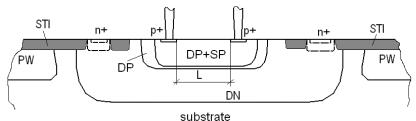

H18 High Voltage NFETs

a leap shead in analog

|                                                     | Asymmetric, thinnest oxide, isolated well |            | Asymm.,<br>med. oxide<br>in substrate | Asymmetric, medium oxide,<br>isolated well |          | Asymmetric, thickest oxide, isolated well |          | Symmetric, thickest oxide, in substrate |          |

|-----------------------------------------------------|-------------------------------------------|------------|---------------------------------------|--------------------------------------------|----------|-------------------------------------------|----------|-----------------------------------------|----------|

| Parameter                                           | nfeti20t                                  | nfeti50t   | nfet20mh                              | nfeti25m                                   | nfeti50m | nfeti20h                                  | nfeti50h | nfet20hs                                | nfet50hs |

| Min Drain-source breakdown (V)                      | 29                                        | 83         | 27                                    | 33                                         | 73       | 28                                        | 79       | 32                                      | 85       |

| Tox (physical, nm) / Max VGS (V)                    | 3.5 / 1.98                                | 3.5 / 1.98 | 12 / 5.5                              | 12 / 5.5                                   | 12 / 5.5 | 52 / 20                                   | 52 / 20  | 52 / 20                                 | 52 / 20  |

| Ldrawn (µm)                                         | 0.2                                       | 0.2        | 0.4                                   | 0.4                                        | 0.4      | 0.5                                       | 0.5      | 0.7                                     | 1.3      |

| V <sub>T</sub> (short wide V)                       | 0.43                                      | 0.40       | 0.80                                  | 0.71                                       | 0.72     | 2.0                                       | 2.14     | 2.15                                    | 2.15     |

| IDsat (µA/ µm)                                      | 200                                       | 172        | 400                                   | 343                                        | 266      | 580                                       | 353      | 340                                     | 230      |

| On Resistance $m\Omega$ -mm <sup>2</sup>            | 35.1                                      | 168        | 17.1                                  | 45.2                                       | 143      | 29.5                                      | 138      | 47.1                                    | 316      |

| On Resistance m $\Omega$ -mm <sup>2</sup> (butted)* | 29.8                                      | 155        | 14.4                                  | 39.2                                       | 132      | 25.5                                      | 128      |                                         |          |

Pitch for  $R_{sp}$  on resistance calculation includes full drain, source, *and* independent body contact (\*mh devices butted source contact)

## H18 High Voltage PFETs

a leap ahead in analog

|                                                     | Asymmetric, thinnest oxide |            | Asymmetric, medium<br>oxide |          | Asymmetric, thickest oxide |         | Symmetric, thickest oxide |          |

|-----------------------------------------------------|----------------------------|------------|-----------------------------|----------|----------------------------|---------|---------------------------|----------|

| Parameter                                           | pfet20t                    | pfet50t    | pfet25m                     | pfet50m  | pfet20h                    | pfet50h | pfet20hs                  | Pfet50hs |

| Min Drain-source breakdown (V)                      | -30                        | -70        | -32                         | -70      | -35                        | -70     | -28                       | -70      |

| Tox (physical, nm) / Max VGS (V)                    | 3.5 / 1.98                 | 3.5 / 1.98 | 12 / 5.5                    | 12 / 5.5 | 52 / 20                    | 52 / 20 | 52 / 20                   | 52 / 20  |

| Ldrawn (µm)                                         | 0.2                        | 0.2        | 0.6                         | 0.6      | 0.6                        | 0.6     | 2.0                       | 3.0      |

| $V_{T}$ (short wide V)                              | -0.35                      | -0.35      | -0.51                       | -0.52    | -2.48                      | -2.52   | -1.80                     | -1.80    |

| IDsat (µA/ µm)                                      | 140                        | 123        | 220                         | 204      | 345                        | 309     | 250                       | 160      |

| On Resistance $m\Omega$ -mm <sup>2</sup>            | 53.0                       | 187        | 66.0                        | 194      | 63.0                       | 183     | 129                       | 630      |

| On Resistance m $\Omega$ -mm <sup>2</sup> (butted)* | 41.8                       | 166        | 53.8                        | 174      | 51.7                       | 166     |                           |          |

Pitch for  $R_{sp}$  on resistance calculation includes full drain, source, *and* independent body contact (\*mh devices butted source contact)

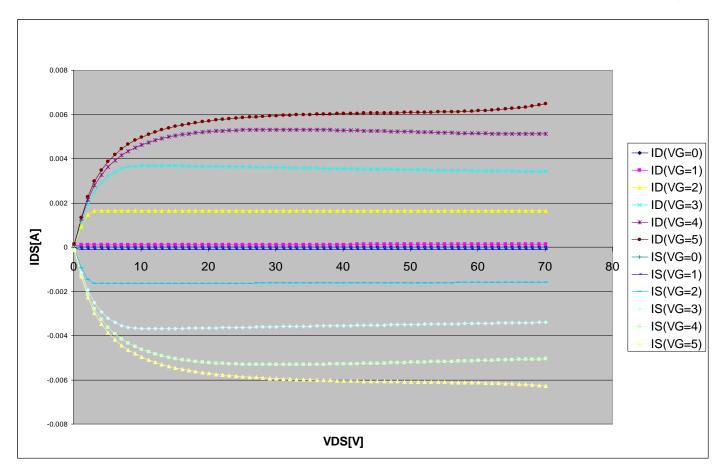

H18 Devices: NFETI50 Device Family

a lean shead in analon-

#### Note the active breakdown for the stationary curve tracing is for the 50V devices higher than 70V.

## H18 Devices: NFETI50 Device Family

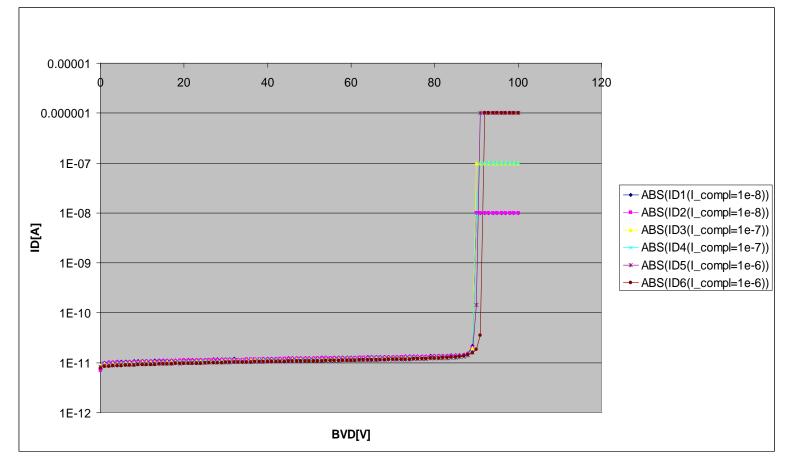

NFETI50M blocking curve

a leap shead in analog -

#### The breakdown should start abrupt without any premature leakage current

H18 Devices: NFETI50 Device Family

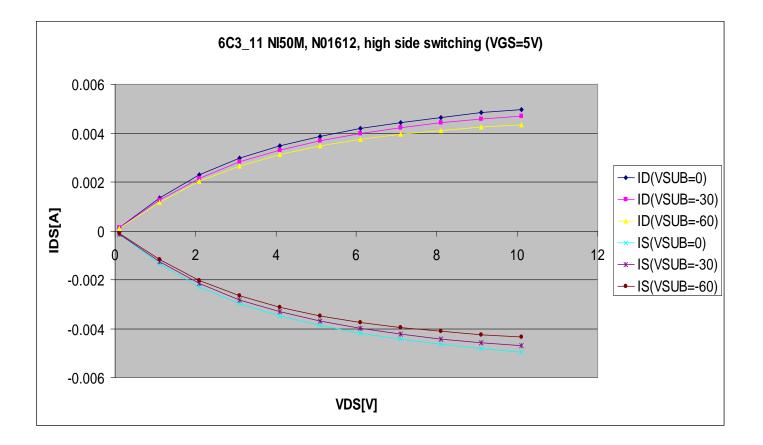

NFETI50M high side switching behavior

a leap shead in analog -

#### Note: The drain voltage in the curve with the lowest current is 60+10=70V above substrate potential.

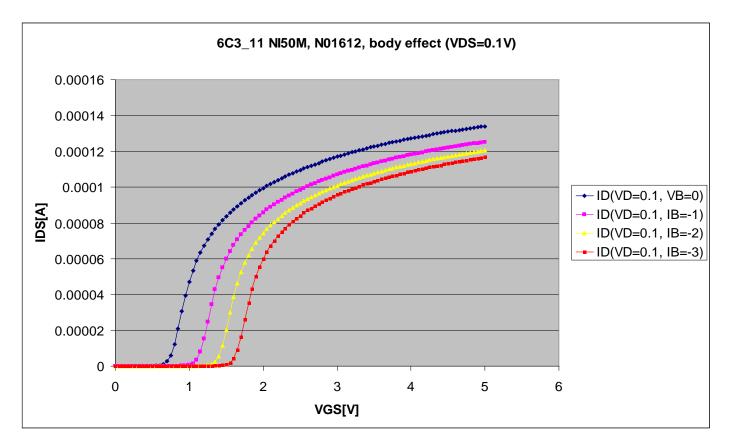

H18 Devices: NFETI50 Device Family

#### NFETI50M body effect

a leap ahead in analog

#### © 2010 austriamicrosystems

### H18: HV Resistors

- Linear current-voltage relationship over wide range of applied voltage

- Resistance scales with width

*austriamicrosystems*

a leap ahead in analog

- The pinch-off characteristic for high current density is modeled

- Weff calculated from various W/L

|                | Rs<br>(Ω / sq) | Temp Coeff (linear)<br>10 <sup>-3</sup> / K | Temp Coeff (quad)<br>10 <sup>-3</sup> / K |

|----------------|----------------|---------------------------------------------|-------------------------------------------|

| HV NW Resistor | 3074           | 5.14                                        | 1.47                                      |

| HV PW Resistor | 725            | 2.32                                        | 0.53                                      |

a leap altead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

## H18: Low Voltage FET Options

austriamicrosystems

a leap ahead in analog

|                                     |         | H18 Spec Target Value |         |                 |  |  |

|-------------------------------------|---------|-----------------------|---------|-----------------|--|--|

| Device Description                  | Vt (mV) | ld sat<br>(µA/µm)     | Vdd (V) | Library<br>Name |  |  |

| Thin ox NFET                        | 355     | 600                   | 1.8     | nfet            |  |  |

| Thin ox NFET in HV isolation        | 355     | 600                   | 1.8     | nfeti           |  |  |

| Thin ox PFET                        | 420     | 260                   | 1.8     | pfet            |  |  |

| Thin ox PFET in HV isolation        | 420     | 260                   | 1.8     | pfeti           |  |  |

| High Vt NFET                        | 525     | 500                   | 1.8     | nfethvt         |  |  |

| High Vt PFET                        | 520     | 210                   | 1.8     | pfethvt         |  |  |

| 5V Medium ox NFET                   | 625     | 630                   | 5.0     | nfetm           |  |  |

| 5V Medium ox NFET in HV isolation   | 625     | 630                   | 5.0     | nfetim          |  |  |

| 5V Medium ox PFET *                 | 650     | 345                   | 5.0     | pfet            |  |  |

| 5V Medium ox PFET in HV isolation * | 650     | 345                   | 5.0     | pfeti           |  |  |

All specifications match those found in C18

$^{\ast}$  Corresponds to shorter (0.5  $\mu m$ ) gate length device

a leap altead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

## **Design Documents**

### **Basic Design & Process Information**

#### **Process Parameters Documents**

Operating conditions Structural & geometrical parameters Electrical parameters Figures of merit (e.g. FT ,FMAX) Compact Modeling Documents SPICE Models

Features and Limitations

#### Design Rule Documents Rules, Guidelines, Recommended Layout Structures

#### **Element Layout Documents**

Element specification Internal only RF-Devices RF Modeling Figures of merit (e.g. Qmax)

Noise Documents Noise Measurements Noise Modeling

Matching Documents Matching Measurements Matching Modeling

Parasitic Modeling Parasitic diodes and Bipolar Tr. for HVMOS

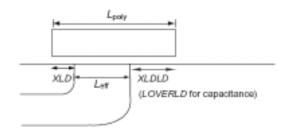

### Compact modeling for the CMOS Process

- –PSP & BSIM3v3 for std. MOS transistor

- •Scalable, physical, predictable.

- -High voltage transistor modeled as subcircuits

- JFET models for all diffusion resistors

SGP model for all pnp (Vert,Lat)

Voltage and Temp. dependent capacitance & resistor modeling

Mismatch modeling for all devices

Noise modeling (1/f & thermal noise)

RF- modeling for MOS, Res, Cap, Varactor.

a leap ahead in analog

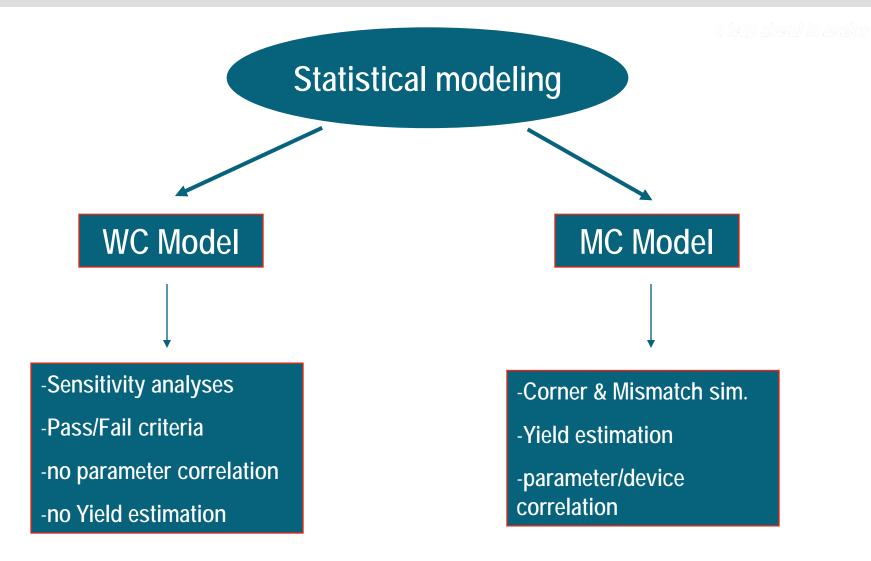

#### Process variation overview

a leap ahead in analog

# H35 120V Devices (Compact Modeling)

a lean shead in smaloo

| Model Features |                |                         |                               |                     |                      |                                     |                               |  |  |  |

|----------------|----------------|-------------------------|-------------------------------|---------------------|----------------------|-------------------------------------|-------------------------------|--|--|--|

| Device         | Scalable Model | 1/f noise <sup>*)</sup> | Temp. Modeling<br>-40 – 180°C | Worst Case<br>Model | Monte Carlo<br>Model | Mismatch<br>Parameter <sup>*)</sup> | parasitic model <sup>*)</sup> |  |  |  |

| NMOSI120M      | х              | х                       | х                             | х                   | х                    | х                                   | х                             |  |  |  |

| NMOSI120H      | х              | х                       | х                             | х                   | х                    | х                                   | х                             |  |  |  |

| PMOS120M       | x              | x                       | x                             | x                   | х                    | х                                   | х                             |  |  |  |

| PMOS120H       | х              | х                       | х                             | х                   | х                    | х                                   | х                             |  |  |  |

## H35 120V Characteristic Curves

a leap ahead in analog

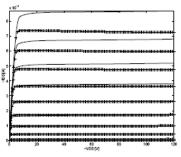

#### 7.1 NMOSI120M

Fig.7.1.1 NNO81120M output oharaoteristic of a typical water. W/L=40/10, VO8= 1.0 1.6 2.0 2.6 3.0 3.6 4.0 4.6 6.0 6.6 V, VB8=0 V. + = measured, -- = B8IMSV3 model

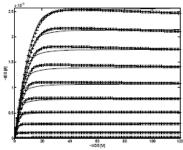

#### 7.2 NMOSI120H

Fig.7.1.2 NMO81120M output obaraoteristic of a typical wafer. W/L=40/0.5, VGS= 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 6.0 6.6 V, VBS=0 V. + = measured, -- = B8IM3VS model

Fig.7.2.2 NMO81120H output oharaoteristio of a typical water. W/L=400.5, VOS= 2.9 4.8 6.7 8.8 10.6 12.4 14.3 16.2 18.1 20 V, VBS=0 V. + = measured, -- = B81M3v3 model

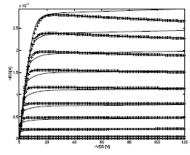

#### 7.3 PMOS120M

Fig.7.8.1 FMO8120M output charaoteristic of a typical wafer. W/L=2016, VO8= -1.0 -1.6 -2.0 -2.6 -0.0 -8.6 -4.0 -4.6 -5.0 -6.6 V, VB8=0 V. + = measured, -- = B81M8v3 model

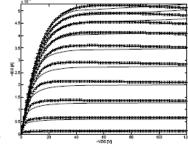

#### 7.4 PMOS120H

Fig.7.4.1 PMO8120H output oharaoteristic of a typical wafer. W/L=20/5, V08= -2.9 -4.8 -8.7 -8.6 -10.5 -12.4 -14.8 -16.2 -18.1 -20 V, VB8=0 V. + = measured, -- = B8IMSv8 model

Fig.7.8.2 PMO8120M output oharaoteristio of a typical wafer. W/L=20/1, V68= -1.0 -1.5 -2.0 -2.5 -8.0 -3.5 -4.0 -4.5 -5.0 -6.6 V, VB8=0 V. + = measured, -- = B8IM3v8 model

Fig.7.4.2 PNO8120H output oharaoteristic of a typical wafer. W/L=2011.2, VO8= -2.8 -4.8 -6.7 -8.8 -10.5 -12.4 -14.8 -18.2 -18.1 -20 V, VE8=0 V. + = measured, -- = B8IM3V3 model

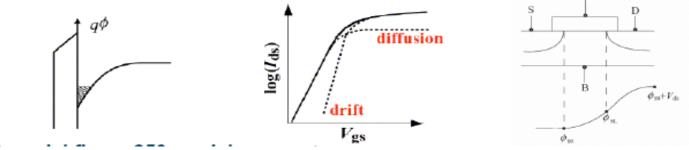

## HISIM-HV Model for HV LDMOS

a leap ahead in analog

- Developed as extension of HiSIM: Complete surface potential based model

unified description of device characteristics for all bias regions

- Based on drift-diffusion theory using charge sheet and gradual channel approximation

- Capable of modeling symmetrical and asymmetrical devices: COSYM= 0/1

- Self-heating effect modeling: COSELFHEAT=0/1

- Substrate current modeling: COISUB=0/1

# HV HSIM\_HV Model to Hardware Results

a leap ahead in analog

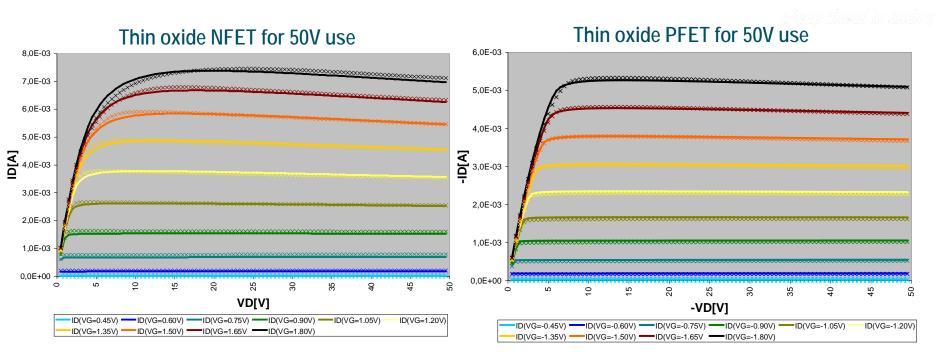

Excellent agreement between measured results and HiSIM\_HV SPICE model. Model features include:

- Surface potential iterative calculation used for an accurate description of drift region

- Self-heating included

- Simulation speed and accuracy is improved compared BSIM (SPICE) + subcircuit.

# Outline

a leap abead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

## H18: LV and HV ESD Protection

a leap ahead in analog

### Strategies for 1.8V and 5.0V Applications:

- Power Supply Protection Devices

- 1.8V or 5.0V RC-Triggered Power Clamp

- 1.8V or 5.0V Silicide-Blocked NFET

- I/O ESD Protection Devices

- P+/NW Diodes

- N+/PW Diodes

- 1.8V or 5.0V Silicide-Blocked NFET

- ESD protection devices are offered in standard well and in HV Well

### Strategies for 20V, 25V and 50V:

- Power Supply Protection Devices

•HV Clamp based on 20V, 25V or 50V HV-PFETs

- I/O ESD Protection Devices

- 25V Forward Diode

- 50V Forward Diode

### Characterization

- Use 100ns TLP, 30ns and 1ns TLP to emulates device behavior under HBM, MM and CDM conditions

- Also wafer level testing with HBM tester

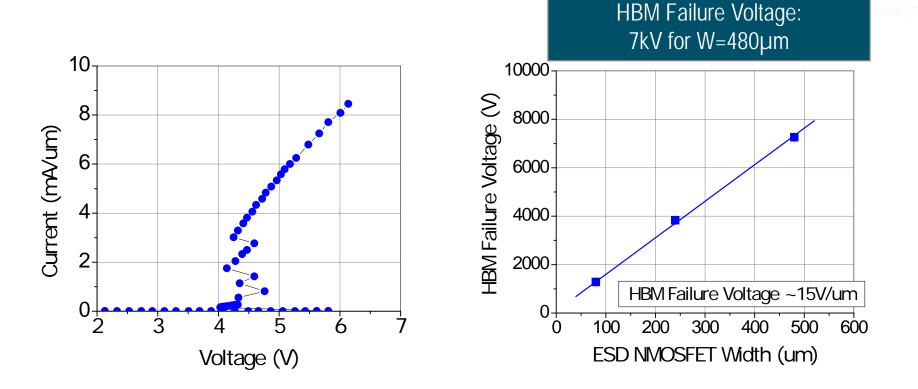

# LV Silicided 1.8V NFET Scalability

a leap ahead in analog

- 100ns TLP I-V of a 1.8V, gate-grounded silicide-blocked NFET with drain silicide-block length of  $2\mu m$

- HBM data shows good scaling of failure voltage ~15V/ $\mu$ m of device width

- ESD protection devices are available in H18 HIT-Kit for protection of low voltage and high voltage devices

- ESD devices are designed to be fully scalable to enable a area optimized solution

- Detailed recommendations and ESD data summary is available in ESD Reference Guide that is provided with the HIT-Kit

- ESD Design review is provided upon request for all designs

- Demonstrated scalable ESD solutions (HBM 2-8kV)

- Failure currents of protections exceed tester capability

# HV NFET SOA and Reliability

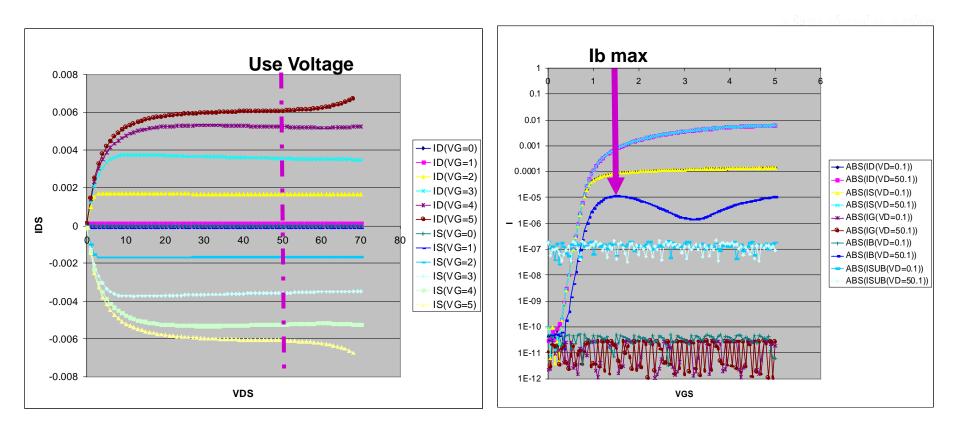

Forward IV and body current plots for isolated HV NMOS NFETI50M Output current stable (Ids) beyond use voltage Body current (Ib) peaks at Vgs~1.5V

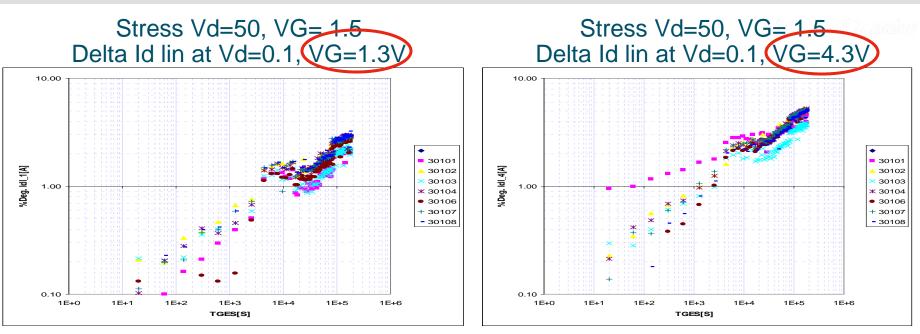

# HV Isolated NFET Idlin Stability (NFETI50M)

a leap ahead in analog

Id<sub>lin</sub> parameter shift with (stress time) is key for power applications

Measure Id<sub>lin</sub> stability after stress at Vds=50V, Vgs=1, 1.5V (worst case)

Gm, Vt, Id<sub>sat</sub> drift << Id<sub>lin</sub>

Use data to construct SOA tradeoffs with respect to L, Vd,% shift (lifetime)

Id<sub>lin</sub> lifetime > 10 years ; *industrial* and *automotive* grade stability

Id<sub>lin</sub> lifetime @60V stress exceeds *consumer* grade stability

| Temperature lifetime profile: (-40 +125)° C for 15 years |                                           |

|----------------------------------------------------------|-------------------------------------------|

|                                                          | (-40 +150)° C for 10 000 hours            |

| Voltage levels:                                          | VG1.98V/5.5V/20V                          |

|                                                          | VD1.98V/5.5V/20V/50V                      |

| Oxides:                                                  | Defect Density: <1 Defect/cm <sup>2</sup> |

|                                                          | max. oxide area: 5mm <sup>2</sup>         |

| ESD:                                                     | ESD Library up to 4kV HBM*                |

|                                                          |                                           |

\* According to MIL-STD-883C method 3015.7 and JESD22-A114 and ANSI/ESD STM5.1

# Outline

a leap abead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- **Design Kit**

- Conclusions

# Analog/Mixed Signal High Performance Interface Tool Kit

The AMS HIT-Kit enables product developers to concentrate on their core competence IC design rather than on setting up and mastering the EDA environment

### This leads the Partner to:

- **.** Shorter Time to Market

- Complete Environment for First Time Right Designs

- . More Efficient Designs (Die Size, Performance, Yield)

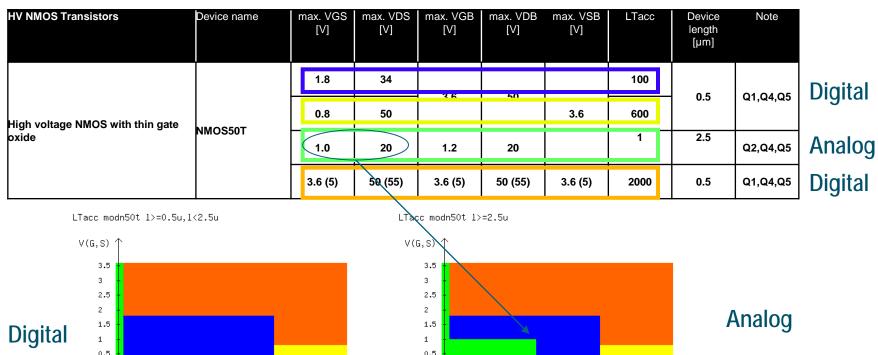

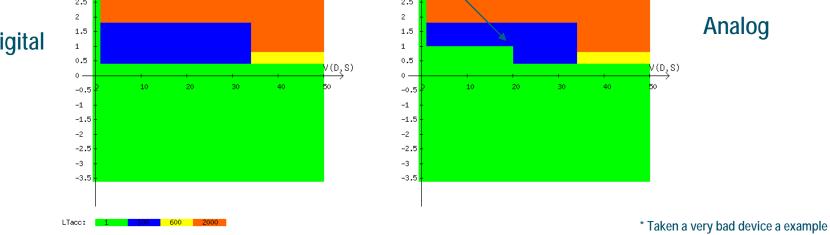

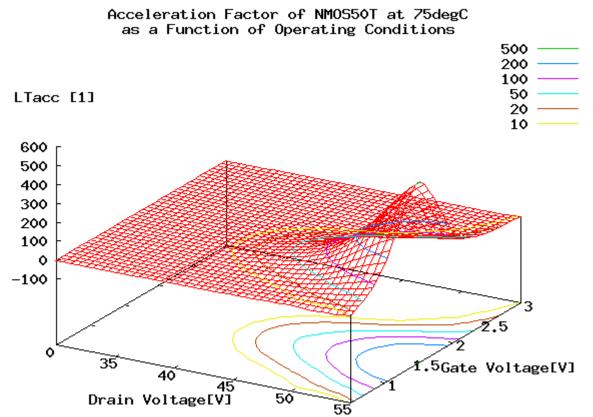

# LTacc – LifeTime Acceleration Factor for Simulation a leap ahead in analog

### LTacc defined in the Process Parameter Document:

# NMOS50T HC Reliability Model

a loop alloud in allolog

# -Acceleration Factors for NMOS50T based on self-heating and operating conditions analysis.

- "Plug and Play" for IC designers

- All major EDA tools supported

- All process technologies supported with latest versionsof EDA tools

- All devices supported throughout the whole design flow

- Complete modeling of active and passive devices

(high accuracy, Monte Carlo, corner, mismatch, noise, HDL, IC package, up to system level)

#### a leap ahead in analog

# HIT-Kit Benefits (cont.)

- Supports complete flow for RF, Mixed Signal and High Voltage design

- Additional Userware for special Tasks

(Bonding-Diagram Editor, Safe Operating Area Check, Revision Block Generator etc.)

- Full Mixed-Signal Library Concept

- HIT-Kit is fully compliant with QS9000 quality certificate

- HIT-Kit developers provide technical support

# **Customer Support**

#### Hotline

**Online Documentation** http://asic.austriamicrosystems.com

#### Data sheets

Design Documents

HIT-Kit Information

•Tool usage

News & Alerts

Download area

Special High-Voltage Designer Forum

#### **Training & Tutorials**

#### austriamicrosystems High-Voltage CMOS Designers Forum

Due to of the variety of applications that can be realized using a High-Voltage CMOS process, different design methods and layout techniques are applicable. High-Voltage CMOS design is always based on the designers experience and knowledge of the process. It is very important that designers are familiar with all devices and their parasitics.

This forum provides the possibility to gain detailed design knowledge and High-Voltage CMOS process (H35) related information:

#### Process information

- High Voltage technology selection guide

- H35 process options and available devices

#### **Design support**

- <u>High Voltage Design Kit</u> (v3.70)

- Frequently Asked Questions (FAQs)

- High Voltage Discussions

- Safe Operating Area Check (SOAC)

- CDF Parameters and Pcell Parameters

- High Voltage Glossary

#### **Design documents:**

- H35 50V CMOS Process Parameters ENG-238

- H35 50V CMOS Design Rules ENG-243

- H35 50V CMOS Noise Parameters ENG-244

- H35 50V CMOS Matching Parameters ENG-245

#### Additional documentation:

- Layout Guidelines

- Parasitic Devices

Requirements: This service is offered to registered users only. You need to have a valid user account on our technical web server. If not yet registered, you may create your personal web account here. Please note that a mutual Confidentiality Agreement (CA) has to be signed with austriamicrosystems AG to get registered. For further information please contact our local sales representative. Please send your feedback and/or suggestions for improvement to hitkit@austriamicrosystems.com

# Outline

a leap altead in analog

- Let's scale down first

- Introduction & Company Overview

- **Technology Integration**

- High Voltage Device Description

- Low Voltage RF Device Description

- **Device Models**

- ESD, SOA and Reliability

- Design Kit

- Conclusions

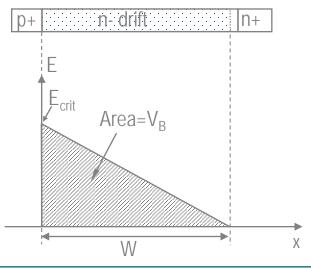

- H35/H18 is a HV CMOS power management platform which exceeds or matches BCD technology performance at lower process complexity (cost).

- ➢HV n- and p-channel specific on-resistance is lower than all foundry offerings from 30V-80V BV<sub>ds</sub>

- offers a rich suite of HV FETs, bipolars, JFETs and SBDs in a triple-well triple-gate oxide process

- H35/H18 supports a rich suite of passive components including precision resistors, capacitors, varactors, ESD components

- ➤ H35/H18 LV devices are IP-compatible to the CMOS 350/180nm platform (C35/C18) for IP re-use across derivative nodes

- > H35/H18 device library is hardware verified with full reliability qualification

- We offer a long experience of High-Voltage CMOS process development and design to our customers.

# Some famous last words....

a leap shead in analog

Do you have it in smaller size?

# **AP** austria**micro**systems

a leap ahead in analog

austria**micro**systems AG Full Service Foundry 8141 Unterpremstaetten AUSTRIA T: +43 3136 500 Email: foundry@austriamicrosystems.com http://www.austriamicrosystems.com http://asic.austriamicrosystems.com

# Your partner for High Performance Analog IC Solutions