### PixESL: A virtual Electronic System Level prototyping framework

Jashandeep Dhaliwal on behalf of the EP R&D Work Package 5

25/09/2023

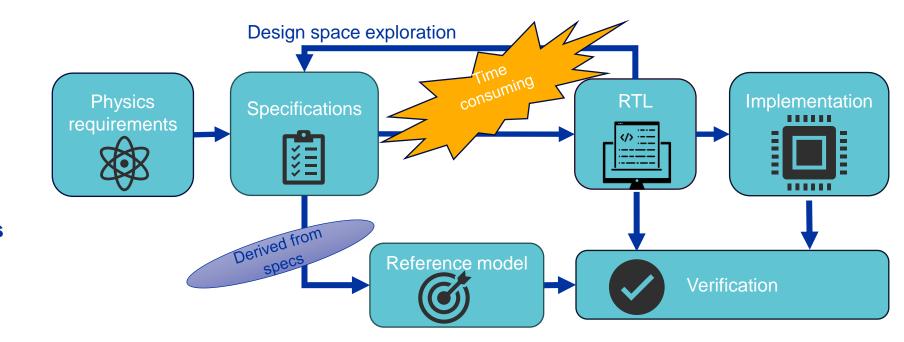

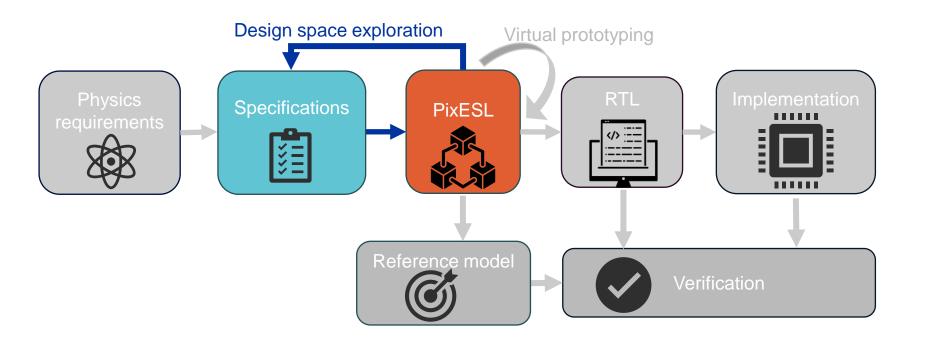

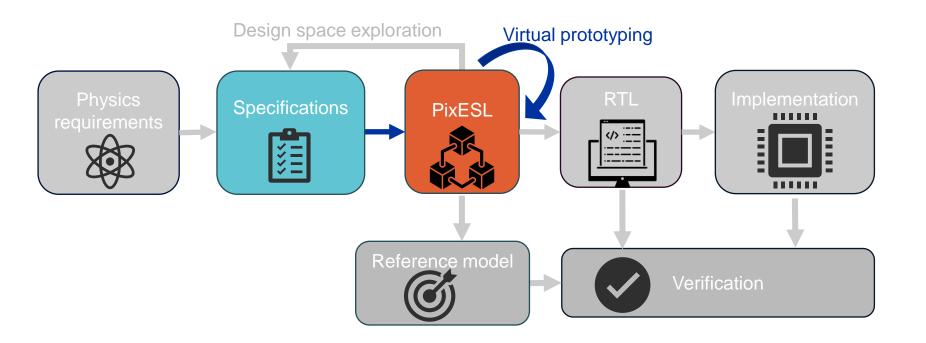

### **Detector Design Flow**

#### Limitations

- the design space exploration requires:

- HDL description of the system

- Verification environment

- Long simulation and iteration time

- The reference model has to be derived from the specifications

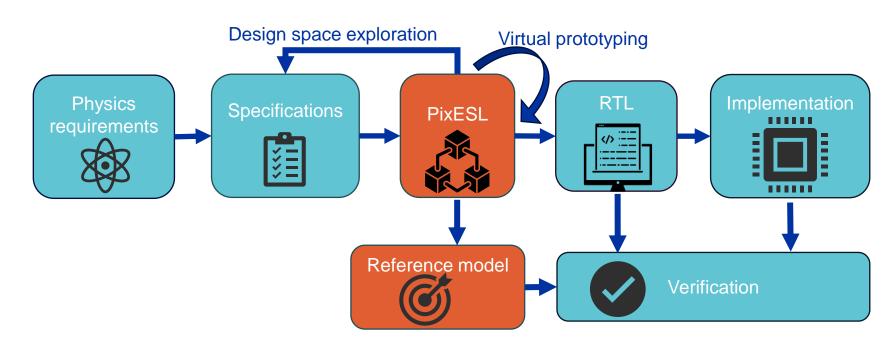

### **Detector Design Flow with PixESL**

#### Goals

Develop a **high-level description of the system**, from front-end to backend, to:

- Refine specifications and performance evaluation during prototyping

- Provide a **reference model** for verification

- Provide a virtual prototyping environment for new features development

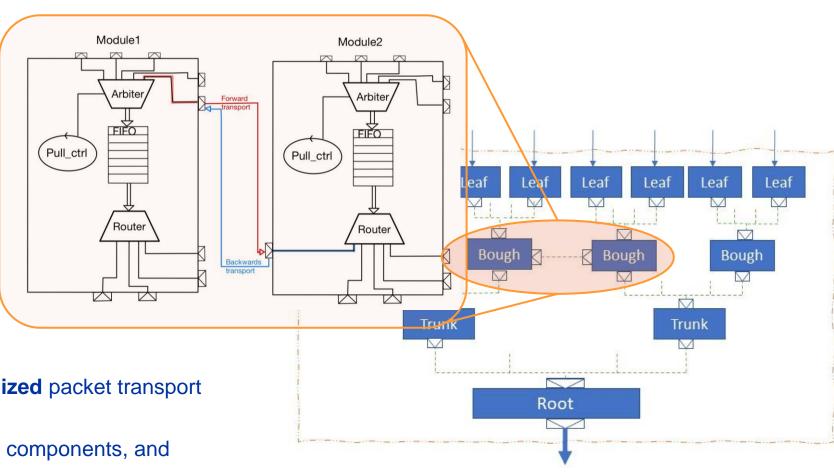

## **PixESL - methodology**

#### **Open-source:**

- The model is based on C++ and

- Performance analysis are based c

#### **User-friendly**:

- The framework supports architec configurability (structure, memori interconnections)

- User and developer roles are ser

#### **Reusable**:

- Generalized layers and standardized packet transport (TLM)

- A **library** of layer types, functional components, and packet transport types

- Common integrated metrics analyzer

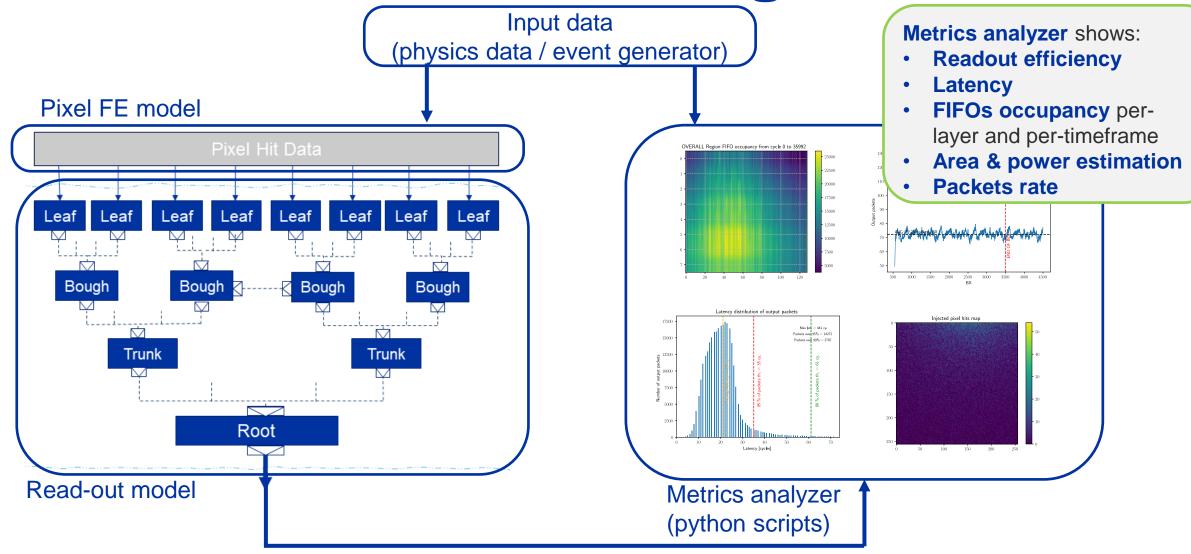

### **PixESL – Framework Diagram**

### **Design space exploration**

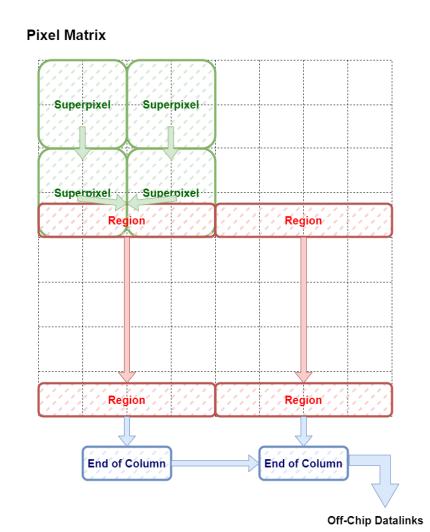

## LHCb Velopix2

- Velopix2 has been chosen as the first case-study: it is the upgrade to the pixel detector in the primary LHCb tracker

- Develop a data-driven readout architecture

- Based on physical events

- Main challenge: higher occupancy (x2 Velopix1)

#### Thanks X. Llopart and S. Esposito for the support!

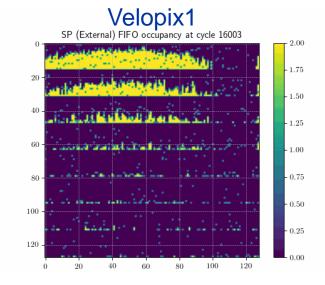

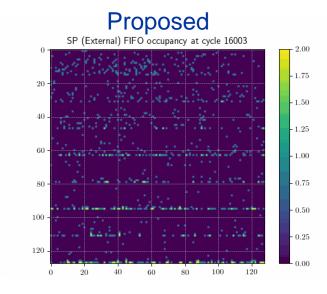

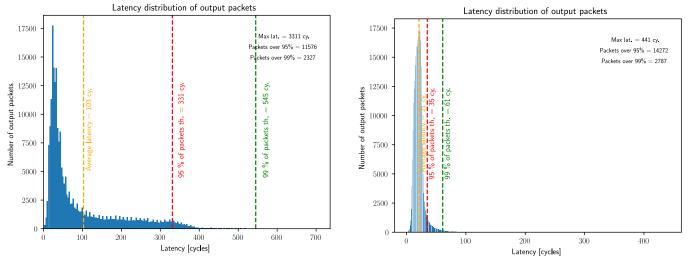

### **LHCb Velopix2 - Results**

| Velopix1   | Proposed                   |

|------------|----------------------------|

| 256x256    | 256x256                    |

| 128x128    | 128x128                    |

| 64x8       | 128x8                      |

| 64 (8 ch.) | 128 (16 ch.)               |

|            |                            |

|            | 256x256<br>128x128<br>64x8 |

| Readout eff. | 80 %     | 99.5 %  |

|--------------|----------|---------|

| Avg. latency | ~100 cy. | ~20 cy. |

# Virtual prototyping

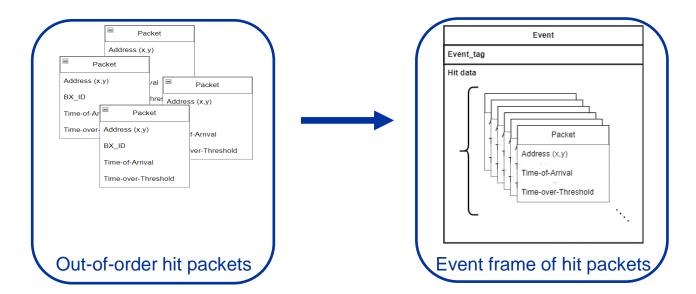

## Sort&Bin – Virtual prototyping

#### Sort&Bin module:

- ASIC module, placed between the EoC and off-chip data links of Velopix2

- Accumulates hit packets over time and groups them in bins based on event tag (BX)

#### Goals:

- Data reduction (~20 %)

- Fixed latency

- Power savings

## Sort&Bin – Virtual prototyping

#### Grouped packets vs # of bins Method: Average latency [#cycles] Develop a **SystemC** Grouping efficiency [%] count description of the module ВΧ Study the **performance** 64 bins with **PixESL**

Target: >90% grouping

# of bins

Number of bins

Target: Bin size > Max packets per event

Hits per BX

Bin size

Hits per BX distribution

Avg hits = 51.2

128 Dackers

ullet

•

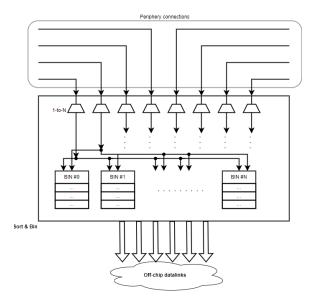

### Sort&Bin – RTL & PnR

#### Sort&Bin:

- 64 Bins with 128 packets per bin

- RTL: DP-SRAM-based module

#### Virtual prototyping:

- facilitates the creation of a new feature in the early stages of the development process

- provides a self-contained prototyping environment

- provides a reference model for RTL validation

- Implemented in 28nm

- Power consumption: ~50 mW

- Area: 3.6 mm<sup>2</sup>

### Conclusions

- PixESL is a valid tool for high-level modelling and architectural analysis

- The framework presents an effective and quick prototyping approach:

- Workforce: ~2 FTE for 3 years (2023-25)

- Development time: ~3 months

- Modelling of Velopix2: ~1 month

- Modelling of Sort&Bin: ~1 week

- Runtime: ~15 BX/s

- Metrics analyzer allows us to find bottlenecks and limitations

- New features can be developed by virtual prototyping

- Project mgmt. Davide Ceresa

- Developer

- Jashandeep Dhaliwal

- Developer

- Francesco E. Brambilla

(<u>davide.ceresa@cern.ch</u>) (<u>jashandeep.dhaliwal@cern.ch</u>) (<u>francesco.enrico.brambilla@cern.ch</u>)

### **CONTRIBUTORS & PLANNING**

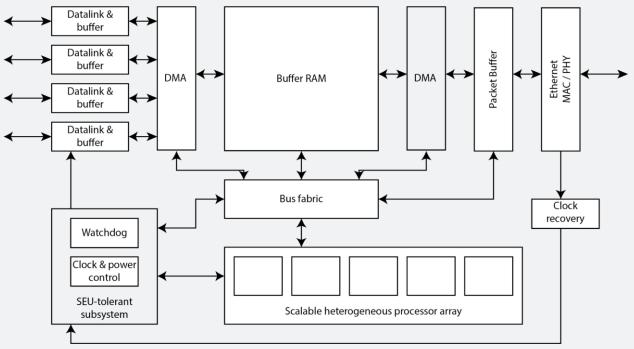

### **UK Consortium Contribution**

- UK (STFC) Consortia

- Royal Holloway, Birmingham, Warwick, Bristol, Manchester, RAL.

- Motivation

- Develop common interface ASIC to couple a range of specialised FE ASICs to a common industry-standard off-detector interface.

- Plans for DRD7.2.c

- Virtual Framework User

- Evaluation and feedback

- Possibly more...

- Contribution

- Q4 2023: requests for funds

- ~1.2 FTE for 4 years

Proposed common interface ASIC for detector readout, timing, and control

### VIRTUAL ELECTRONIC SYSTEM LEVEL PROTOTYPING PROJECT

#### Key notions:

- Abstraction

- Exploration

- Reusability

- Accessibility

#### **Applications**:

- Detector readout architecture

- On-chip processing prototyping

- Front-end/sensor modeling (?)

#### Institutes / Resources:

- Confirmed: CERN / 2 FTE, STFC / 1.2 FTE

- To be confirmed: IPHC Strasbourg / I FTE, PSI / ?

### Plan:

- I. Identify participants (technical contacts)

- 2. Kick-off meeting in late October 2023

- a. User/developer roles

- b. Development Plan

- i. More study cases

- ii. Framework extension

- iii. New tools development

- c. Task assignment

- 3. Project proposal with deliverables