# **Timepix readout**

#### A readout system for a pixelated TPC

#### **Michael Lupberger**

University of Bonn

RD51 7<sup>th</sup> annual meeting, 13<sup>th</sup> - 15<sup>th</sup> of April 2011 CERN

- Motivation

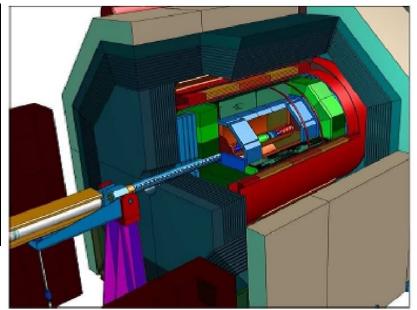

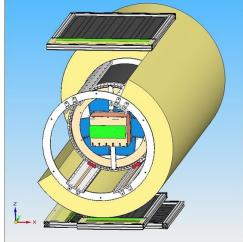

- ILC detector

- TPC tracking

- Endplate concepts

- Timepix chip

- Readout system: status

- New readout system

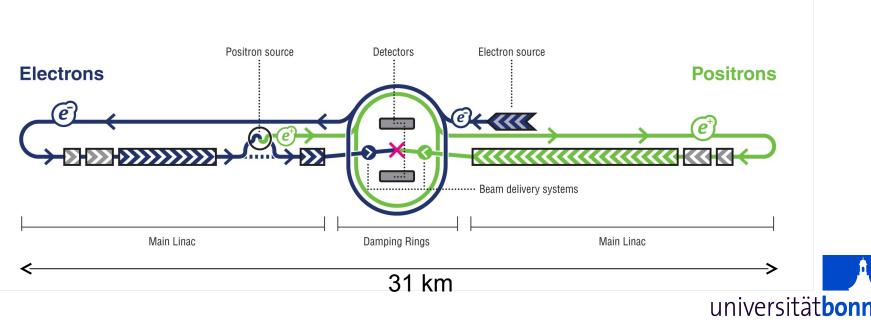

- International Linear Detector

- constrains on momentum resolution:  $\sigma_{1/p} \sim 5 \times 10^{-5}/\text{GeV/c}$

- Use Time Projection Chamber (TPC) as central tracker

| Size                                | ø = 4.1 m                                     |

|-------------------------------------|-----------------------------------------------|

|                                     | L = 4,6 m                                     |

| Momentum res                        | δ(1/p <sub>t</sub> ) ~10 <sup>-4</sup> /GeV/c |

| $\sigma_{_{ m point}}$ in $r arPhi$ | ~100 µm                                       |

| $\sigma_{_{point}}$ in $rz$         | ~ 0,5 mm                                      |

| dE/dx res                           | < 4,5 %                                       |

- For high point resolution

- $\rightarrow$  use micro pattern gaseous detectors

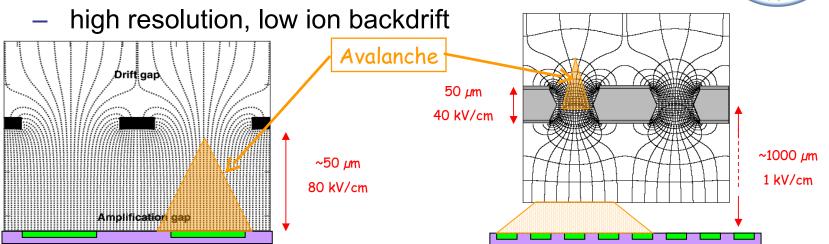

#### **MPGDs**

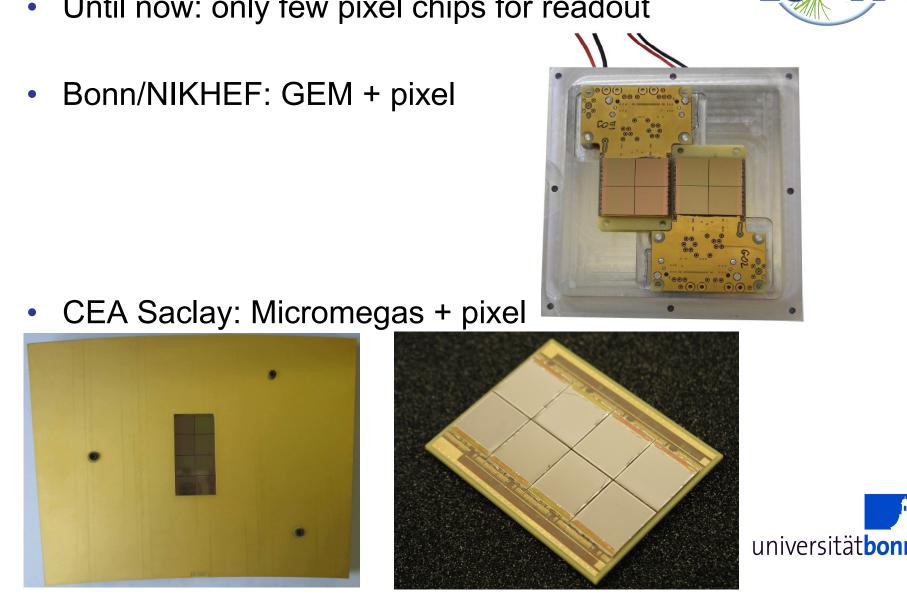

Gas amplification process: Micromegas or GEM

- Readout structure: Pads or pixel

- Different setups tested @ Large Prototype of LCTPC collab.

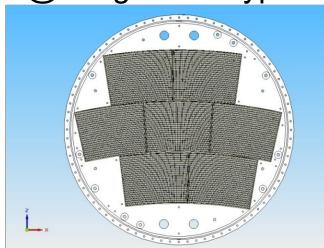

#### **Pixelated endplate**

Until now: only few pixel chips for readout

5

# **Timepix chip**

• Readout chip: The Timepix chip

#### Properties

- 1,4 x 1,4 cm<sup>2</sup> active surface

- 256 x 256 pixel matrix

- CMOS 250 nm technology, IBM

- 55 x 55 µm<sup>2</sup> per pixel

- amplifier/shaper (t<sub>rise</sub> ~150 ns)

- 14 bits count clock cycles

- $\rightarrow$  Pixel pit when/how long

- clock up to 100 MHz in every pixel

- lower threshold

- noise level ~ 500 e-

universität**bon**

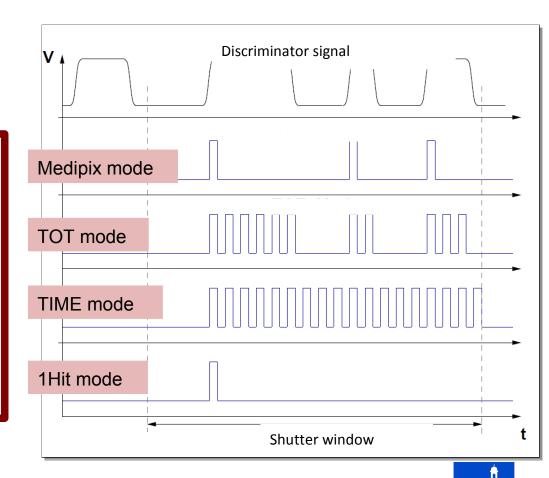

## **Timepix chip**

- 4 different modi to operate

- <u>Medipix:</u>

Pixel hit how often

– <u>Time-over-threshold:</u>

Pixel hit how long

$\rightarrow$  proportional to charge

– <u>Time:</u>

Pixel hit when

$\rightarrow$  time of arrival

– <u>1Hit:</u>

Pixel hit in shutter window

universität**bon**

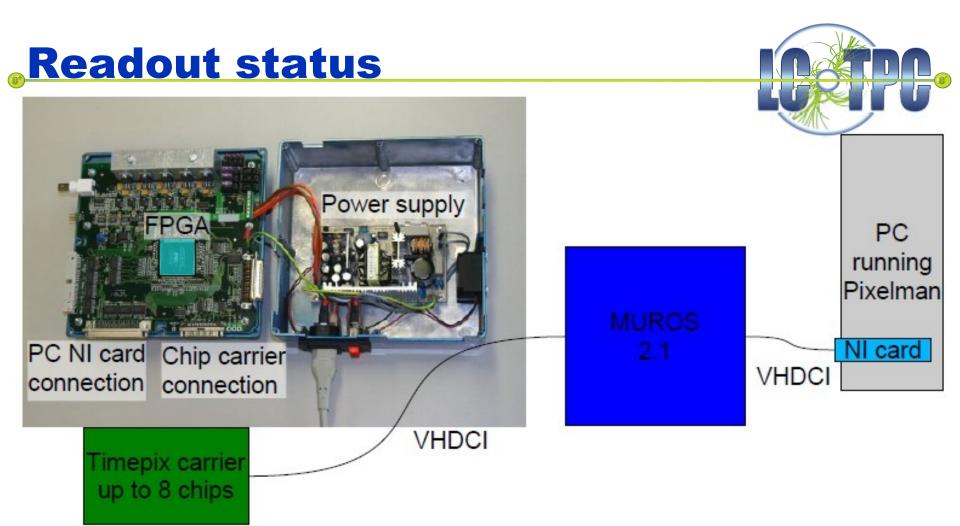

### Readout system: status

• MUROS v2.1:

- designed at NIKHEF for Medipix2 and Timepix chip readout (new FPGA code)

- serial readout for at most 8 Timepix chips

- VHDCI cable <3 m to Timepix carrier board</li>

- VHDCI cable to NI card in PC

- Timepix readout: theo. < 50 frames/sec</li>

lowered by shutter length

- adjustable readout frequency [<240MHz]</li>

- data acquisition on PC(Pixelman software)

http://www.nikhef.nl/pub/experiments/medipix/muros.html

- Problems with MUROS v2.1:

- only limited availability, no production

- NI card and driver out of date

- at most 8 chips daisy chained

#### New readout system

- Goals:

- ultimately read out ~100 chips

- $\rightarrow$  large area detector (e.g. full TPC endplate module)

- modular system  $\rightarrow$  use SRS (RD51)

- ethernet based

- use Virtex6 FPGA

- zero suppression

- triggerable, integrate with slow control & calibration

- Timepix2 compatibility in view

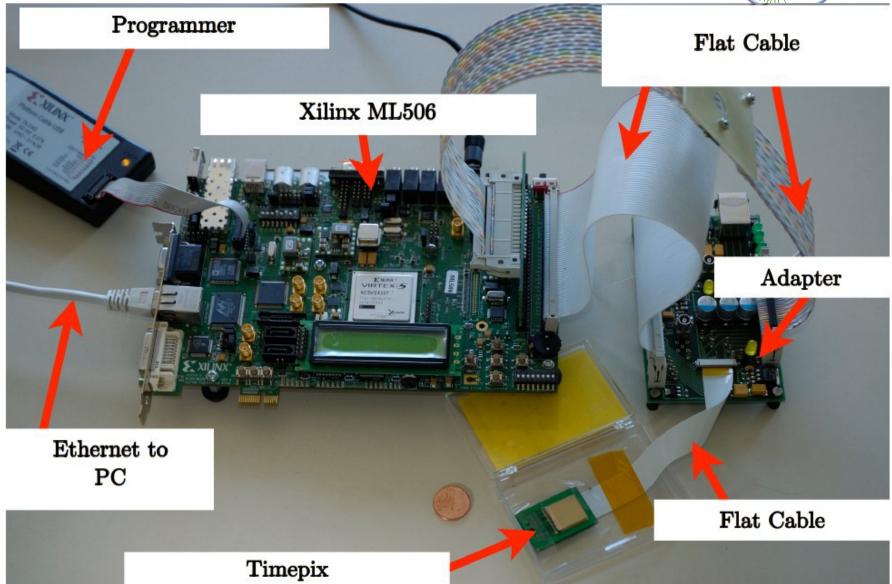

### First steps

- Single chip readout (Uni Mainz)

- Timepix chip on FR4 carrier

- LVDS link

- Adapter board

- trigger

- test pulses

- power supply

- Xilinx ML506 evaluation board (Virtex5)

- Timepix control

- ethernet (UDP) communication

- PC software

- command prompt based

- Timepix control

- data acquisition

#### Mainz readout system

- On-chip Ethernet MAC

- On-board Gigabit Ethernet phy chip

- 1000BASE-T

- no embedded CPU

- Firmware

- VHDL description

- common clock for digitisation and data transfer, crystal based

- serial/deserial interface to the Timepix bit-serial port

- Timepix matrix data not buffered in FPGA

- $\rightarrow$  kept on Timepix while awaiting packet transmission

- shutter with programmable delay and width

- software control or

- external trigger (TLU)

- non-volatile storage of hardware description on CF card universitation

#### Bonn activities

- Setup of second Mainz system in Bonn

- Xilinx ML506 board with Virtex5 FPGA

- single Timepix readout

- adapter board

- Re-target to Virtex6

- Xilinx ML605 board with Virtex6 FPGA

- firmware modifications to Virtex5 VHDL

- new ethernet MAC

- adapt to different clock and pin setup

- implement Timepix control modules

- solve timing problems

- hardware modifications

- new adapter board for cabling

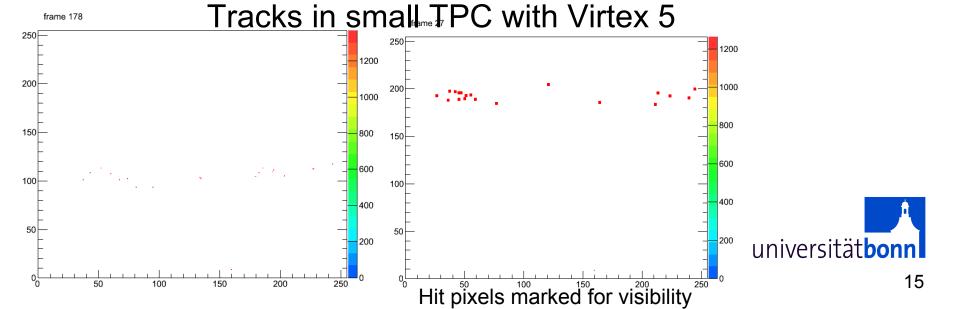

#### **TPC readout with V5/V6** Virtex 5 Virtex 6 frame 0 frame 0

### Way to go

- Use Modular system: Scalable Readout System SRS.

- small set of modular components

- performance at low cost

- designed for scalability

- (e.g. 1 FEC for 8 chips x

- 14 FEC/crate = 112 chips)

- plugin-choice of frontend ASICs  $\rightarrow$  to do

- Multi chip (first step: 4 or 8) readout with Virtex6 (Bonn)

- Or single chip readout with SRS

- Mechanics of box to house Readout card, including all connectors, supplies, switches and LEDs (Saclay)

#### Summery

- Development of pixelated readout for a TPC

- Other field of interest: LHC upgrade:

- pixelatex gaseous inner tracker layers (Gossip)

- concept lately approved by ATLAS upgrade steering committee

- New readout system required

- Development of an FPGA based modular system using SRS

- Read out ~100 Timepix chips

- International Linear Collider

- one of the concepts for a future  $e^- e^+$  collider

- 0.5 TeV (1TeV) centre of mass energy

- beam structure: 1 ms trains every 200 ms

- one interaction point, 2 detectors (push-pull)