DRAFT

# Wishlist future ASIC

Ad-hoc draft for suggestions towards a common ASIC for gas detectors

Please send suggestions **before** the Wednesday 6 Dec WG5 meeting

| Task                                                              | Performance goal                                                                                                                                                                                                           | Comments                                                                                                                                | Possible deliverables next 3-5 y                                                                                                                                        |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Muon systems) New front end electronics                          | <ul> <li>1 fC threshold</li> <li>Geometrical avalanche quenching</li> <li>High sensitivity electronics and new detector structures to achieve stable and efficient operation (rate, occupancy) up to O(MHz/cm2)</li> </ul> | - Study of the integration of the FE electronics in the detector Faraday cage - Study of the integration of electronics and readout PCB | <ul> <li>Conceptual electronics design based on gas detector simulation and experimental measurements</li> <li>Development and test of a front-end prototype</li> </ul> |

| (Large-volume drift chambers) Front-end ASIC for cluster counting | <ul><li>- High bandwidth</li><li>- High gain</li><li>- Low power</li><li>- Low mass</li></ul>                                                                                                                              | achieve efficient cluster counting and cluster timing performances                                                                      | full design, construction and test of a first prototype of the front-end ASIC for cluster counting                                                                      |

| (Straw chamber) Electronic readout, ASIC                          | - Time readout with sub-ns precision - Leading edge and trailing edge time readout                                                                                                                                         | - Dedicated R&D on ASIC                                                                                                                 | - ASIC<br>- Readout system                                                                                                                                              |

| (Time Projection Chambers) Low-power FEE                          | •< 5 mW/ch for >1e6 pad TPC - ASIC development in 65 nm CMOS                                                                                                                                                               | •continuous vs. pulsed                                                                                                                  | - Present stable operation of a multi-<br>channel TPC prototype with a low-<br>power ASIC                                                                               |

| (Gaseous photon detectors) FEE                                    | <ul><li>- High input C</li><li>- Low noise</li><li>- large dynamic range</li></ul>                                                                                                                                         | •                                                                                                                                       | - present an ASIC concept/prototype                                                                                                                                     |

| (Gaseous timing detectors) Low-noise FEE                          | <ul> <li>- High input C</li> <li>- large dynamic range</li> <li>- Fast rise time</li> <li>- sensitivity to small charge</li> <li>- Low noise</li> </ul>                                                                    | •                                                                                                                                       | Define an ASIC                                                                                                                                                          |

## Higher dynamic range

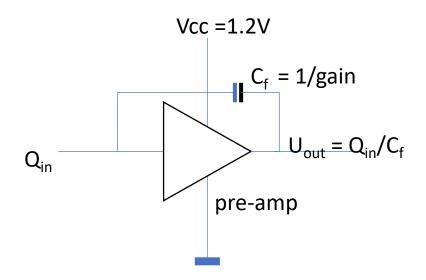

increase  $V_{cc}$  for preamps ? dual gain: Qin -> 2 channels with gain1/gain2 = 4, 8, 16 logarithmic or dual-slope preamp

• • • •

#### Higher rates, less deadtime

interleaved SAR ADC blocks 10 or 12 bit?

••••

### Higher spark immunity

add integrated TVS to inputs

use newer input MOS technologies

add fast common-mode stabilizer to preamp inputs

....

#### More flexible ASIC parameter Controls

add selective I2C register access

#### Faster and slower peaking times

16 ns ... 400ns

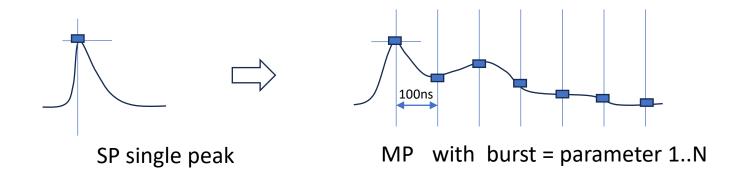

#### picoSeC Ion tail cutter

auto-reset CSA at 1st peak

#### Enhance peakfinder-only mode by adding 10-MHz trailing samples

Add simple Fast OR (threshold) output 32ch or 16 ch ?

Preamp gain settings

settable per channel

power of 2 increase