# Radiation damage investigation of epitaxial p-type silicon using Schottky and pn-junction diodes

E. GIULIO VILLANI, <u>CHRISTOPH KLEIN</u>, THOMAS KOFFAS, ROBERT VANDUSEN, GARRY TARR, ANGELA MCCORMICK, DENGFENG ZHANG, IOANA PINTILIE, ANDREI NITESCU, PHILIP PATRICK ALLPORT, LAURA GONELLA, IOANNIS KOPSALIS, IGOR MANDIC, FERGUS WILSON, YEBO CHEN, PEILIAN LIU

LAST RD50 WORKSHOP, 28 NOV - 1 DEC 2023

#### • What:

- fabricate Schottky and n<sup>+</sup>p diodes on p-type epitaxial (50µm thick) silicon wafers

- doping concentrations as they are normally found in CMOS MAPS devices

#### • <u>Why:</u>

- investigate and gain a deeper understanding of radiation bulk damage in CMOS sensors

- develop reliable damage models that can be implemented in TCAD device simulators

#### • <u>How:</u>

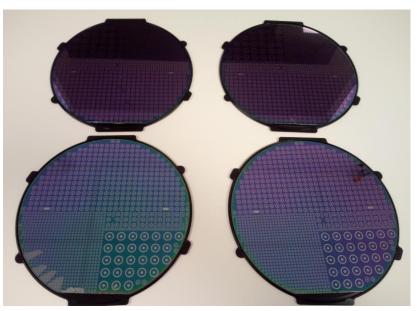

- 6-inch wafers at five B-doped epitaxial levels (10<sup>13</sup> to 10<sup>17</sup> cm<sup>-3</sup>) 25x each, total **125 wafers**

- fabrication process at ITAC (RAL) and Carleton University Microfabrication Facility (CUMFF)

- measurements will be carried out at RAL, Carleton, Birmingham, JSI, IHEP

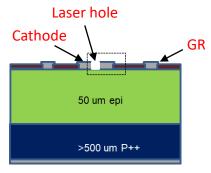

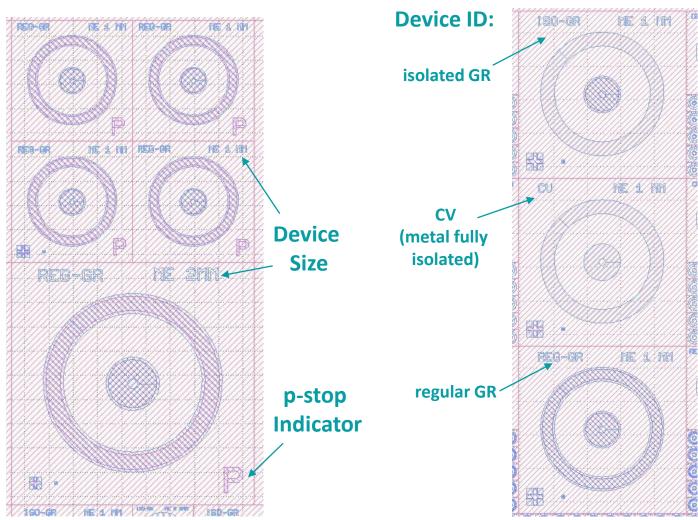

## Design and layout of devices

#### 5 type of devices proposed:

- #1: 2 mm Ø cathode with 0.4 mm Ø central hole, 10 x 10 mm<sup>2</sup> area

- #2: 1 mm Ø cathode, 0.2 mm Ø central hole, 5 x 5 mm<sup>2</sup>

- #3: 0.5 mm Ø cathode, no central hole, 2.5 x 2.5 mm<sup>2</sup>

- #4: 0.1 mm Ø cathode, no central hole, 0.5 x 0.5 mm<sup>2</sup>

- 'cell' with the previous 3 flavors (2,3,4) grouped together, to exploit wafer uniformity on small area

- **#5**: 6 TLM points for contact and epi resistance

- 2 masks only (metal and oxide)

- detailed description during the <u>35th RD50 workshop</u>

## Fabrication details & comparison

#### RAL-ITAC

- Schottky fabrication process only, optimised on test wafers

- oxide deposition @150°C

- Al sputtering immediately after etching (no thin SiO2 layer)

- Al lift-off in Acetone ultrasonic tank

#### CUMFF

- pn-junction and Schottky processes, optimised on test wafers

- 6" substrate wafers laser cut into 4" or 6" wafer pieces

- high temperature thermal oxidation

- Al front metal thermal deposition, back Al via e-beam evaporation

- front metal patterning + etching

full details of fabrication processes in <u>E.G. Villani's</u> <u>talk from the 36<sup>th</sup> RD50 Workshop</u>

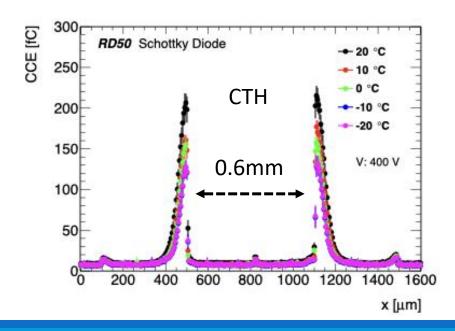

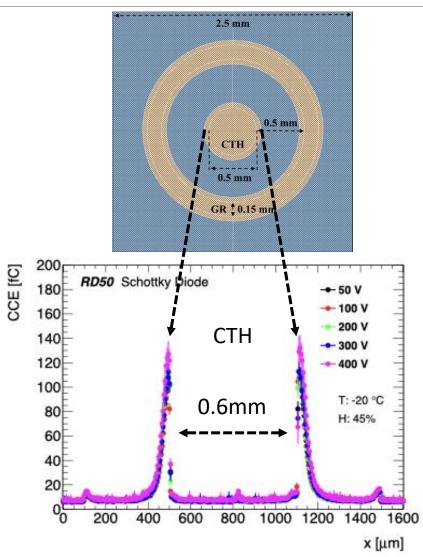

## Charge Collection Efficiency: RAL Schottky (unirrad.)

- Schottky diode with no central laser hole

- Bias Voltages: 50, 100, 200, 300, 400 V

- Temperatures: 20, 10, 0, -10, -20°C

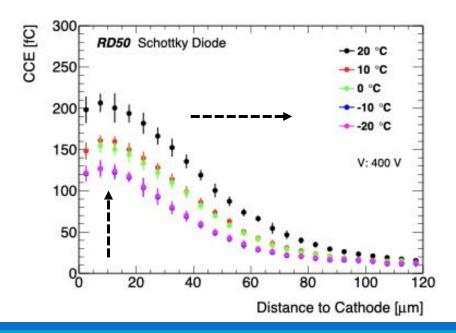

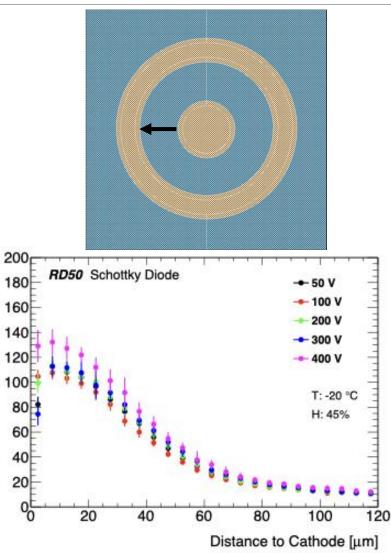

## Charge Collection Efficiency: RAL Schottky (unirrad.)

- depleted thickness decreases with increased distance from the cathode edge

- at fixed bias voltage, the higher the temperature, the larger the CCE; due decrease in light absorption

- at low temperature, no significant improvement on CCE for various bias voltages

CCE [fC]

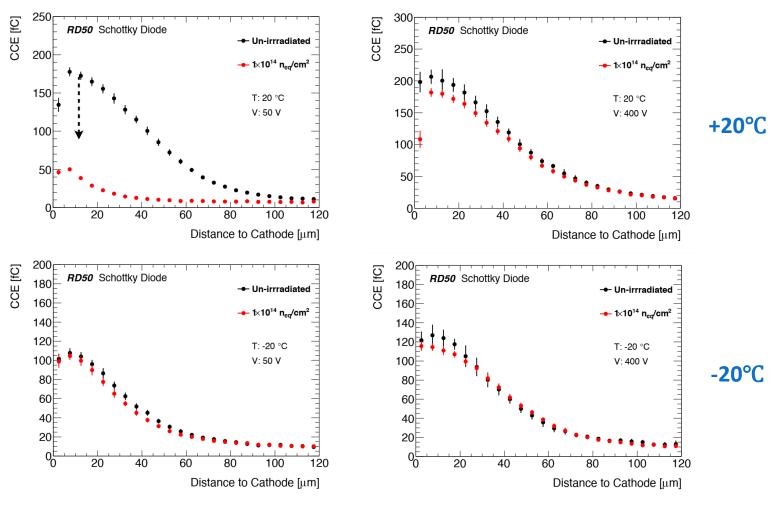

## Charge Collection Efficiency: irrad. RAL Schottky

- CCEs of Schottky diodes before/after neutron irradiation (1x10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>)

- charge trapping effects reduced at higher bias voltage or low temperature

**50V**

**400V**

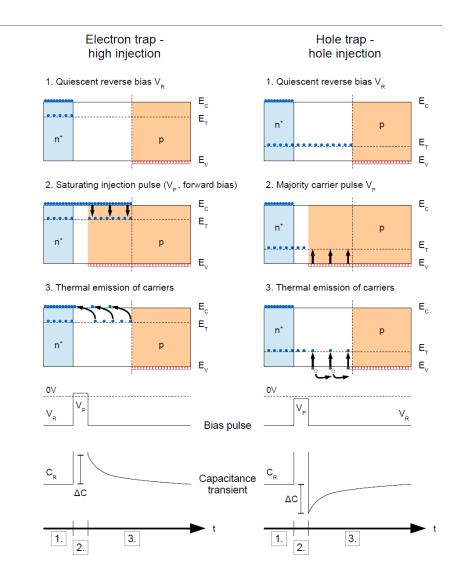

## Measurement methods: DLTS/I-DLTS

- 1. DUT is under constant reverse bias

- filling pulse with specific voltage V<sub>P</sub> and duration is applied, adjusted to trap states of interest

- $V_p$  as reduced reverse bias  $\rightarrow$  majority carrier traps (holes)

- V<sub>P</sub> slight forward bias → minority carrier traps (electrons), if capture rate much larger than competing majority traps

- 3. bias back to prior level, measure transients

- capacitance or current transients, depending on sample

- usually average O(100) transients per temperature point

- plot ΔC or ΔI vs. temperature for fixed rate window corresponding to emission rate

- analysing spectrum for varying rate window [t<sub>1</sub>; t<sub>2</sub>] yields Arrhenius plot of trap levels

## Measurement methods: DLTS/I-DLTS

- 1. DUT is under constant reverse bias

- 2. filling pulse with specific voltage  $V_P$  and duration is applied, adjusted to trap states of interest

- $V_P$  as reduced reverse bias  $\rightarrow$  majority carrier traps (holes)

- $V_p$  slight forward bias  $\rightarrow$  minority carrier traps (electrons), if capture rate much larger than competing majority traps

- 3. bias back to prior level, measure transients

- capacitance or current transients, depending on sample

- usually average O(100) transients per temperature point

- plot ΔC or ΔI vs. temperature for fixed rate window corresponding to emission rate

- analysing spectrum for varying rate window [t<sub>1</sub>; t<sub>2</sub>] yields Arrhenius plot of trap levels

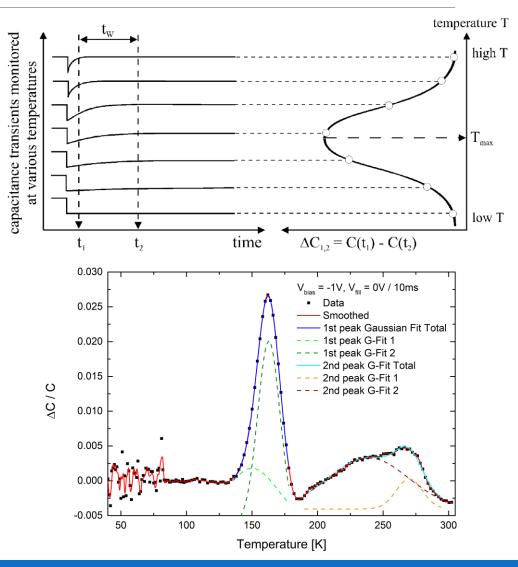

## DLTS: RAL Schottky diode (unirrad.)

DLTS spectrum:

- 1 peak with 2 majority carrier traps

- 'minority' carrier trap

⇒ vanishes for reduced + shorter filling

pulse

$\Rightarrow$  surface/interface states likely

• large majority carrier trap for larger filling pulses at room temperature

| T <sub>median</sub> [K] | E <sub>trap</sub> [eV] | σ [cm²] |

|-------------------------|------------------------|---------|

| 170                     | 0.312                  | 5.5E-15 |

| 180                     | 0.294                  | 3.3E-16 |

2023-Nov-29

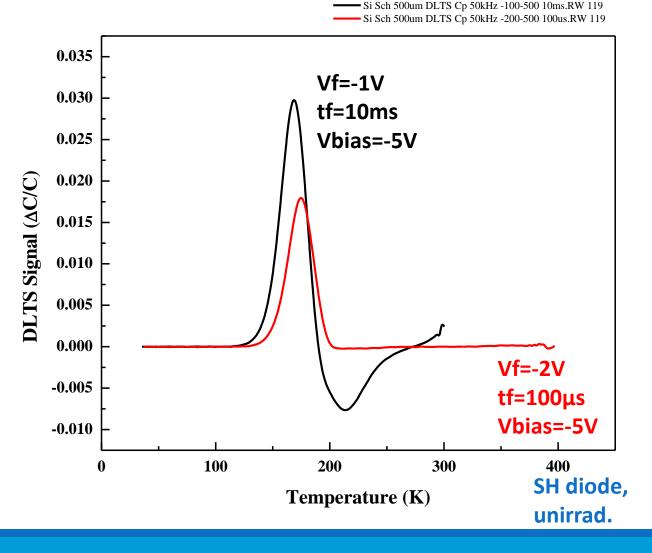

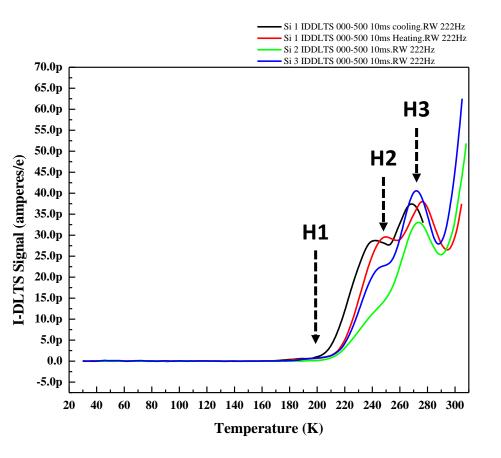

## I-DLTS: irrad. RAL Schottky (Semetrol setup)

- regular DLTS difficult due to high leakage current

- similar to capacitance DLTS, but no AC test signal, measures current transients

- double-pulse variant for increased sensitivity

- filling pulse 0V/10ms at -5V

- trap signals at 200K, 240K, 270K, and possibly >300K

signal at > 300K may be due to increasing current

|    | T <sub>median</sub> [K] | E <sub>trap</sub> [eV] | σ [cm²]        |

|----|-------------------------|------------------------|----------------|

| H1 | 200                     |                        |                |

| H2 | 250                     | 0.46 ± 0.009           | 2.4E-15 ± 1.5X |

| H3 | 275                     | 0.58 ± 0.014           | 4.5E-14 ± 1.8X |

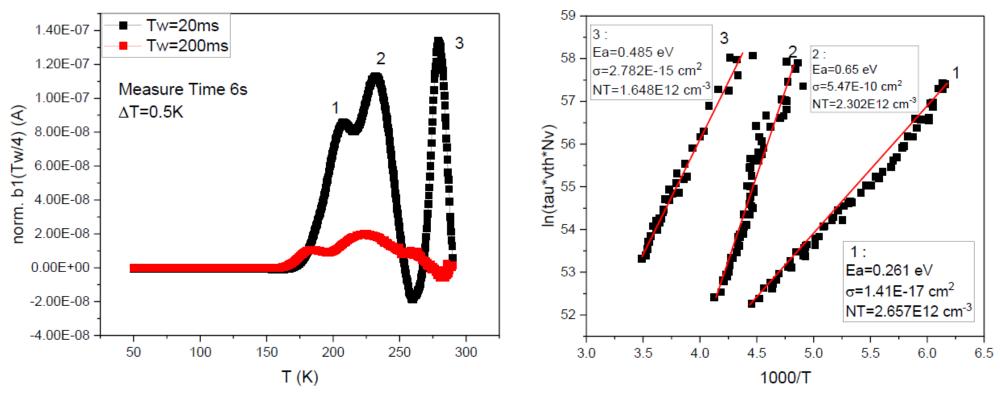

## I-DLTS: irrad. RAL Schottky (Bucharest setup)

• double-pulse I-DLTS

- $-5V_{bias}$ ;  $V_{fill,1} = -5V / 10ms$ ;  $V_{fill,2} = 0V / 10ms$

- three deep defects identified

SH diode, 1x10<sup>15</sup> irrad.

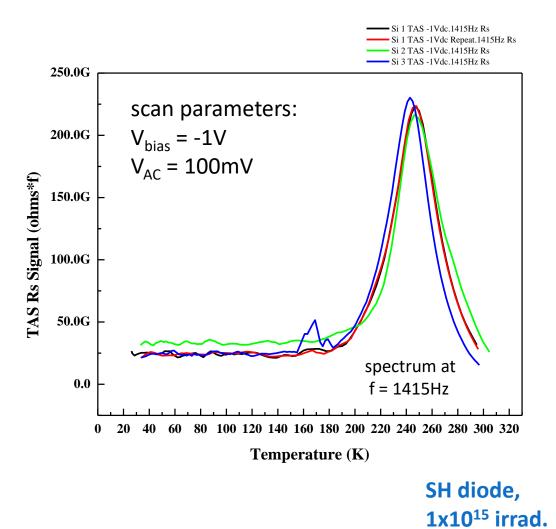

#### TAS: irrad. RAL Schottky

- measure capacitance, resistance, and conductance as function of frequency and temperature

- steps/peaks in temperature dependence indicate thresholds for new traps contributing

- applicable for low-doped or high-resistivity materials

- complements DLTS

- useful for irradiated devices with high fluences

- trap energy is 0.4-0.5 eV above the valence band

- consistent with I-DLTS results

| sample        | E <sub>trap</sub> [eV] | σ [cm²]                      |

|---------------|------------------------|------------------------------|

| Si 1          | 0.433 ± 0.006          | 3.6x10 <sup>-14</sup> ± 1.3X |

| Si 1 (repeat) | 0.422 ± 0.008          | 2.2x10 <sup>-14</sup> ± 1.5X |

| Si 2          | 0.486 ± 0.008          | 4.0x10 <sup>-13</sup> ± 1.5X |

| Si 3          | 0.445 ± 0.009          | 9.3x10 <sup>-14</sup> ± 1.5X |

2023-Nov-29

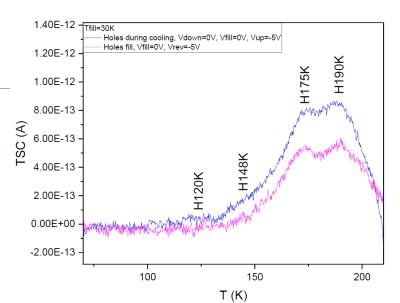

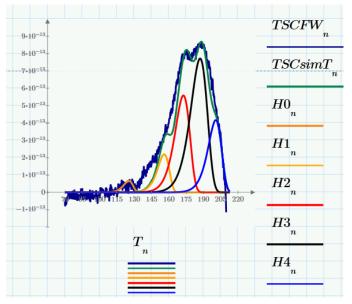

#### TSC: irrad RAL Schottky

- two measurements with cooling under different conditions:

- OV during cooling, deep defects filled with holes

- reverse bias -5V during cooling, 0V filling pulse at 30K

- heating 11K/min with -5V<sub>bias</sub>

- TSC spectrum results simulated:

|                                                                             | $E_t(eV)$ | $\sigma(cm^2)$   | $N_T(cm^{-3})$           |

|-----------------------------------------------------------------------------|-----------|------------------|--------------------------|

| H0 (known as H116K, hole<br>trap with electric field<br>enhanced emission)  | 0.3       | $7 * 10^{-16}$   | $1.05 * 10^{11}$         |

| H1 ((known as H140K, hole<br>trap with electric field<br>enhanced emission) | 0.375     | $4 * 10^{-16}$   | 4.3 * 10 <sup>11</sup>   |

| H2 (known as H152K, hole<br>trap with electric field<br>enhanced emission)  | 0.354     | $4 * 10^{-18}$   | 13.85 * 10 <sup>11</sup> |

| H3                                                                          | 0.368     | $1.1 * 10^{-18}$ | $21.5 * 10^{11}$         |

| H4                                                                          | 0.538     | $4.5 * 10^{-15}$ | $9.5 * 10^{11}$          |

#### SH diode, 1x10<sup>15</sup> irrad

- RAL Schottky diodes underwent neutron irradiation at Ljubljana

- post-irradiation results from DLTS and CCE measurements

Outlook:

- CUMFF pn-junction diodes sent out for irradiation

- > TCAD simulations of Schottky diodes ongoing

- ongoing charge collection measurements at RAL and DLTS + TAS at Carleton

comparison of pre/post-irradiation, input for TCAD simulation

## Backup

#### **Fabrication details**

#### <u>CUMFF</u>

new masks made, including isolated MOS gate GR variation for all device types + optional p-stop

full 6" Schottky wafers @RAL

new masks with different structure flavours @CUMFF

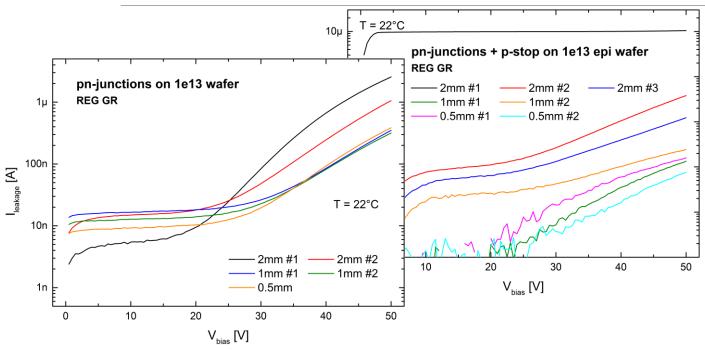

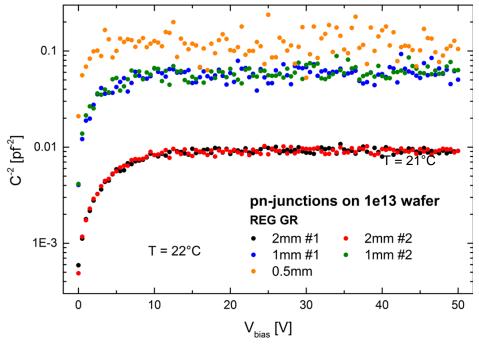

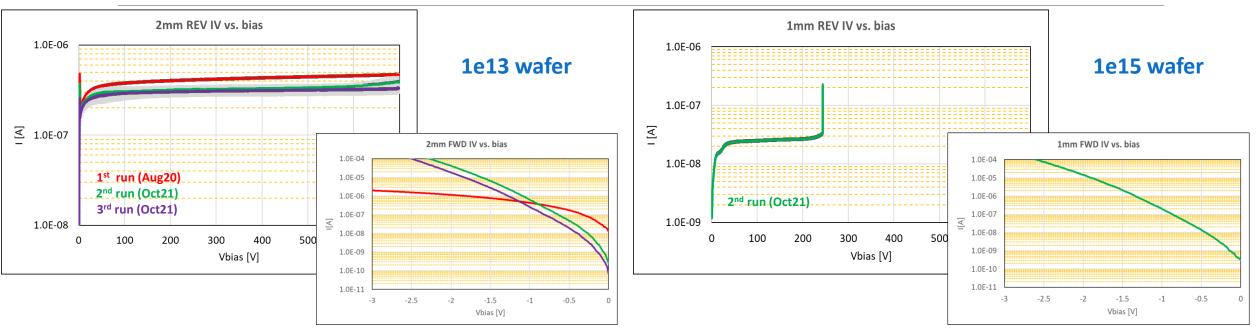

## IV + CV measurements: CUMFF pn-junctions (1e13 vs. 1e16)

- current can vary by large margin on same wafer

- very low initial current often seen

- no hard breakdowns observed; gradual increase in current

- leakage current at much lower levels compared to first fabrication iterations

#### more basic electrical measurements in backup

- depletion of epi layer at low voltages

- small differences for different structure flavours

- agrees with back-of-the-envelope calculation for high-resistivity 50um epi layer

- capacitance scales nicely with structure size

#### IV measurements: RAL Schottky (1e13 vs. 1e15)

- reverse bias IV similar in all runs, slightly lower leakage in the two latest runs

- breakdown voltage > 700V

- forward bias shows very different characteristics

- expected lower leakage in reverse bias, with lower BV

- measured BV is high for this doping

- forward bias ~linear

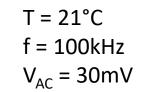

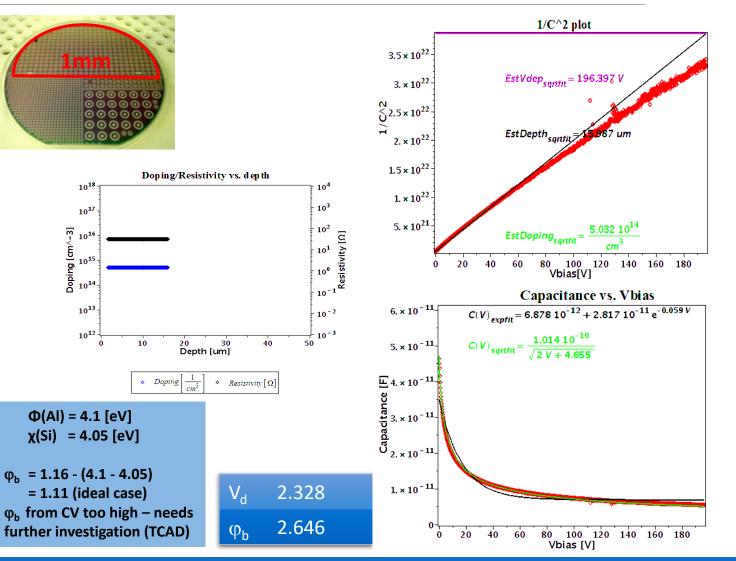

#### CV measurements: RAL 1e13 Schottky

#### CHRISTOPH KLEIN - LAST RD50 WORKSHOP

1018

10<sup>17</sup>

√ mɔ] 10<sup>15</sup> Buido 10<sup>14</sup>

10<sup>13</sup>

10<sup>12</sup>

$\Phi(AI) = 4.1 [eV]$  $\chi(Si) = 4.05 [eV]$

$\phi_{\rm b} = 1.16 - (4.1 - 4.05)$

= 1.11 (ideal case)

10

μ 10<sup>16</sup>

2023-Nov-29

## CV measurements: RAL 1e15 Schottky

- 2 HR wafers show doping as expected

- CV plot not really well described by  $1/\sqrt{V}$  fit

- barrier height estimate from CV too high

- estimate from IV in progress

- devices on 1e15 wafer so far show very good  $1/\sqrt{V}$  Cap dependence

- doping as expected

- barrier height clearly too high

$T = 21^{\circ}C$ f = 100 kHz $V_{AC} = 30 mV$

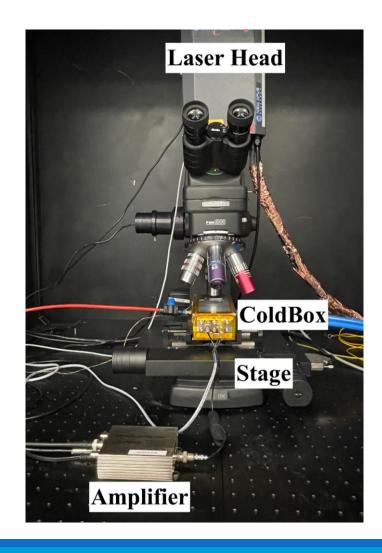

## **Charge Collection Efficiency: Setup**

- Laser: IR(1064 nm), 5µm x 50µm, 23.44 ± 0.2 pJ

- Stage: move step of 5µm

- Temperature: -20°C ... +20 °C