# **Commissioning of the Upstream Tracker for the LHCb Upgrade I**

## S. Cesare, on behalf of the LHCb UT collaboration

Università degli Studi di Milano, INFN Sezione di Milano

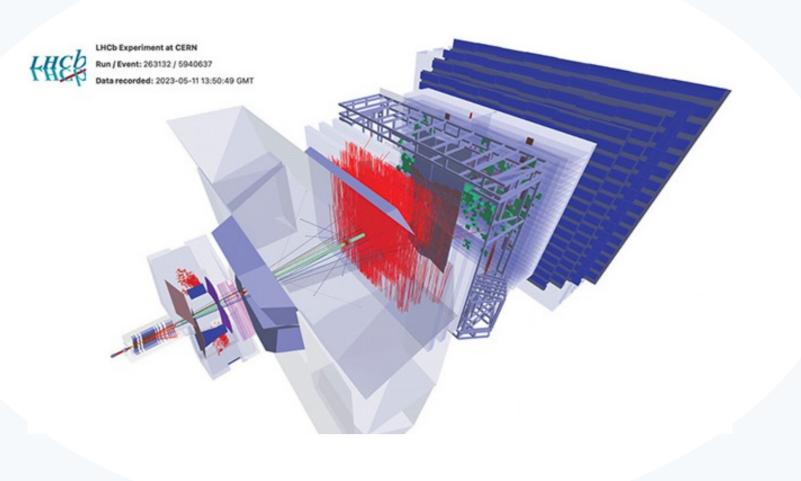

## LHCb AND THE UPSTREAM TRACKER

- The LHCb experiment is a forward spectrometer located at the Large Hadron Collider (LHC).

- The Upstream Tracker (UT) is placed upstream of the bending magnet and is fundamental for: - software trigger implementation - reconstruction of  $K_S$  and  $\Lambda$ - reduction of the ghost rate

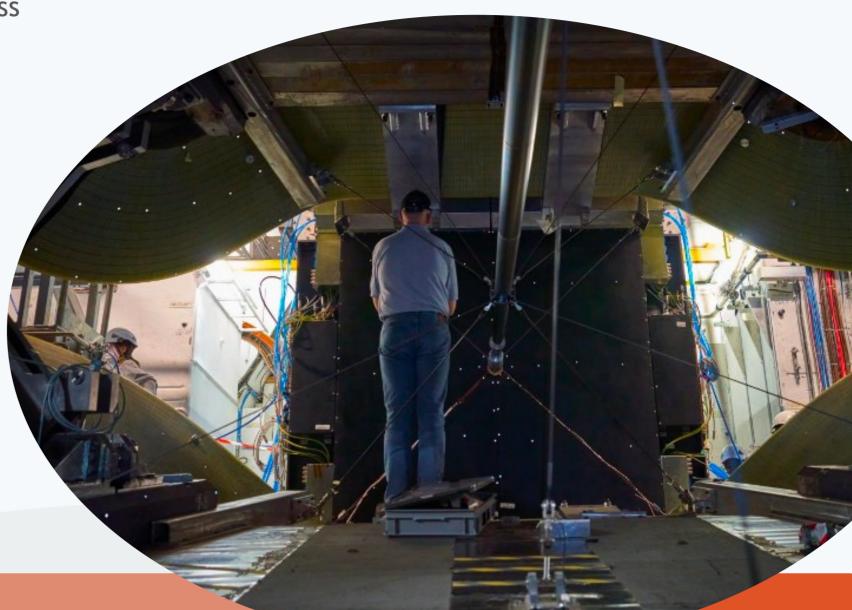

## **A SILICON STRIP DETECTOR**

- Four planes of silicon microstrip sensors with vertical and stereo (+/- 5°) orientation

- **A-Type:** p-in-n, 190 μm pitch, 320 μm thickness

- **B- Type** n-in-p, ½ pitch, 320 μm thickness

- **C-**, **D-**type: n-in-p, ½ pitch, 250 µm thickness

- Expected to operate at -5° C

- Hybrids: VERA (4 ASICs), SUSI (8 ASICs)

- Front-end ASIC (SALT):

- **CMOS** 130 nm

- Peaking time ~ 25 ns

- **S/N** ~ 15

- Rad hard: 30Mrad TID +TMR against SEE effects

Installation completed successfully in March 2023.

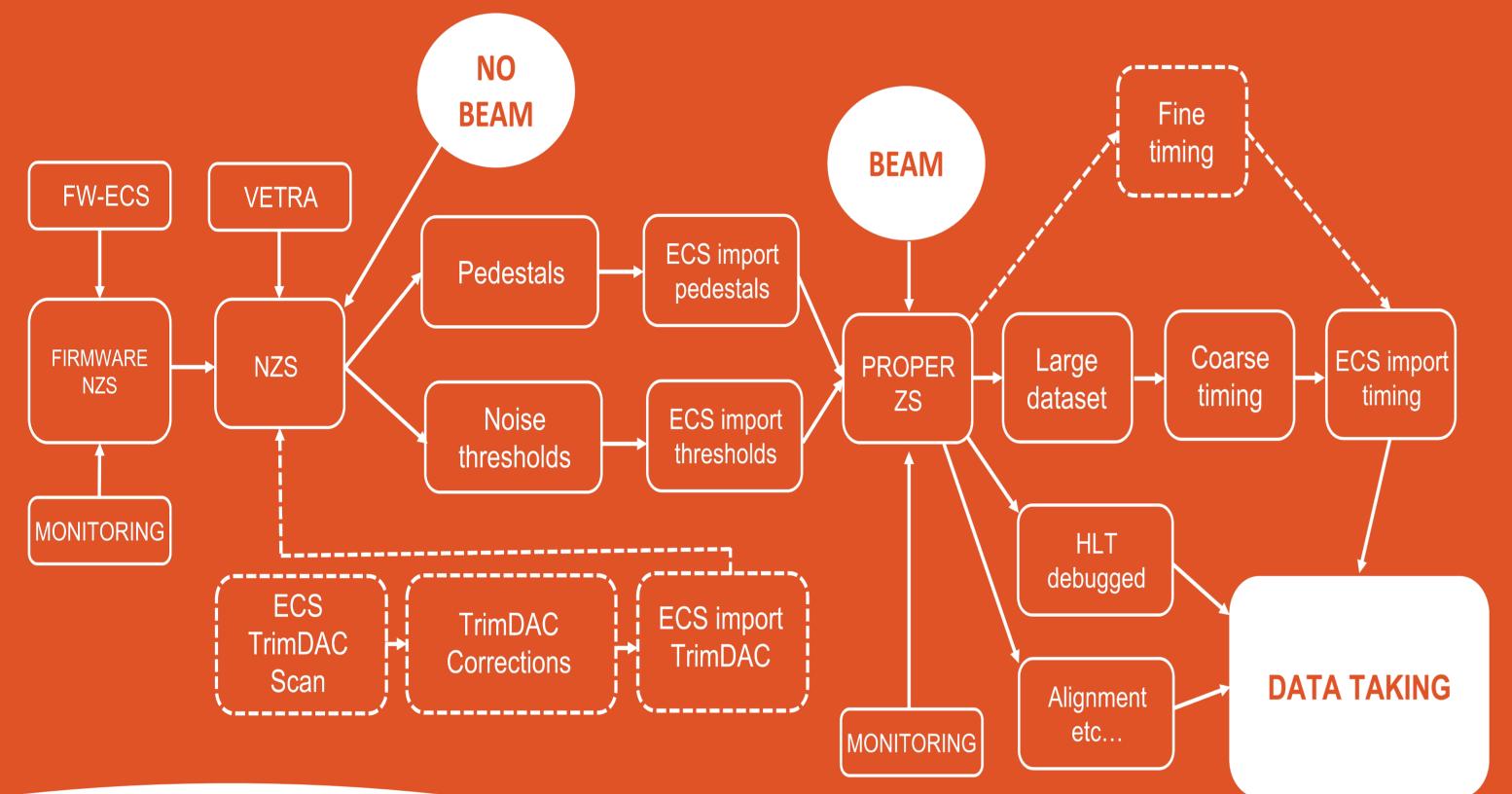

# PATH TO DATA TAKING

## **TIME ALIGNMENT**

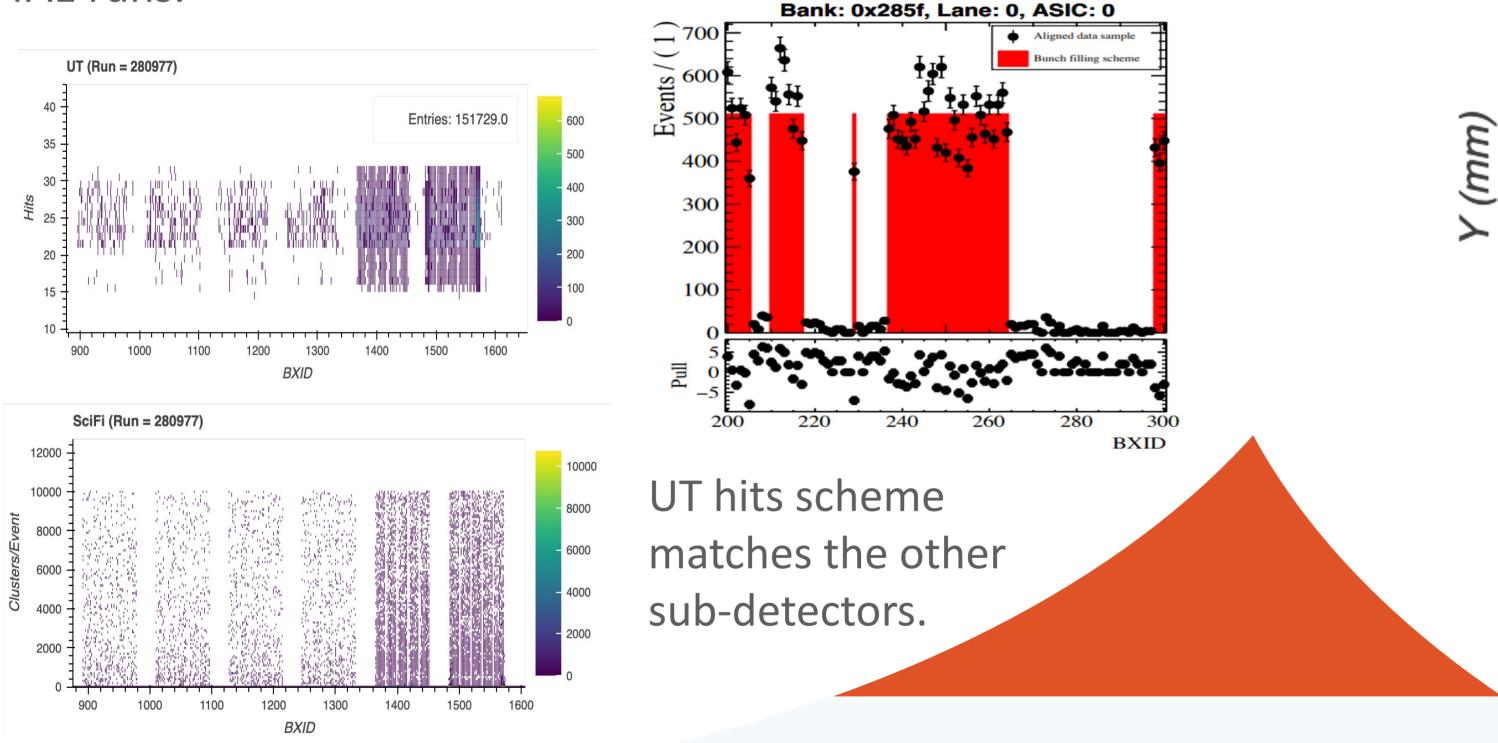

Need to align the UT hits with the bunch filling scheme of the LHC (BXID)

## FIRMWARE

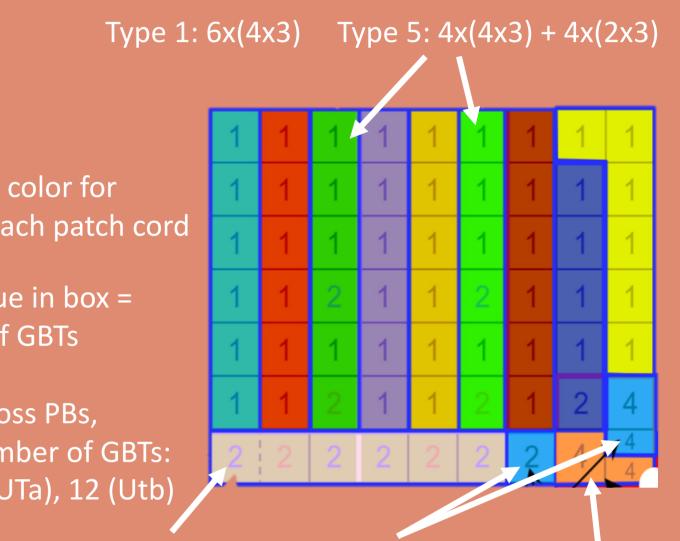

The readout of the detector is made with PCIe40 cards hosting Intel Arria 10 FPGA. UT firmware has 5 different flavours used for different detector regions having different occupancies.

| GBT frame byte | 13 | 12 | 11     | 10 | 9 | 8      | 7 | 6      | 5      | 4      | 3 | 2 | 1 | 0 |  |

|----------------|----|----|--------|----|---|--------|---|--------|--------|--------|---|---|---|---|--|

| 4 x 3-eports   |    |    | 24-bit |    |   | 24-bit |   | 24-bit |        | 24-bit |   |   |   |   |  |

| 2 x 3-eports   |    |    | 24-bit |    |   |        | 2 | 24-bit |        |        |   |   |   |   |  |

| 2 x 4-eports   |    |    | 32-bit |    |   |        |   |        | 32-bit |        |   |   |   |   |  |

| 2 x 5-eports   |    |    | 40-bit |    |   |        |   | 40-bit |        |        |   |   |   |   |  |

Value in box = # of GBTs Implemented to work in Non-zero-suppressed (NZS) Across PBs, Number of GBTs: and in Zero-suppressed (ZS) 10(UTa), 12 (Utb) mode

Type 2: 10/12x(2x3) Type 3: 10x(2x4) Type 4: 8x(2x5)

First data collected in the **Global LHCb** data taking during the lons run (Pb-Pb collisions) before the start of YETS 2023-2024, useful to develop offline software.

The ZS bank decoder provides the number of hits for each ASIC that are then fitted to the BXIDs histograms without the need of dedicated TAE runs.

#### UTaU (Layer1) - Granularity per SECTOR (4 ASICS) (Run = 280977)

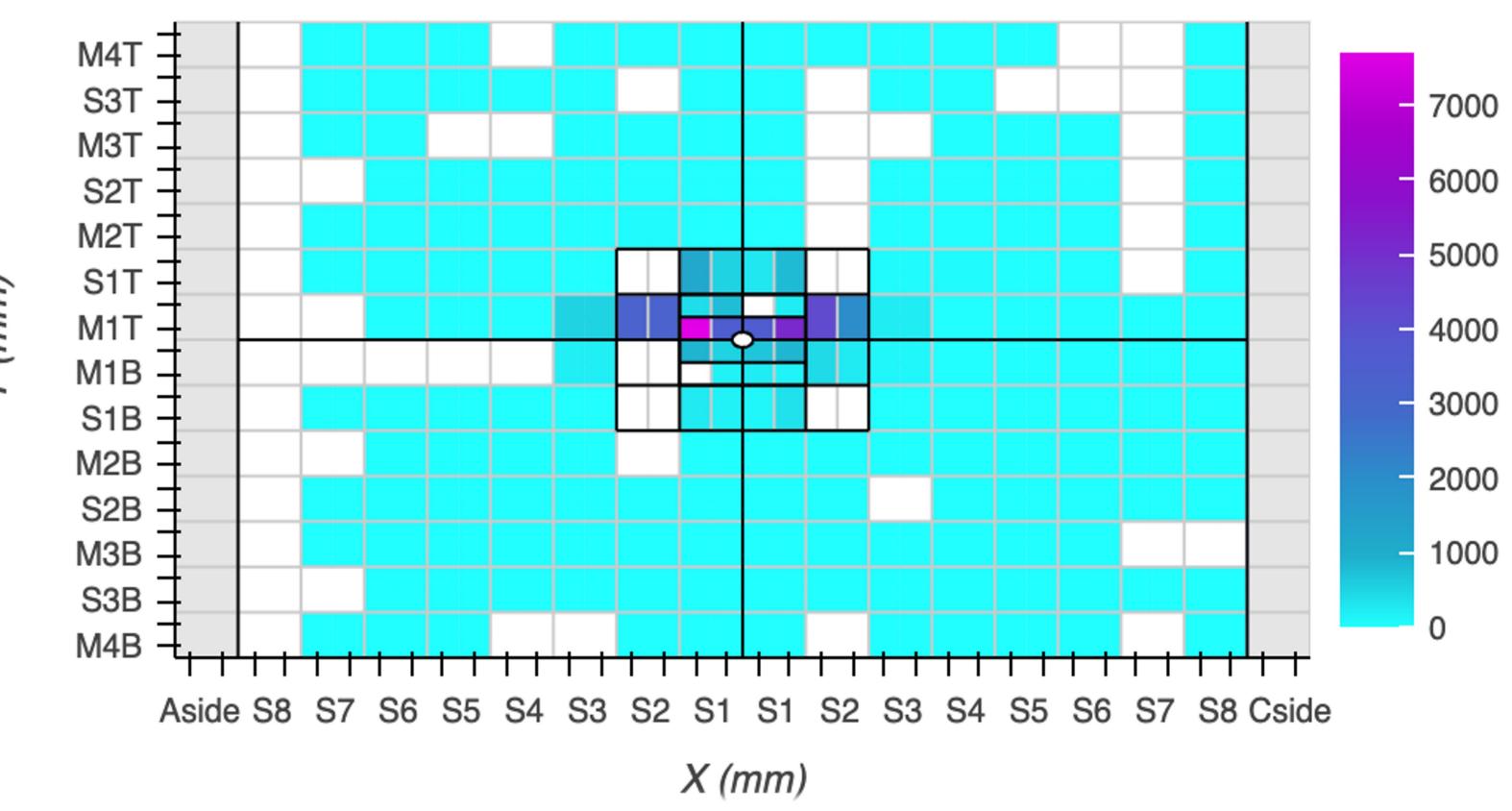

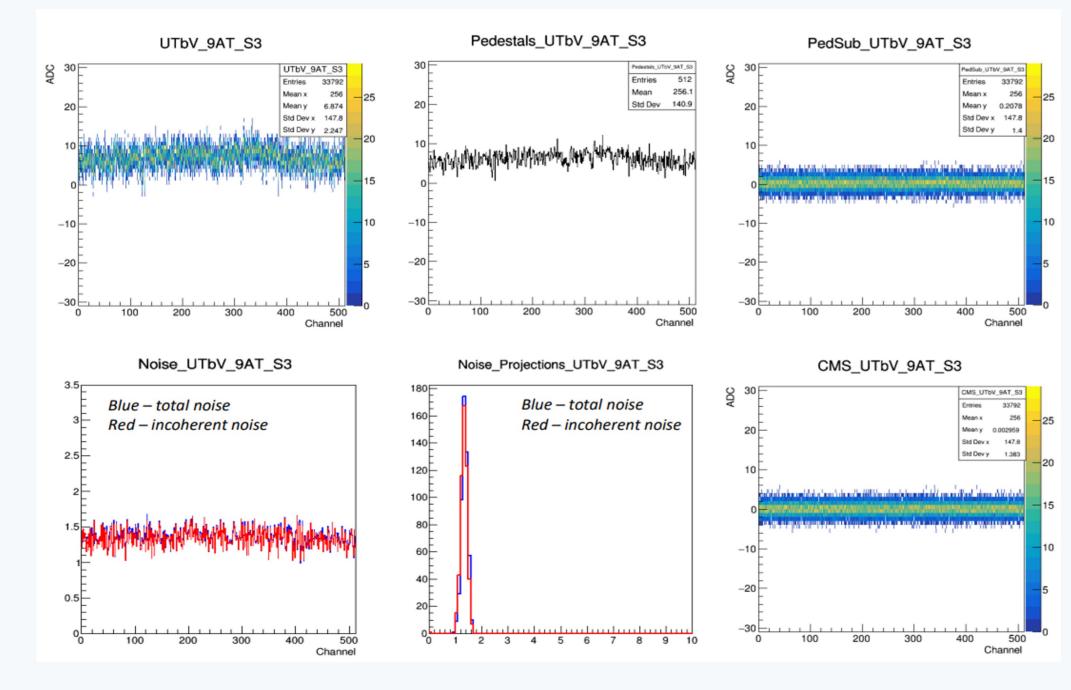

### **OFFLINE CALIBRATION**

Dedicated software package (VETRA), part of the LHCb software project.

#### **CURRENT STATUS AND NEXT STEPS**

Preliminary results:

- uniform incoherent noise in the detector

- observed the variation of pedestals across the layer

- noise check after pedestal subtraction

- agreement with the early performance studies

- Detector performances measured in the commissioning phase are aligned with the ones measured in the laboratory.

- Ongoing analysing of the first commissioning data.

- First data acquisition in Global data taking of LHCb during the ion runs.

- Continuing working to guarantee stable data taking conditions.

#### **ACKNOWLEDGMENTS**

We acknowledge the outstanding effort of the LHCb collaboration and of the UT group. S.C. acknowledges support from the ERC Consolidator Grant SELDOM G. A. 771642.

13<sup>th</sup> LHC students poster session, Nov. 27<sup>th</sup> 2023