## Assembly and Testing of ATLAS ITk pixel detector modules + Argonne Micro Assembly Facility (AMAF) virtual tour

2024, May 15

DPF-PHENO 2024 at University of Pittsburgh/Carnegie Mellon University

https://indico.cern.ch/event/1358339/contributions/5899237/

Kim Doyeong 김도영 Argonne National Laboratory

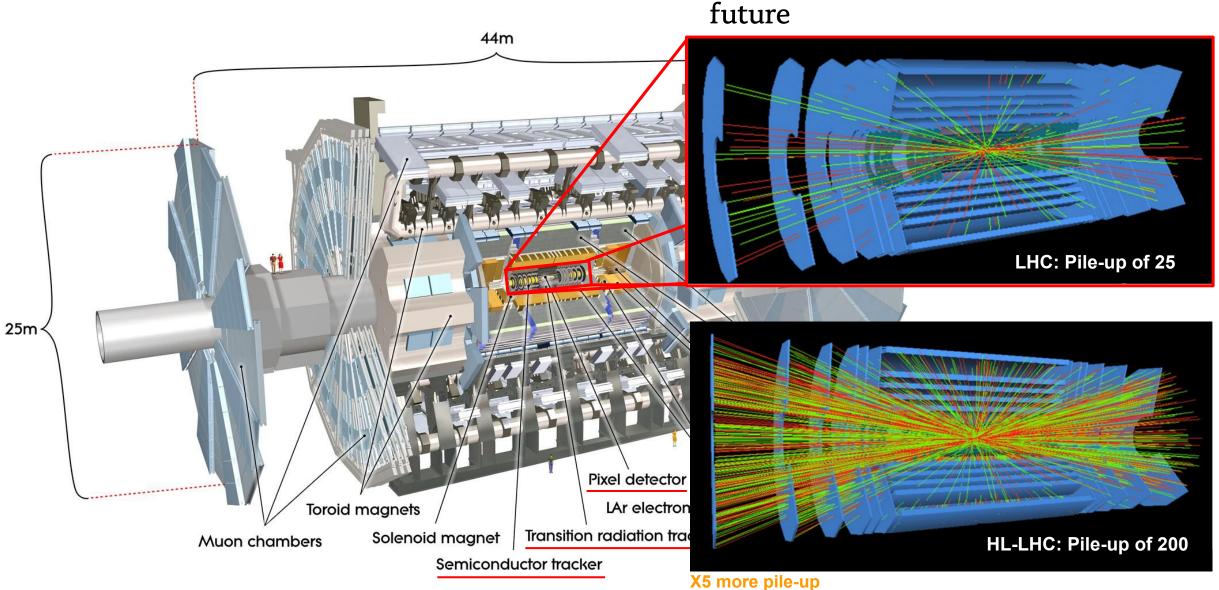

# Why we want the HL-LHC upgrade?

GOAL of the HL-LHC: to increase the integrated luminosity by a factor of 10 beyond the LHC's design value

Photo by Maximilien Brice, CERN

Kim Doyeong 김도영, Argonne National Laboratory

## ATLAS: multi-purpose particle detector

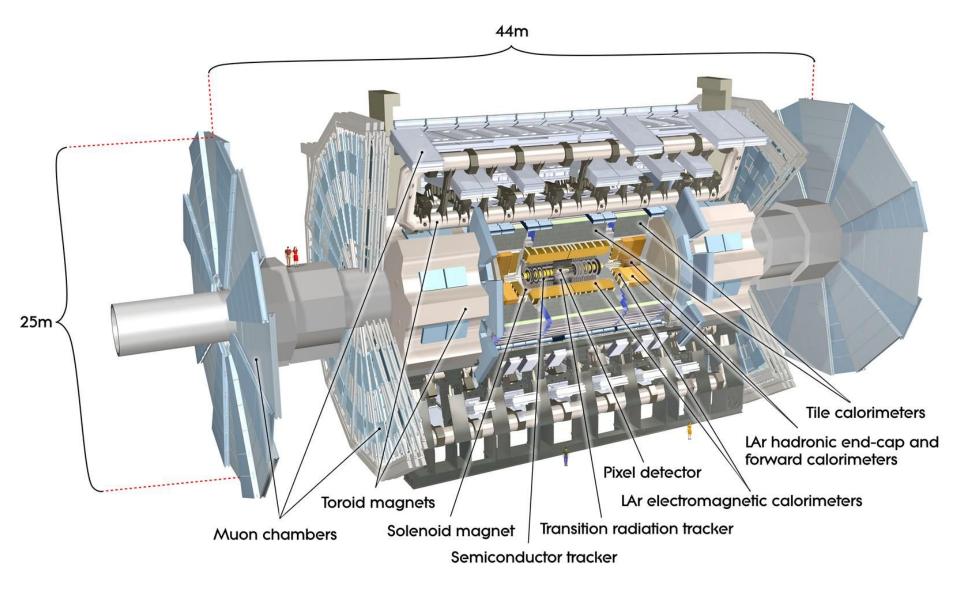

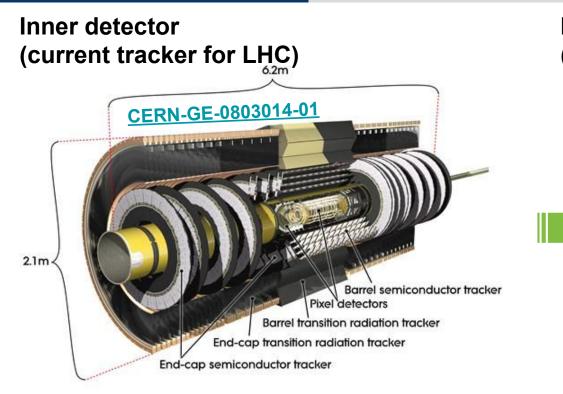

## **Inner Detector:** current ATLAS tracker for LHC

## Inner Detector: current ATLAS tracker for LHC

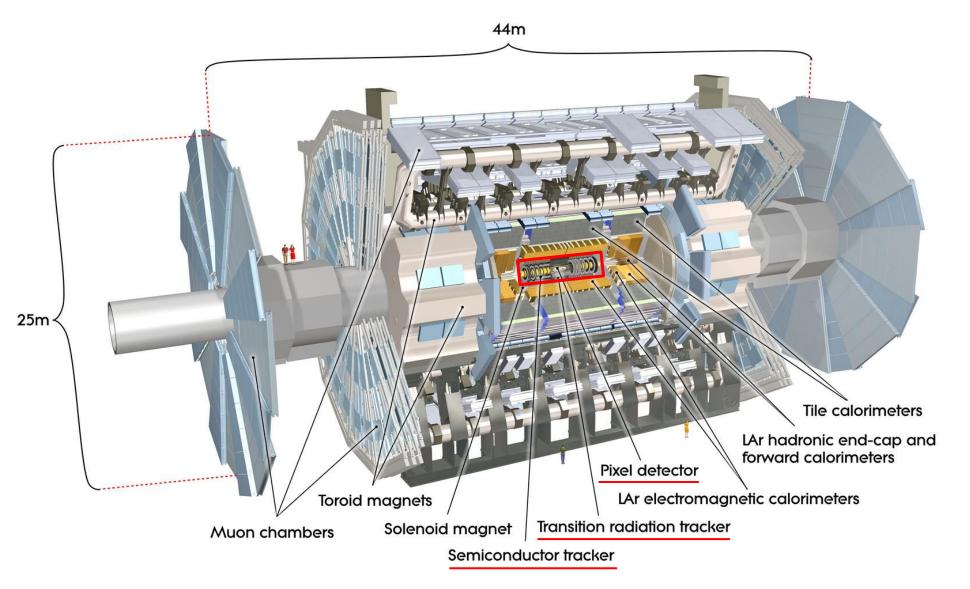

# Challenges in HL-LHC data taking condition

Kim Doyeong 김도영, Argonne National Laboratory

unprecedented radiation environment

6

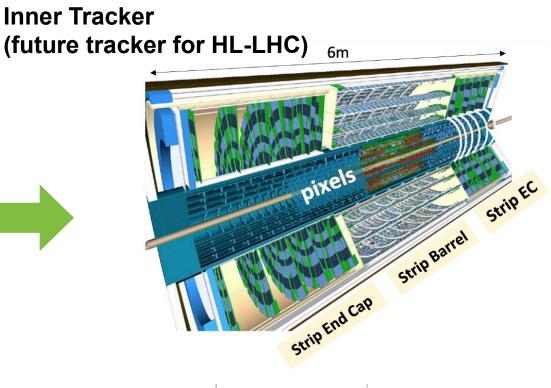

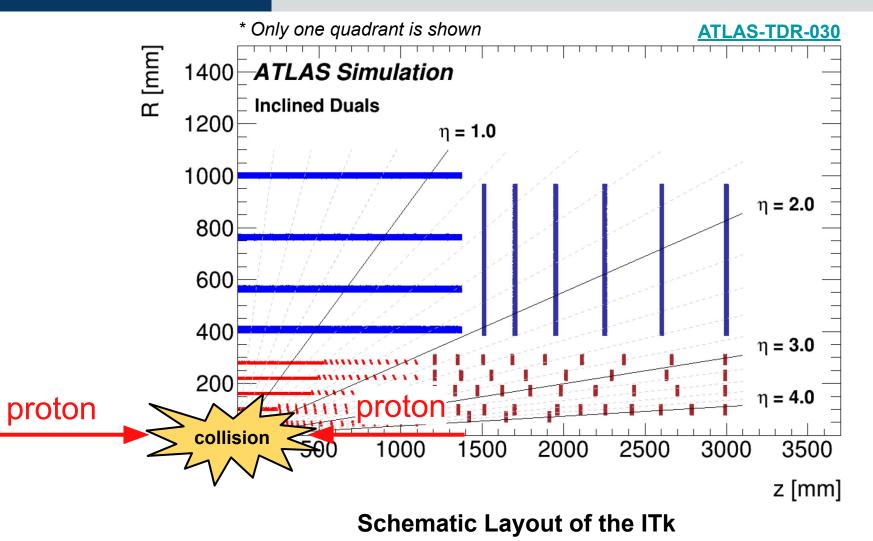

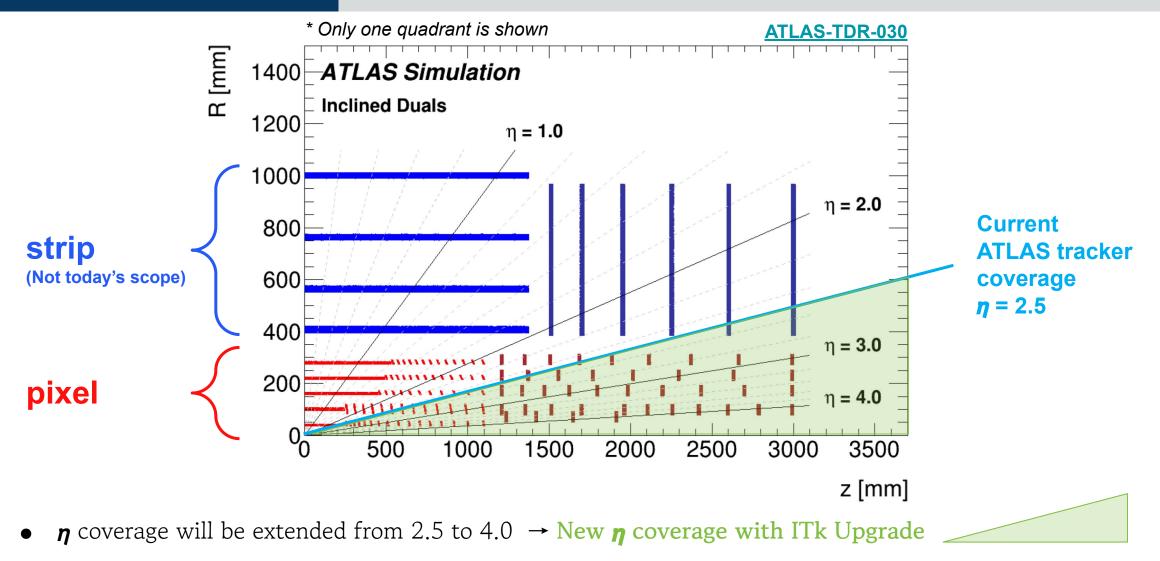

# ATLAS Inner Tracker (ITk) Upgrade

- HL-LHC upgrade will involve current ATLAS tracker being replaced by all-silicon Inner Tracker (ITk) Tracker (ITk)

- New technology: silicon sensors, readout, data transmission, and improved radiation hardness

|                    | Inner Detector | Inner Tracker |      |

|--------------------|----------------|---------------|------|

| # of pixels        | 92 milliion    |               | X 55 |

| Pixel Silicon area | 1.9 m²         | 12.98 m²      |      |

| Trigger rate       | 100 kHz        | 1 MHz         | X 10 |

| η coverage         | 2.5            | 4             |      |

## New territory with the ITk Upgrade

## New territory with the ITk Upgrade

# New territory with the ITk Upgrade

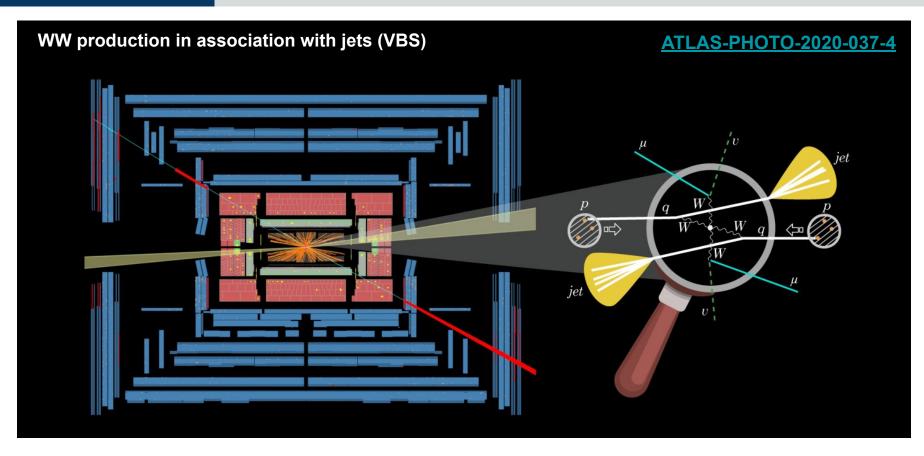

- The forward tracker extension significantly improves the measurement precision in the benchmark physics channels

- Simply increasing the integrated luminosity will not lead to significant improvement without the forward extension

Kim Doyeong 김도영, Argonne National Laboratory

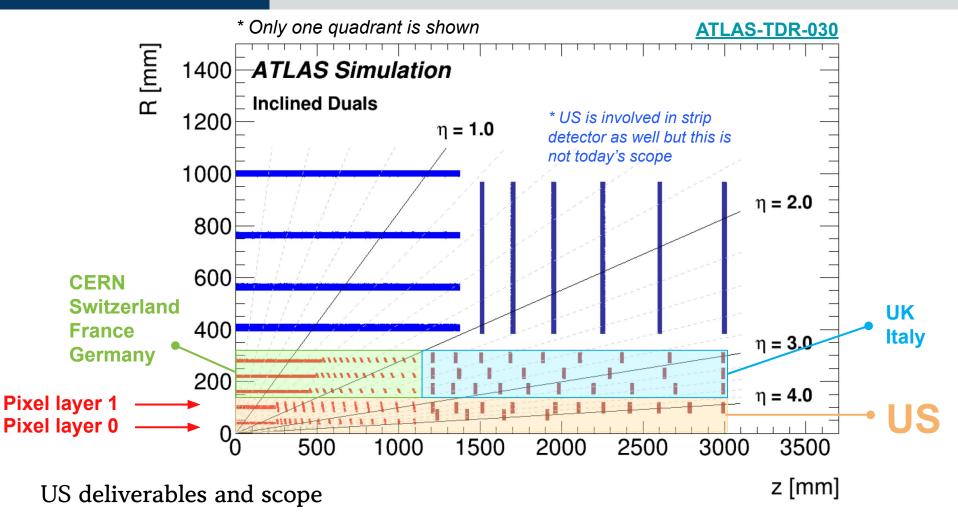

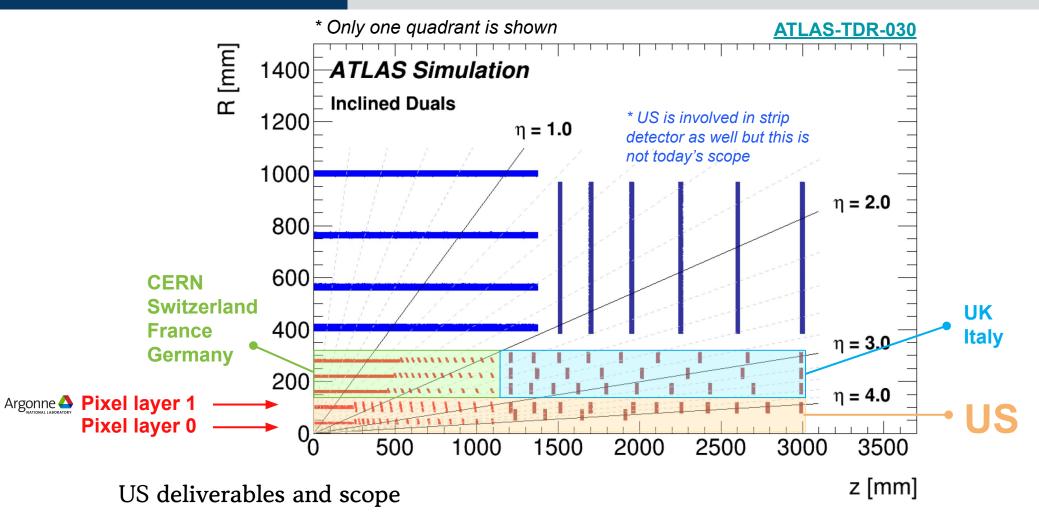

# ATLAS ITk pixel

- Layers 0-1: Inner System (IS)

- Layers 2-4: Outer System (OS) 1) Outer Barrel (OB)

Kim Doyeong 김도영, **Argonne National Laboratory**

2) Endcaps (EC)

# ATLAS ITk pixel

- Layers 0-1: Inner System (IS)  $\rightarrow$  A fully integrated standalone detector

- $\circ$   $\,$  Mechanical design, Module assembly and loading, integration  $\,$

# ATLAS ITk pixel

- Layers 0-1: Inner System (IS)  $\rightarrow$  A fully integrated standalone detector

- Mechanical design, Module assembly and loading, integration

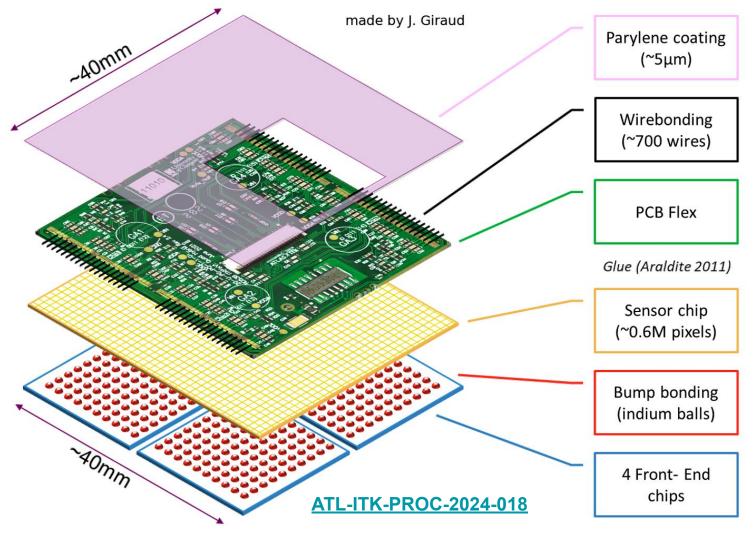

# ITk Pix Module at ANL ITk pixel sub-detector: Layers 1 of Inner System (IS)

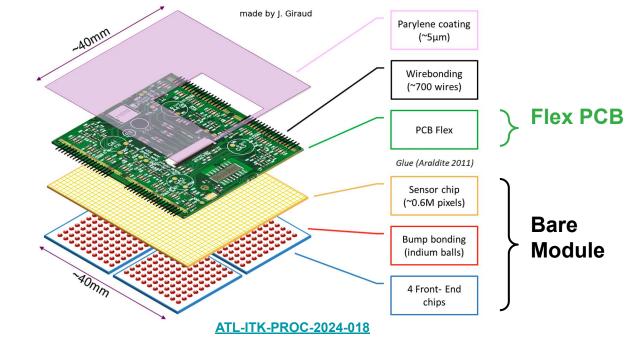

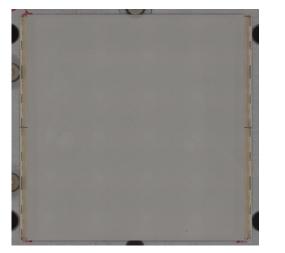

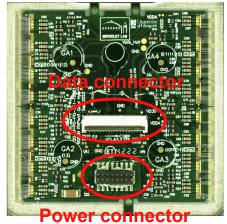

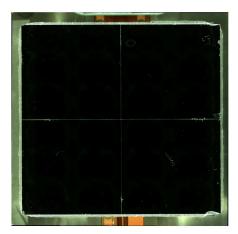

#### Quadruplet module for Layer 1

Argonne

will assemble ~1100 (70%) quadruplet modules! + test <sup>1</sup>/<sub>3</sub> of assembled modules

#### Major challenges:

- High production rates

- o fast assembly & testing

→ high level of automation and parallelization are required

- Over a temperature range of ~80  $^\circ\!\!\mathrm{C}$

- No glue delamination

- No disconnected bumps

Kim Doyeong 김도영, Argonne National Laboratory

## AMAF Avengers

Jessica Metcalfe

Tim Cundiff

Manoj Jadhav

Tanvi Wamorkar

Kim Doyeong

Daniel Aceves Jon Dale Nichols

#### Matias Mantiñan

Visual Inspection

Metrology

Wire

Gluing

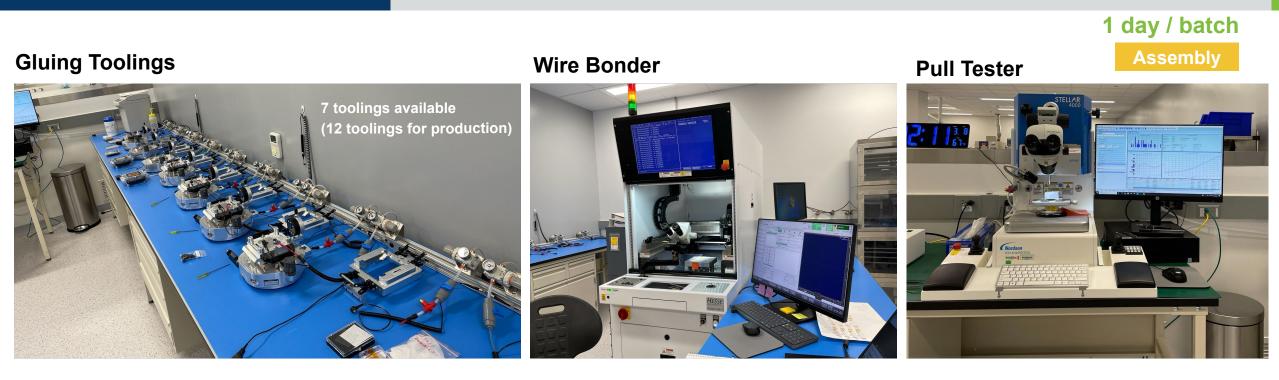

#### AMAF is ISO 7 clean room

AMAF\_user\_attire\_

Hair net Mask (while handing silicon)

Gloves (while handing silicon)

Lab coat

ESD safe clean-room shorese OR booties

Safety glasses

Kim Doyeong 김도영, Argonne National I

Argonne 合 16

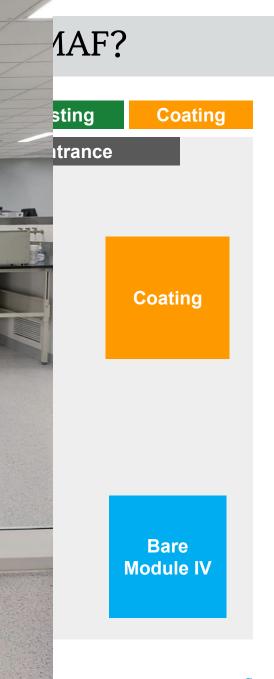

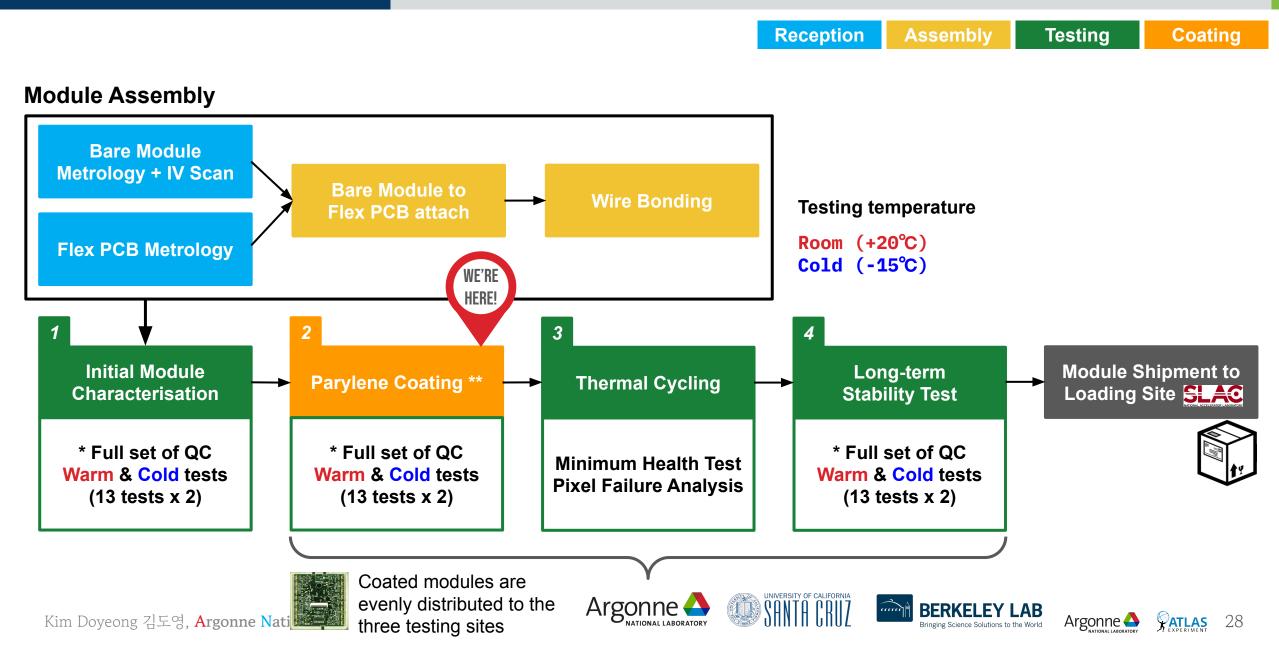

# What's going on at AMAF?

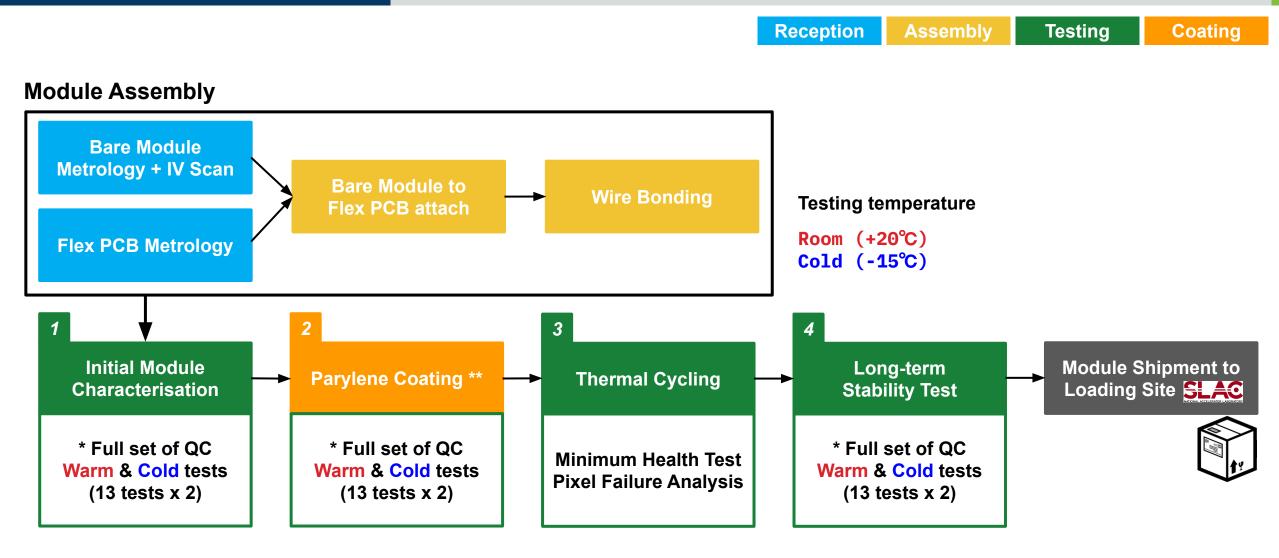

#### Workflow at Argonne

#### Bare Module

= sensor + 4 front-end chips bump bonded

#### **Flex PCB**

Bare module and Flex PDB are provided by industry

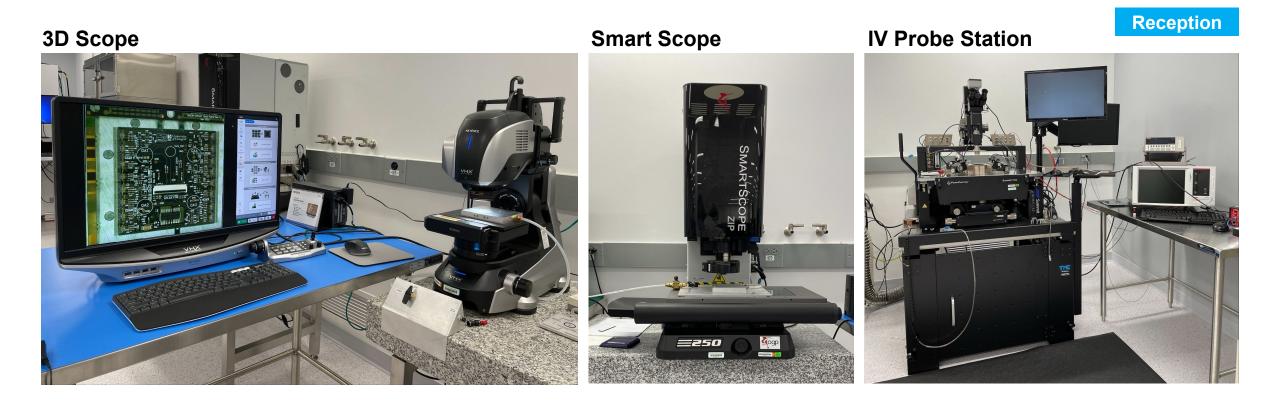

- Visual inspection and metrology are performed both before and after the module assembly

- The processes of measurement with Smart Scope, data visualization, and uploading to the PDB are fully automated, allowing for quick verification of whether the module metrology results are within the specified range

Assembly

#### **Bare Module**

= sensor + 4 front-end chips bump bonded

╋

#### Flex PCB

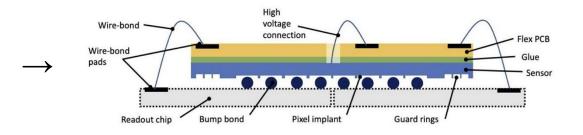

#### **Assembled Module**

#### flex PCB is

- 1) glued to the backside of the sensor tile

- 2) wirebonded to the front-end chips

#### Inventory

- Gluing requires 1) large glue coverage (>80%) 2) uniform glue distribution (±15μm) 3) alignment (<±100μm)

- 8h curing time (over night)

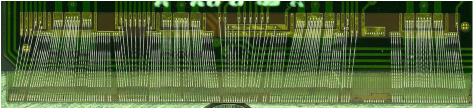

- Wire bondings

- ~170 wire bondings / chip (high density, various lengths and angles)

- 0.5h wire bonding & pull testing (in the morning)

- other preparation (handling, PDB uploading)

Essential to the success of wire bonding

Wire bondings for one front-end chip

#### Same day testing

X 4

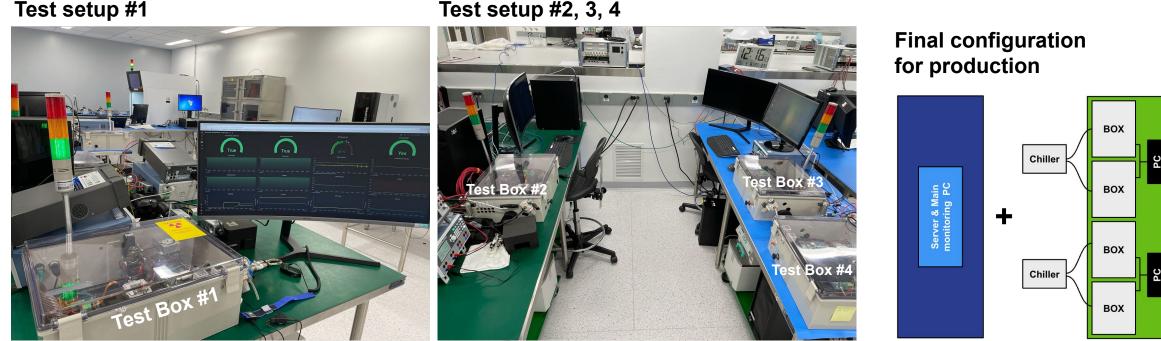

Test setup #1

- Four test boxes are available (aim to have 16 test boxes for production)

- After all the assembly process, the module is tested on the same day (basic electrical tests & source scan) •

- Aim to performed all tests with one button (We are almost there!) Ο

- Six team members are trained for testing Ο

Kim Doyeong 김도영, Argonne National Laboratory

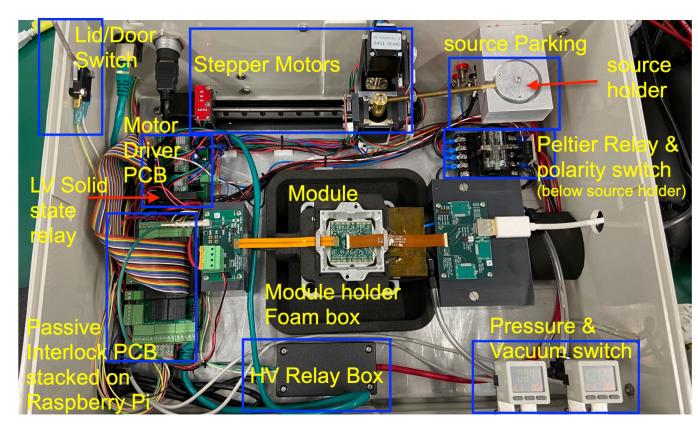

# ANL's test setup

## List of testings

- ✓ Calibration scans

- ✓ Pixel thresholds tuning

#### 5h for warm tests 6h for cold tests per module

Testing

- for initial characterization

- ✓ Pixel failure analysis

- Disconnected bump scans

- Threshold scan with zero bias

- Source scan

- Others

- ✓ Front-end chip testings

- ✓ Assembled module IV-scan

- All tests (at warm and cold temperatures and thermal cycle) can be done in this box without moving the modules around

- All instruments can be controlled remotely

- All tests are automatically logged, and results are automatically uploaded to the local database

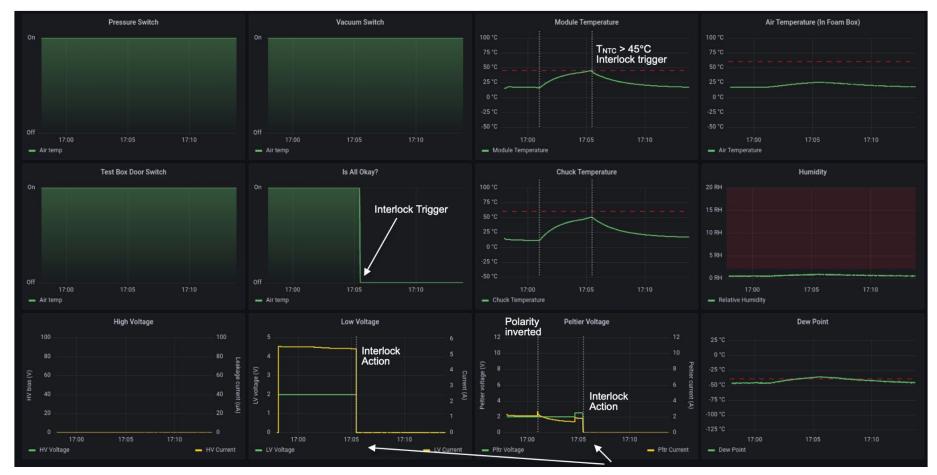

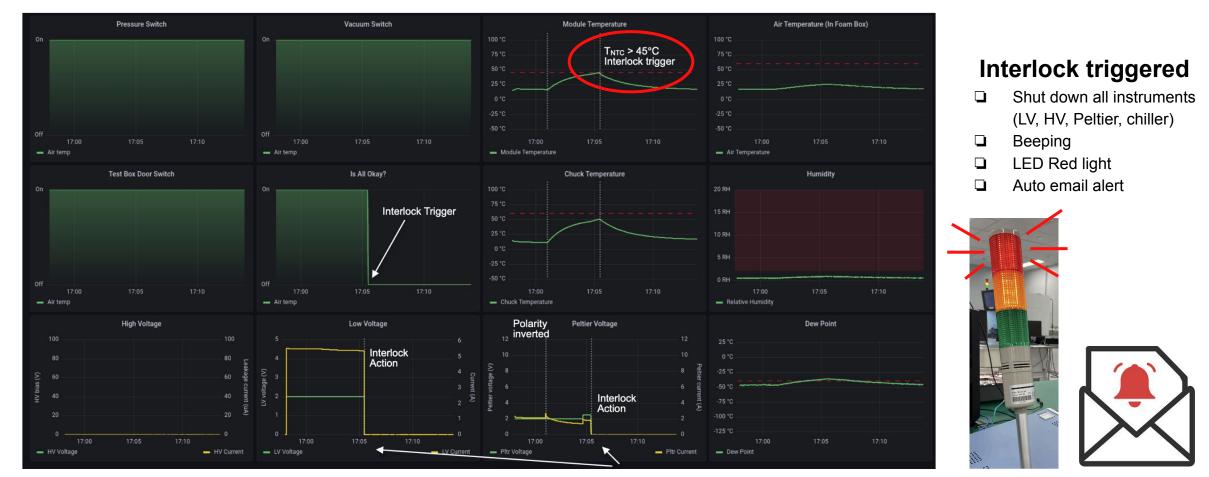

# Module Test Setup Box - Interlocks

- Raspberry Pi sends module&air temperature, humidity, dew point, vacuum, pressure, a box lid switch to DAQ

- The HV-LV voltages/currents and Peltier voltages/currents are recorded directly using SCPI commands

- The values are fed to InfluxDB with Grafana display (monitoring every 1s, visualization sync every 5s)

Kim Doyeong 김도영, Argonne National Laboratory

LV and Peltier power turned off

# Module Test Setup Box - Interlocks

Argonne 🍊

26

- Raspberry Pi sends module&air temperature, humidity, dew point, vacuum, pressure, a box lid switch to DAQ

- The HV-LV voltages/currents and Peltier voltages/currents are recorded directly using SCPI commands

- The values are fed to InfluxDB with Grafana display (monitoring every 1s, visualization sync every 5s)

Kim Doyeong 김도영, Argonne National Laboratory

LV and Peltier power turned off

#### Inventory

Parylene coater

#### Masking/demasking station

Coating

#### Real module after demasking

- Specialized plastic coating material to protect sensitive electrical components

- o Spark protection

- $\circ$  Scratch protection

- $\circ$  Wirebond protection

- Bump bond strengthening

- Specific areas (power connector, data cable connector) should remain w/o parylene

## Full QC Workflow

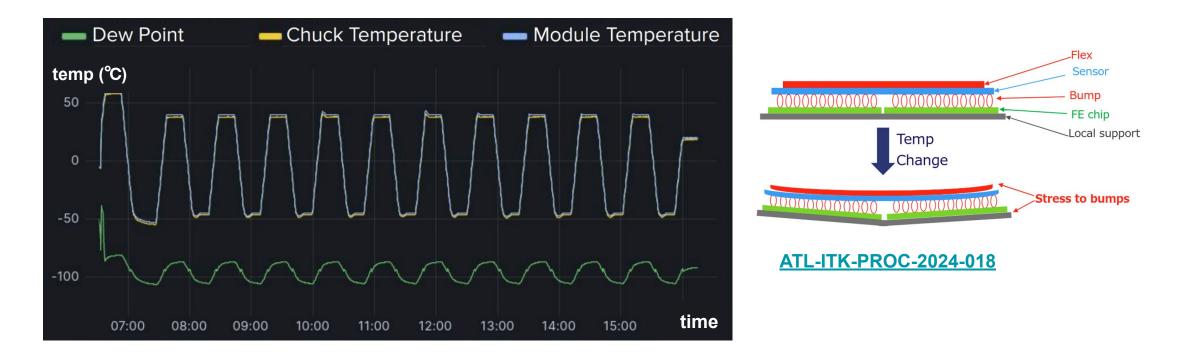

## Thermal cycle

- The quality control of the modules also involves characterising the module again after applying some thermal stress (1 extreme cycle [-55, 60]℃ + 10 cycles [-45, 40]℃)

- During the thermal cycles, the bump bondings connecting the sensor tile to the front-end chips are stressed and may disconnect → **Pixel failure analysis**

## Summary and outlook

- ANL is fully ready to deliver massive ATLAS ITk pixel module production for HL-HLC upgrade

- Most of the steps from assembly to testing are automated

- Most of the team members are trained for testing and assembly process

- The excellent track parameter resolution and the forward tracking extension are essential for reaching our milestones in the HL-LHC physics program

ex) VBF, VBS, Higgs Self-Coupling, Long-lived particle, and many more!