# Interplay with DRD7

Sorin Martoiu, Marco Bregant

1<sup>st</sup> DRD1 Collaboration Meeting Working Group 5: Electronics for gaseous detectors 31/01/2024

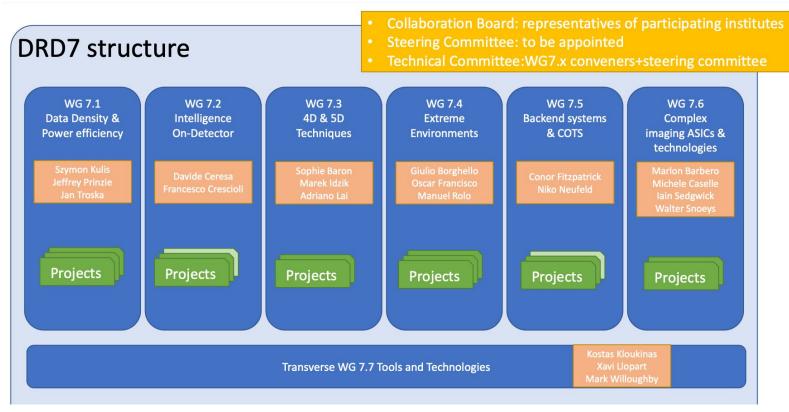

# About DRD7: "Electronics"

# DRD7 current proposed projects: a rich portfolio!

## 7.1.a Silicon Photonics Transceiver Development

· Medium-speed variant (4I x 25Gbps), and low-speed variant for

#### cryogenic applications

- Design of PIC, driver, TIA - Environmental characterization

- Packaging

- Fiber coupling, integration and testing

# 7.1.b Powering Next Generation Detector Systems

- High efficiency, low material budget

- High Voltage CMOS and GaN

- 28nm CMOS DCDC resonant converter IP - High efficiency shunt LDO regulator

- Parallel and Serial Powering

- System-level characterization - Radiation hardness and reliability

# 7.1.c Wireless Data and Power Transmission

- Multi-hop free space optical data transmission

- System-level analysis, demonstrators, custom design and full chain evaluation

- Exploration of wireless power transmission

# 7.4.a Modeling and development of cryogenic CMOS

# PDKs

- TSMC 65nm or 28nm

- Parameter extraction down to 4K

- Development of mixed-signal cold-IPs - Characterization and documentation of developed IP blocks

- Demonstrator crvo-chip

# 7.4.b Radiation resistance of advanced CMOS nodes

Rolling survey of technologies

- Focusing on specific nodes (i.e.7nm finfets or 3nm LGAA), or specific effects (low dose rate, NIEL scaling, noise, ...) - New material systems (GaN, SiGe, ...)

- Facilities and qualification protocols for ultra-high doses

# 7.4.c Cooling and cooling plates

- · Ceramics cooling plates

- Fabrication and validation of high-pressure resistance, leak tightness, and performance

- Microchannel cooling

- Fabrication of silicon interposers with

# 7.2.a eFPGA, Programmable Logic Array IP

#### (TBC)

- Study and comparison of open frameworks

- Radiation hardening and characterization

- Development of software and infrastructure for synthesis and mapping of user-code

- 7.2.b Radiation-tolerant RISC-V processor

# and SoC platform

- Enabling reconfigurable, retargetable ASICs

- Abstract design methodology

- Reusable, standardized IP blocks

- Control processor (RISCV) and framework - Programmable, flexible logic blocks

# 7.2.c Virtual electronic system prototyping

- High-level description of system, front-end to back-end

- Specification and performance modeling

- Reference for verification - Virtual prototyping

# 7.5.a COTS architectures, tools and IPs

Benchmark common TDAQ algorithms/workflows

- Define figures of merit

- Develop optimized reference implementations

- Maintain knowledge and community-led repository

## 7.5.b No backend, direct 100GbE rad-tol

# solutions from FE to DAQ

- Feeding directly COTS switches

- NICs or DAQ processors

- Feeding intermediate COTS-based aggregators - Low latency bridge to COTS switch

# 7.5.c Generic backend board (TBC)

· Critically review specificities of DAQ systems in HEP

- Slow custom links from frontend, interfaces to custom timing system, additional monitoring and configuration data streams, inline processing, etc.

Compare, discuss and benchmark performance of parallel

#### developments

- Explore possibility of establishing a common X-experiments base in hardware, firmware and

# 7.3.a High performance TDC and ADC

## blocks at ultra-low power

- Medium/high resolution, multi-channel ADC @40MS/s,

- High precision, multi-channel TDC (10ps)

- Experts' platform for sharing, comparing and benchmarking ideas, designs and ASICs

# 7.3.b Time measurement and distribution

- · Characterization, simulation and calibration of timing sources

- Develop and compare procedures

- Study and implement standard/generic solutions

- Timing distribution techniques and systems

- Explore limits of COTS components

- Investigate and compare alternatives - Develop protocols for precise & deterministic clock distribution

# 7.6.a Common access to selected CMOS

# imaging technologies and IP blocks

Tower-180nm, LFoundry-110nm, TPSCo-65nm

- Provide efficient and affordable access to technologies

- Develop and distribute PDKs and IPs - Manage legal and commercial frameworks

- Share test results

# 7.6.b Common access to 3D and advanced

# integration

- Access to research or commercial facilities mastering

- chiplets, 2.5/3D and Si-photonics integration

- TSV. RDL, interposers, C2C, C2W and W2W bonding

- Development and prototyping of demo

# 7.7 Tools and Technologies

# DRD7 "philosophy": (from "Organisation of the DRD7 collaboration" V6, 09/5/23:)

- DRD7 is an R&D collaboration, and *will not provide a design or fabrication service for ASICs or other components*; this is the role of engineering teams at institutes and laboratories participating in the various DRD projects.

- Where common developments across DRDs are agreed, either of IP, or of complete devices or subsystems, DRD7 is available to set up a review and coordination body.

- Funding for specific electronic developments and prototypes in DRDs should be allocated to the relevant collaborations, with prioritisation decisions made by the collaborations as part of their funding request and review. In case of complex electronics developments (and in particular of ASICs), a review coordinated by DRD7 will be instrumental in lowering the development risk and limiting duplication of effort.

- Funding for DRD7 R&D and coordination activities will be separately requested, including the costs of common tools, the costs of specialised personnel (for instance, verification experts), specific R&D developments at both device and system level, and the technical facilities necessary for R&D.

- **Proposals for R&D projects involving electronics and data-processing** can be included in either detector-related DRDs or in DRD7, taking into account the following guidelines:

- Projects in DRD7 will target common generic developments, or exploration of cutting-edge technologies requiring negotiated access to frameworks and complex design flows. They may involve high costs, expert coordination or unique expertise, and can possibly only be effectively delivered as a common community effort. They will follow design practices enabling later volume production in industry and/or using COTS components.

- Projects in individual DRDs will target developments driven by DRD-specific requirements. They will typically be smaller-scale

prototypes exploring or benchmarking novel concepts or technologies and delivering demonstrators. They will focus on diversity and

originality, but will not necessarily be suitable for large-scale production.

□ DRD≠7 should try to identify if *common generic development* concerning ASIC and/or DAQ can be setup across collaborations

# DRD1 needs for electronics. (work Packages extract)

| Task                                                                    | Performance goal                                                                                                                                                                                                               | Comments                                                                                                                                                                                       | Possible deliverables next 3-5 y                                                                                                                                            |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Muon systems)<br>New front end electronics                             | <ul> <li>1 fC threshold</li> <li>Geometrical avalanche quenching</li> <li>High sensitivity electronics and new detector structures to achieve stable<br/>and efficient operation (rate, occupancy) up to O(MHz/cm2)</li> </ul> | <ul> <li>Study of the integration of the FE electronics in the detector Faraday cage</li> <li>Study of the integration of electronics and readout PCB</li> </ul>                               | <ul> <li>Conceptual electronics design based on gas detector<br/>simulation and experimental measurements</li> <li>Development and test of a front-end prototype</li> </ul> |

| (Large-volume drift chambers)<br>Front-end ASIC for cluster<br>counting | - High bandwidth<br>- High gain<br>- Low power<br>- Low mass                                                                                                                                                                   | achieve efficient cluster counting and cluster timing performances                                                                                                                             | full design, construction and test of a first prototype<br>of the front-end ASIC for cluster counting                                                                       |

| <b>(Straw chamber)</b><br>Electronic readout, ASIC                      | <ul> <li>Time readout with sub-ns precision</li> <li>Leading edge and trailing edge time readout</li> </ul>                                                                                                                    | - Dedicated R&D on ASIC                                                                                                                                                                        | - ASIC<br>- Readout system                                                                                                                                                  |

| (Time Projection Chambers)<br>Low-power FEE                             | <ul> <li>&lt; 5 mW/ch for &gt;1e6 pad TPC</li> <li>- ASIC development in 65 nm CMOS</li> </ul>                                                                                                                                 | •continuous vs. pulsed                                                                                                                                                                         | - Present stable operation of a multi-channel TPC prototype with a low-power ASIC                                                                                           |

| (Gaseous photon detectors)<br>FEE                                       | - High input C<br>- Low noise<br>- large dynamic range                                                                                                                                                                         | •                                                                                                                                                                                              | - present an ASIC concept/prototype                                                                                                                                         |

| (Gaseous timing detectors)<br>Low-noise FEE                             | - High input C<br>- large dynamic range<br>- Fast rise time<br>- sensitivity to small charge<br>- Low noise                                                                                                                    | •                                                                                                                                                                                              | Define an ASIC                                                                                                                                                              |

| <b>(Muon systems)</b><br>Scalable multichannel<br>readout system        | Front-end link concentrator to a powerful FPGA with possibilities of triggering an O(20GBit/s) to DAQ                                                                                                                          | <ul> <li>FPGA based architecture</li> <li>FPGA with embedded processing for triggering and ML</li> <li>Basic firmware and software can be bootstrapped from existing readout system</li> </ul> | First prototype by end of 2024 for commissioning at test beams                                                                                                              |

| (Large-volume drift<br>chambers)<br>Scalable multichannel DAQ<br>board  | <ul> <li>High sampling rate</li> <li>Dead-time-less</li> <li>DSP and filtering</li> <li>Event time stamping</li> <li>Track triggering</li> </ul>                                                                               | <ul> <li>FPGA based architecture</li> <li>ML algorithms-based firmware</li> </ul>                                                                                                              | working prototype of a scalable multichannel<br>DAQ board                                                                                                                   |

| <b>(Straw chamber)</b><br>Electronic readout, ASIC                      | <ul> <li>Time readout with sub-ns precision</li> <li>Leading edge and trailing edge time readout</li> </ul>                                                                                                                    | - Dedicated R&D on ASIC                                                                                                                                                                        | - ASIC<br>- Readout system                                                                                                                                                  |

# DRD7 rich portfolio, overlaps with DRD1 desiderata?

## 7.1.a Silicon Photonics Transceiver Development

· Medium-speed variant (4I x 25Gbps), and low-speed variant for

#### cryogenic applications

- Design of PIC, driver, TIA

Environmental characterization

- Environmenta

Packaging

- Fiber coupling, integration and testing

# 7.1.b Powering Next Generation Detector Systems

- High efficiency, low material budget

- High Voltage CMOS and GaN

- 28nm CMOS DCDC resonant converter IP

High efficiency shunt LDO regulator

- High efficiency shunt LDO regulato

- Parallel and Serial Powering

- System-level characterization

Radiation hardness and reliability

## 7.1.c Wireless Data and Power Transmission

- Multi-hop free space optical data transmission

- System-level analysis, demonstrators, custom design and full chain evaluation

- Exploration of wireless power transmission

# 7.4.a Modeling and development of cryogenic CMOS

# PDKs

- TSMC 65nm or 28nm

- Parameter extraction down to 4K

- Development of mixed-signal cold-IPs

Characterization and documentation of developed IP blocks

- Gnaracterization and docun

Demonstrator cryo-chip

# 7.4.b Radiation resistance of advanced CMOS nodes

Rolling survey of technologies

Focusing on specific nodes (i.e.7nm finfets or 3nm LGAA), or specific effects (low dose rate, NIEL scaling, noise, ...)

New material systems (GaN, SiGe, ...)

Facilities and qualification protocols for ultra-high doses

- Facilities and qualification protocols for ultra-high doses

# 7.4.c Cooling and cooling plates

- Ceramics cooling plates

- Fabrication and validation of high-pressure resistance, leak tightness, and performance

- Microchannel cooling

- Fabrication of silicon interposers with i

# 7.2.a eFPGA, Programmable Logic Array IP

#### (TBC)

- Study and comparison of open frameworks

- Radiation hardening and characterization

- Development of software and infrastructure for synthesis and mapping of user-code

- 7.2.b Radiation-tolerant RISC-V processor

# and SoC platform

- Enabling reconfigurable, retargetable ASICs

- Abstract design methodology

- Reusable, standardized IP blocks

- Control processor (RISCV) and framework

Programmable, flexible logic blocks

# 7.2.c Virtual electronic system prototyping

- High-level description of system, front-end to back-end

- Specification and performance modeling

- Reference for verification

Virtual prototyping

# 7.5.a COTS architectures, tools and IPs

Benchmark common TDAQ algorithms/workflows

- Define figures of merit

- Develop optimized reference implementations

- Maintain knowledge and community-led repository

### 7.5.b No backend, direct 100GbE rad-tol

# solutions from FE to DAQ

- Feeding directly COTS switches

- NICs or DAQ processors

- Feeding intermediate COTS-based aggregators

Low latency bridge to COTS switch

# 7.5.c Generic backend board (TBC)

Critically review specificities of DAQ systems in HEP

Slow custom links from frontend, interfaces to custom timing system, additional monitoring and configuration data streams, inline processing. etc.

· Compare, discuss and benchmark performance of parallel

#### developments

- Explore possibility of establishing a common X-experiments base in hardware, firmware and

# 7.3.a High performance TDC and ADC

### blocks at ultra-low power

- Medium/high resolution, multi-channel ADC @40MS/s,

- High precision, multi-channel TDC (10ps)

- Experts' platform for sharing, comparing and benchmarking ideas, designs and ASICs

# 7.3.b Time measurement and distribution

- Characterization, simulation and calibration of timing sources

- Develop and compare procedures

- Study and implement standard/generic solutions

- Timing distribution techniques and systems

- Explore limits of COTS components

- Investigate and compare alternatives

- Develop protocols for precise & deterministic clock distribution

# 7.6.a Common access to selected CMOS

# imaging technologies and IP blocks

Tower-180nm, LFoundry-110nm, TPSCo-65nm

- Provide efficient and affordable access to technologies

- Develop and distribute PDKs and IPs

Manage legal and commercial frameworks

- Manage legal and commerce

Share test results

# 7.6.b Common access to 3D and advanced

# integration

- Access to research or commercial facilities mastering

- chiplets, 2.5/3D and Si-photonics integration

- TSV, RDL, interposers, C2C, C2W and W2W bonding

- Development and prototyping of demo

# 7.7 Tools and Technologies

# DRD7 rich portfolio, overlaps with DRD1 desiderata?

- Study and comparison of open frameworks

- Radiation hardening and characterization

(TBC)

# 7.1.a Silicon Photonics Transceiver Development

· Medium-speed variant (4I x 25Gbps), and low-speed variant for

#### cryogenic applications

- Design of PIC, driver, TIA - Environmental characterization

- Packaging

- Fiber coupling, integ

# 7.1.b Pov 7.1 a Silicon Photonics Transceiver

retargetable ASICs

7.2.a eFPGA, Programmable Logic Arra

Development of software and infrastructure for synthesis and mapping of us

7.2.b Radiation-tolerant RISC-V process

nework

elina

# flong term" answers to some of our

blocks at ultra-low power

7.3.a High performance TDC and ADC

ID

# requests are worked out here...

- Develop protocols for precise & deterministic clock distribution

Timing distribution techniques and systems

Study and implement standard/generic solutions

- Explore limits of COTS components

- Investigate and compare alternatives

#### High efficier - High Voltage CMOS

- 28nm CMOS DCDC - High efficiency shun

- 7.1.b Powering Next Generation Detector Systems

#### Parallel and - System-level charac

- Radiation hardness 7.1.c Wire 7.4 b Radiation resistance of advanced CMOS nodes

#### Multi-hop fre - System-level analys Exploration

7.5.a COTS architectures, tools and IPs

# 7.4.a Mo

- PDKs

- several middle/long term "basic" R&Ds TSMC 65n that should be followed to keep us updated - Parameter extracti - Development of m

#### - Characterization a - Demonstrator crvc 7.4.b Ra

### Rolling survey of technologies

- Focusing on specific nodes (i.e.7nm finfets or 3nm LGAA), or specific effects (low dose rate, NIEL scaling, noise, . - New material systems (GaN, SiGe, ...) - Facilities and qualification protocols for ultra-high doses

# 7.4.c Cooling and cooling plates

- · Ceramics cooling plates

- Fabrication and validation of high-pressure resistance, leak tightness, and performance

- Microchannel cooling

- Fabrication of silicon interposers with

ectures, tools and IPs AQ algorithms/workflows

nic system prototyping

system, front-end to back-end

itions epository

```

direct 100GbE rad-tol

to DAQ

witches

```

- Feeding intermediate COTS-based aggregators - Low latency bridge to COTS switch

- 7.5.c Generic backend board (TBC)

- · Critically r

- Slow custom link 7.7 Tools and Technologies configuration data processing, etc.

· Compare, here the forums and the exchange of knowledge occurs developme

- Explore possibility or establishing a common x-experiments base in hardware, tirmware and

# 7.6.a Common access to selected CMOS imaging technologies and IP blocks

- Tower-180nm, LFoundry-110nm, TPSCo-65nm

- Provide efficient and affordable access to technologies

- Develop and distribute PDKs and IPs - Manage legal and commercial frameworks

- Share test results

7.6.b Common access to 3D and advanced

# integration

· Access to research or commercial facilities mastering chiplets, 2.5/3D and Si-photonics integration

- TSV, RDL, interposers, C2C, C2W and W2W bonding

- · Development and prototyping of demo

# How DRD1 does see interplay with DRD7

# Understood the more long term and generic R&D in DRD7:

- Gas targeted ASIC in DRD1, we expect DRD7 support us in accessing foundries and design kits (-> WG 7.7 OK!). Repository for IP exchange is also very welcome.

- We acknowledge and share the concern about NDAs and technology access limitations/boundaries. May be, DRD7 can help/coordinate having pre-approved<sup>(\*)</sup> framework/models of NDAs that simplifies the cooperation of groups from different institution and countries working on the same task/project, as well as basic assistance and guidelines for "export licences" when they are needed

- There may be technological aspects specific to DRD1 in the course of various developments that may need a "heavier" endorsement than what the teams in DRD1 alone can provide.

- DRD1 (RD51) has an history of developing (quite) general purpose scalable acquisition system (SRS), and plans to continue doing. How does that fit/interact with DRD7? Not now... may be in the future?

- Electronics development is ultimately carried out by individual researchers or institutes as sub-task of individual DRDs (and in most cases funding follows the same pattern). With increasing development cost comes the need for the community to stay together and help each other also across DRDs

- An example is the joint collaboration between developers in DRD6 and DRD1 on electronics for calorimetry

- Would DRD7 being the place where electronics developers of different DRDs will "meet", "exchange experiences", and "know each other", and, eventually, collaborations are triggered? i.e. should DRD7 organize meetings for this purpose, without absorbing any deliverables from the other DRDs? WG 7.7?

(\*) the idea here is to have a NDA document, already discussed and approved by (CERN?) lawyers and involved companies (e.g. foundries) that, as long as the clauses inside are respected, can be used (signed) to support effective cooperation (full project sharing) between people of different institutions and countries, avoiding case by case long negotiations.

Comments? Suggestions? Requests?

# Electronics "wish-list" in DRD1

- High performance charge-sensitive front-end circuit specific for medium and large volume gaseous detectors (MPGD, TPC, drift chambers, straw tubes, RPC, ...)

- High input capacitance ( 2-2000 pF )

- Low noise/high sensitivity (eg. ~100e@2pF; 50mV/fC)

- Low power ( ~ few mW/ch)

- High dynamic range (12-14bits, 1:50000, several strategies)

- Precise timing (10-100ps linked to lon tail processing and extraction of electron charge peaks)

- High event-rate (1MHz/cm2 -> several MHz/channel)

- Pixelated readouts (charge- or photon-sensitive detectors with high timing resolution)

- Optimization of pixel size (>200 μm)

- Provide a large-area pixel-based readout

- Architectural innovations R&D

- Versatile front-end circuitry (variable parametric front-end and shaping circuit, variable resource distribution,...)

- Cluster-counting (continuous readout, 1GHz analog bandwidth front-end, 2GSps high-sampling rate, on-line processing with direct mathematical algorithms or Machine Learning)

- o Deadtime-less readout, self-trigger vs continuous sampling with digital data compression

- High-rate data-acquisition (> 1MHz/ch, up to Tb/s total DAQ bandwidth scalable systems mapped on switched networks, generic DAQ for different Front-Ends )

- Technological developments

- High-voltage tolerance/spark protection

- Detector biasing via ASIC (eg TSV for HV)

- Combined detector & electronics assembly technology, cooling & services integration (integration of the FE electronics in the detector Faraday cage)

- Platform for sharing and collaborative development of Processing IPs and building blocks

- Sharing and co-design of front-end building blocks.

- Signal/Event Processing on- or off-chip (eg. peak finding, baseline restoration, feature extraction, etc.... reusable IP library for online use in FPGA/ASIC or offline in software)

- Proper mechanism for open access, end user agreement, protection of Intellectual Property and authorship recognition.