# 高輝度LHC-ATLAS実験に向けた初段ミューオントリガー回路に 実装されるタイミングアライメントモジュールの量産のための品質試験

牧田藍瑠 (ICEPP, The University of Tokyo)

ICEPP Symposium 18-21 Feb. 2024

## 0. 概要

LHC-ATLAS実験の初段ミューオントリガーシステムは、高速応答可能なガス検出器であるTGC(Thin Gap Chamber)の出力を用いたコインシデンスによるトリガーシステム である。そのフロントエンドは検出器からの出力信号を適切に遅延させて受信タイミングを揃えた後、各信号の立ち上がりをバンチ交差クロックに対応させる(バンチ識別) 役割を担う。バンチ識別を正しく行うためにはバンチ交差に同期したクロックを、O(100 ps)程度の精度で位相を揃えて全1500枚のフロントエンド回路に対して供給すること が必要である。これを実現するためにはフロントエンドボードが受信したクロックの位相の測定が必要になるが、高輝度 LHC-ATLAS実験に向けて、これを遠隔で全数に対し て行うことができる測定システムを実装した。 TAM(Timing Alignment Master)モジュールはクロック位相測定のための基準クロックを低スキューで配布する役割を持つ。 TAMのデザイン・機能として、同位相クロックを分配するほか、VME通信のマスターとして他のモジュールを制御する機能がある。TAMモジュールの量産に向けた品質試 験セットアップの構築を行った。本試験ではTAMの動作確認のため、「光通信によるTAMの制御」「VME通信によるTAMからの他のモジュールの制御」「クロックの再構成 と他モジュールへのクロックの分配」「TAMコンフィギュレーションのための不揮発メモリへの書き込み」「クロック送受信インターフェースのクロックスキューの測定」と

いう項目を検証した。これらの機能試験を最終試作回路に対して行い、全ての機能が正常動作することを確認した。加えて、本試験を通じて試験自動化のためのソフトウェア

の実装などによって、効率的な品質試験セットアップを開発した。これにより、今後の量産機の機能試験を高速かつ正確に行うことが期待できる。

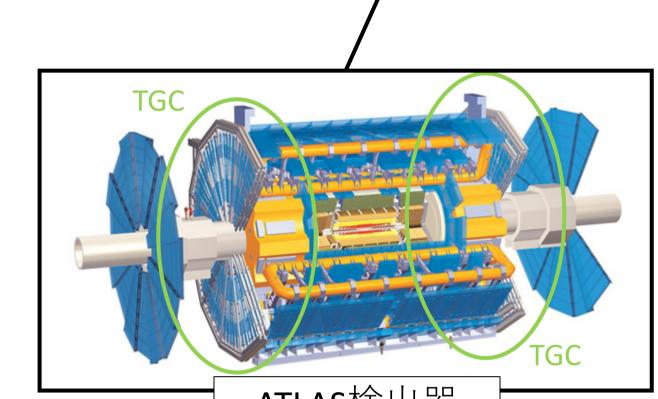

## LHC-ATLAS実験

#### LHC (Large Hadron Collider)

- 世界最高エネルギー( $\sqrt{s}$ =13.6 TeV)での陽子-陽子衝突

- 40 MHz (25 ns毎)での陽子バンチ交差

- 陽子交差の多くは興味のない物理事象 →事象の取捨選択トリガーが重要

## ATLAS (A Toroidal LHC ApparatuS) 検出器

- 多様な生成粒子を観測する汎用検出器

- BSM探索やHiggs精密測定等の目的

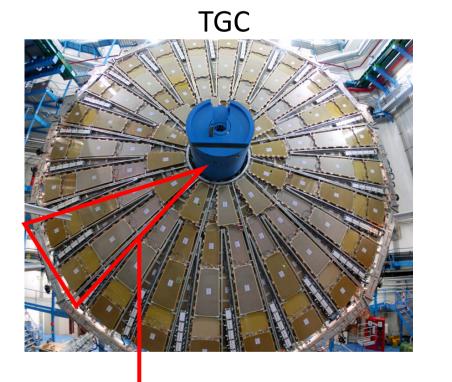

#### TGC (Thin Gap Chamber)

- ミューオン検出のためのMWPC

- ATLAS初段ミューオントリガーの エンドキャップ部を担当

- ヒットコインシデンスにより エレクトロニクス上で運動量を概算

ATLAS検出器

# 2. 高輝度LHC-ATLASにおけるTGCエレクトロニクス

#### 高輝度LHC

- アップグレードが施され、2029年から運転開始

- ルミノシティが約3倍に向上

- 陽子衝突レートの増加に対するTrigger DAQシステムの仕様変更 →TGCエレクトロニクスの刷新

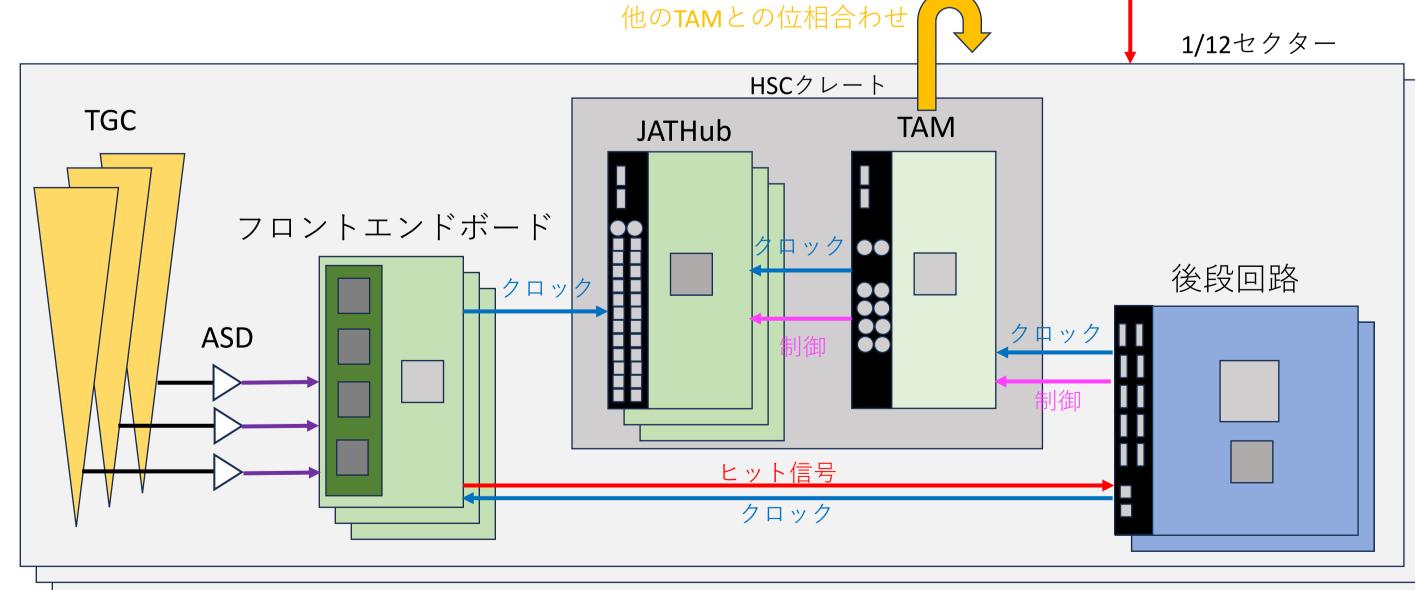

### 高輝度LHCにおけるTGCエレクトロニクス

- ヒット信号は

- 1. ASD(Amplifier-Shaper-Discriminator)でデジタル化

- 2. フロントエンド回路でLHCクロックと同期 (バンチ識別)

- 3. 後段回路でトリガー演算される+後段への読み出される

- フロントエンドボード1500台に同位相でクロックを分配する必要がある

## フロントエンド回路への同位相クロック分配

後段回路からフロントエンドボードへのクロック分配はファイバー長の違いから 同位相でない. そのため、そのクロック位相を揃える機構をJATHubとTAMが担う

- JATHub (JTAG Assistance Hub) TAMから同位相クロックを受信 それを基準にフロントエンドのクロック位相合わせ

- TAM (Timing Alignment Master) →本研究の試験対象 後段回路からクロックを受信 他のTAMとクロック位相合わせ その同位相クロックをJATHubに分配

## 3. TAMの機能と品質試験の概要

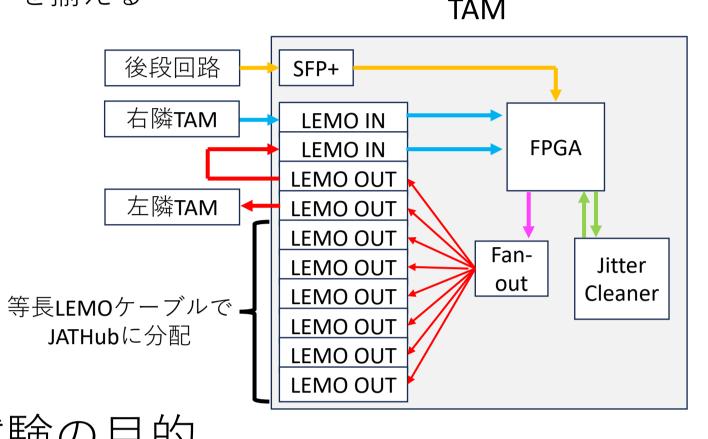

## TAMの機能・役割

- VMEマスターとしてJATHubのコントロール

- 低スキュー(O(100 ps))での同位相クロックの分配

- TAM内はFan-out素子と等長LEMOケーブルで位相を揃える

- TAM間は右隣のTAMのクロックと自身の出力クロックの位 相を測定し、位相を揃えるロジックをFPGAで実装して位相 を揃える

2024年度からの量産機30台のQAQC試験を踏まえて

- 最終試作回路の機能検証

- 試験手順の効率化

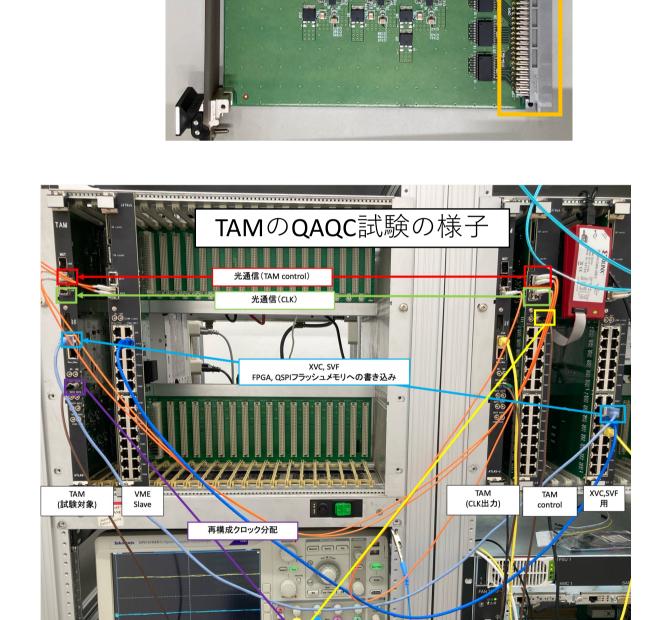

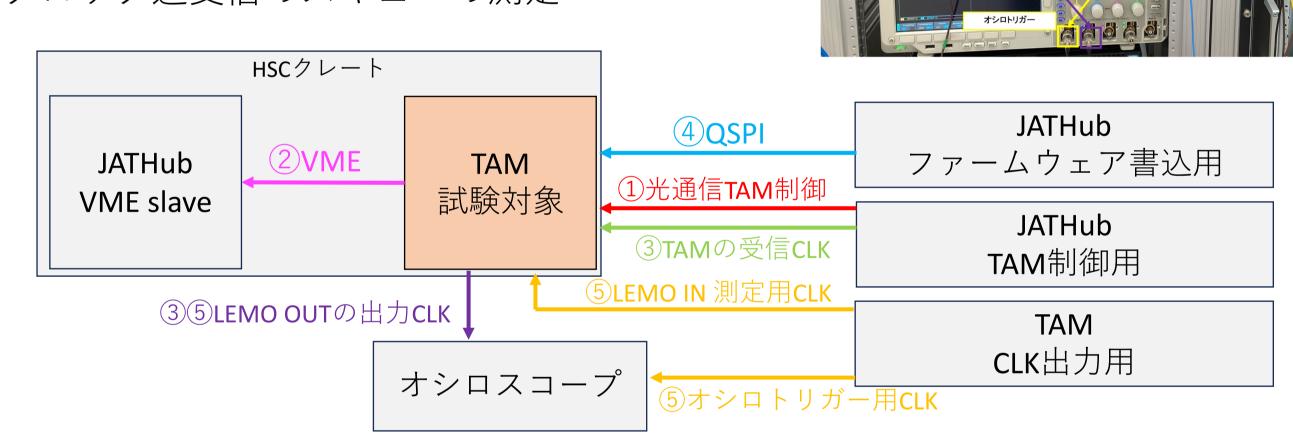

## 試験項目

- 光通信によるTAMのレジスタ読み書き

- ② VME通信でのスレーブのレジスタ読み書き

- 受信したクロックの再構成とその分配

- TAMのQSPIフラッシュメモリへの書き込み

- クロック送受信のスキューの測定

TAMのQAQC試験の概念図 後段回路の代わりにJATHubとTAMで機能を代用

## 4. 試験手順の効率化の工夫

自動化のためのソフトウェアの実装

- レジスタ読み書きを行い、正しい挙動か判定するアプリを実装

- QSPIフラッシュメモリの書き込みを行い、正しく書き込めたか判定するア プリを実装

試験項目毎に入力クロックを切り替える機能を実装

- 試験項目の③と⑤は入力クロックが異なる(③:SFP+, ⑤:LEMO IN)

- ③→⑤に移行する際にTAMのレジスタを書き換えるだけで試験を間断無く 続行可能

ケーブルの抜き差し,ファームウェア書き込みの回数を最小化

- 試験用ファームウェアを反映したJATHubブート用SDの作成

- 試験項目の実施順を調整

→所要試験時間は1台あたり10分程度

# 5. 試験結果と量産試験の展望

## 試験結果

- 最終試作回路の全ての機能が正常動作

- クロックスキューも想定内の値

- 試験手順も問題なく遂行可能なことを確認

## 量産試験の展望

- 現段階の最終試作回路で量産可能

- 2024年度からのQAQC試験の準備が完了

- 本研究で開発した試験手順により、TAM量産機全30台のQAQC試験 は5時間程度で完了する見積もり

#### TAM最終試作機のLEMO IN/OUT port のクロックスキュー

| LEMO OUT port | 0(基準) | 1      | 2    | 3      | 4      | 5      | 6      | 7      |

|---------------|-------|--------|------|--------|--------|--------|--------|--------|

| Skew          | 0 ps  | -60 ps | 0 ps | -40 ps | +40 ps | -40 ps | +20 ps | -40 ps |

| LEMO IN port | 0(基準) | 1       |  |  |

|--------------|-------|---------|--|--|

| Skew         | 0 ps  | -220 ps |  |  |

O(100 ps)程度であり問題なし