### Advances and synergy in monolithic sensor developments

ALPIDE prototype: 200 MeV protons at PSI

CERN, February 29th, 2024

walter.snoeys@cern.ch

- The workshop organizers

- Colleagues from CERN and other institutes, ALICE and ITS3 upgrade, Experimental Physics RD WP1.2, ATLAS Itk ...

Concentrated on technology and the evolution of our developments, had to made some selection, and then concentrated on the 65 nm, and tried to give also some personal observations.

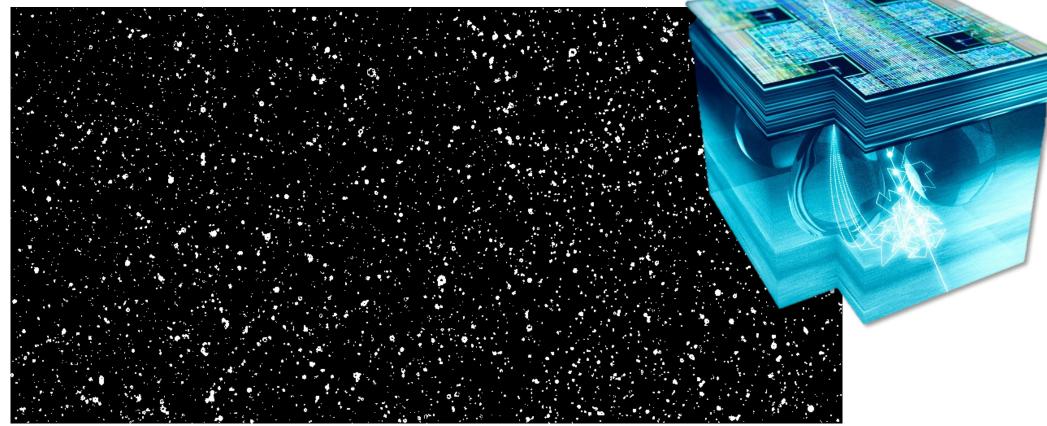

## CMOS Monolithic Active Pixel Sensors revolutionized the imaging world

#### reaching:

- Iess than 1 e<sup>-</sup> noise

- > 40 Mpixels

...

- Wafer scale integration

- Wafer stacking (now offered by foundries)

Silicon has become the standard in tracking applications both for sensor and readout

... and now CMOS MAPS make their way in High Energy Physics !

Hybrid still in majority in presently installed systems

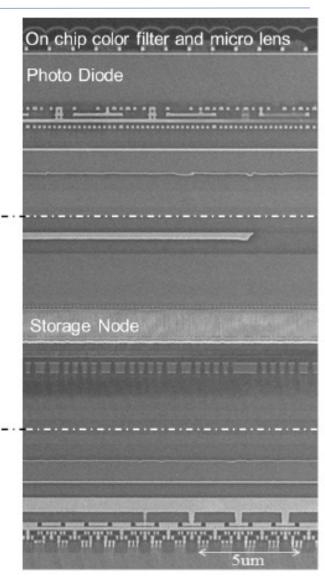

Top part (BI-CIS process technology)

Middle part (DRAM process technology)

Bottom part (Logic process technology)

Sony, ISSCC 2017

New technologies (TSV's, microbumps, wafer stacking...) make the distinction between hybrid and monolithic more vague.

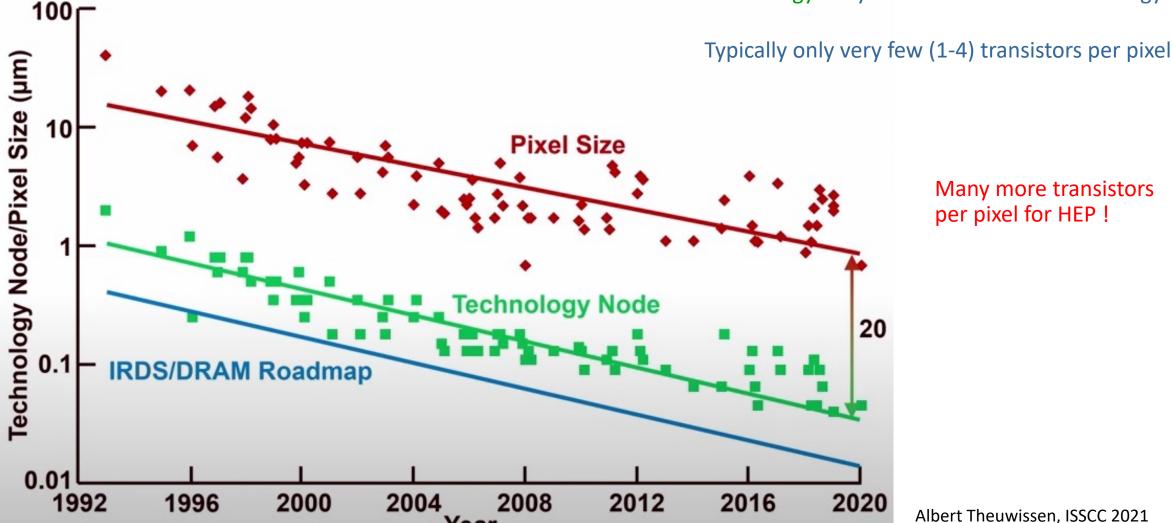

Evolution of pixel size and technology node for visible:

# **Pixel Size Evolution**

Pixel size: 20x above technology feature size

Technology: 10 years behind DRAM technology

Year

| <b>Requirements for High Energy Physics</b>                                     |                          | Dose   | Fluence                                                  |  |  |

|---------------------------------------------------------------------------------|--------------------------|--------|----------------------------------------------------------|--|--|

| Requirements for high Energy highes                                             |                          | (Mgy)  | (10 <sup>16</sup> 1MeVn <sub>eq</sub> /cm <sup>2</sup> ) |  |  |

| Radiation tolerance                                                             | ALICE ITS                | 0.01   | <b>10</b> <sup>-3</sup>                                  |  |  |

| <ul> <li>CMOS circuit typically more sensitive to ionizing radiation</li> </ul> | LHC                      | 1      | 0.10.3                                                   |  |  |

| <ul> <li>Sensor to non-ionizing radiation (displacement damage)</li> </ul>      | HL-LHC 3ab <sup>-1</sup> | 5      | 1.5                                                      |  |  |

|                                                                                 | FCC                      | 10-350 | 3-100                                                    |  |  |

Single particle hits instead of continuously collected signal in visible imaging

- Sparse images < or << 1% pixels hit per event

- Near 100% efficiency, full CMOS in-pixel needed, often circuit (much) more complex

#### Position resolution (~µm)

#### Low power consumption is the key for low mass

- Now tens of mW/cm<sup>2</sup> for silicon trackers and hundreds of mW/cm<sup>2</sup> for pixels

- Despite enhanced detector functionality for upgrades, material penalty limits power consumption increase

#### More bandwidth

Time resolution

Time stamping ~ 25 ns or even lower, ... much lower (10s of ps)

#### Larger and larger areas

- ALICE ITS2 10 m<sup>2</sup>, discussions on hundreds to even thousands square m<sup>2</sup>,

- Interest for versatile sensors programmable for different applications (P. Allport CERN EP seminar 2020)

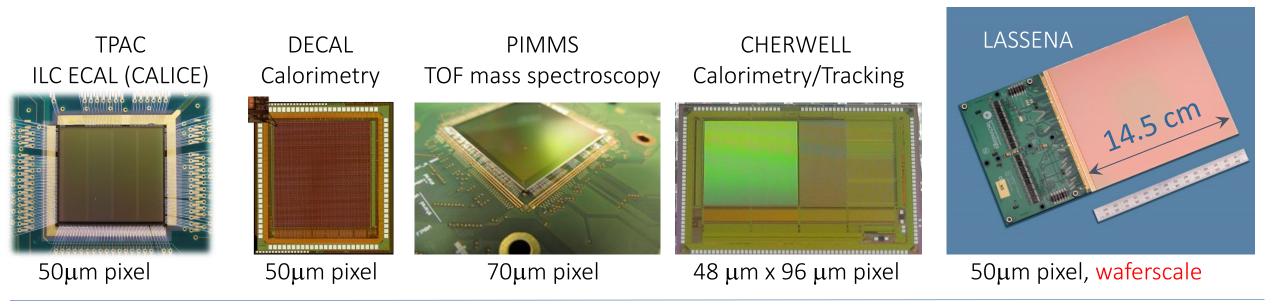

### Monolithic sensors in HEP move into mainstream CMOS technology

CCDs in SLD detector at SLAC, C. Damerell et al.

MIMOSA28 (ULTIMATE) in STAR ALPIDE in ALICE

- IPHC Strasbourg First MAPS system in HEP Twin well 0.35 μm CMOS

- Integration time 190 μs

- No reverse bias -> NIEL few 10<sup>12</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

- Rolling shutter readout

First MAPS in HEP with sparse readout similar to hybrid sensors Quadruple well 0.18 µm CMOS

- Integration time <10 µs</p>

- Reverse bias but no full depletion

-> NIEL ~10<sup>14</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

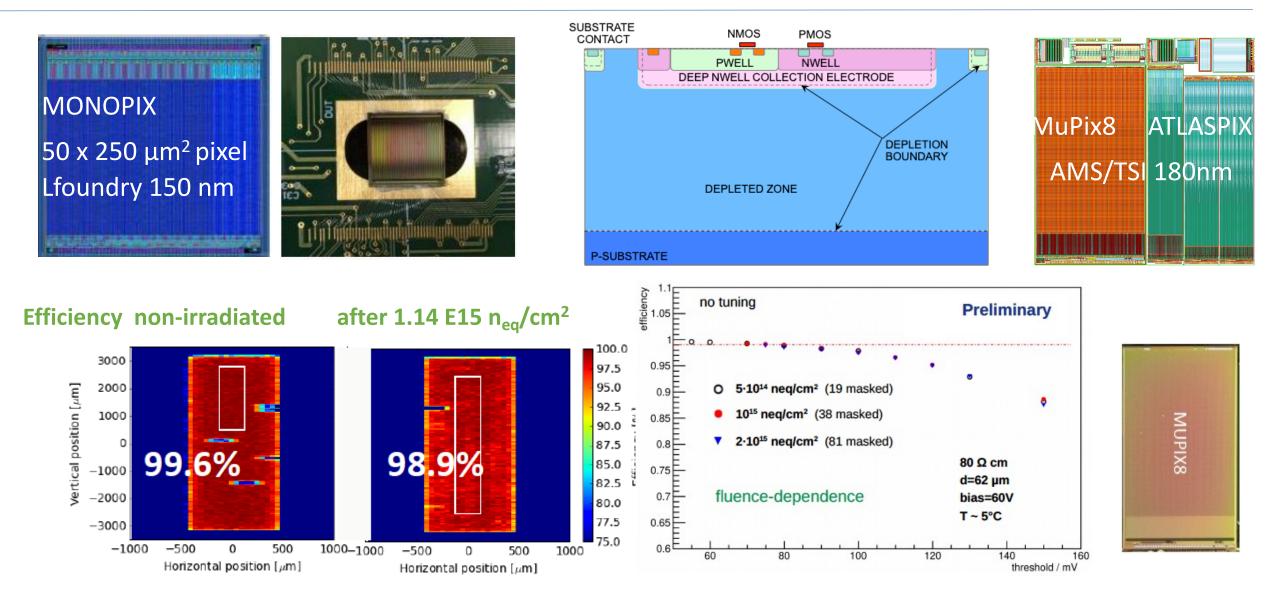

DEPLETED MAPS for more operating margin, better time resolution and radiation tolerance Large collection electrode LF Monopix, MuPix,... Extreme radiation tolerance and timing uniformity, but large capacitance Small collection electrode ARCADIA LF, TJ Malta, TJ Monopix, Fastpix, CLICTD, ...

- Sub-ns timing

- NIEL >10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> and beyond

Commercial deep submicron CMOS technology evolved "naturally" towards

- Very high tolerance to ionizing radiation, some caveats, cfr G. Borghello, F. Faccio, requires extensive irradiation campaigns

- Availability of substrates compatible with particle detection

- Imaging technology not absolutely required, but some flexibility/features very beneficial for sensor optimization, both for small and large collection electrode structures.

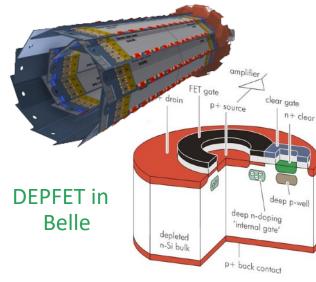

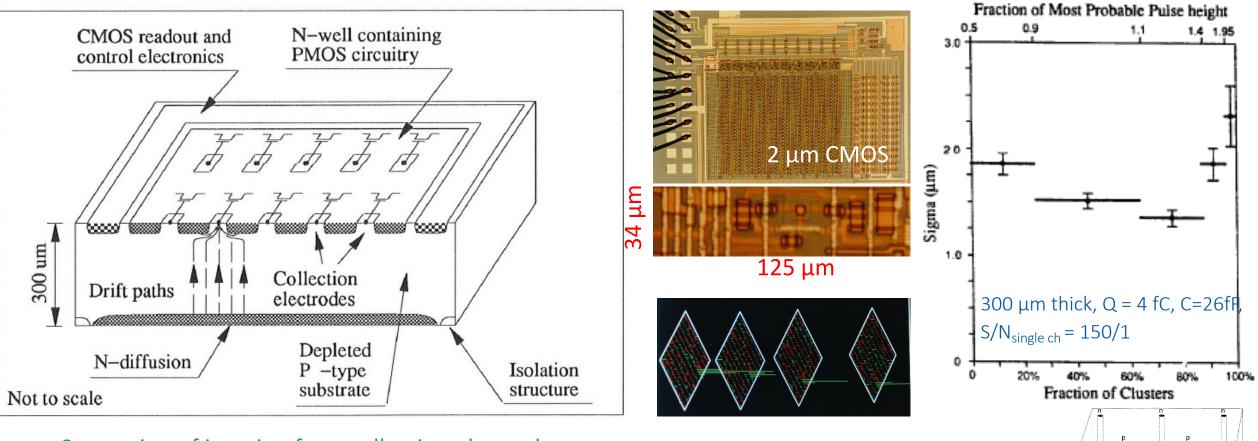

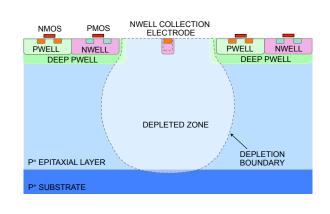

### Small collection electrodes, this example CMOS but double sided process

- Separation of junction from collection electrode

- Better than 2 μm position resolution even at large pitch due to good S/N

- Improved back side trench isolation lead to sensors with 3D electrodes (S.Parker, J. Segal) →

C. Kenney, S. Parker, J. Plummer, J. Segal, W. Snoeys et al. NIM A (1994) 258-265, IEEE TNS 41 (6) (1994), IEEE TNS 46 (4) (1999)

Other examples: ~ 1 μm resolution: SOI sensor, pitch 13.75 μm *M. Battaglia et al. NIM A 654 (2011) 258-265, NIM A 676 (2012) 50-53* Position resolution: good S/N for interpolation Junction separation and back side processing: see below

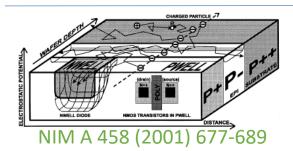

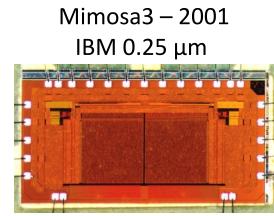

# Mimosa series – IPHC Strasbourg – towards standard CMOS

A monolithic active pixel sensor for charged particle tracking and imaging using standard VLSI CMOS technology

R. Turchetta<sup>a,\*</sup>, J.D. Berst<sup>a</sup>, B. Casadei<sup>a</sup>, G. Claus<sup>a</sup>, C. Colledani<sup>a</sup>, W. Dulinski<sup>a</sup>, Y. Hu<sup>a</sup>, D. Husson<sup>a</sup>, J.P. Le Normand<sup>a</sup>, J.L. Riester<sup>a</sup>, G. Deptuch<sup>b,1</sup>, U. Goerlach<sup>b</sup>, S. Higueret<sup>b</sup>, M. Winter<sup>b</sup>

#### Rolling shutter readout

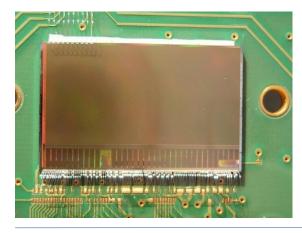

**Mimosa26 – 2008** AMS 0.35 μm

18.4  $\mu$ m pixel pitch 576x1152 pixels

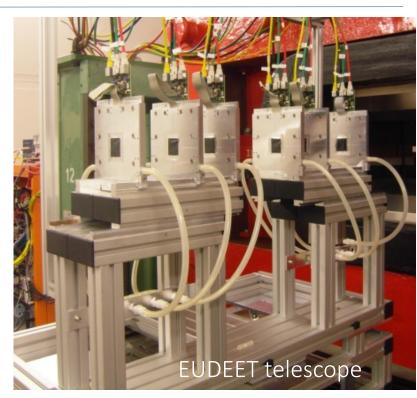

First MAPS with integrated zero-suppressed readout First MAPS used for several applications, also for EUDEET telescope

Mimosa1 – 1999 AMS 0.6 μm

Mimosa2 – 2000 MIETEC 0.35 μm

$20 \mu m$  pixel

$8\mu m$  pixel

....

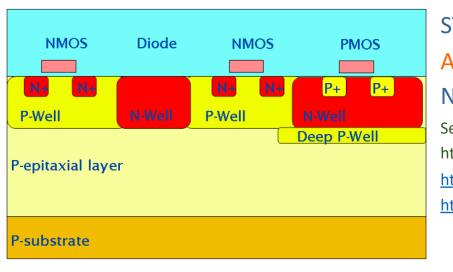

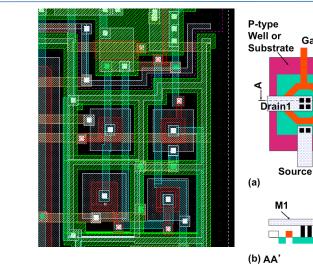

# The INMAPS process: quadruple well for full CMOS in the pixel

STFC development, in collaboration with TowerJazz A game changer Additional deep P-well implant allows complex in-pixel CMOS and 100 % fill-factor New generation of CMOS sensors for scientific applications (TowerJazz CIS 180nm) Sensors 2008 (8) 5336, DOI:10.3390/s8095336 https://iopscience.iop.org/article/10.1088/1748-0221/7/08/C08001/meta https://iopscience.iop.org/article/10.1088/1748-0221/14/01/C01006/meta https://iopscience.iop.org/article/10.1088/1748-0221/14/01/C01006/meta

courtesy of N. Guerrini, STFC

Standard INMAPS process also used for the ALPIDE (27  $\mu$ m x 29  $\mu$ m pixel) and MIMOSIS (CBM)

#### Depleted MAPS: Large collection electrode: rad hard, but large C (100fF or more), but excellent time resolution

T. Hirono et al., https://doi.org/10.1016/j.nima.2018.10.059

Courtesy I.Peric and A. Schoening

### Depleted MAPS: Large collection electrode: MONOLITH: SiGe BiCMOS development

- Heterojunction Bipolar Transistor (HBT) gives cut-off

frequencies otherwise only reached in more

advanced CMOS technologies

- Large collection electrode hexagonal pixel arrangement

- On latest prototype

- Full efficiency

- ~ 20 ps time resolution without gain layer

- Radiation tolerance 10<sup>16</sup> n<sub>eq</sub>/cm<sup>2</sup>, also for the HBT !

Courtesy G. lacobucci

### ARCADIA Sensor: LF 110 nm

|         | Sensor pad   | pwell |

|---------|--------------|-------|

| High Re | sistivity Si |       |

L. Pancheri 2022 IEEE Transactions on Electron Devices Vol. 67, No. 6, June 2020

- Depleted MAPS

- Developed in a collaboration between INFN and LFoundry

- 110 nm CMOS, 6 metal layers

- Adding gain layer (gain 10-20) to reach 20 ps resolution

- Prototypes received in January 2023

- Pixel size: 250 x 100 μm<sup>2</sup>

- Diode area : 220 x 70 μm<sup>2</sup>

- Sensor capacitance: 127 fF

- Electronics size: 280 x 8 μm<sup>2</sup>

- Active thickness: 50 μm<sup>2</sup>

### EP RD WP1.2 on monolithic CMOS sensors: small collection electrode

### Long term goal: develop CMOS sensors in sub 100nm technologies

- Synergy with development of the stitched sensor in the ALICE ITS3 upgrade

- First technology selected: TPSCo 65 nm CMOS imaging technology

- TPSCo (joint venture TJ & Panasonic): several 65 nm flavors: high density logic, RF, and imaging (ISC)

- ISC preferred: 2D stitching experience, special sensor features, different starting materials, lower defect densities, etc

- Initially 5 metal layers, now 7 metals, asking for 1 more very thick.

First submission: MLR1 December 2020 Second submission: ER1 November 2022

65 nm development profited significantly from 10 years of experience in TowerJazz 180 nm.

R&D

FP

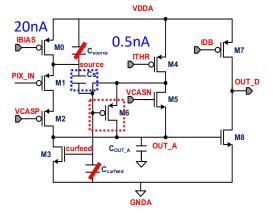

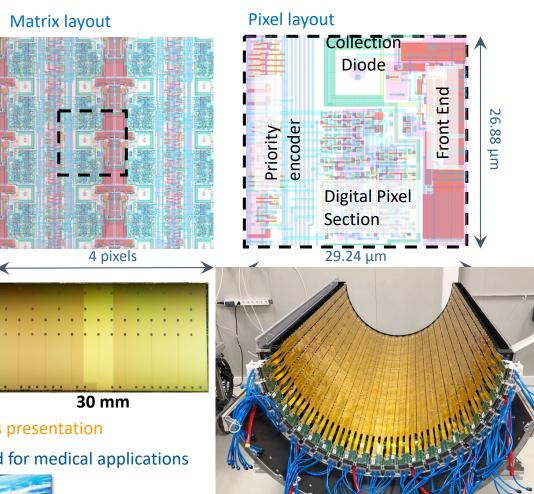

#### TowerJazz 180 nm: ALPIDE chip in ALICE ITS2

- TJ CMOS 180 nm INMAPS imaging process (TJ) >  $1k\Omega$  cm p-type epitaxial layer

- Small 2  $\mu$ m n-well diode and reverse bias for low capacitance C(sensor+circuit) < 5 fF

- 40 nW continuously active front end D. Kim et al. DOI 10.1088/1748-0221/11/02/C02042

- Q<sub>in</sub>/C ~ 50 mV, analog power ~ (Q/C)<sup>-2</sup> NIM A 731 (2013) 125

- Zero-suppressed readout, no hits no digital power G. Aglieri et al. NIM A 845 (2017) 583-587

- Ratio between 15 x 30 mm<sup>2</sup> and 10 m<sup>2</sup> in the experiment not ideal -> stitching -> P. Riedler's presentation

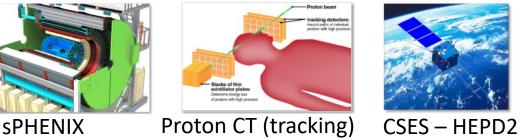

- ALPIDE (ALICE Pixel Detector) to be used for several other physics experiments, in space and for medical applications

Design team: G. Aglieri, C. Cavicchioli, Y. Degerli, C. Flouzat, D. Gajanana, C. Gao, F. Guilloux, S. Hristozkov, D. Kim, T. Kugathasan, A. Lattuca, S. Lee, M. Lupi, D. Marras, C.A. Marin Tobon, G. Mazza, H. Mugnier, J. Rousset, G. Usai, A. Dorokhov, H. Pham, P. Yang, W. Snoeys (Institutes: CERN, INFN, CCNU, YONSEI, NIKHEF, IRFU, IPHC) and comparable team for test 1 MPW run and 5 engineering runs 2012-2016, production 2017-2018

4 pixels

ш Ш

15

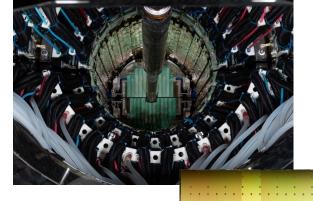

### ALICE Inner Tracker System 2 (ITS2) taking data

7 cm

### ITS 3 upgrade: replace 3 inner layers with wafer scale stitched sensors<sup>1</sup>

(1) https://indico.cern.ch/event/1071914, ALICE ITS3 – a next generation vertex detector based on bent, wafer-scale CMOS sensors, Magnus Mager (CERN) (1) https://cds.cern.ch/record/2703140/files/LHCC-I-034.pdf - Letter of Intent for an ALICE ITS Upgrade in LS3

## Pixel optimization in 180 nm (started in 2012)

Charge sharing

# Process optimization: 65 nm very similar

65 nm development profited significantly from 10 years of experience in TowerJazz 180 nm.

Charge collection speed

Charge sharing

"10th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging" PoS(Pixel2022)001, DOI: <u>https://doi.org/10.22323/1.420.0001</u>

20230613 | Front End Electronics 2023 | Monolithic Sensor Development in TPSCo 65nm ISC

R&D

EP

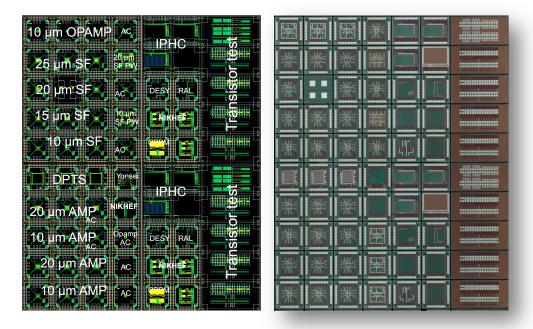

## Development of monolithic sensors for high energy physics in TPSCo 65nm ISC technology

- CERN EP R&D (WP1.2 Monolithic Pixel Detectors) investigating sub 100 nm technologies for HEP

- Many contributors, strong synergy with ALICE ITS3 upgrade, very large measurement team (40-50 people)

- First technology selected TPSC 65 nm ISC, two submissions so far:

MLR1 (December 2020): 1.5 x 1.5 mm<sup>2</sup> test chips Learn about the technology, characterize pixels, transistors and building blocks

ER1 (December 2022): 1.5 x 1.5 mm<sup>2</sup> test chips Prove we can design wafer-scale stitched sensors

similar process modifications as in 180 nm, but more needed in 65 nm <a href="https://doi.org/10.22323/1.420.0001">doi.org/10.22323/1.420.0001</a> Summary of WP1.2: <a href="https://indico.cern.ch/event/1233482/contributions/5264293/attachments/2596131/4482445/EP\_RandD\_Days\_WP1.2\_2023\_02\_20.pdf">https://indico.cern.ch/event/1233482/contributions/5264293/attachments/2596131/4482445/EP\_RandD\_Days\_WP1.2\_2023\_02\_20.pdf</a>

26cm long single silicon

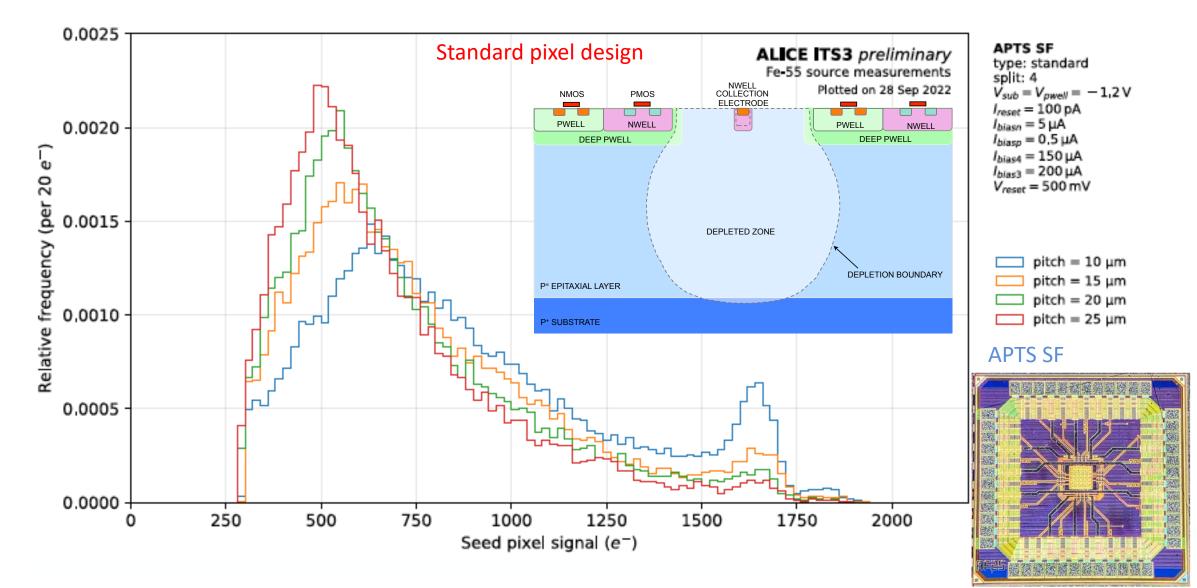

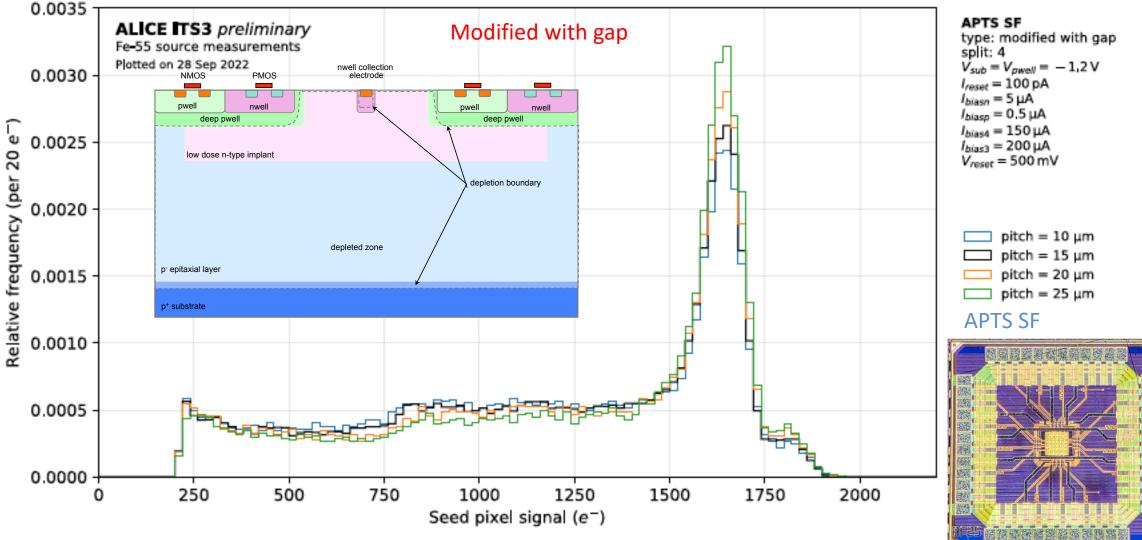

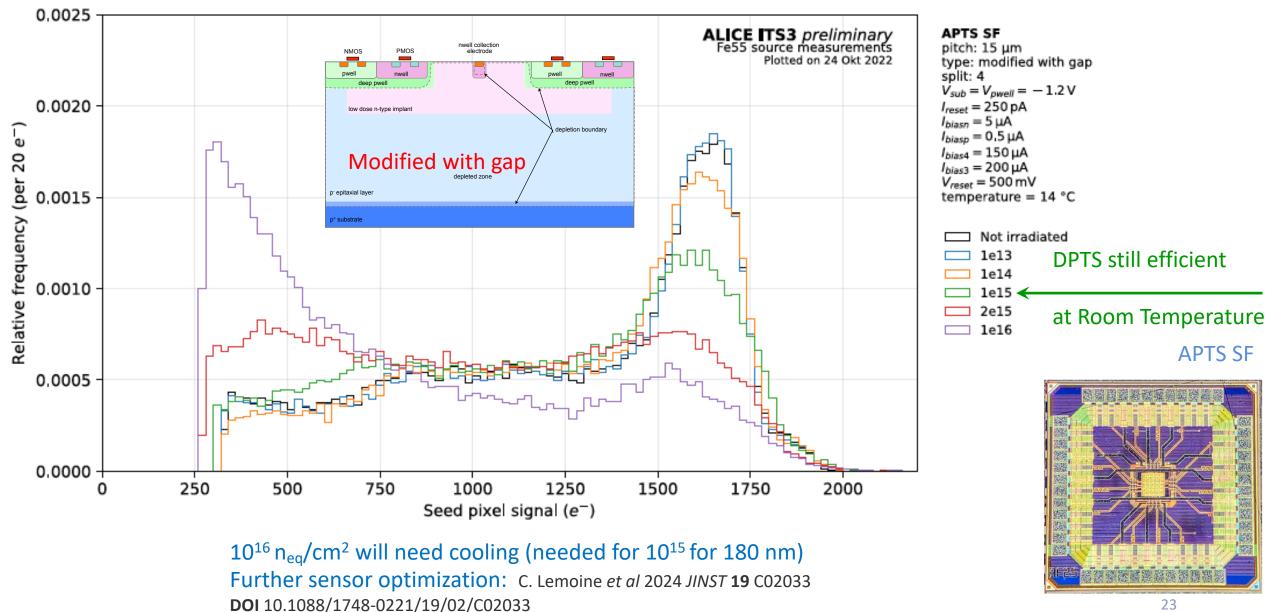

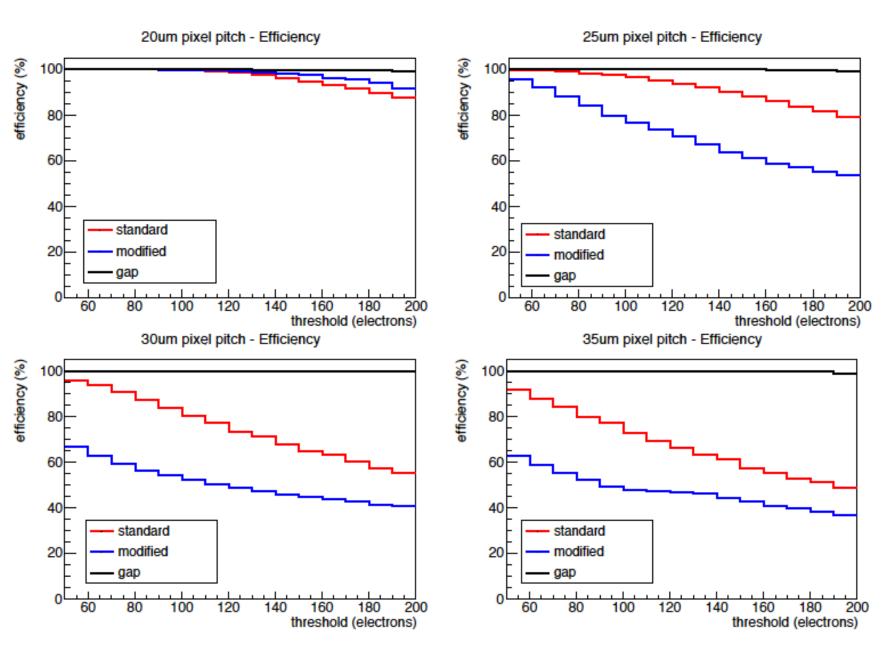

### Pitch dependence for different variants <sup>55</sup>Fe

See also: I. Sanna IEEE NSS 2022

ALICE team measurement

### Pitch dependence for different variants <sup>55</sup>Fe

See also: I. Sanna IEEE NSS 2022

#### ALICE team measurement

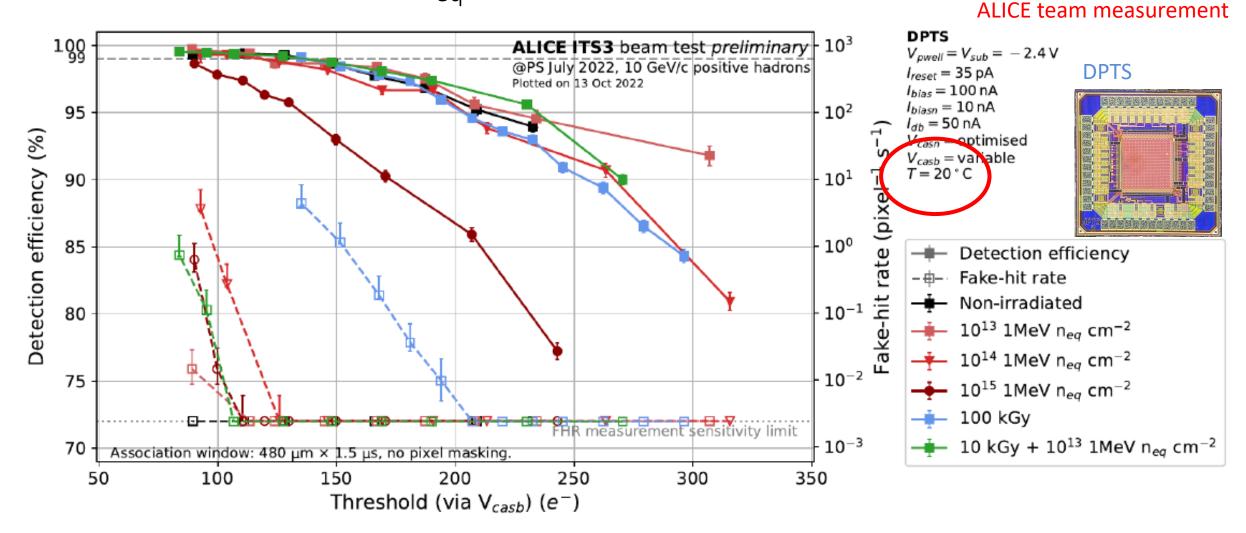

### Remarkable result !

Sensor with gap is only variant conserving efficiency at larger pixel pitches

~ 99 % efficiency at  $10^{15} n_{eq}/cm^2$  ... at room temperature doi: 10.1016/j.nima.2023.168589

- Fully efficient sensor, analog front end, digital readout chain in 15 x 15 μm<sup>2</sup> pixel (DPTS) including sensor optimization

- Transistor total ionizing dose tolerance doi: 10.1088/1748-0221/18/02/C02036 and SEU in line with other 65 nm technologies

- KEY ACHIEVEMENT: 65nm ISC qualified for HEP, many features not yet explored (wafer stacking, special imaging devices...)

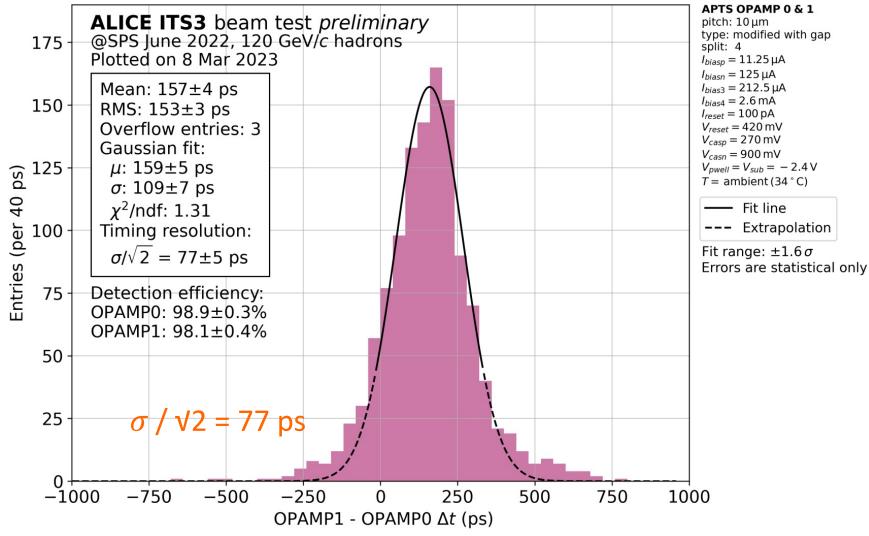

### Sensor timing

#### ALICE team measurement

#### **APTS OPAMP**

(180nm FASTPIX about 100 ps with time walk and cluster size correction, J. Braach et al. doi:10.48550/arXiv.2306.05938)

22

Bong-Hwi, U. Savino et al. ULITIMA 2023

Irradiation results: exploring paths to higher fluences (I. Sanna et al.)

ALICE team measurement

23

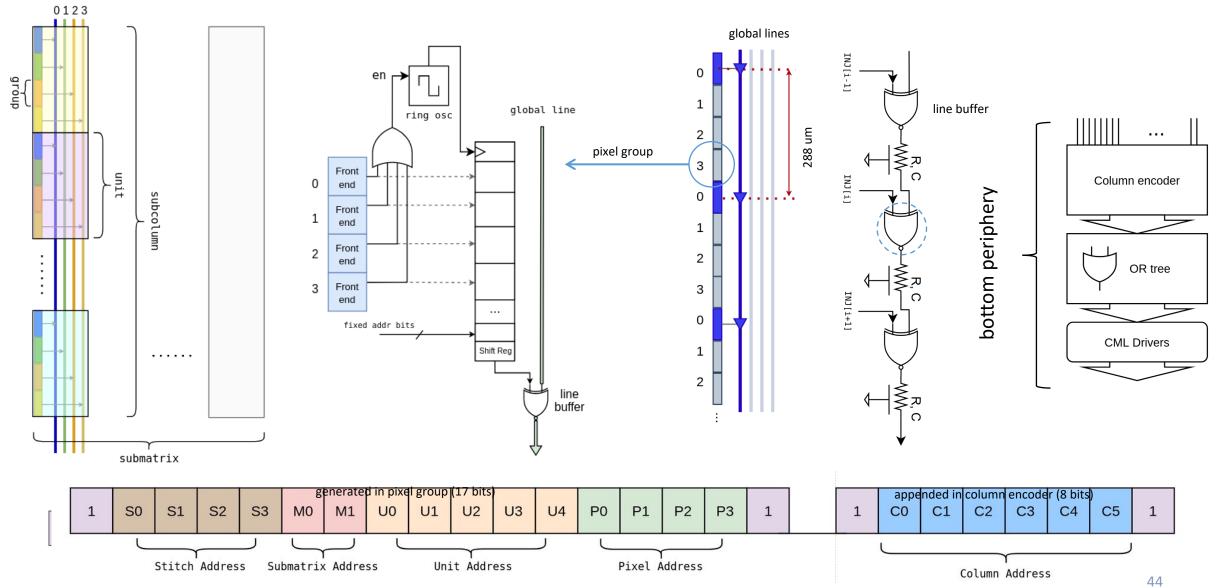

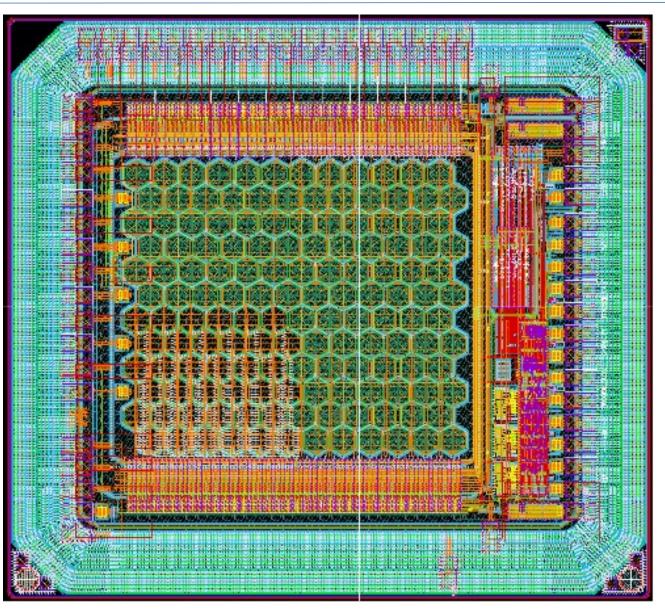

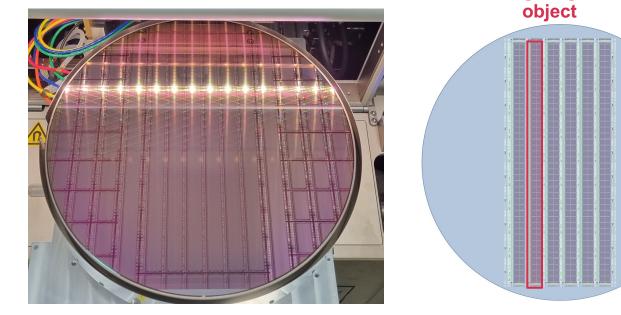

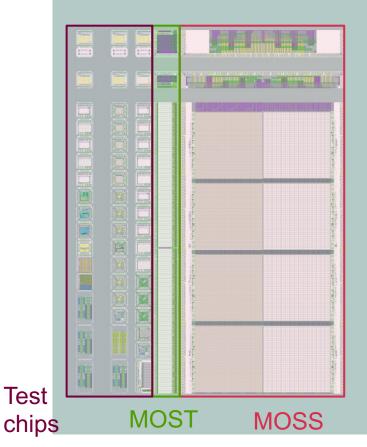

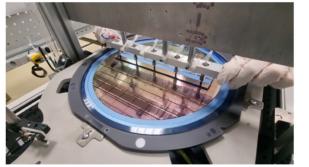

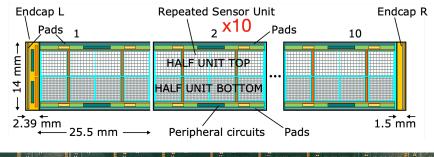

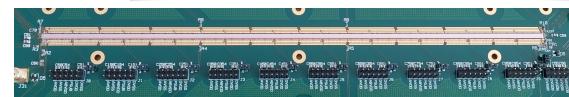

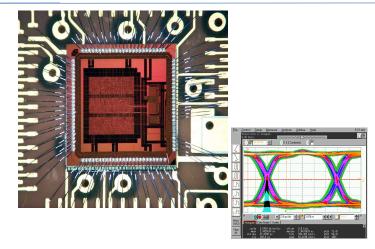

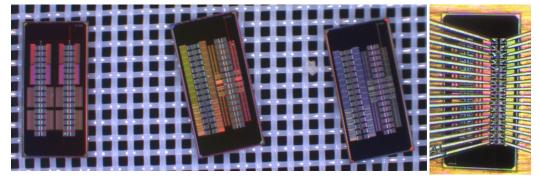

# **ER1** submission

- Two stitched sensor chips, 6 of each per wafer, digital on top design

- MOSS chip (1.4 x 26 cm)

٠

- Conservative layout (DFM rules), Alpide-like readout scheme and 1/20 power segmentation

- MOST chip (0.25 x 26 cm)

- High local density with high granularity of power gating to mitigate faults, async hit driven readout

- 51 chiplets for prototyping blocks and pixel chips

- PLL, pixel prototypes, fast serial links, SEU test chips, ...

- IPHC, NIKHEF, STFC, DESY, SLAC, INFN, CERN...

- Learn stitching methodology, wafer assembly and automated signoff (P. Leitao et al.)

- Learn about yield, design for manufacturing (DFM) and defects masking

- Study power schemes, leakage, spread, noise and speed

- Practical application: Alice ITS3 upgrade

- WP1.2 and DRD7.6a :Technology and support development for different clients (other DRD's (like DRD3) and experiments) with organization of common runs

- New metal stack: new I/Os, PDK, DDK, DRC rules

- Custom DRC and LVS rule check, custom DFM standard library

- Legal framework, nda ...

#### reticle

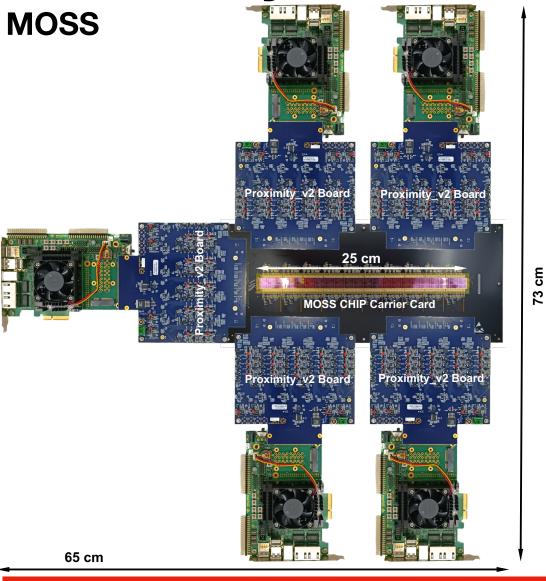

# ER1 test systems

ICE

- same FPGA board (x1) as MOSS +

- oscilloscope for readout +

MOST

Test system scale in size as the sensors do

Magnus Mager | Stitched MAPS | HSTD 13, Vancouver, December 2023

Magnus Mager (CERN) | Stitched MAPS | HSTD43 | 07.12.2023 | X

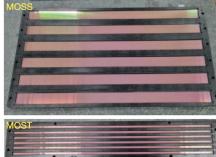

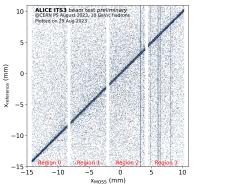

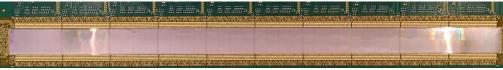

### MOSS (25.9 cm x 1.4 cm)

- 10 repeated sensor units:

- top half at 22.5 um pitch and bottom half at 18 um pitch,

- each half powered completely independently with 4 conservatively designed submatrices -> many power domains

- synchronous readout

- First operation in beam in August (D. Colella TIPP2023)

- Detection efficiencies and fake hit rates (M. Mager HSTD 2023)

- Intense effort on powering tests and yield investigations and more detailed characterization

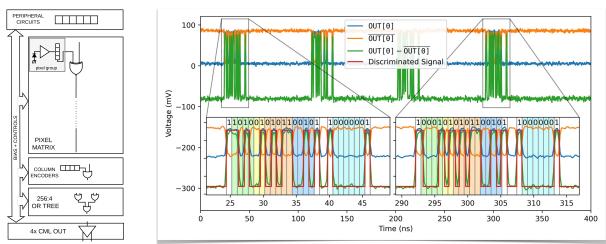

### MOST (25.9 cm x 0.25 cm)

#### 10 repeated sensor units:

- 18 um pitch, very densely designed pixel matrix

- Global power distribution + conservatively designed highly granular power switches to switch off faulty parts

- Asynchronous, hit-driven readout, low power consumption + timing information

- Basic functionality established, detailed characterization ongoing, yield investigations to be started.

- Pulsing signal and output signals at the end of the chip, round trip more than 50 cm, ~ 200 ns, with ~800 repeaters, all 256 signal lines functional.

### **NEXT STEP: MOSAIX chip for ITS3**

MOSAIX chip is being designed, submission in the fall.

- 12 repeated sensor units

- Learnings from MOSS and MOST on stitching are fed back into the design

- Use power switches with power granularity from 20 in MOSS to 144 per segment here

- 3, 4 and 5 segments for layer 0, 1 and 2, respectively

266 111 HaltLayer z Rφ (azimuthal direction) folded around beam-pipe C side A side 58 SEGMENT 74,064 8 18,516 548 55 Layer 0: 3 segments 21,666 Z-axis (equatorial direction) Layer 1: 4 segments beam length Layer 2: 5 segments 259,992 Repeated Sensor Unit 4,5 1,5 (RSU) 265,992 27

(M. Mager HSTD 2023)

ALICE

rφ

### ALICE 3 sensor specification estimates <a href="https://arxiv.org/pdf/2211.02491.pdf">https://arxiv.org/pdf/2211.02491.pdf</a>

| ALICE |

|-------|

| LOI es      | stimates,   | 24 MHz pp o   | collision      | rate, 1/r <sup>2</sup> - | - scaling    | Hit                      | Rate                      | Ba            | andwi             | dth               |           |                              |               | ALICE     |

|-------------|-------------|---------------|----------------|--------------------------|--------------|--------------------------|---------------------------|---------------|-------------------|-------------------|-----------|------------------------------|---------------|-----------|

|             |             | Layer         | Radius<br>(cm) | Surface (m2)             | Pixels (1e6) | Hit Rate<br>(1e6/cm^2/s) | Hit Rate<br>(1e9/layer/s) | Hits (Gbit/s) | Noise<br>(Gbit/s) | Total<br>(Gbit/s) | Power (W) | NIEL<br>(1 MeV<br>n_eq/cm^2) | TID<br>(Mrad) |           |

| Vertex Dete | ector       | 0             | 0.5            | 0.016                    | 160          | 94                       | 17                        | 274           | 1                 | 275               | 13        | 9,00E+15                     | 288           |           |

|             |             | 1             | 1.2            | 0.038                    | 380          | 16                       | 7.3                       | 117           | 2.4               | 119               | 32        | 1,60E+15                     | 50            |           |

|             |             | 2             | 2.5            | 0.079                    | 790          | 3.8                      | 3.6                       | 57            | 5                 | 62                | 66        | 3,60E+14                     | 12            |           |

| Middle Laye | ers         | 3             | 3.8            | 0.29                     | 120          | 1.7                      | 1.8                       | 28            | 0.7               | 79                | 175       | 1,60E+14                     | 5             |           |

|             |             | 4             | 7              | 0.55                     | 220          | 0.48                     | 1.2                       | 18            | 1.4               | 43                | 131       | 4,60E+13                     | 1.5           |           |

|             |             | 5             | 12             | 0.94                     | 370          | 0.16                     | 0.8                       | 13            | 2.4               | 27                | 224       | 1,60E+13                     | 0.5           |           |

|             |             | 6             | 20             | 1.6                      | 620          | 0.058                    | 0.6                       | 9.9           | 4                 | 19                | 374       | 5,60E+12                     | 0.2           |           |

| Outer Track | ker         | 7             | 30             | 2.3                      | 930          | 0.026                    | 0.5                       | 7.9           | 6                 | 16                | 561       | 2,50E+12                     | 0.08          |           |

|             |             | 8             | 45             | 7.5                      | 3000         | 0.012                    | 0.6                       | 9.6           | 19.1              | 33                | 1792      | 1,10E+12                     | 0.04          |           |

|             |             | 9             | 60             | 10                       | 4.00E+03     | 6.50E-03                 | 0.5                       | 8.2           | 25.5              | 36                | 2389      | 6,30E+11                     | 0.02          |           |

|             |             | 10            | 80             | 13.3                     | 5.30E+03     | 3.70E-03                 | 0.4                       | 6.8           | 34                | 42                | 3185      | 3,50E+11                     | 0.01          |           |

|             |             |               |                | 1                        | Vertex Dete  | ctor Midd                | le Layers                 | Outer Tra     | cker l            | TS3               | ITS       | 2                            |               |           |

| Pi          | ixel size ( | μm^2)         |                |                          | O(10         | x 10)                    | O(50 x 50)                | O(50          | ) x 50)           | O(20              | x 20)     | O(30 x 30)                   |               |           |

| Pc          | osition re  | solution (μ   | m)             |                          |              | 2.5                      | 10                        |               | 10                |                   | 5         | 5                            |               |           |

| Ti          | me resol    | ution (ns R   | VIS)           |                          |              | 100                      | 100                       |               | 100               | 100* / O(1        | .000)     | O(1000)                      |               |           |

| in          | -pixel rat  | e (/ pixel /  | s)             |                          |              | 100                      | 100                       |               | 100               |                   |           |                              |               |           |

| Fa          | ake-hit ra  | te (/ pixel / | event)         |                          |              | <1e-7                    | <1e-7                     |               | <1e-7             | <                 | <1e-7     | << 1e-6                      |               |           |

| Pc          | ower con    | sumption (    | mW / cr        | n^2)                     |              | 70                       | 20                        |               | 20                |                   | 20**      | 47 / 35***                   | F. Reid       | dt et al. |

|             |             |               |                |                          |              |                          |                           |               |                   |                   |           |                              |               |           |

Need significant improvement in:

- Power-performance ratio, not only in front end, but also on and off chip data transmission, and architecture

- Radiation tolerance for inner layers

=> Observing convergence in sensor development targets, mostly common in the short term for different HEP applications, with longer term incremental R&D (L. Musa <u>https://indico.cern.ch/event/994685/contributions/4181740/attachments/2193327/3707745/MUSA\_ECFA\_IS\_2021FEB.pdf</u>) see also D. Contardo

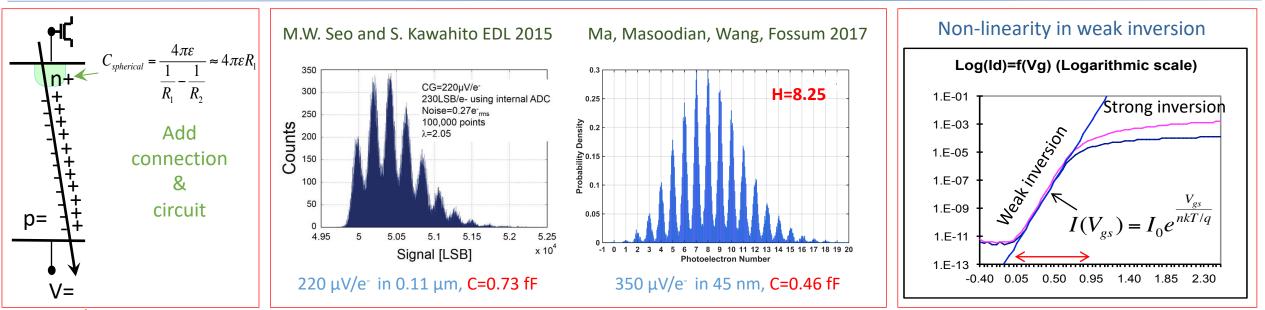

## Analog power consumption ~ $(Q/C)^{-2}$ (NIM A 731 (2013) 125)

- Q/C several 10's of mV in 180 nm

- "Conventional" approach

- ITS3 ~ 36 nW front end for about 10 mW/cm<sup>2</sup> (ALPIDE in 180nm ~ 40 nW), very significant area reduction for ITS3

- Increase in power to obtain speed for better timing is not sufficient.

- Reduce capacitance further, using:

- tricks from imaging technology, at present not yet explored

- now very conventional nwell collection electrode...

- Still need to extract signal charge from underneath the readout circuit !

- deeper submicron: 2500 e- to switch inverter in 65 nm, 850 e- in 28 nm, 100 e- in 5 nm A. Marchioro 2019 CERN EP seminar

#### Holy Grail: For Q/C > 400 mV, analog power consumption goes to zero. ... or gain layers like LGADs!

### Power consumption and voltage drops

Energy to transfer 1 bit to the periphery (assume line toggle, not step):

1 cm line at 1.8 V =  $CV^2$  = 2 pF x (1.8 V)<sup>2</sup> = 6.5 pJ Lower VDD in deep submicron = 2 pF x (1 V)<sup>2</sup> = 2 pJ Caveat: 2pF/cm can increase depending on line load...

- Digital power density proportional to activity level (hit densities...) and column height, but now leakage also important !!

- Voltage drops proportional to the square of the column height and power density

- For constant power density (eg analog) voltage drops proportional to the square of the column height

- Digital voltage drops for long distance sin full CMOS proportional to the third power of the column height

- Significant challenge for stitched devices, in addition to yield

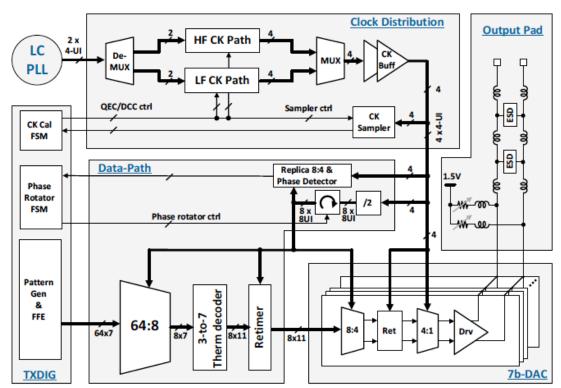

### **Off-detector transmission:**

ISSCC 2013 / SESSION 2 / ULTRA-HIGH-SPEE

2.6 A 32-to-48Gb/s Serializing Transmitter Using Multiphase Sampling in 65nm CMOS

Amr Amin Hafez, Ming-Shuan Chen, Chih-Kong Ken Yang

University of California, Los Angeles, CA

| Block            | Power (mW) | Fraction (%) |

|------------------|------------|--------------|

| VCO              | 26.6       | 30.2         |

| Divider Chain    | 18         | 20.5         |

| Buffer/PFD/CP    | 2          | 2.3          |

| Predriver/Driver | 26.4       | 30           |

| Serializer       | 15         | 17           |

| Total            | 88         | 100          |

INTEL, ISSCC2021, 224Gbps, PAM-4, 1.7 pJ/bit, 10 nm technology

State of the art: a few mW/Gbps, already earlier but also now at much higher bandwidths

Significant circuit complexity

For HEP important penalty for SEU robustness due to triplication/larger devices...

Important: data concentration, physical volume for material budget, and technology

After years of R&D monolithic sensors for HEP move to CMOS MAPS in mainstream CMOS technology, but requirements for HEP are not completely identical to those for visible light imaging, and some technology flexibility can still be beneficial.

Circuit radiation tolerance as for standard CMOS, which naturally evolved towards significant tolerance with some caveats.

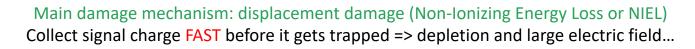

Sensor radiation tolerance, precision timing and improved efficiency can be obtained for small collection electrodes from optimization for fast charge collection using techniques based on general principles applicable to different technologies. Large collection electrode sensors provide extreme radiation tolerance and more uniform sensor timing but exhibit large input capacitance.

Decreasing technology feature size or special imaging sensor features or gain layers can increase the voltage excursion on a small collection electrode and ultimately reduce analog front end power to zero and allow precision timing at lower power.

Hybrid vs Monolithic distinction is becoming more vague: 2D integration combined with stitching will bring us a long way, but 3D through wafer-stacking could help for the most challenging applications and is becoming more and more readily available.

Feasibility studies on stitched devices will determine the size of the sensors we will design in the future and whether and to what extent we can profit from unbeatable wafer-scale integration. (production volume is in the outer layers, we need to be prepared for volume test/acceptance/monitoring)

TPSCo 65 nm ISC now qualified for HEP and made available to the community through CERN EP RD WP1.2 and together with LF 110nm IS and TJ 180 nm through DRD7.6, with PDK/design environment support, interface to the foundry, common IP development and organization of common runs for other DRD's like DRD3, projects and experiments. Still many learnings in the present developments.

A Monolithic Active Pixel Sensor or MAPS is a complex circuit with extra constraints: sensor bias, coupling into the sensor, ...

- The increasing complexity of the sensor chips require evolution towards digital-on-top design techniques with increasing verification effort.

- Need team of expert chip designers, complemented with device/TCAD/Monte Carlo experts for sensor optimization and simulation. It takes years to train people for this activity and our community, also at CERN, struggles to preserve critical mass and know-how for this activity.

- Significant and fast progress has been made in several developments, but it takes a very significant design and measurement effort (eg 65 nm qualification) requiring federation/concentration of resources in the HEP community.

We cannot sustain many parallel developments in the community, but we observe convergence in sensor development requirements for different future HEP applications

Large area pixel sensors are enabling devices for many cutting edge research fields and practical applications like tracking in HEP, medical imaging, space-borne instruments, etc, illustrated by the interest in chips like ALPIDE and successful developments like Medipix/Timepix !

MAPS are one of the few areas where production volume even within HEP would not be negligible, but where **our community** can have an impact not only on the quality of its own measurements, but also on society in general, and which we should try to exploit to enable access to the most advanced technologies.

Large area pixel sensors are enabling devices for many cutting edge research fields and practical applications like tracking in HEP, medical imaging, space-borne instruments, etc, illustrated by the interest in chips like ALPIDE and successful developments like Medipix/Timepix !

MAPS are one of the few areas where production volume even within HEP would not be negligible, but where **our community** can have an impact not only on the quality of its own measurements, but also on society in general, and which we should try to exploit to enable access to the most advanced technologies.

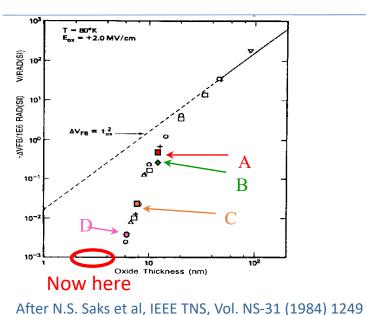

### Circuit radiation tolerance: like standard CMOS

G. Anelli et al., IEEE TNS-46 (6) (1999) 1690

P. Moreira et al. http://proj-gol.web.cern.ch/proj-gol/

#### Total ionizing dose:

- Intrinsic transistor has become more and more radiation tolerant due to thinner gate oxide ۲

- In LHC enclosed NMOS transistors and guard rings in 0.25 µm CMOS to avoid large leakage current ٠

- In deeper submicron enclosed geometry usually no longer necessary for leakage, but for small dimensions parasitic effects dominate e.g. ۲ F. Faccio et al. IEEE TNS-65 (1) 164, 2018 from spacers, new gate dielectrics, requires extensive measurement campaigns

Gate1

Source1

Drain2

Source2

#### Single event effects:

- Single Event Upset : triple redundancy with majority voting (now special scripts S. Kulis) ٠

- Latch-up not observed so far in LHC, but observed on MAPs at STAR, and in new technologies => need attention in the design ۲

### Key achievement after MLR1: TPSCo 65 nm qualified for HEP

- Chain of sensor with process modifications, analog front end, and digital readout fully efficient in test beam validating

process modifications and pixel designs.

- Pixel pitch

DPTS 15  $\mu$ m pixel pitch, stitched devices in ER1 18  $\mu$ m and 22.5  $\mu$ m (180 nm: ALPIDE ~ 28  $\mu$ m)

Sensor variant with gap conserves efficiency at larger pixel pitches.

• Radiation tolerance

NIEL: DPTS 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> at room temperature, 10<sup>16</sup> n<sub>eq</sub>/cm<sup>2</sup> will need cooling (needed for 10<sup>15</sup> for 180 nm) TID: transistors in line with other 65 nm CMOS technologies, leads to tested tolerance beyond 100 Mrad for several circuits (ringoscillators, VCO, DAC, bandgap, etc) SEU: cross-sections in line with other 65 nm CMOS technologies

Timing (only established really for the sensor now);

APTS\_OA ~ 80 ps requires further study, no timewalk correction yet etc (180 nm: FASTPIX ~ 100 ps) see backup

• Many features in the technology still unexplored: special imaging devices, wafer stacking, ....

EP R&D Open day 2023, WP1.2 Summary: https://indico.cern.ch/event/1233482/contributions/5264293/attachments/2596131/4482445/EP\_RandD\_Days\_WP1.2\_2023\_02\_20.pdf Proceedings on process optimization: https://pos.sissa.it/420/083 Article on DPTS chip (under review at NIMA): https://doi.org/10.48550/arXiv.2212.08621

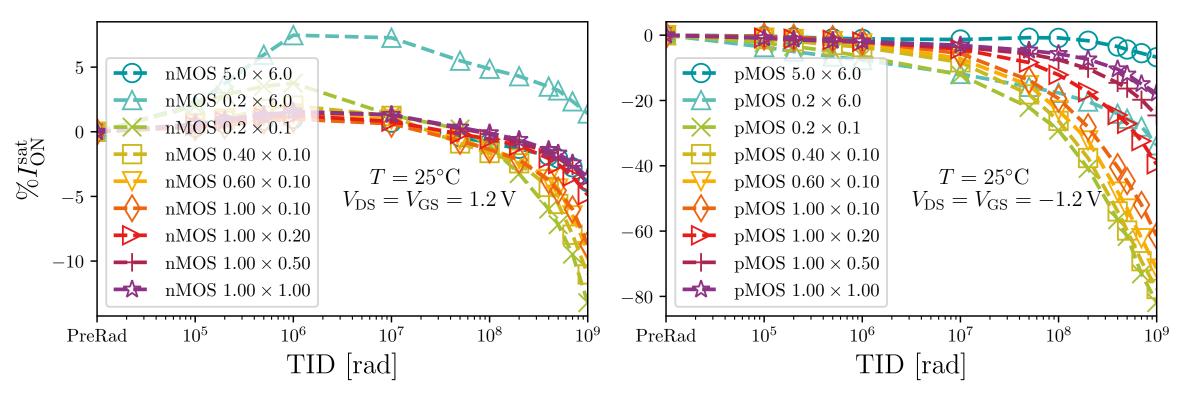

### Transistor radiation tolerance

In line with other 65 nm technologies, no showstoppers.

Small size PMOS transistors degrade significantly after several hundred Mrad.

#### Caveat: modeling of transistors with significant reverse bias

A. Dorda Martin et al. "Measurements of total ionizing dose effects in TPSCo 65 nm and influence of NMOS bulk bias". doi: 10.1088/1748-0221/18/02/C02036

20230613 | Front End Electronics 2023 | Monolithic Sensor Development in TPSCo 65nm ISC

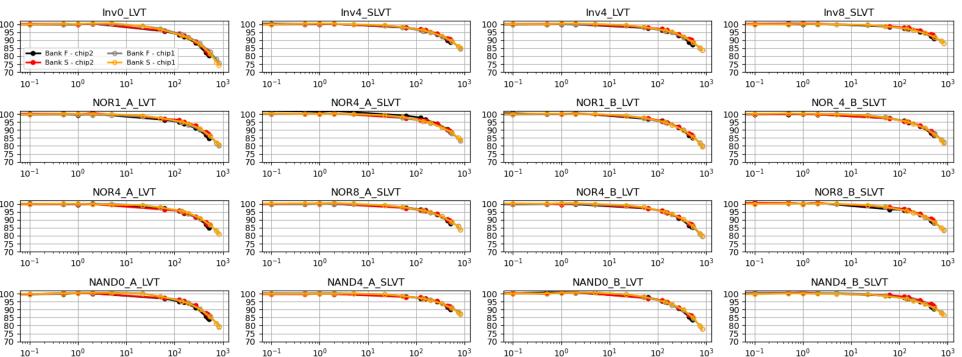

### Ringoscillator test chip

CPPM: Pierre Barrillon, Marlon Barbero, Denis Fougeron, Alexandre Habib and Patrick Pangaud (TWEPP 2022)

- CPPM contributed to MLR1 with a Ring Oscillator test chip to characterize the standard cells of the TJ 65 nm technology.

- The chip contains 48 ring oscillator based on different standard cells.

- 2 banks of 24 Rows each with the purpose of testing two approaches while irradiating:

- Functional: the oscillation is enabled

- Static: the oscillation is disabled

- Oscillation frequency drops by 12-25 % after 830 Mrad. Degradation more pronounced for smaller cells.

- Also several analog designs radiation tolerant up to several 100 Mrad, eg DACs (IPHC), VCO, bandgap (NIKHEF)...

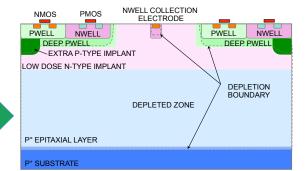

### Different pixel flavors at larger pixel pitches

Simulations by J. Hasenbichler for MIPS

Charge sharing reduces the signal in a single pixel and reduces efficiency especially for larger thresholds.

Only the gap concentrates charge sufficiently to remain efficient for large pixel pitches

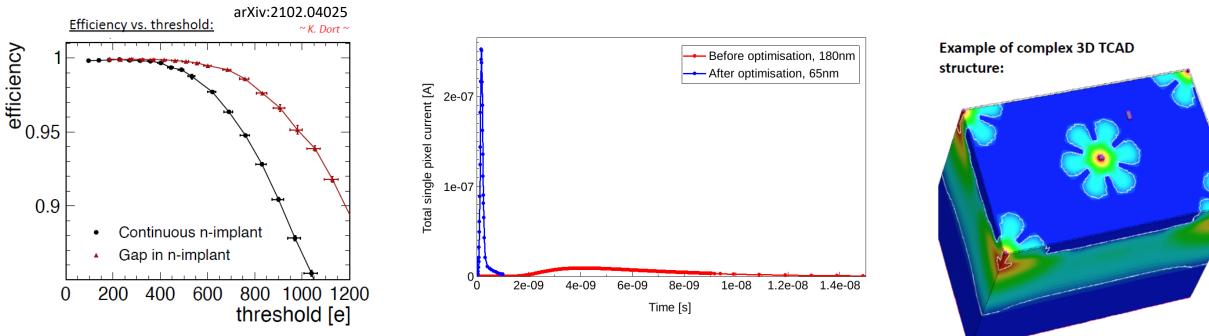

### Process optimizations for small collection electrode

- Efficiency improvement is not only simulated but also measured, even before irradiation (see top left: efficient operating window is almost doubled)

- The optimization over different pixel pitches and flavors, and technologies has improved the timing by several orders of magnitude. Simulations of even more complex structures bring peak-to-peak variations in the order of 50 ps at the moment

- These techniques have now been applied to several chips, and technologies and are generally applicable.

- See M. Muenker's CERN EP detector seminar

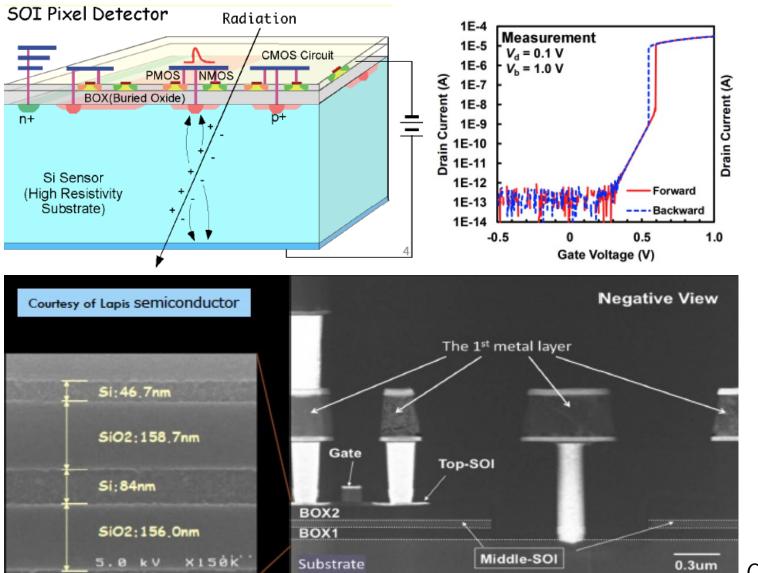

### SOI development in Japan

- Fully depleted 0.15 and 0.2 µm SOI technologies, impressive technology development

- Large user base, more than 20 MPWs so far in addition to dedicated runs

- Some freedom on sensor material

- BOX causes reduced radiation tolerance,several measures for improvement, likedouble box, see bottom left

- Also research on

- steep slope transistors doi:10.1109/SISPAD.2019.8870519

- pinned diodes doi:10.3390/s18010027

•••

Funded by Japan MEXT KAKENHI Grant-in-Aid for Scientific Research on Innovative Areas 25109001

Courtesy Y. Arai

#### Technology also used in presentation by Mizuki Uenomachi 42

#### Small collection electrode: small capacitance, but radiation tolerance and timing more challenging

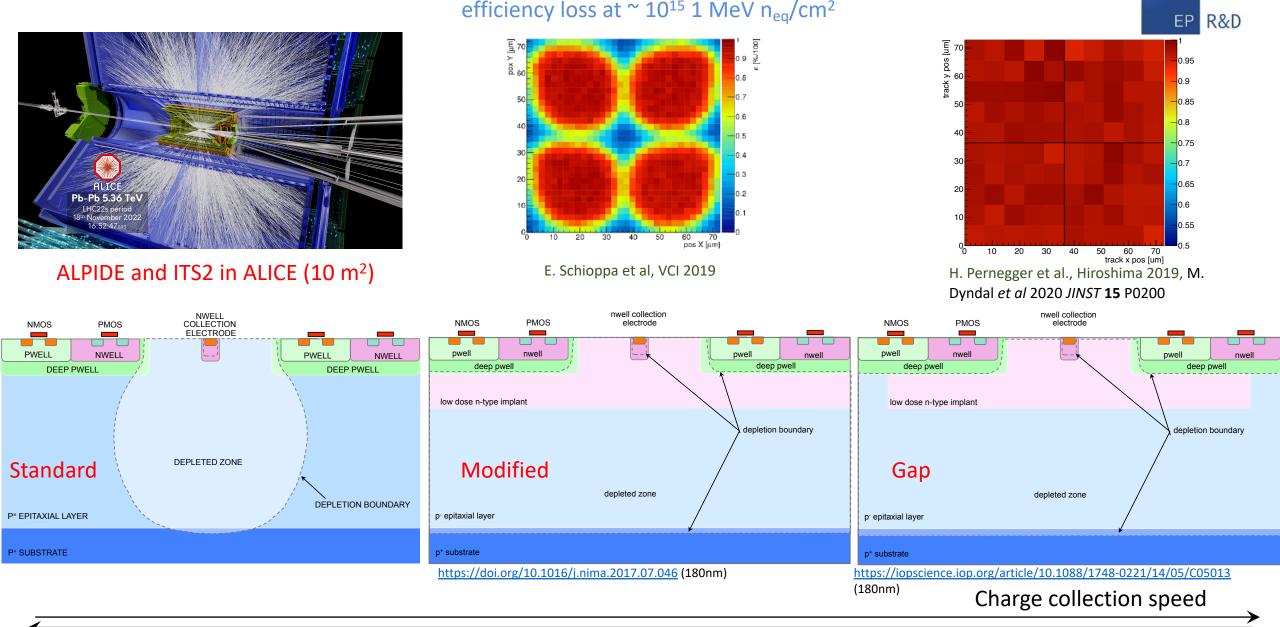

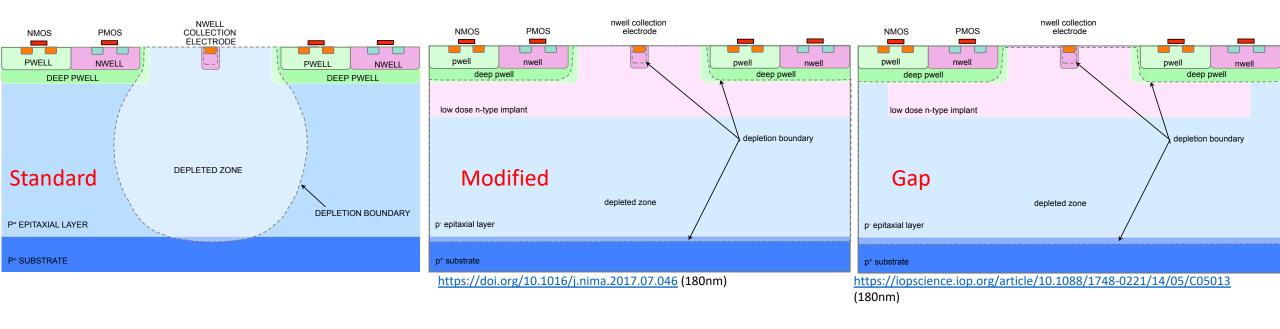

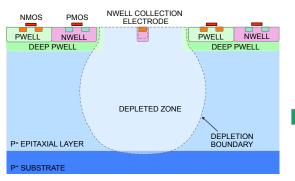

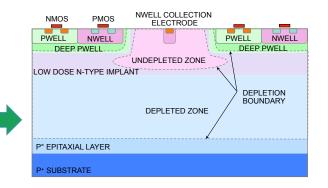

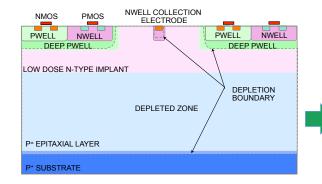

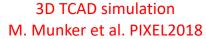

Sensor optimization: Moving the junction away from the collection electrode for full depletion, better time resolution and radiation hardness... and better efficiency, especially for thin sensors

Standard, not fully depleted (ALPIDE)

Additional implant for full depletion => order of magnitude improvement Side development of ALICE for ALPIDE NIMA 871 (2017) pp. 90-96 Triggered development in ATLAS H. Pernegger et al, 2017 JINST 12 P06008

Not fully depleted at low reverse bias

Efficiency drop at pixel edges

after irradiation

for 36.4 x 36.4  $\mu$ m<sup>2</sup> pixel

needs improvement

E. Schioppa et al, VCI 2019

Depletion at higher reverse bias (MALTA1, MONOPIX)

Significant improvement verified Also encouraging results with Cz H. Pernegger et al., Hiroshima 2019 M. Dyndal et al., doi:10.1088/1748-0221/15/02/P02005 M. Van Rijnbach, <u>doi:</u> <u>10.48550/arXiv.2308.13231</u>

Further improvements by influencing the lateral field

Other similar developments for fast charge collection and depletion:

T.G. Etoh et al., Sensors 17(3) (2017) 483, <u>https://doi.org/10.3390/s17030483</u>

H. Kamehama et al., Sensors 18(1) (2017) 27, <u>https://doi.org/10.3390/s18010027</u>...

L. Pancheri et al., PIXEL 2018, <u>https://doi.org/10.3390/s18010027</u>

60 70 pos X [μm}

C. Kenney et al. NIM A (1994) 258-265, IEEE TNS 41 (6) (1994), IEEE TNS 46 (4) (1999)

# MOST Chip: more detail