# Thin n-in-p pixel sensors and the SLID-ICV vertical integration technology for the ATLAS upgrade at HL-LHC

A. Macchiolo

L. Andricek, M. Ellenburg, H.G. Moser, R. Nisius, R.H. Richter, S. Terzo, P. Weigell

Max-Planck-Institut für Physik & MPI Halbleiterlabor (HLL), Munich

In collaboration with **Fraunhofer**

International Workshop on Semiconductor Pixel Detectors for Particles and Imaging, Inawashiro, Japan

# **PIXEL2012**

EMFT

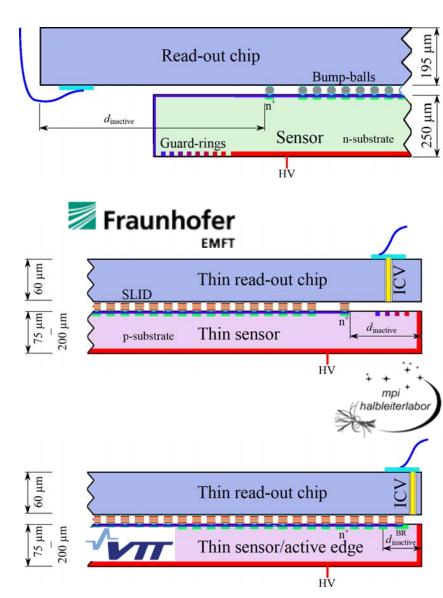

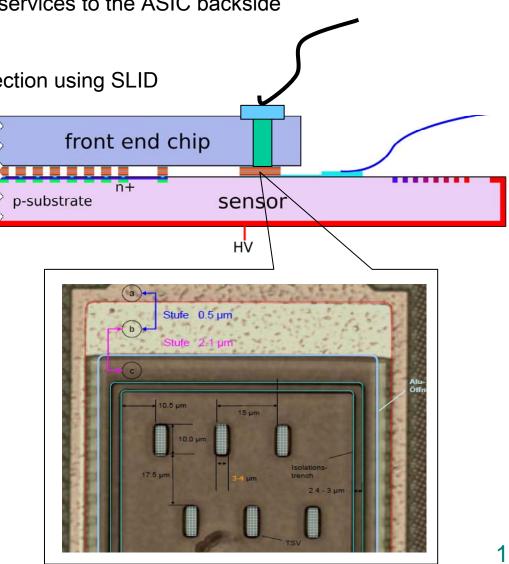

## R&D towards a 3D integrated demonstrator module

R&D towards a fully 3D integrated demonstrator pixel assembly allowing for a minimized inactive area:

□ from the present ATLAS pixel module design ...

$\Box$  ... to a 3D integrated assembly with thin sensors (75-150 µm range) interconnected with the Solid Liquid Interdiffusion technique, SLID, to thin chips (down to 60 µm thickness)

□ Through Silicon Vias (TSV) etched in the readout chip on the front-side on the positions of the original wire bonding pads to route signal and services to the ASIC backside

Production of active edge sensors to achieve a fully four-side buttable module, in collaboration with VTT (Finland)

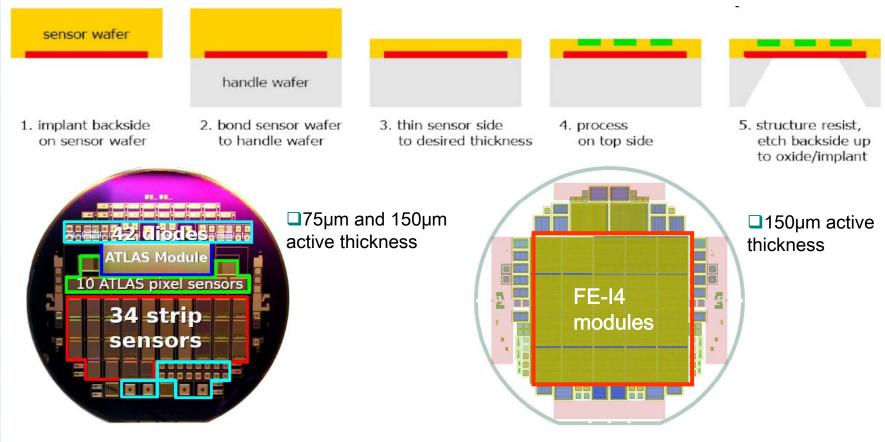

## Thin pixel technology at MPP-HLL

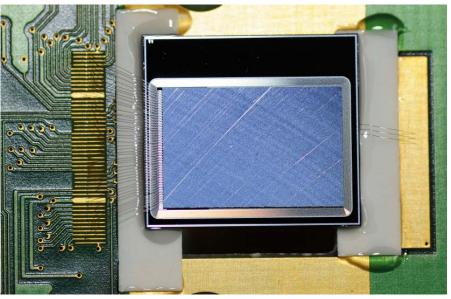

□n-in-p 6" wafers with ATLAS FE-I3 compatible sensors

$\square$  75  $\mu m$  thick sensors interconnected with SLID to FE-I3 chips, thinned down to 200  $\mu m,$  at EMFT

- **I** n-in-p 6" wafers with ATLAS FE-I4 sensors (pitch 50  $\mu$ m x250  $\mu$ m)

- □ IBL compatible GR  $\rightarrow$  450 µm dead edge

- $\hfill \Box$  Interconnected to FE-I4 chips with bump-bonding at  $_3$  IZM

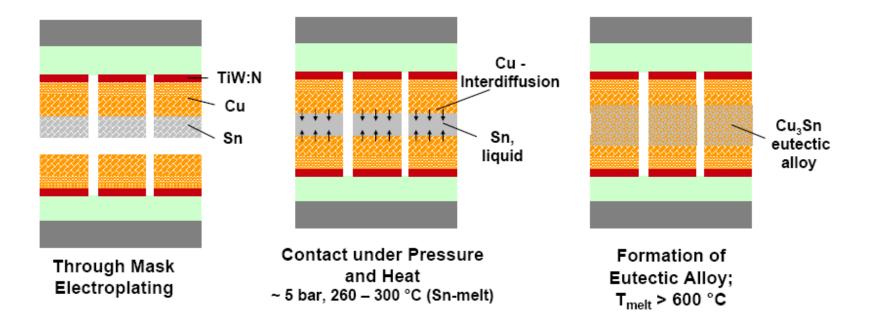

# **EMFT SLID Process**

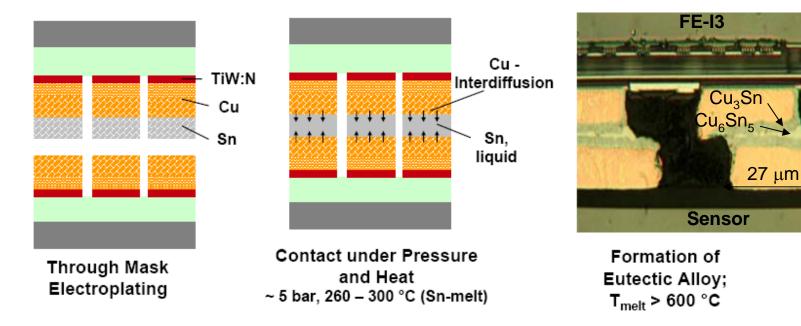

## Metallization SLID (Solid Liquid Interdiffusion)

- □ Alternative to bump bonding (less process steps "lower cost" (EMFT)).

- Small pitch possible (~ 20  $\mu$ m, depending on pick & place precision).

- □ Stacking possible (next bonding process does not affect previous bond).

- □ Wafer to wafer and chip to wafer possible.

- □ For the analysis of the interconnection efficiency: <u>arXiv:1202.6497</u>

# **EMFT SLID Process**

## Metallization SLID (Solid Liquid Interdiffusion)

- Alternative to bump bonding (less process steps "lower cost" (EMFT)).

- Small pitch possible (~ 20  $\mu$ m, depending on pick & place precision).

- Stacking possible (next bonding process does not affect previous bond).

- □ Wafer to wafer and chip to wafer possible.

- □ For the analysis of the interconnection efficiency: <u>arXiv:1202.6497</u>

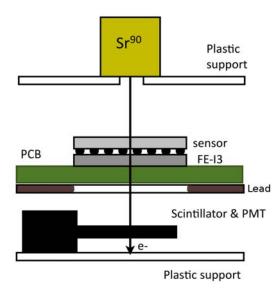

## Set-up for the pixel module characterization

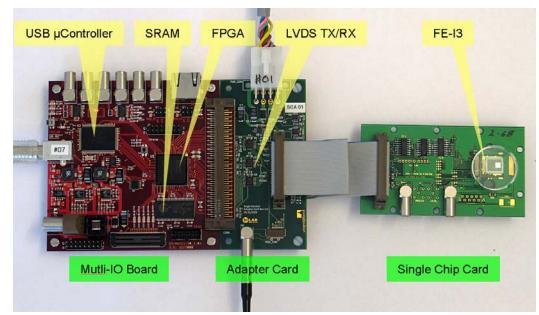

Pixel modules glued and wirebonded to a detector board designed by the University of Bonn in two versions for FE-I3 and FE-I4

Measurements performed with the ATLAS USBPix read-out system

September 2012

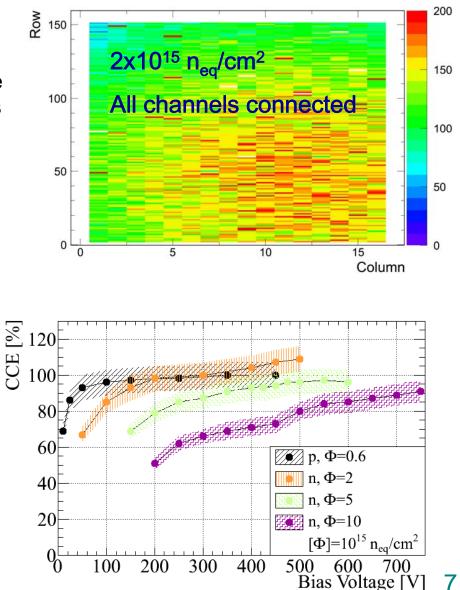

## Post irradiation characterization of SLID modules

□ Good Charge Collection efficiency after irradiation up to 10<sup>16</sup> n<sub>eq</sub>/cm<sup>2</sup>

□ Number of unconnected channels stable after irradiation and multiple thermal cycles  $(+20^{\circ}C \rightarrow -50^{\circ}C)$

SLID interconnection is radiation hard and withstands thermal cycling

$5x10^{15} n_{eq}/cm^{2}$

MPV = 4.8 ke

$V_{bias}$ =600V

20

30

Charge in ke

10

Hit Map

<u>Conference, Inawashiro</u> 20000 A. Macchiolo, PIXEXL2012 15000 10000 5000

September 2012

A. Macchiolo, PIXEXL2012 Conference, Inawashiro, 7

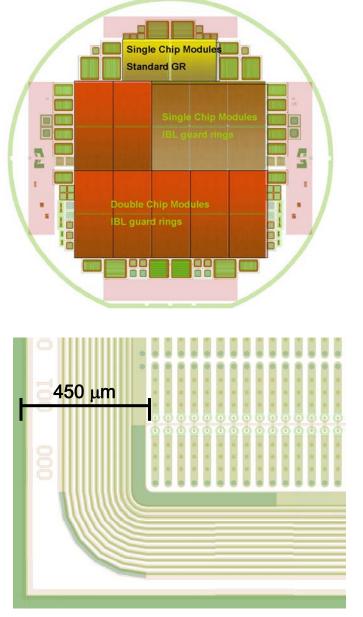

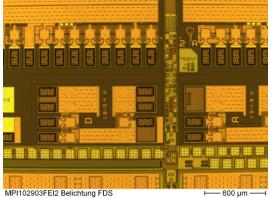

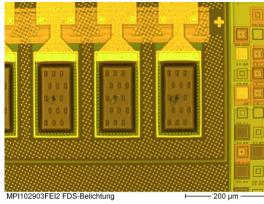

## MPP-HLL SOI2 production: FE-I4 sensors, 150 $\mu m$ thick

#### Pixel sensors with FE-I4 geometry

- □ Single and Double Chip Modules

- □ SCM 1.7x2.1 cm<sup>2</sup> dimensions

- Pitch 25x250 μm<sup>2</sup>

- **450** μm inactive edge (IBL specifications)

#### **11 Single Chip Modules analyzed**

□ Interconnection by bump-bonding at IZM

$\hfill 1$  module irradiated at  $2x10^{15}~n_{eq'}~cm^2$  at KIT with 25 MeV protons

$\hfill 3$  modules irradiated at  $4x10^{15}~n_{eq/}~cm^2$  in Los Alamos with 800 MeV protons

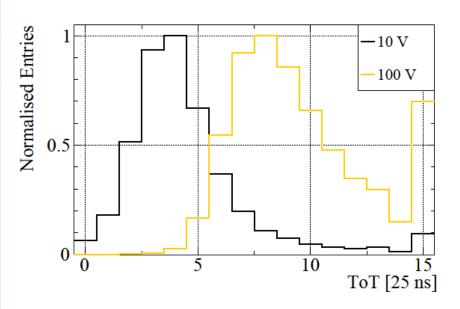

<sup>90</sup>Sr Scan with Threshold=1600 e , Tuning of 10 ToT for 15 ke

□ FE-I4 chip with 4-bit resolution ToT

❑ No injection capacitance measurement circuitry was implemented in FE-I4A → difficoult determination of the absolute charge calibration

$\square$  MPV compatible with 12ke, value expected with a thickness of 150  $\mu$ m

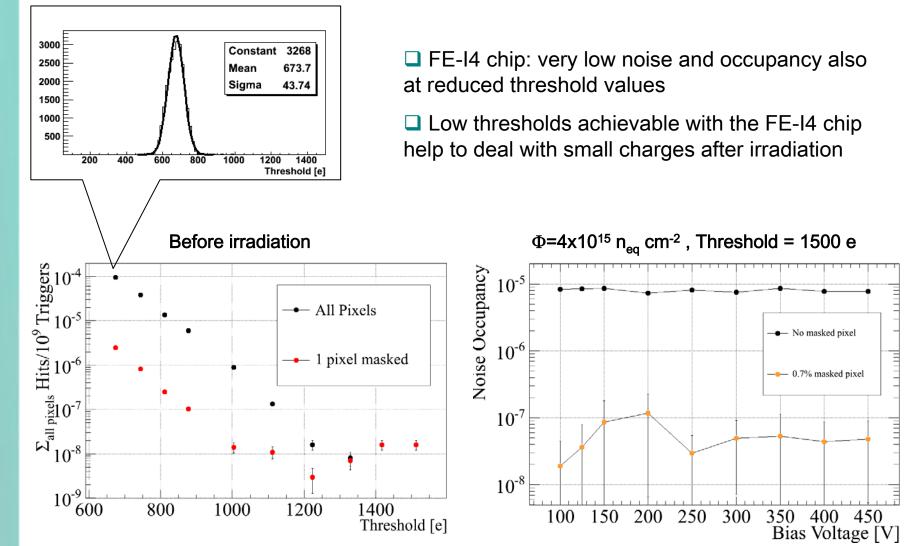

## FE-I4 n-in-p modules: noise occupancy at low thresholds

10

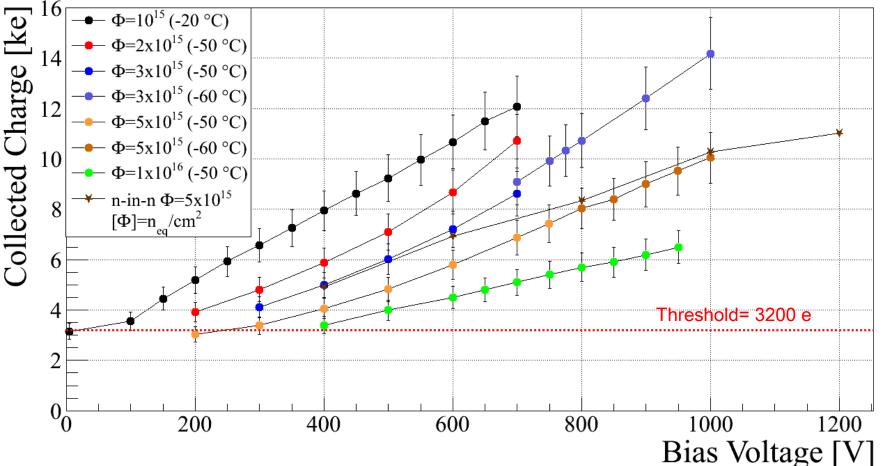

## CC for FE-I3 n-in-p pixels, 285 $\mu m$ thick

Charge collection summary of neutron irradiated CiS n-in-p modules, <sup>90</sup>Sr scan *Ch. Gallrapp, A. La Rosa, A. Macchiolo, R. Nisius, H. Pernegger, R.H. Richter , P. Weigell*

C. Gallrapp et al., "Performance of novel silicon n-in-p planar Pixel Sensors", Nucl. Instrum. Meth. A679 (2012) 29

11

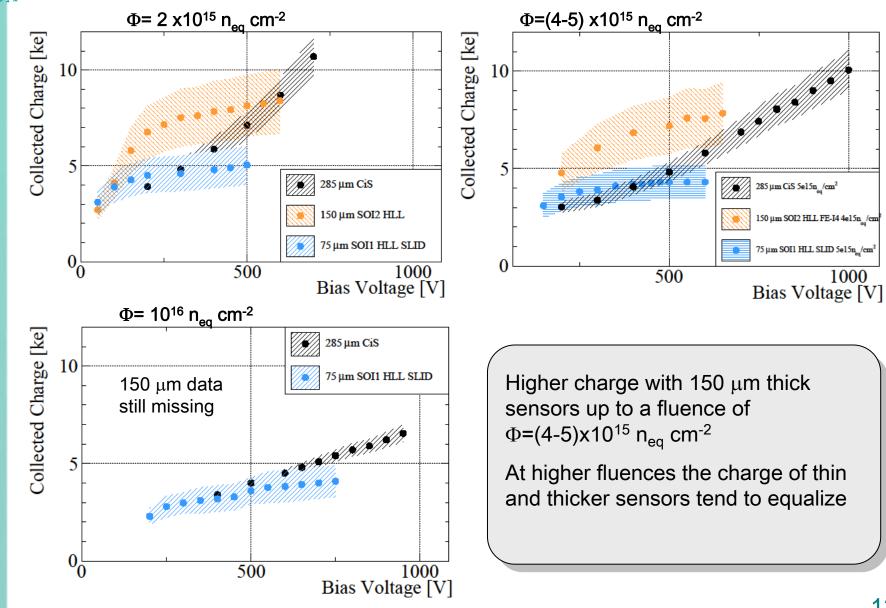

## Comparison of CC for n-in-p pixels of different thickness

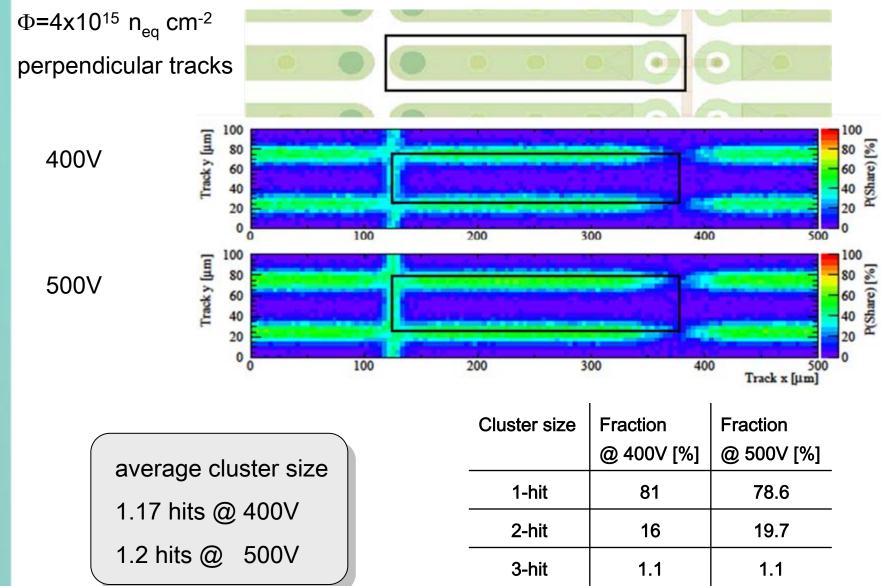

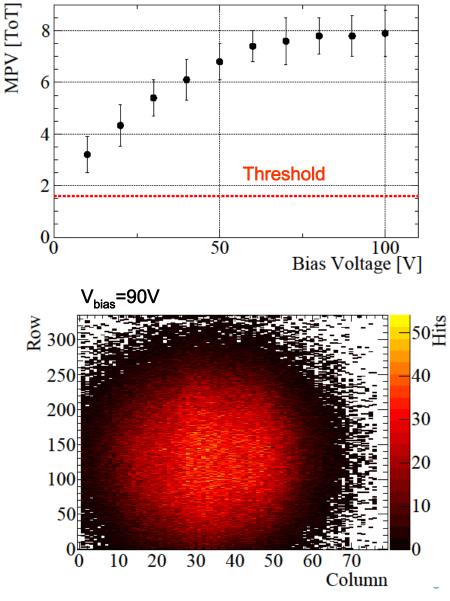

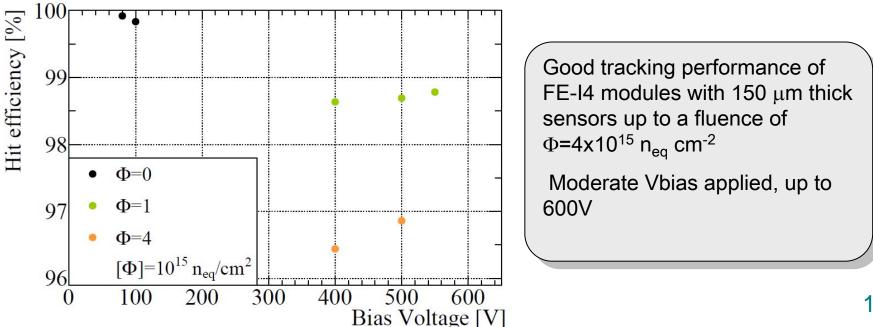

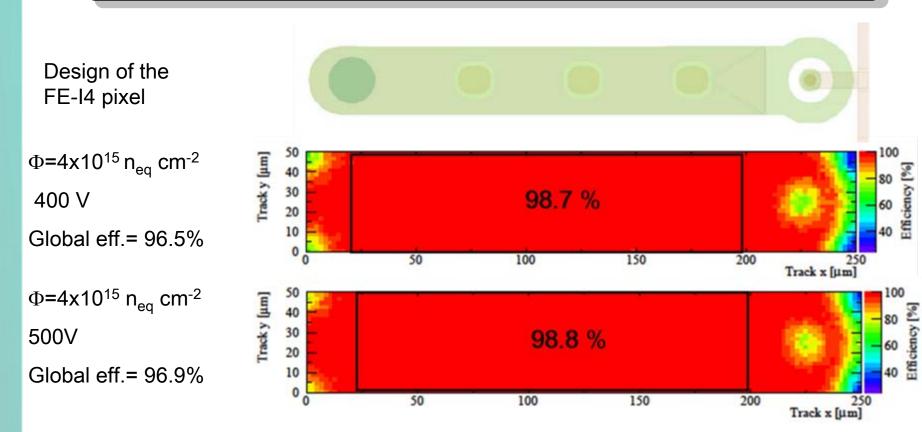

## **Test-beam results for FE-I4 modules**

□ Test-beams with EUDET telescope

□ 120 GeV pions at CERN-SPS and 5-6 GeV/c electrons at DESY

□ Many thanks to the PPS test-beam crew

S. Altenheiner, M. Backhaus, M. Bomben, K. Dette, M. Ellenburg, D. Forshaw, C. Gallrapp, M. George, I.~Gregor, J. Janssen, J. Jentzsch, R. Klingenberg, A. Kravchenko, T.Kubota, A.Macchiolo, T.Plümer, R.Nagai, B.Ristic, I. Rubinskiy, A. Rummler, Y.Takubo, S.Terzo, K. Toms, R. Wang, Y. Unno, P. Weigell, J. Weingarten

Hit efficiency of the module projected in one single pixel cell, Eudet telescope, 120 GeV pions at CERN-SPS

$\square$  Main loss of efficiency in the bias dot and in the bias rail  $\rightarrow$  problem is relevant only for perpendicular tracks, as in this case

## MPP 3D R&D Program: Through Silicon Vias

□ TSV etched in the read-out chip on the front-side on every wire bonding pad of the FE-I3 chip to route signal and services to the ASIC backside

- ASIC thinned to 60 µm

- thin sensors /ASIC interconnection using SLID

#### Processing sequence:

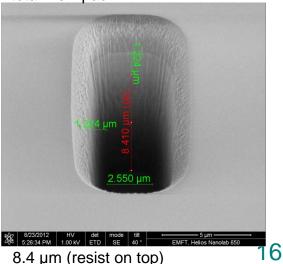

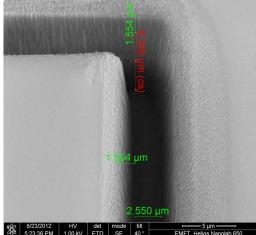

- Via-etching in Bosch-process, TSV cross-section of  $3x10 \ \mu m^2$

- insulation with TEOS (low T)

- filling of vias with Tungsten

- attachment to handle-wafer on the top side and thinning to desired thickness of chip ~ 60  $\mu m$

- redistribution layer on the backside

- SLID-interconnection to sensor wafer.

## MPP 3D R&D Program: Through Silicon Vias

Processing status on the first hot wafer: etching of the dielectric layers accomplished

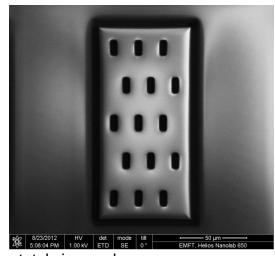

total view pad array & test field

total view pad array

total view pad

Very narrow TSV allows for their possible use to connect every single pixel

8.34 µm (resist on top)

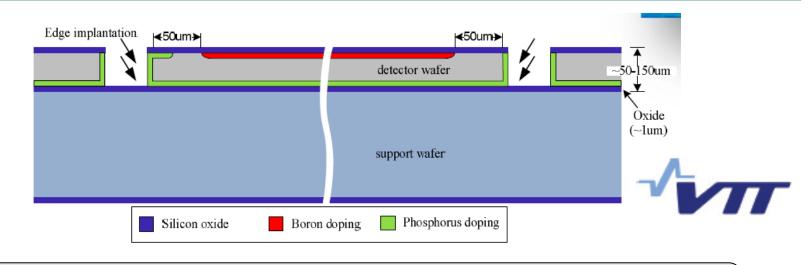

## Active edges with planar n-in-p sensors

#### n-in-p pixels at VTT: active edge process with back-side implantation extended to the edges

See J. Kalliopuska talk "Results of a Multi Project Wafer Process of Edgeless Silicon Pixel Detectors"

Multi-project run at VTT including ATLAS FE-I3 and FE-I4 n-in-p pixel sensors with different edge design

□ 100  $\mu$ m and 200  $\mu$ m active thickness  $\rightarrow$ together with the active edges makes these sensors very attractive candidates for the inner layers in Phase II

- □ p-spray isolation method transferred from HLL to VTT

- □ Flip-chipping performed at VTT after bump-deposition on the FE-I4 chip wafers

September 2012

A. Macchiolo, PIXEXL2012 Conference, Inawashiro, 7

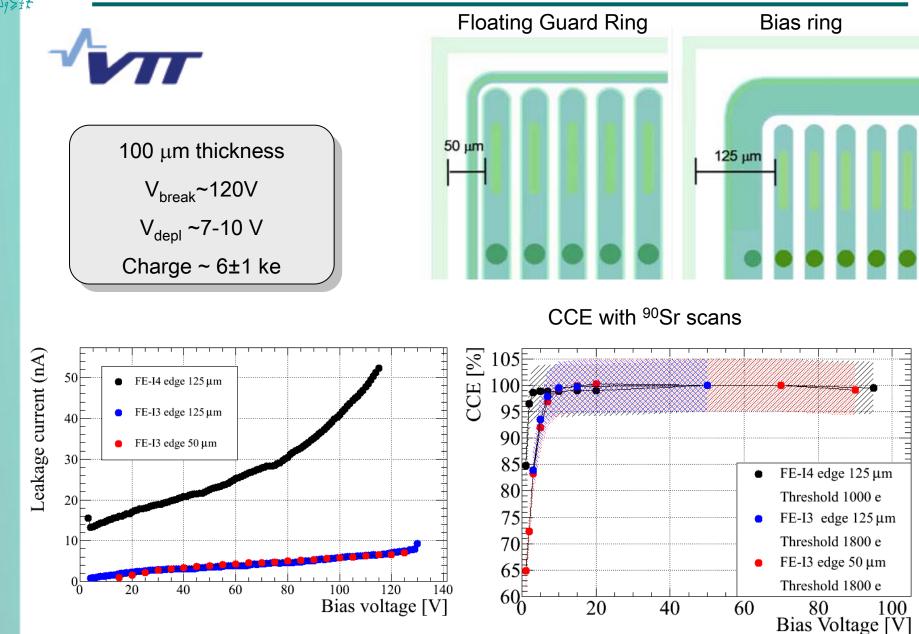

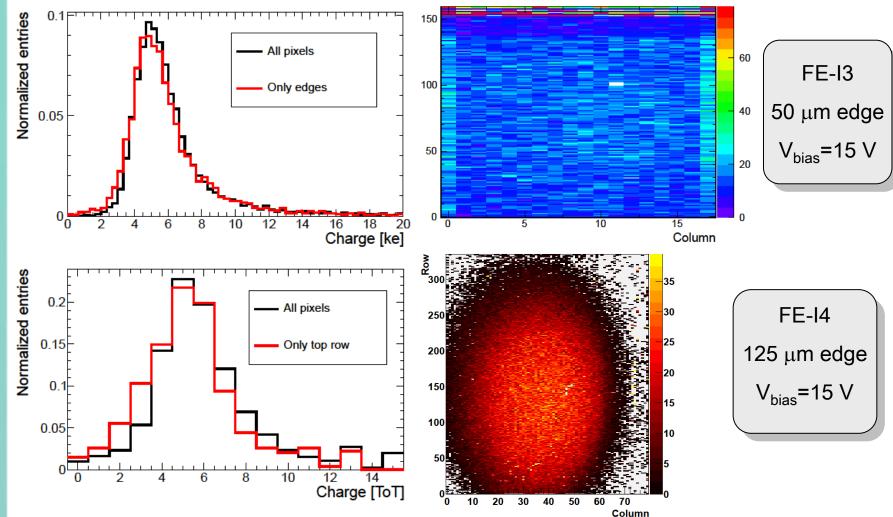

## Active edges with planar n-in-p sensors

## Active edges with planar n-in-p sensors

Edge pixels show the same charge collection properties as the central ones

Plan to study the hit reconstruction efficiency at the edges with test-beam before and after irradiation

□ Good performance of pixel detectors with thin n-in-p sensors irradiated up to a fluence of  $\Phi$ =10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>, demonstrated in measurements with radioactive sources and beam tests.

□ Low thresholds achievable with FE-I4 chip and thin n-in-p pixels help to obtain good tracking performance also with small signals.

□ SLID interconnection technology proved to be stable after irradiation, up to  $\Phi$ =10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>. Plans to extend the tests with further runs on FE-I3 and FE-I4 wafers.

□ TSV with narrow cross-sections are being etched on FE-I3 wafers. If applied to a TSV compatible chip, this technique will allow for four-side buttable modules.

□ First active edge pixels, 100  $\mu$ m thick, interconnected to FE-I3 and FE-I4 chips. Preliminary tests show good behavior of the modules down to an inactive side of 50  $\mu$ m → very thin pixels with active edges represent very good candidates for the inner layers of the pixel detectors at HL-LHC.

A. Macchiolo, PIXEXL2012 Conference, Inawashiro, 7 September 2012

## **Back-up slides**

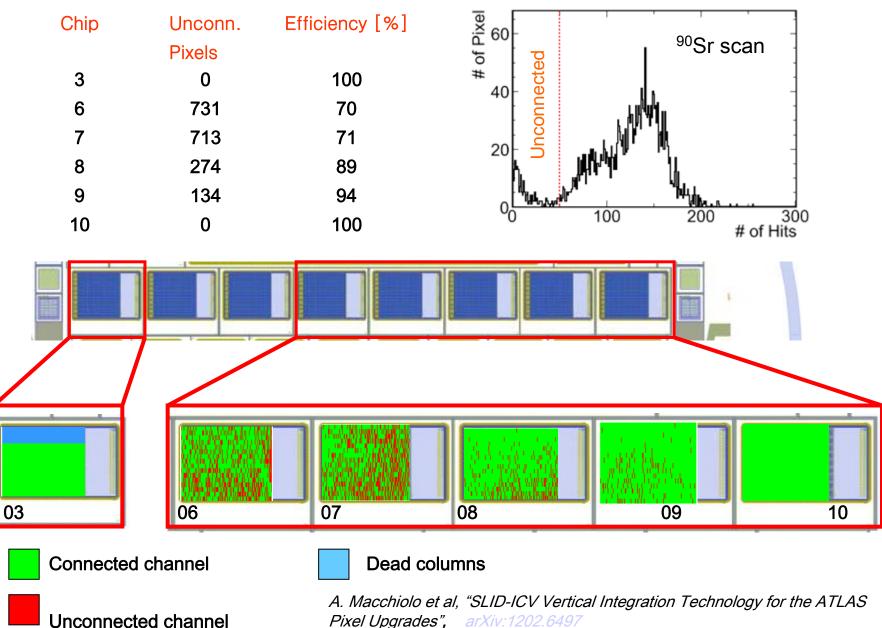

## **Overview of SLID interconnection efficiency**

Pixel Upgrades", arXiv:1202.6497

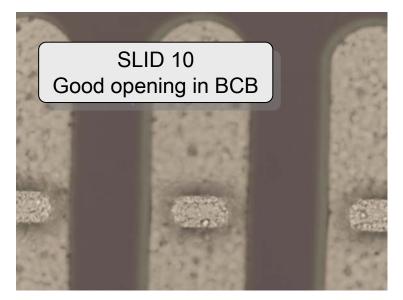

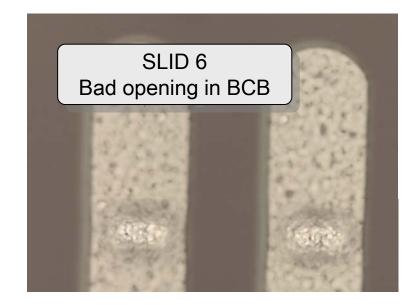

### Problem with contact opening in BCB passivation

BCB (BenzoCycloButhene) passivation deposited to planarize the sensor surface before Cu and Sn electroplating

Badly defined BCB contact openings observed in 2 sensor wafers not yet electroplated → pattern fully compatible with the distribution of unconnected channels in the modules Unconnected channels are not an intrinsic SLID problem!

Problem cured for the remaining wafers with a descum process of BCB using a  $SF_6$  plasma at IZM

## FE-I4 module charge-sharing