# Progress of SOI Pixel Process

Sep. 3, 2012 PIXEL2012@Inawashiro Yasuo Arai, KEK yasuo.arai@kek.jp http://rd.kek.jp/project/soi/

# OUTLINE

# Introduction of SOI Technology

- •Recent Progress

- •Summary

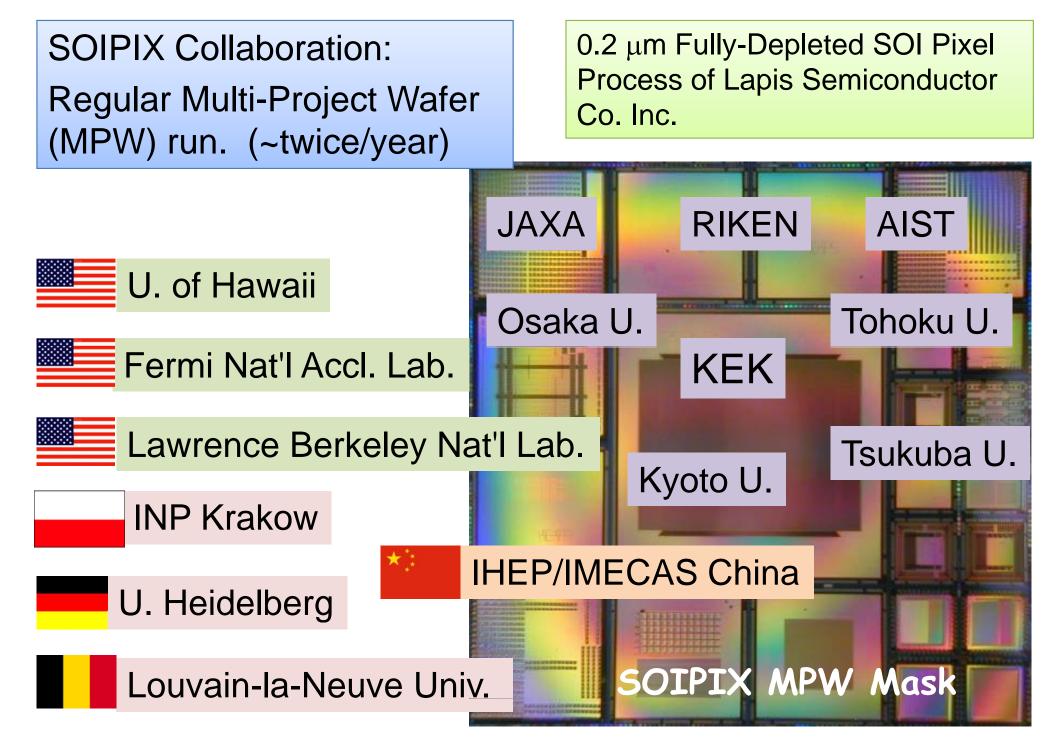

### KEK-Lapis SOI Pixel Related Presentations

Sep. 3. Session 3:

"Development and Deployment Status of X-ray 2D Detector for SACLA", T. HATSUI.

Sep. 4, Session 4:

- "High-Resolution Monolithic Pixel Detectors in SOI Technology", T. MIYOSHI.

- "A thin fully-depleted monolithic pixel sensor in Silicon On Insulator technology", S. MATTIAZZO.

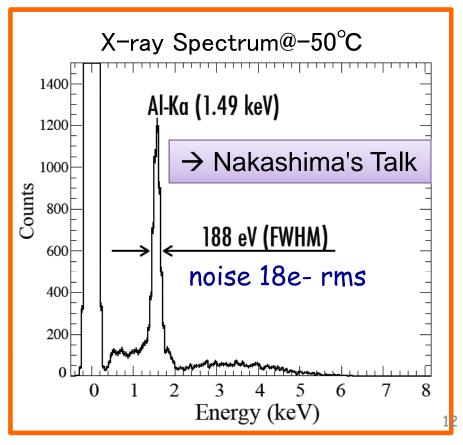

- "Development and characterization of the latest X-ray SOI pixel sensor for a future astronomical mission", S. NAKASHIMA

- "3D Integration for SOI Pixel Detector", M. MOTOYOSHI.

Sep. 6, Session 6

- "Monolithic Active Pixel Matrix with Binary Counters (MAMBO) ASIC, using a nested well structure to decouple the detector from the electronics", F. KHALID.

- "Test of TRAPPISTe Monolithic Detector System", L. SOUNG YEE.

Poster :

- "High Resolution X-ray Imaging Sensor with SOI Technology", A. TAKEDA.

- "Development of the Pixel OR SOI Detector for High Energy Physics Experiments", Y. ONO.

- "Characterization of SOI Monolithic Detector System", R. ALVAREZ.

- "A study on the dynamic range of integrating SOI chips", Lu YUNPENG

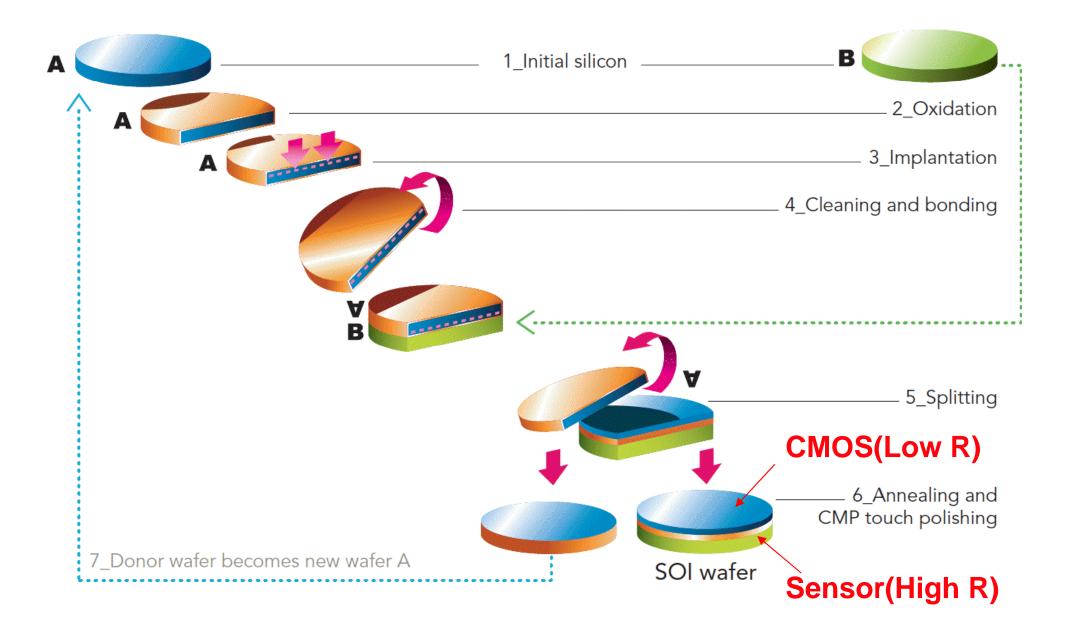

#### SOI Wafer Production (Smart Cut by SOITEC)

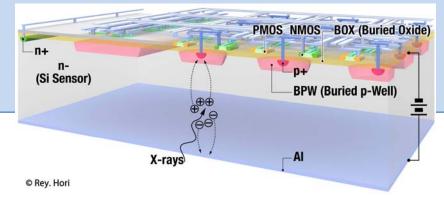

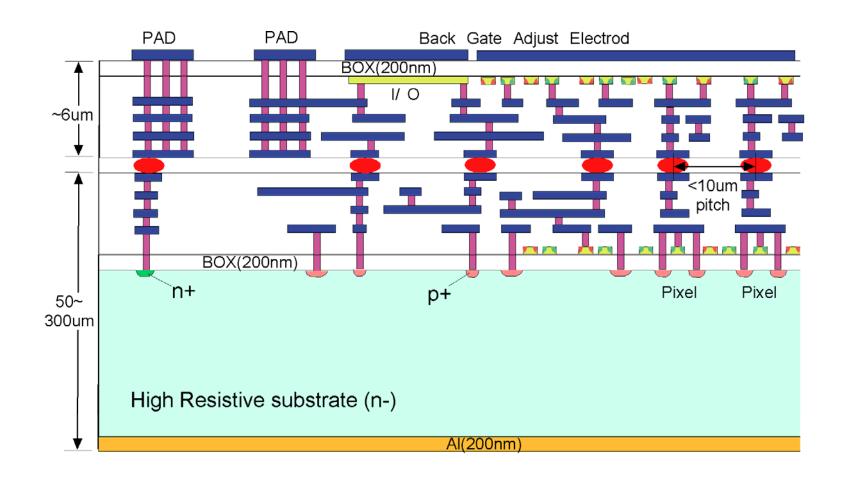

# SOI Pixel Detector (SOIPIX)

Monolithic Detector having fine resolution of silicon and data processing power of CMOS LSI by using Silicon-On-Insulator (SOI) Technology.

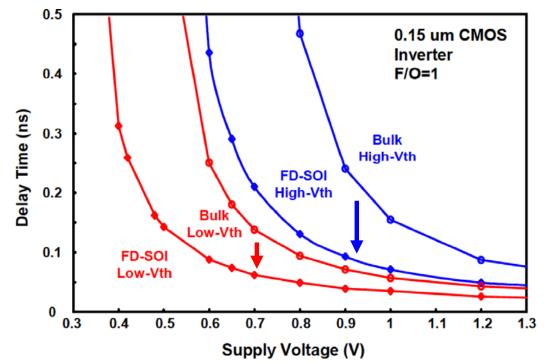

# SOI Performance : Smaller Junction Capacitance Bulk SOI

Cj is 1/10 of Bulk technology. Gate Capacitance is 30-40% Lower.

High Speed / Low Power

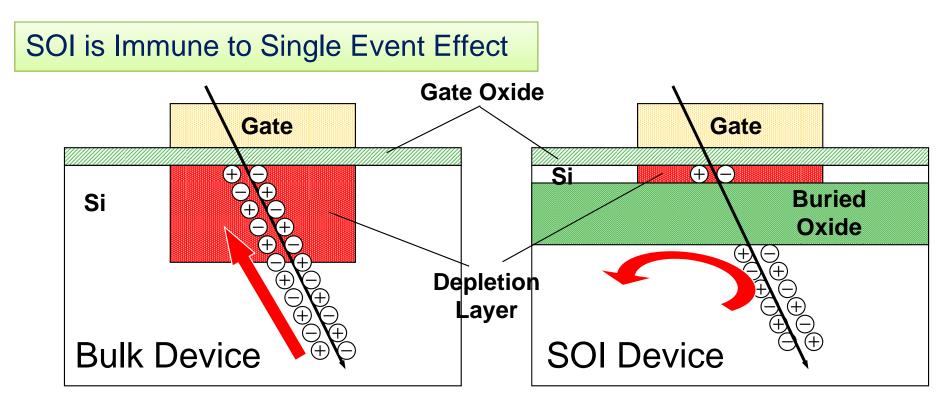

#### **Radiation Tolerance**

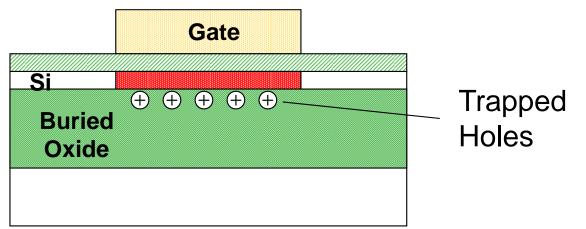

But not necessary strong to Total Ionization Dose due to thick BOX layer

This must be remedy for the application under high radiation environment.

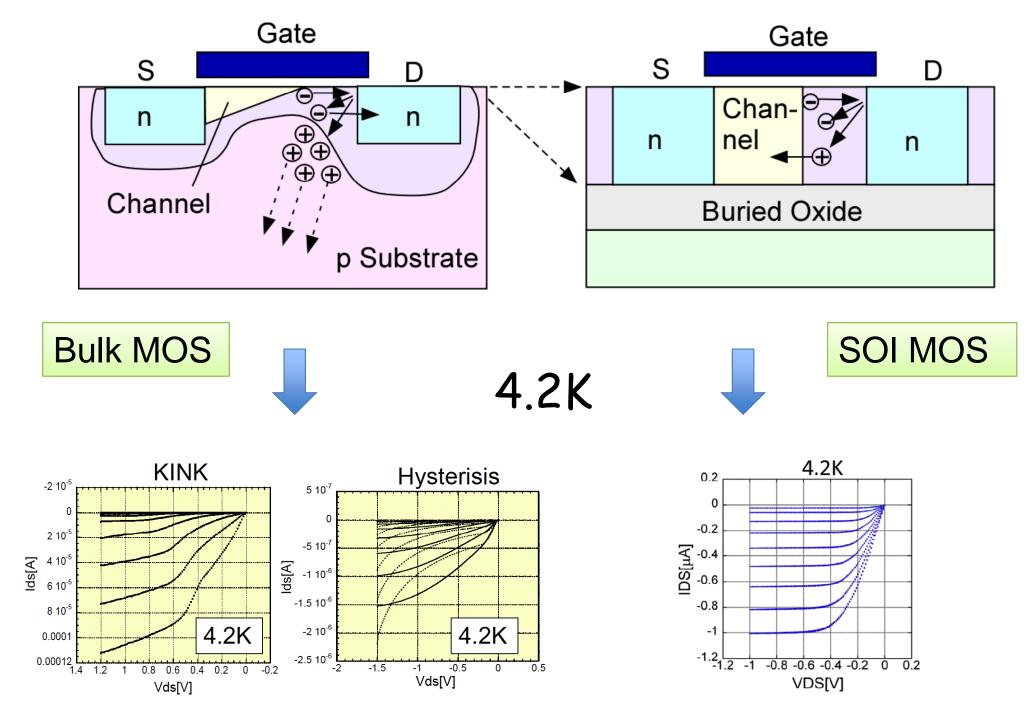

#### Operation at Cryogenic Temperature

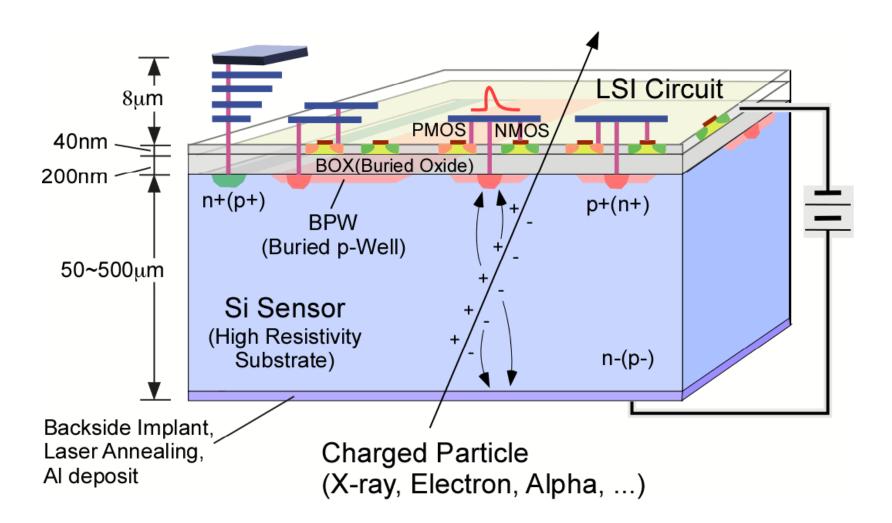

# Feature of SOI Pixel Detector

- No mechanical bonding. Fabricated with semiconductor process only, so high reliability, low cost are expected.

- Fully depleted thick sensing region with Low sense node capacitance.

- On Pixel processing with CMOS transistors.

- Can be operated in wide temperature (4K-570K) range, and has low single event cross section.

- Based on Industry Standard Technology.

#### <u>Lapis (\*)</u> Semiconductor 0.2 $\mu$ m FD-SOI Pixel Process

| Process             | 0.2µm Low-Leakage Fully-Depleted SOI CMOS<br>1 Poly, 5 Metal layers.<br>MIM Capacitor (1.5 fF/um <sup>2</sup> ), DMOS<br>Core (I/O) Voltage = 1.8 (3.3) V                           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

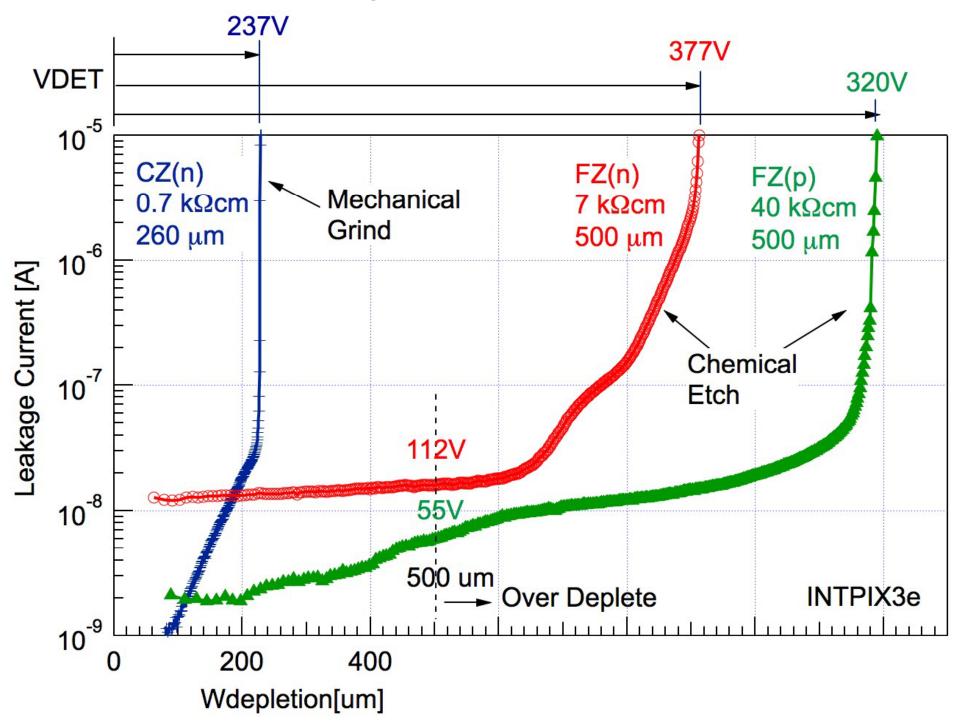

| SOI<br>wafer        | Diameter: 200 mmφ, 720 μm thick<br>Top Si : Cz, ~18 Ω-cm, p-type, ~40 nm thick<br>Buried Oxide: 200 nm thick<br>Handle wafer: Cz (n) ~700 Ω-cm,<br>FZ(n) ~7k Ω-cm, FZ(p) ~25 k Ω-cm |

| Backside<br>process | Mechanical Grind, Chemical Etching, Back side<br>Implant, Laser Annealing and Al plating                                                                                            |

(\*) Former OKI Semiconductor Co. Ltd.

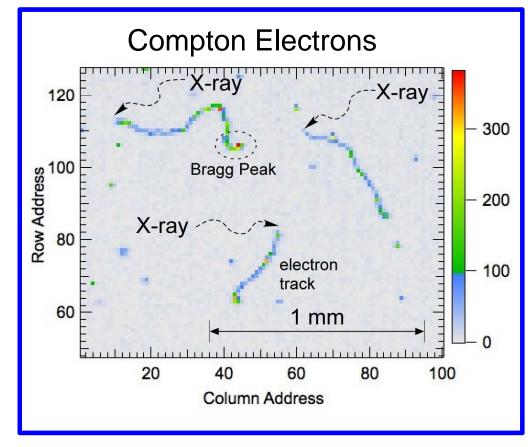

#### **Examples of SOIPIX Measurements**

# Recent Progress

#### High Resistive wafers

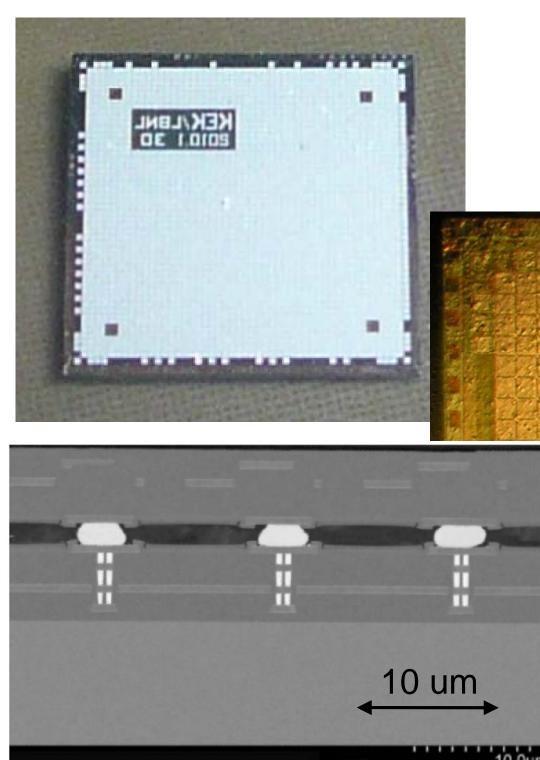

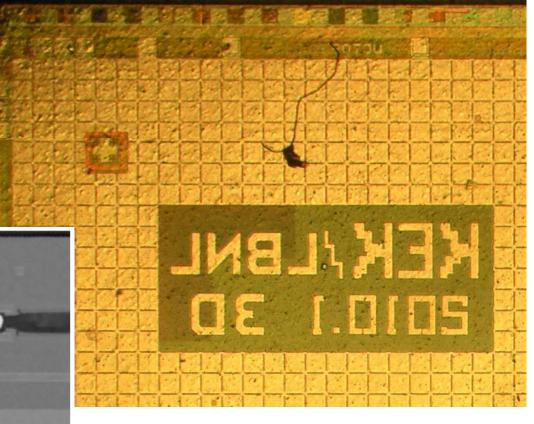

#### Vertical (3D) Integration

3D vertical Integration technique is expected to play an important role in future high performance pixel detector. We have made 3D test chips. These chips were bonded with  $\mu$ -bump technology (~5 um pitch) of T-micro Co. Ltd.

#### SOI 3D Bonded Chip

1<sup>st</sup> SOI 3D Sensor

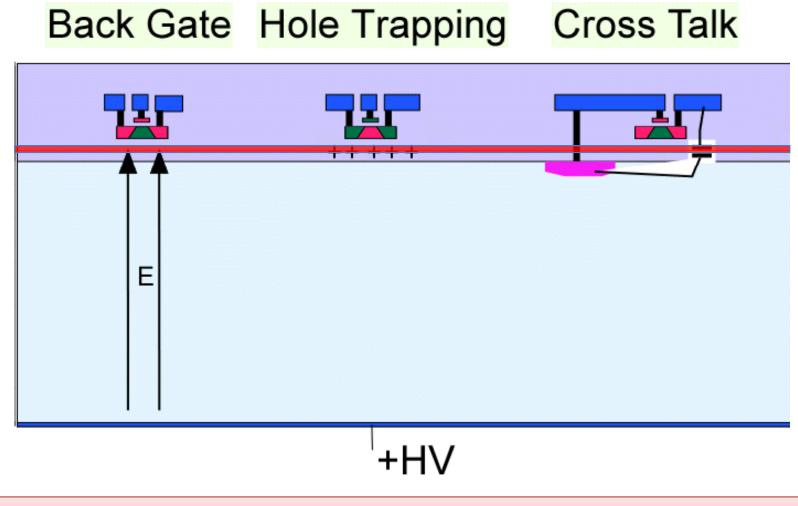

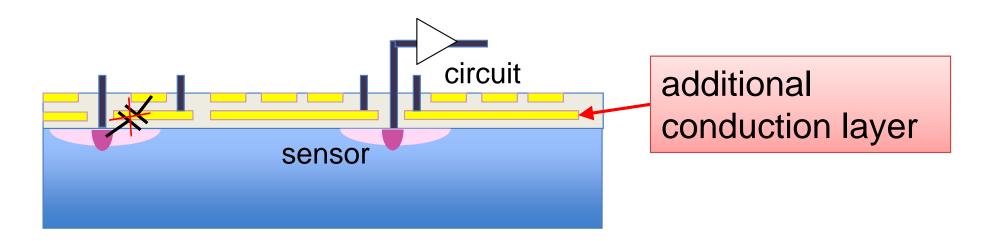

# Isuues in SOI Pixel

Sensor and Electronics are located very near. This cause ...

We need additional back-plane to suppress these effects.

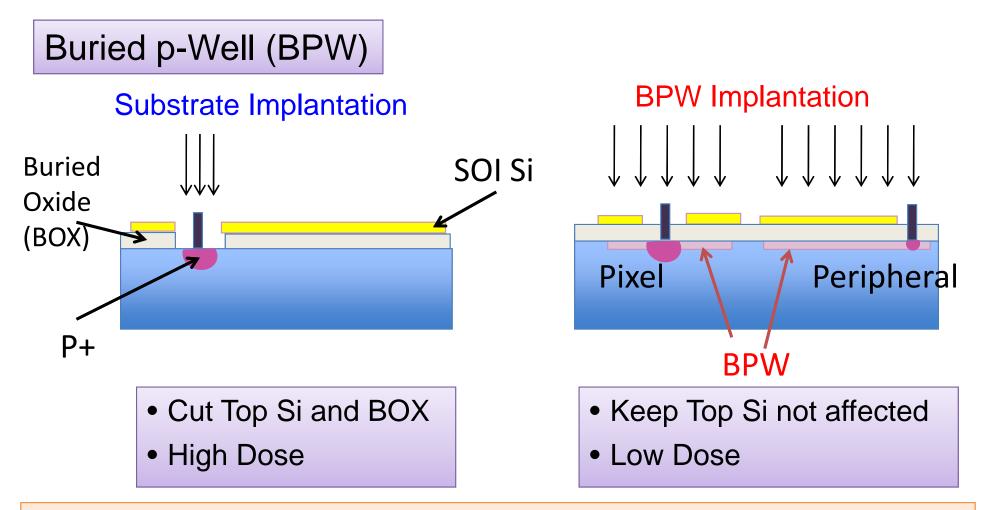

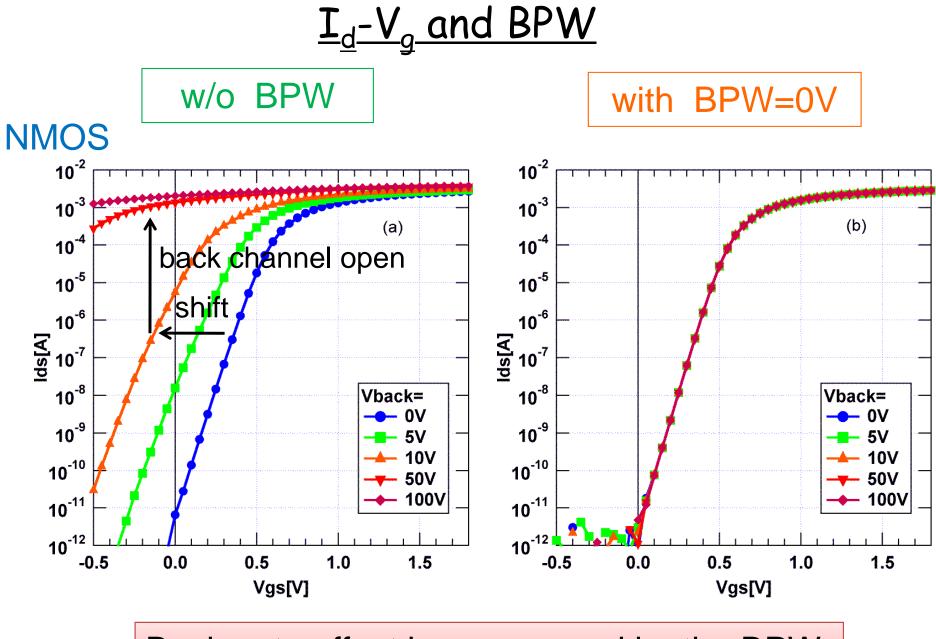

- Suppress the **Back Gate Effect**.

- Shrink pixel size without loosing sensitive area.

- Increase break down voltage with low dose region.

- Less electric field in the BOX which improve radiation hardness.

Back gate effect is suppressed by the BPW.

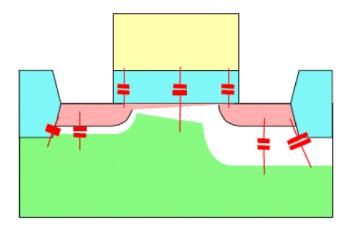

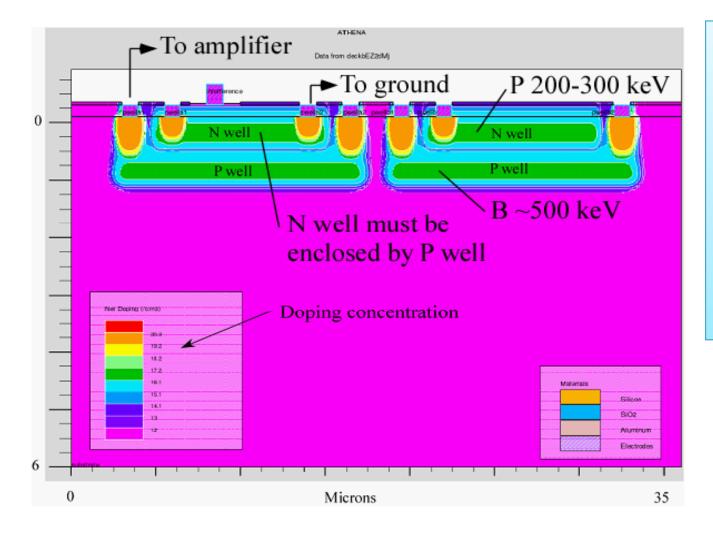

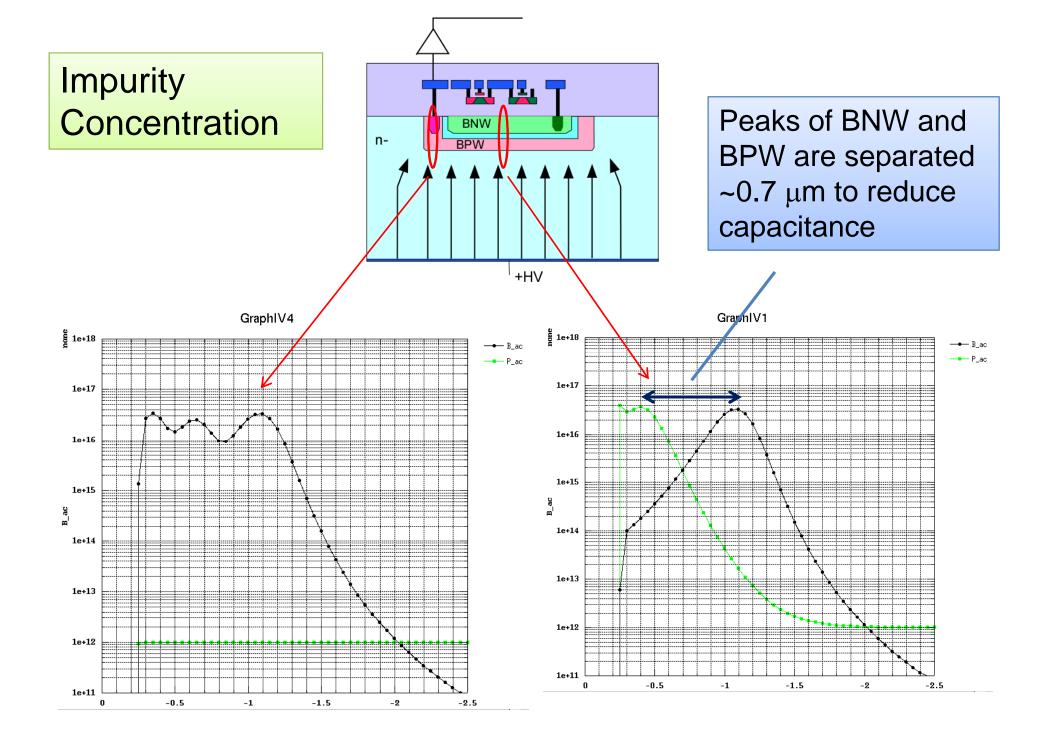

# **Nested Well Structure**

#### → Fahim Kahlid's Talk

- Signal is collected with the deep Buried P-well.

- Back gate and Cross Talk are shielded with the Buried N-well.

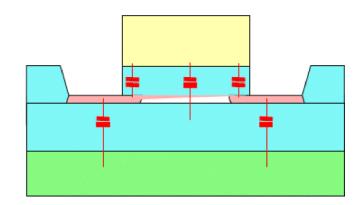

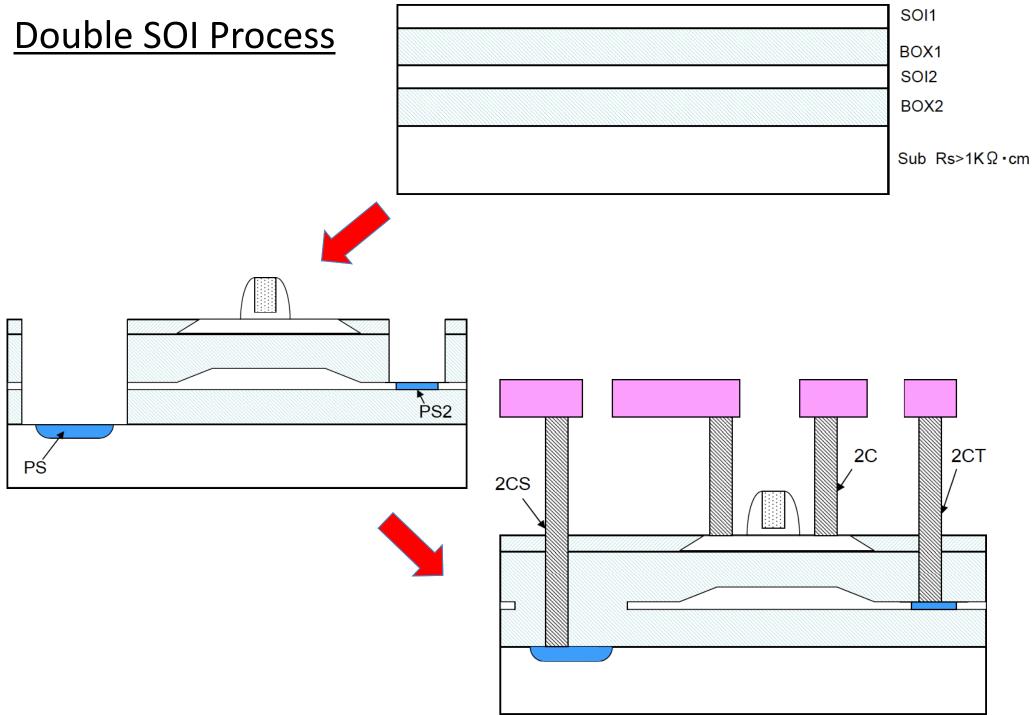

# **Double SOI Wafer**

- Shield transistors from bottom electric field

- Compensate electric field generated by the trapped hole in the BOX.

- Reduce crosstalk between sensors and circuits.

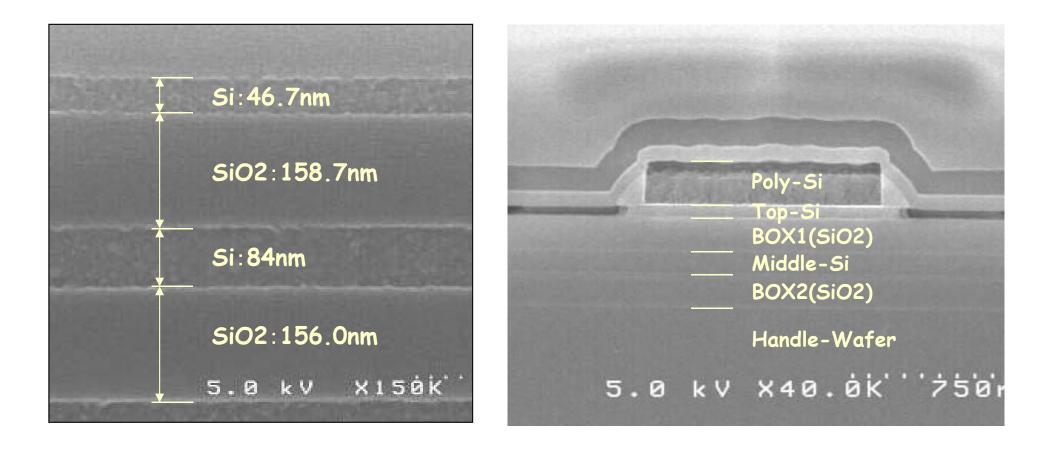

# <u>SEM View of Double-SOI</u> (post Field-Anneal)

(Thickness of Si & SiO2 layers are not yet optimized)

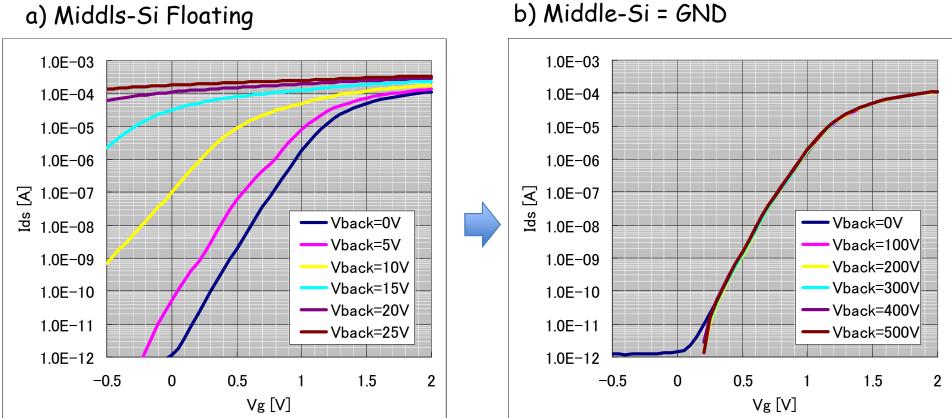

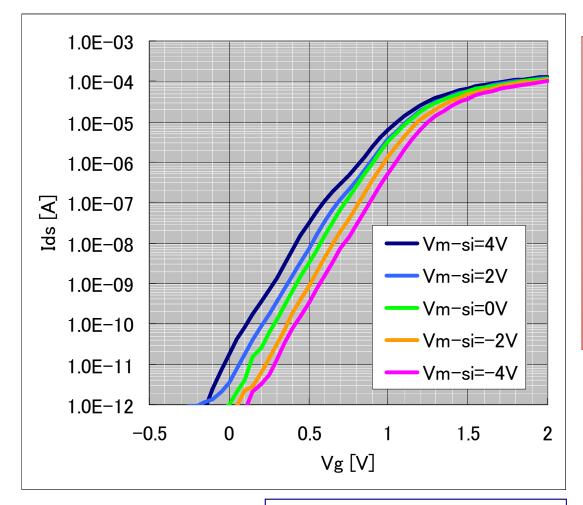

#### Suppression of Back-Gate Effect with Middle-Si layer

a) Middls-Si Floating

Back-Gate Effect is fully suppressed with the Middle Si Layer of fixed voltage.

Nch Core Normal-Vt L/W = 0.2/5.0um Vd=0.1V

#### <u>Trapped Charge Compensation (Threshold</u> <u>Control)with Middle-Si Layer</u>

Nch Core Normal-Vt L / W = 0.2 / 5.0 um Vd=0.1V, Vback: floating Threshold voltage of a transistor is controlled with the bias voltege of the Middle-Si layer. This indicate effects of the trapped charge in the BOX can be compensated with the bias voltage.

#### Summary

- SOI technology has many good features; low power, low variability, large operating temperature range, no latch up..., and Industries are moving to extremely thin SOI.

- SOIPIX is monolithic detector, and many of the technical problems initially existed are solved.

- We have ~twice/year regular MPW runs with increasing no. of users.

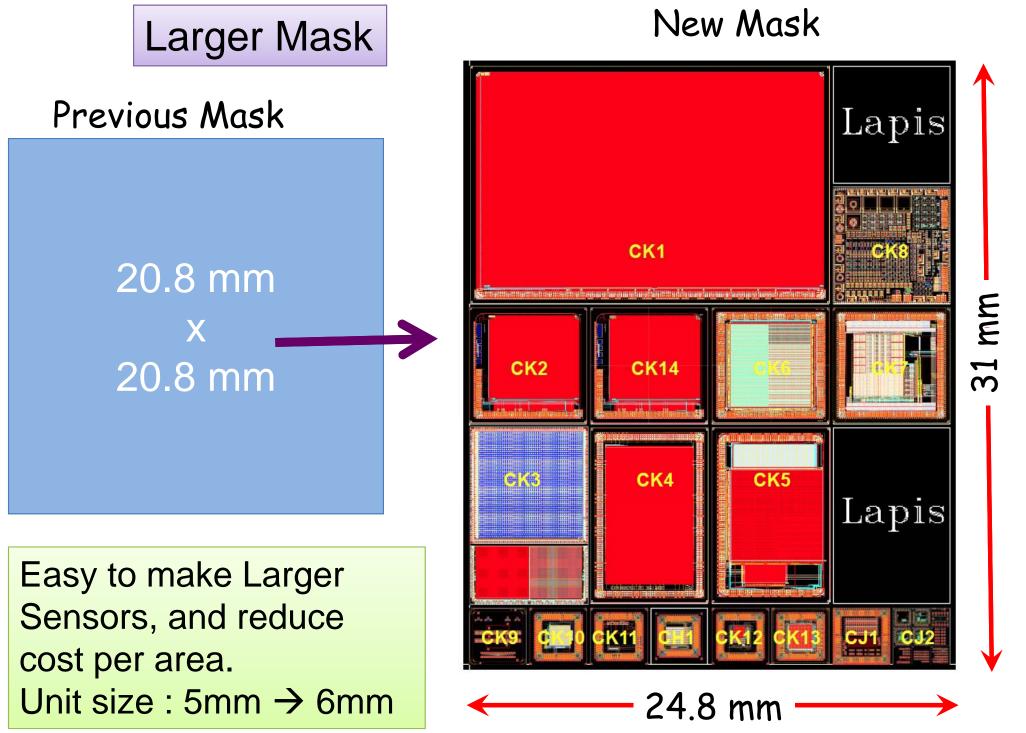

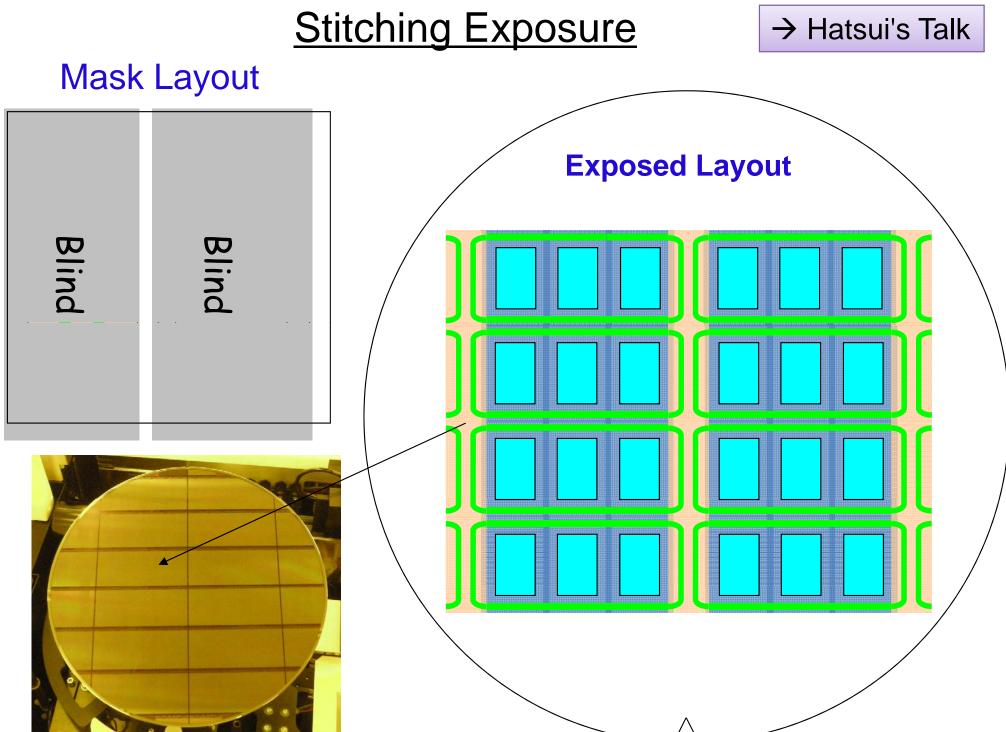

- The process technology is still progressing; Higher resistivity wafer, Nested well structure, Larger mask size, Stitching, etc. ...

- Double SOI wafer is successfully processed.

- We welcome new users to the SOI pixel process.