#### Evaluation of novel n<sup>+</sup>-in-p pixel and strip sensors for very high radiation environment

Y. Unno<sup>a</sup>, S. Mitsui<sup>a</sup>, R. Hori<sup>a</sup>, R. Nagai<sup>g</sup>, O. Jinnouchi<sup>g</sup>, Y. Takahashi<sup>h</sup>,

K. Hara<sup>h</sup>, S. Kamada<sup>b</sup>, K. Yamamura<sup>b</sup>, A. Ishida<sup>b</sup>, M. Ishihara<sup>b</sup>, T. Inuzuka<sup>b</sup>,

Y. Ikegami<sup>a</sup>, Y. Takubo<sup>a</sup>, S. Terada<sup>a</sup>, J. Tojo<sup>a</sup>, R. Takashima<sup>c</sup>, I. Nakano<sup>d</sup>,

K. Hanagaki<sup>e</sup>, N. Kimura<sup>i</sup>, K. Yorita<sup>i</sup>

<sup>a</sup>High Energy Accelerator Research Organization (KEK) and The Graduate University for Advanced Studies (SOKENDAI) <sup>b</sup>Hamamatsu Photonics K.K. <sup>c</sup>Department of Education, Kyoto University of Education <sup>d</sup>Department of Physics, Okayama University <sup>e</sup>Department of Physics, Osaka University <sup>g</sup>Department of Physics, Tokyo Institute of Technology <sup>h</sup>Institute of Pure and Applied Sciences, University of Tsukuba <sup>i</sup>Research Institute for Science and Engineering, Waseda University

Y.Unno, PIXEL2012 at Inawashiro, 2012/9/6

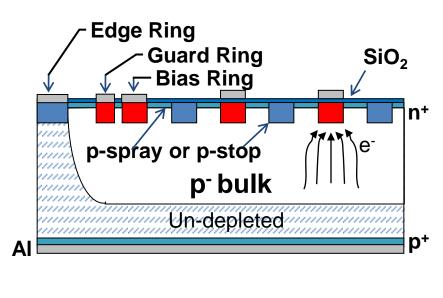

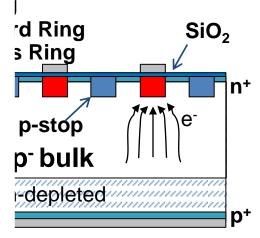

# n<sup>+</sup>-in-p Benefits and Issues

- Starting with "p-type" silicon, with n<sup>+</sup>readout, (n-in-p), has benefits:

- Tolerance against radiation (bulk) damage

- Depletion from the readout side always

- Good signal even partially depleted, initially or heavily damaged towards the end of life

- Collecting faster carrier, electrons

- Larger signal, reduced charge trapping

- Single-sided process

- Cheaper than double-side process

- More foundries and available capacity, world-wide

- Easier handling/testing

- due to more robust back-side than patterned

- Wafer availability in 6-in. with higher resistivity

- Specific requirements

- N-side Isolation

- against electron-layer in the silicon surface attracted to the "positive" charges in the Si-SiO<sub>2</sub> interface

- p-stop or p-spray

- Bias structure

- if AC-coupling readout, e.g., strip sensors

- if requesting testability in DC-coupling, e.g., pixel sensors

- HV protection

- between the front edge and the ASIC, in hybrid pixel modules

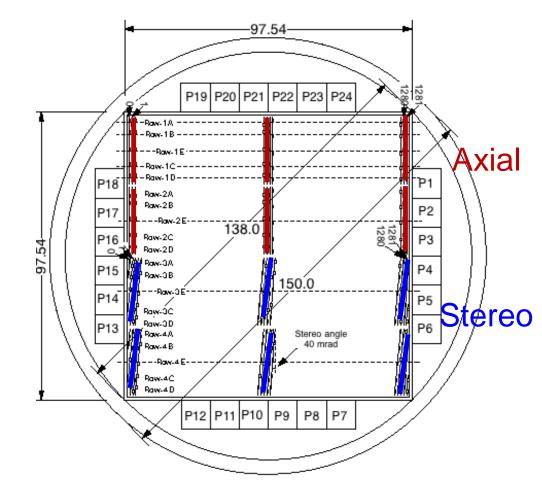

# Novel n<sup>+</sup>-in-p Strip Sensors

- Collaboration of ATLAS with Hamamatsu Photonics K.K. (HPK)

- Silicon wafers

- 6 in., p-type, FZ <100>, 320 μm thick wafers

- >3 k $\Omega$  cm wafers available industrially

- Strip sensors

- large area

- 9.75x9.75 cm<sup>2</sup> sensors

- 4 segments

- 2 axial, 2 stereo

- 1280 strip each, 74.5 mm pitch

- Miniature sensors

- 1x1 cm<sup>2</sup> for irradiation studies

- Y. Unno, et. al., Nucl. Inst.

Meth. A636 (2011) S24-S30

- And the poster (ID=8)

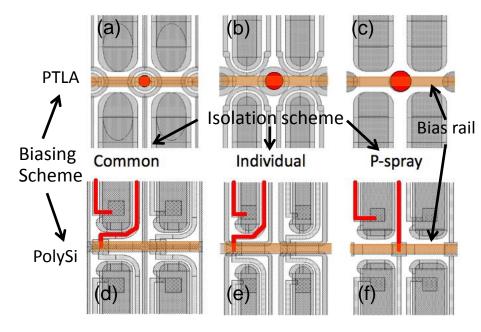

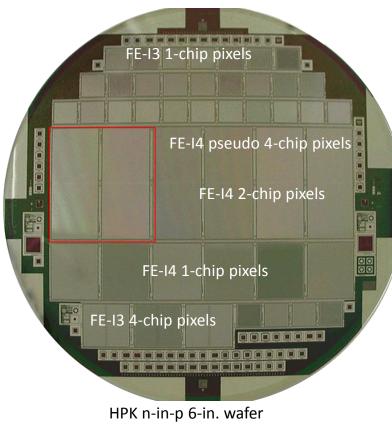

# Novel n<sup>+</sup>-in-p Pixel Sensors

- n-in-p 6-in. wafer process in HPK

- ATLAS FE-I3 and FE-I4 pixel sensors

- Isolation structures

- p-stop (common, individual) or p-spray

- Biasing structures

- Punth-thru dot at 4-corner (PTLA) or PolySi resister

- "Bias rail" is a metal over insulator, no implant underneath.

- No electrode in the silicon, other than the bias "dot"

- Y. Unno et al., Nucl. Instr. Meth. A650 (2011) 129–135

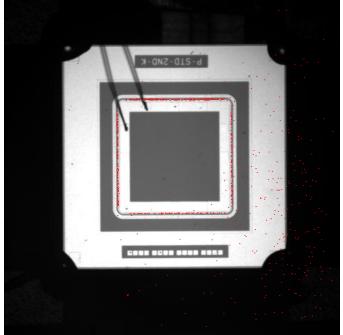

FE-I3 (~1cm ) FE-I4 (~2cm )

#### Thinned sensors

- Finishing 320 μm wafer process first

- Thinning the wafers to 150  $\mu$ m

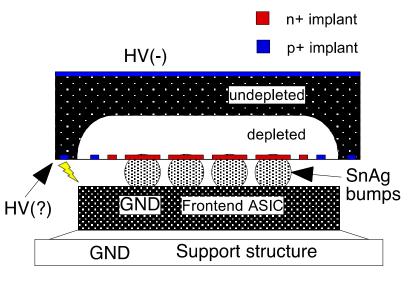

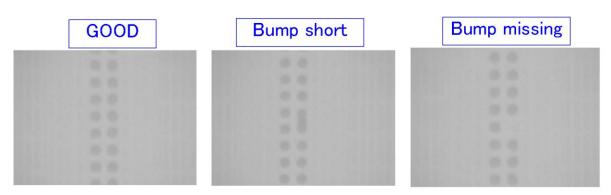

## Pixel modules - Bumpbonding

- Latest achievement

- Lead-free bumps (SnAg)

- 4 cm x 4 cm pixel sensor

- 4x FE-I4 (2 cm x 2 cm) readout ASIC's

- 80 col.\*336 row\*4 chips =1M bumps

- A sample in the HPK display table

ASIC side

Most of bumps( >about 99.8%) look "GOOD". But, some of bumps have short or missing. We are trying to improve the yield.

Sensor side

# The goals of R&D

- Application

- For the very high radiation environment, e.g.,

- High-Luminosity LHC which aims to collect data of 3,000 fb<sup>-1</sup>

- Presently running LHC goal is 300 fb<sup>-1</sup>

- Fluences of hadronic particles in HL-LHC

- Pixels: ~2x10<sup>16</sup> 1-MeV neutron-equivalent (*neq*)/cm<sup>2</sup>

- Strips: ~1x10<sup>15</sup> neq/cm<sup>2</sup>

- Understanding of the radiation effect, specially in the surface, after the studies of irradiated sample:

- Surface resistance Interstrip resistance

- Punch-thru onset voltage PTP structures

- Effect of the surface potential Bias rail, Bias-PTP gate

- Potential of the p-stop

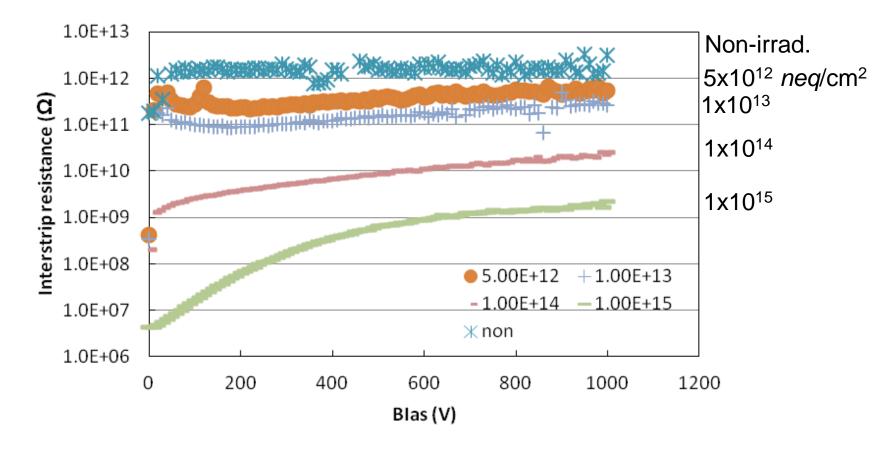

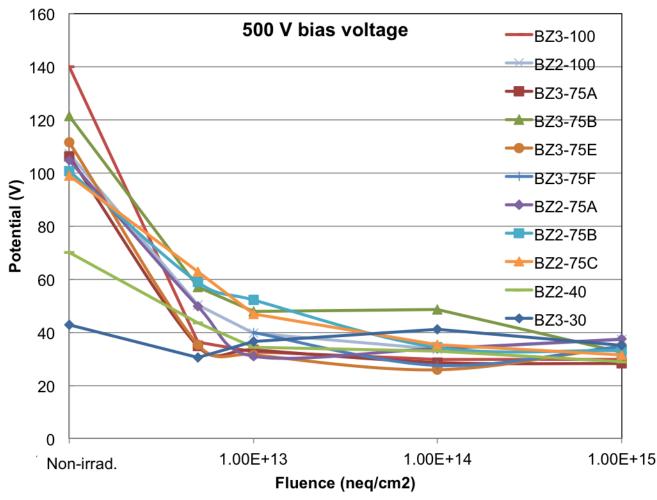

#### Interstrip Resistance

- Interstrip resistance

- decreases with fluence

- increases with bias voltage

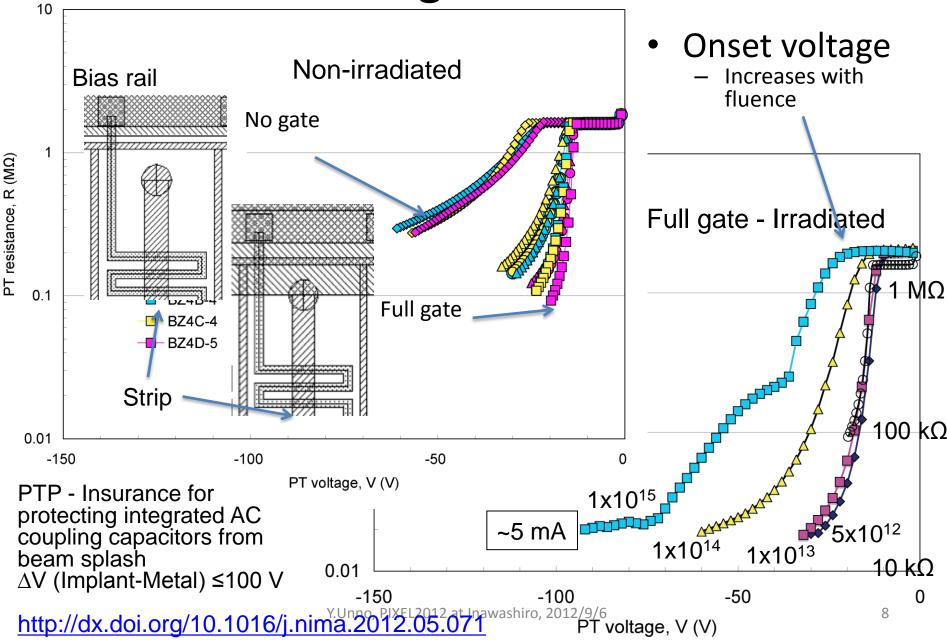

#### PTP Onset Voltage – after irradiation

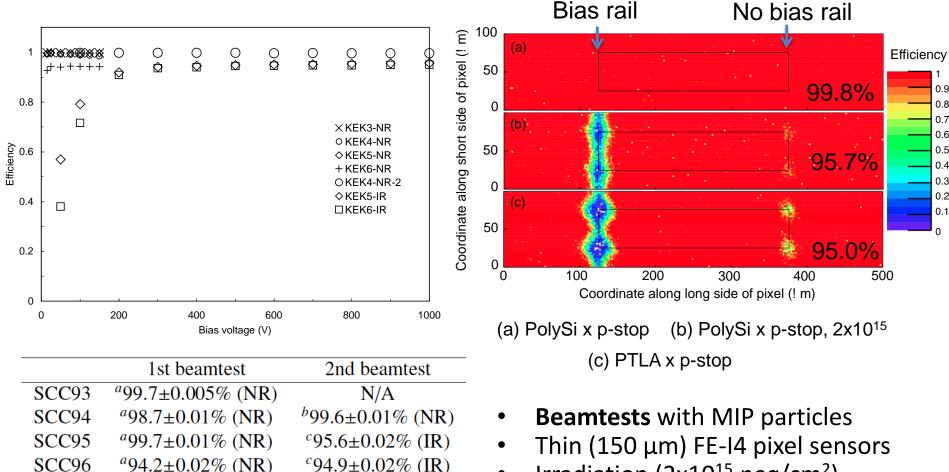

#### Bias Rail Effect – after irradiation

Weighted averages and errors of:  ${}^{a}(100, 125, 150 \text{ V}), {}^{b}(100, 200, 300 \text{ V}),$  ${}^{c}(800, 900, 1000 \text{ V})$

Irradiation (2x10<sup>15</sup> neq/cm<sup>2</sup>)

Successful operation up to 1000 V

Reduction of efficiency specially underneath the bias rail

http://dx.doi.org/10.1016/j.nima.2012.04.081

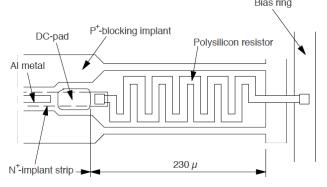

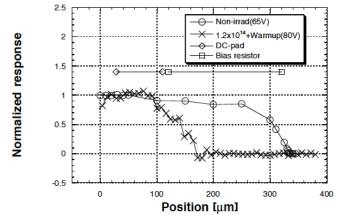

#### Insensitive area - after Irradiation

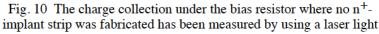

Fig. 9 Structure around the polysilicon bias resistor of the n-side.

The n<sup>+</sup>-implant strip ends at the DC-pad; no n<sup>+</sup>-implant strip was designed under the bias resistor in this detector.

(1064 nm). The laser response was obtained for non-irradiated (circle) and the irradiated (cross) detectors. The areas of the bias resistance (square) and the DC-pad (diamond) are shown together.

Y. Unno et al., IEEE TNS 44 (1997) 736-742

Underneath the gate (metal) seems insensitive after irradiation

20 µm width

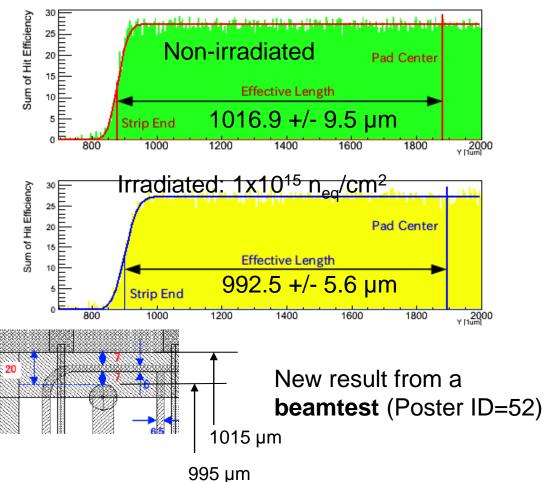

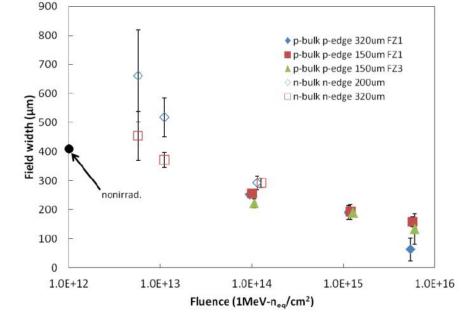

# Sensor Edge – Field Width

Figure 5: Fluence dependence of field width hold up to 1000 V. http://dx.doi.org/10.1016/j.nima.2012.05.071

- Field width

- Area with no implantation

- Required field width

- decreases as fluence increased

- Hot electron images confirm that

- the highest electric field is

- in the bias ring (n<sup>+</sup> implant)

- not in the edge ring (p<sup>+</sup> implant)

#### Potential of p-stop

- Wider the pitch, larger the potential

- Potential decreases and saturates as fluence increase

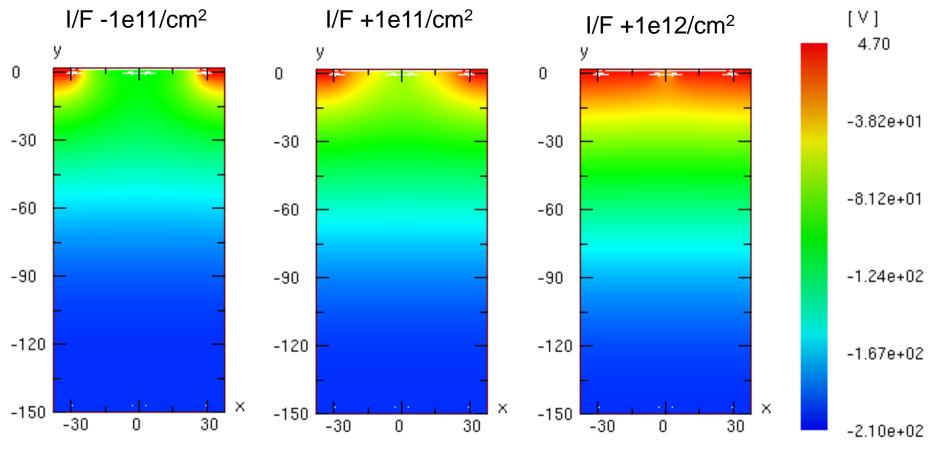

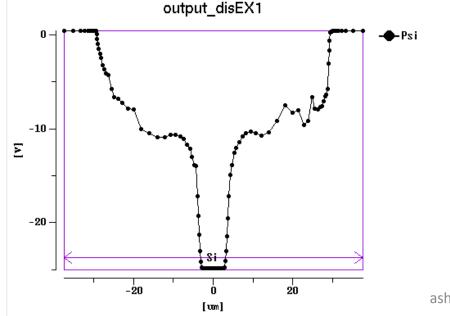

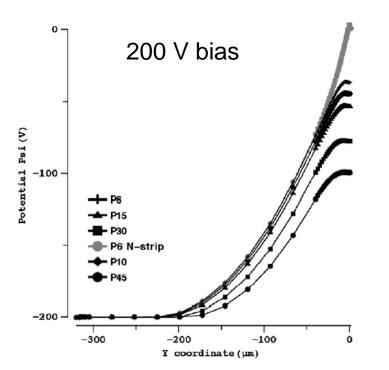

## P-stop Potential - TCAD

- TCAD model

- Thickness 150 μm, Bias voltage = 200 V

- Radiation damage in bulk Bulk resistivity is reduced by increasing the acceptor states, N<sub>eff</sub> ~ 1.4 x 10<sup>12</sup>/cm<sup>3</sup>, full depletion voltage of ~1 kV at 320 μm.

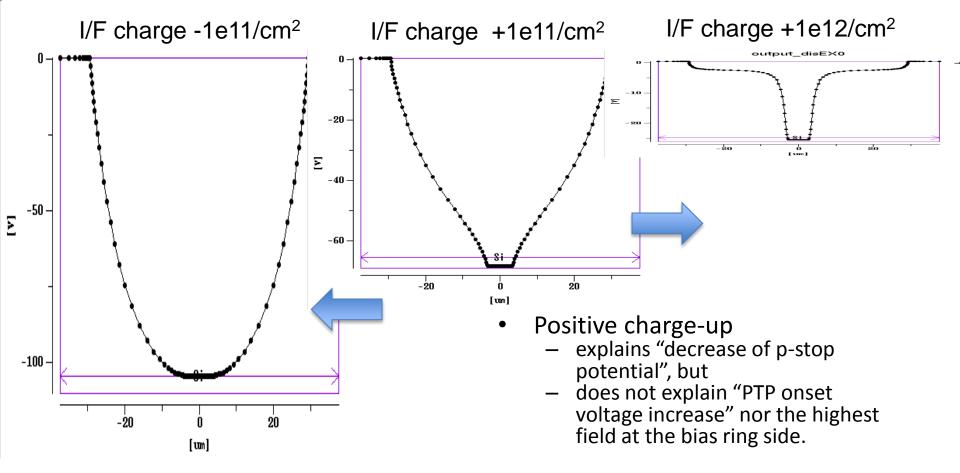

#### P-stop Potential - TCAD

- Negative charge-up

- does not explain "p-stop potential".

- explains "PTP onset voltage", hot spots at the bias ring.

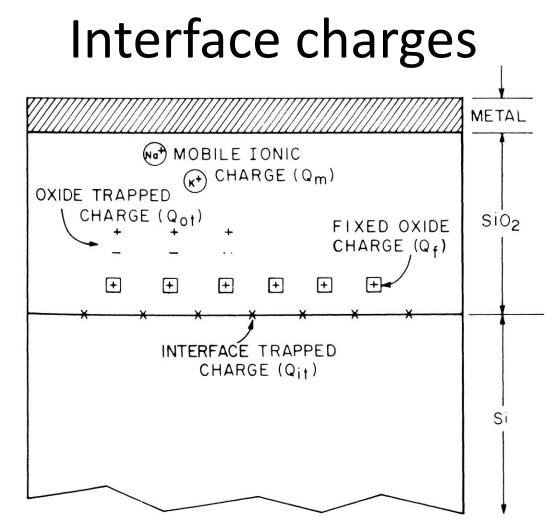

- Fixed oxide charge  $(Q_t)$  known to be "+"

- Interface trapped charge (Q<sub>it</sub>) can be "+" or "-"

- depending on the conditions

## Our explanation, backed with TCAD

- After irradiation,

- Primary factor is the increase of "+" charges, e.g., in the fixed oxide charge

- The evidences suggest that there is a secondary factor of increase of "-" charges in the "interface trapped charge".

- This may explain all observations.

- An example of TCAD...

... failed to converge, though.

## Summary

- Novel n<sup>+</sup>-in-p silicon strip and pixel sensors have been fabricated at HPK successfully.

- and lead-free bumpbonding as well, which makes one-stop fabrication of pixel detectors from the sensor to the module.

- Issues especially associated with the n<sup>+</sup>-in-p sensors were addressed.

- Isolation structures that are robust against the bias voltage up to 1000 V.

- We have accumulated a number of evidences on the surface damage, after irradiation, that we explain, backed by TCAD simulation,

- (1) Primary factor is "+" charge-up of, e.g., Fixed oxide charge, and

- (2) Secondary factor is "-" charge-up of "interface trapped charge".

#### **Backup slides**

#### P-stop Potential - TCAD

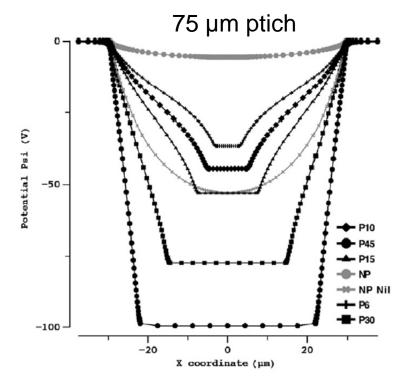

Fig. 7. Electric potential Psi charted vertically through silicon in common p-stop structures with p-stop widths of 6–45  $\mu m$  at the centre between the  $n^{*}$ -strips (P6–P45), and at the  $n^{*}$ -strip (P6 N-strip).

- Silicon wafer

- 320 μm, 3 kΩ cm (=4.7x10<sup>12</sup> cm<sup>-3</sup>)

- Condition: Non-irradiated

- Ratio of p-stop potential-to-bias voltage seems stable for the change of the bulk resistivity

- Y. Unno et al., Nucl. Instr. Meth. A636 (2011) S118–S124

Fig. 6. Electric potential Psi near the silicon surface between n<sup>+</sup>-strips in common p-stop structures with p-stop widths of 6–45 µm (P6–P45), together with references without p-stop and with interface trap charges of  $1\times10^{11}\,cm^{-2}$  (NP) and nil (NP Nil).