### Test of TRAPPISTe Monolithic Detector System

### Lawrence Soung Yee, P. Alvarez, E. Martin, E. Cortina, C. Ferrer

Université catholique de Louvain, Universitat Autonoma de Barcelona

September 6, 2012

**PIXEL 2012**

Test of TRAPPISTe

September 6, 2012 1 / 21

3

(日) (同) (三) (三)

### 1. Introduction

- 2. Monolithic Detector Approach: SOI Technology

- 3. TRAPPISTe Project

- 4. Measurements

- 5. Conclusion

< 🗗 🕨

3

# Section 1

## Introduction

**PIXEL 2012**

Test of TRAPPISTe

September 6, 2012 3 / 21

3

・ロト ・ 日 ・ ・ ヨ ・ ・ ヨ ・

### Silicon Detectors in Particle Physics

Particle Detector: device used to detect, track and identify subatomic particles. State-of-the-art high energy physics experiments use silicon detectors as innermost high-precision tracking device.

- In depleted silicon material, a MIP generates 24K  $e^-h^+$  pairs in  $300\mu m$

- $e^-h^+$  pairs separate in E-field and drift to electrodes

- Moving charges  $\rightarrow$  electric current pulse

- Small current signal is amplified and processed by read-out electronics

Objective: Drive to develop more precise, thinner and radiation hard detectors.

Monolithic pixel devices: Radiation sensor + charge amplifier + signal processing on single Si wafer.

▲□▶ ▲□▶ ▲□▶ ▲□▶ = ののの

## Section 2

# Monolithic Detector Approach: SOI Technology

**PIXEL 2012**

Test of TRAPPISTe

September 6, 2012 5 / 21

-

< 67 ▶

3

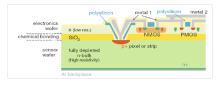

### SOI Technology

Monolithic pixel detector can result in a device with improved spatial resolution and minimized multiple scatterings effects. Different technological options:

Non-standard CMOS on high resistivity bulk, CMOS technology with charge collection in epi-layer, DEPFET pixel sensors, CMOS on Silicon-on-Insolator (SOI)

SOI Wafer: thick high resitivity handle layer, middle  $SiO_2$  layer and a low resistivity top active layer.

- **Detector**  $\rightarrow$  handle layer

- Read-out circuitry  $\rightarrow$  top layer

(日) (周) (三) (三)

Connected by vias

Ensure the proper operation of the readout circuitry while the detector is biased, with the effect of the back gate and radiation effects.

3

# Section 3 TRAPPISTe Project

**PIXEL 2012**

Test of TRAPPISTe

September 6, 2012 7 / 21

3

・ロン ・四 ・ ・ ヨン ・ ヨン

### **TRAPPISTe** Project

Tracking Particles for Physics Instrumentation in SOI Technology

- R&D project with the aim of studying the feasibility of developing a monolithic active pixel sensor with SOI technology.

- Université catholique de Louvain and Universitat Autonoma de Barcelona (2008); part of SOIPIX collaboration (2010).

### TRAPPISTe-1

- WINFAB at UCL, Louvain-la-Neuve, Belgium

- $2\mu m$  FD-SOI CMOS technology

- One metal layer, one poly layer

- 15-25 Ωcm p-type handle layer

- 100 nm top active layer

- 400 nm buried oxide

- $\sim$ 400  $\mu$ m handle layer

- Charge sensitive amplifier study.

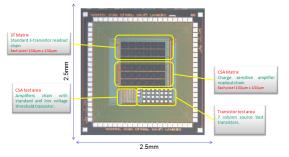

### TRAPPISTe-2

- LAPIS Technology

- 0.20µm FD-SOI CMOS technology

- Five metal layers, one poly layer

- 700 and 10k Ωcm n-type handle layer

- 50 nm top active layer

- 200 nm buried oxide

- $\sim$ 300  $\mu$ m handle layer

Different test areas: a transistor test area, a 3T matrix, an amplifier test area and an amplifier matrix.

3

(日) (同) (三) (三)

Test Systems

The TRAPPISTe chips have been characterized using a custom built PCB controlled by an Altera DE2 FPGA. A laser system LARA (Laser for Radiation Analysis) with motorized stage has been commissioned.

# Section 4

### Measurements

**PIXEL 2012**

Test of TRAPPISTe

September 6, 2012 11 / 21

3

・ロン ・四 ・ ・ ヨン ・ ヨン

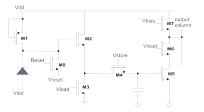

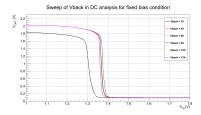

### TRAPPISTe-2: 3T Electrical Characterization I

The architecture is based on a simple three transistor structure where an external shift register is responsible for activating each column output.

- ( A 🖓

### 3T

### TRAPPISTe-2: 3T Electrical Characterization II

Electrical characterization was performed on pixels with 3T read-out architecture.

**PIXEL 2012**

Test of TRAPPISTe

э

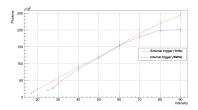

### TRAPPISTe-2: 3T Laser Measurements

Laser measurements were performed on pixels with 3T read-out architecture. Six columns of pixels were implemented. Response to laser despite low back depletion voltage. Movement of laser across pixels results in corresponding pixel response.

TRAPPISTe-2 response when laser is pointing at Row 1 Pix 3

**PIXEL 2012**

September 6, 2012 14 / 21

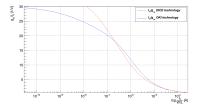

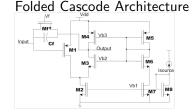

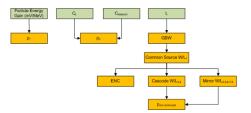

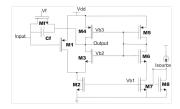

# Design of Charge Sensitive Amplifier (CSA) using $g_m/I_D$

### $g_m/I_D$ Transistor Characteristic

Design methodology to aid in transistor sizing based on amplifier specifications. Same methodology can be used for different techonologies.

September 6, 2012 15 / 21

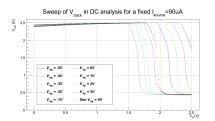

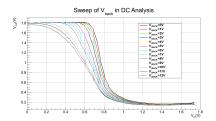

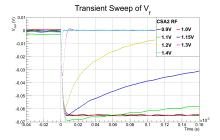

### **TRAPPISTe-1** Electrical Characterization

CSA test structures in UCL 2.0  $\mu m$  technology were characterized. DC curves shift with back voltage until -4V. Output shape determined by feedback transistor.

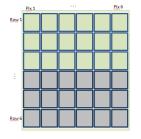

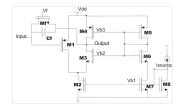

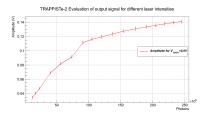

### TRAPPISTe-2 Electrical Characterization

Same architecture as previous CSA, built in LAPIS 0.2  $\mu m$  technology. Test structures show transfer curve shift up to higher  $V_{back}$ , more than 12V.

(日) (同) (三) (三)

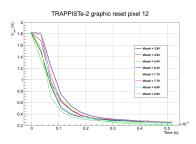

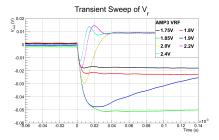

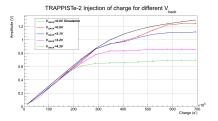

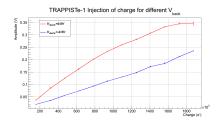

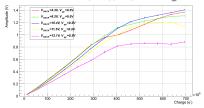

### TRAPPISTe-1 and TRAPPISTe-2 charge injection

Charge injection curves on test structures with input test capacitor:

- C<sub>TRAPPISTe-1</sub>=0.1pF

- C<sub>TRAPPISTe-2</sub>=37.5fF

Variation of curve for different  $V_{back}$ .

TRAPPISTe-2 Improvement of the gain by changing the biasing conditions for different V

(日) (同) (三) (三)

### TRAPPISTe-2 laser measurements

Laser measurements were performed on pixels with integrated CSA. Six columns of pixels were implemented. Response to laser despite low back depletion voltage. Movement of laser across pixels results in corresponding pixel response.

**PIXEL 2012**

Test of TRAPPISTe

19 / 21

# Section 5

Conclusion

**PIXEL 2012**

Test of TRAPPISTe

September 6, 2012 20 / 21

3

<ロ> (日) (日) (日) (日) (日)

### Conclusion

TRAPPISTe: Reasearch and development of monolithic pixel detector in SOI technology.

- TRAPPISTe-1 in WINFAB 2  $\mu m$  FD-SOI CMOS, TRAPPISTe-2 in LAPIS 0.2  $\mu m$  FD-SOI CMOS.

- 3T and transistor test structures characterized.

- Charge sensitive amplifier developed with  $g_m/I_D$  methodology have been characterized.

- Test structures show variation of perfomance due to back voltage.

- Laser response despite low depletion voltage.

- TRAPPISTe-3 to include process techniques to mitigate the back gate effect, such as the buried P-well and nested well process.

You are welcome to visit the Poster ID 63 "**Development of SOI Monolithic Detector System**" to find out more details about our work.

### Thank you for your attention!

3

Image: A math a math