BELGIUM

# **Development of SOI Monolithic Detector System**

UAB **Universitat Autònoma**

de Barcelona

P. Álvarez <sup>1</sup>, L. Soung Yee <sup>2</sup>, E. Martin <sup>1</sup>, E.Cortina <sup>2</sup>, C. Ferrer <sup>1</sup>

<sup>1</sup> Universitat Autònoma de Barcelona, Bellaterra, Spain

<sup>2</sup> Université catholique de Louvain, Louvain-La-Neuve, Belgium

Corresponding author: PaulaLiliana.Alvarez@uab.cat; lawrence.soungyee@uclouvain.be

Poster Id: 63

## Abstract

The electronic readout for the TRAPPISTE series of monolithic pixel detectors has been characterized. Developed in SOI technology, the behavior of the electronics due to the back voltage has been studied to determine the feasibility of implementing a monolithic particle detector.

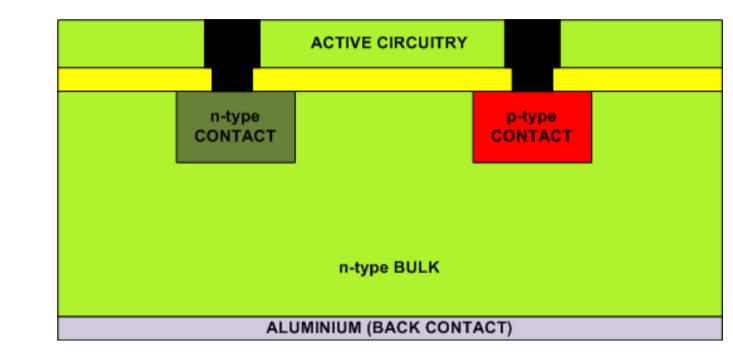

Silicon-on-Insulator CMOS technology can be used to develop monolithic radiation detectors.

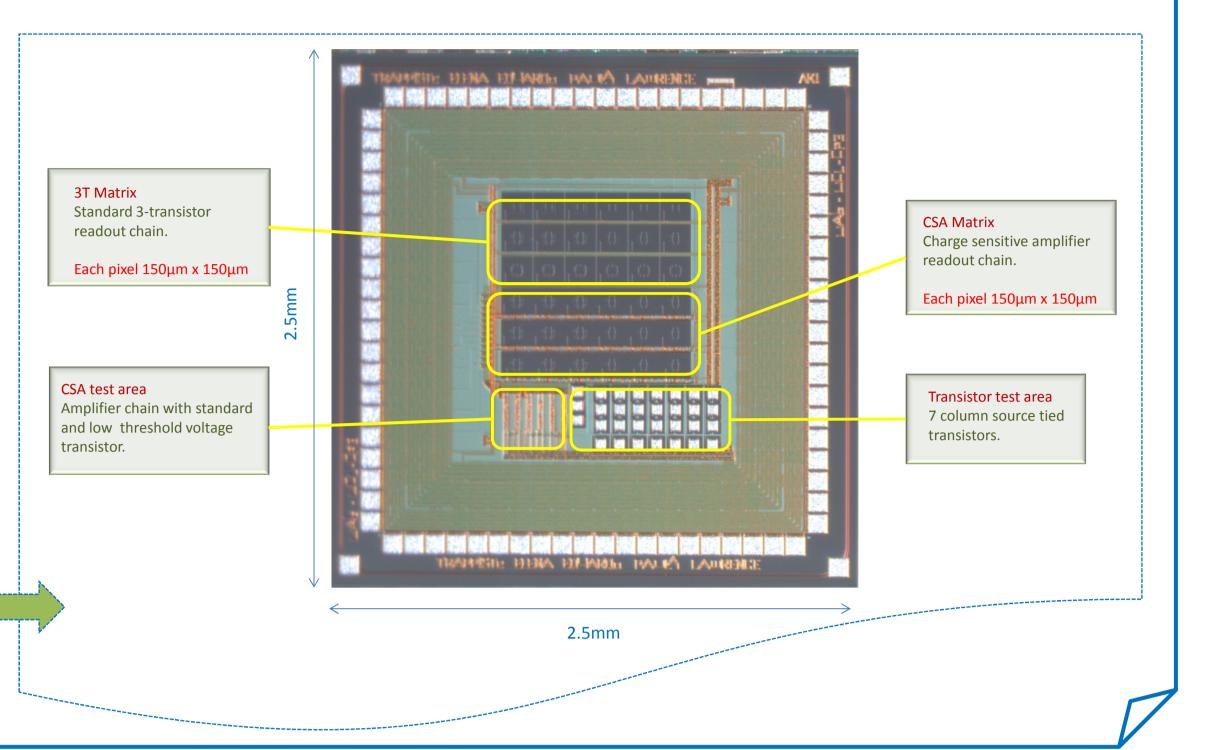

TRAPPISTe Particles (Tracking for **Physics Instrumentation in SOI Technology) project** aims to analyze and study how to minimize effects in SOI technology. To minimize them, different technologies and read-out approaches are evaluated.

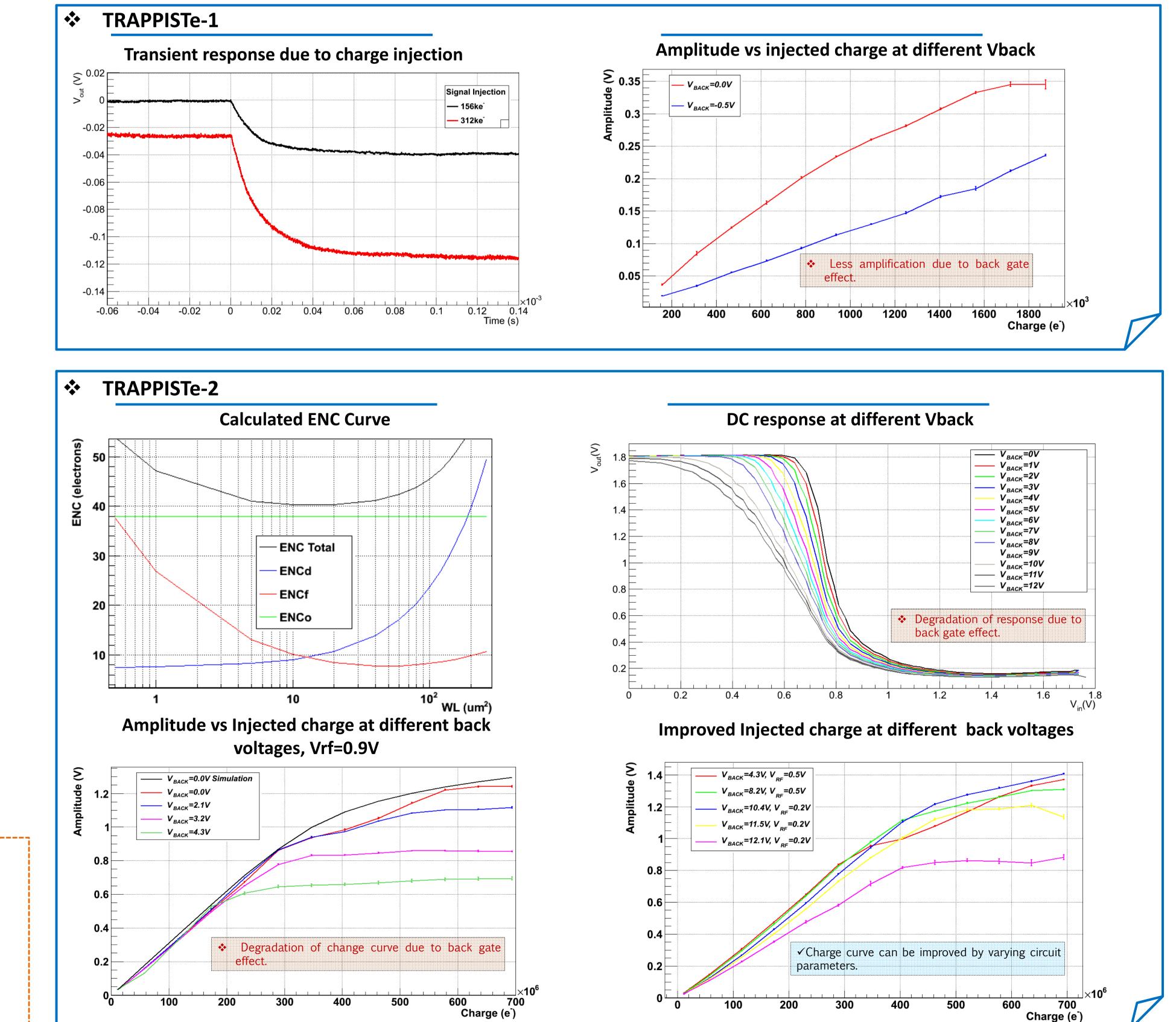

#### **TRAPPISTe-1**

was fabricated using WINFAB 2µm FD-SOI CMOS technology. It provides one metal layer, and a ptype wafer with a resistivity  $\sim 25\Omega$  cm.

Challenge: Its use is subject to the back gate effect because of the voltage applied to deplete the detector. Solution: Among others, increasing the oxide thickness and including different well implantations below the read-out circuitry.

### **TRAPPISTe-2**

was fabricated with LAPIS Semiconductors 0.20µm FD-SOI CMOS technology. It provides five metal layers and high resistivity n-type

substrates of 700 $\Omega$ cm and 10k $\Omega$ cm.

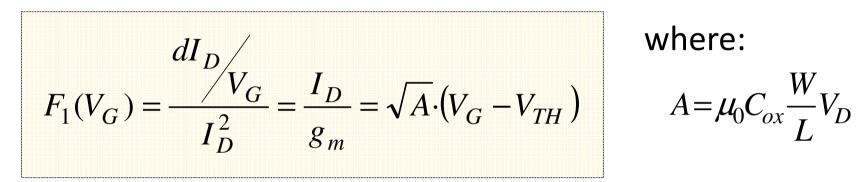

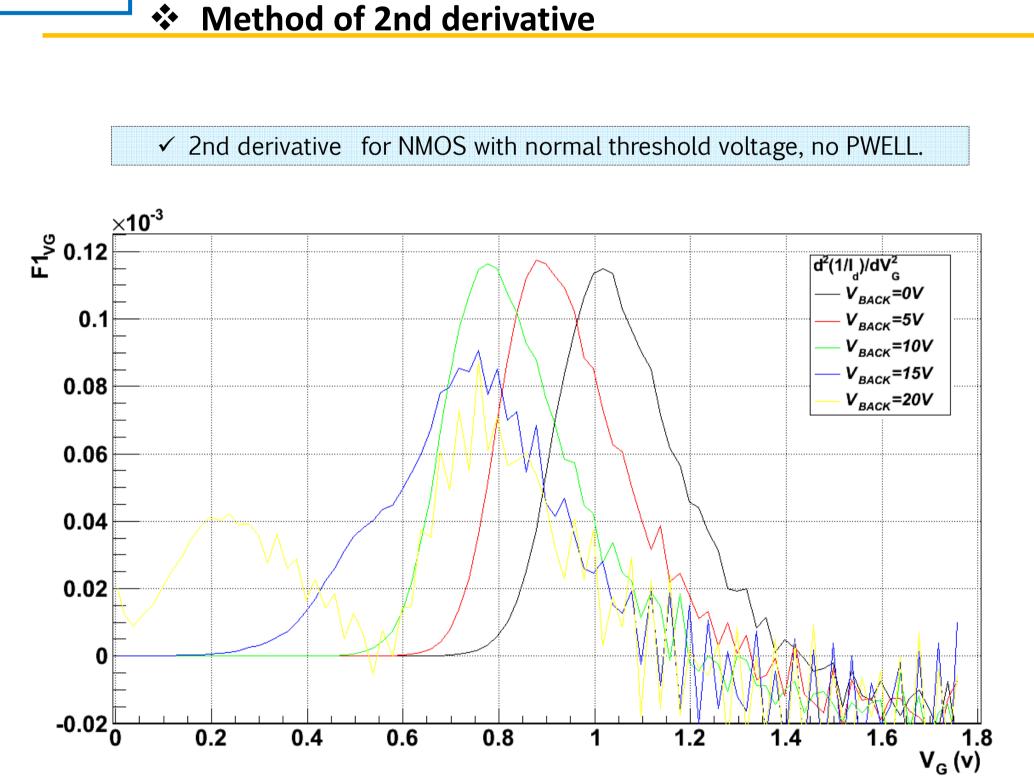

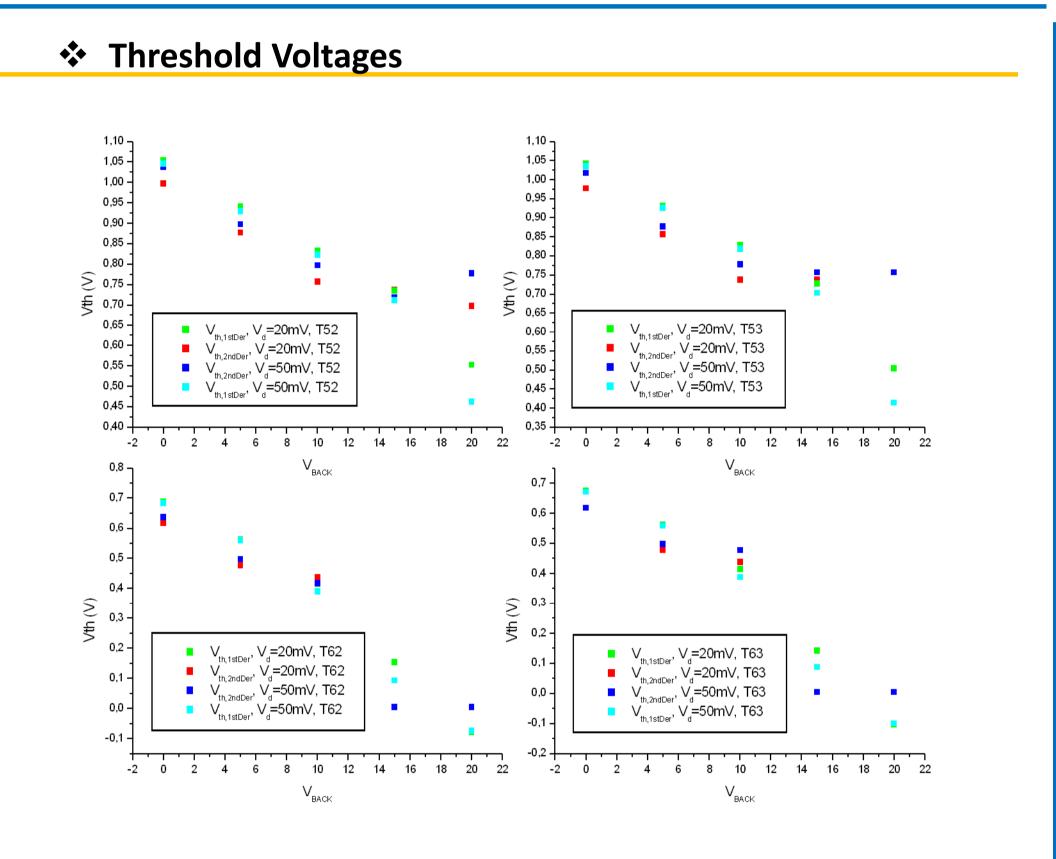

## Characterization of the TRAPPISTe-2 transistor

All of the transistors have a W/L of  $10\mu m/2\mu m$  except for the I/O n-type Depleted MOS (DMOS) transistors which are size 2μm/10μm.

Use of 2 methods (Linear-extrapolation and minimum of 2<sup>nd</sup> derivative) at 2 different biasing conditions (Vd=20mV and 50mV) to obtain V<sub>th</sub>

| Transistor<br>Type     | Characteristics         | Comment           |

|------------------------|-------------------------|-------------------|

| NMOS (52)              | Vth, normal             | PWELL             |

| NMOS (53)<br>NMOS (62) | Vth, normal<br>Vth, low | NO PWELL<br>PWELL |

|                        |                         |                   |

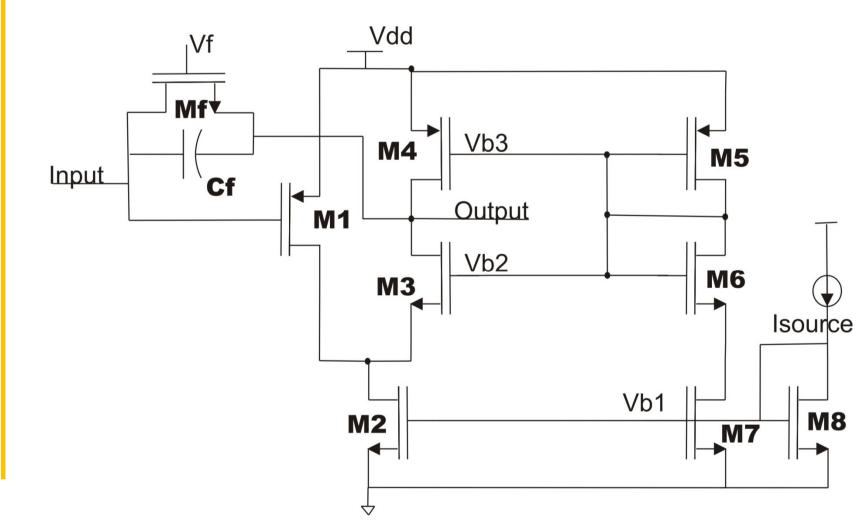

## **Charge Sensitive Amplifier**

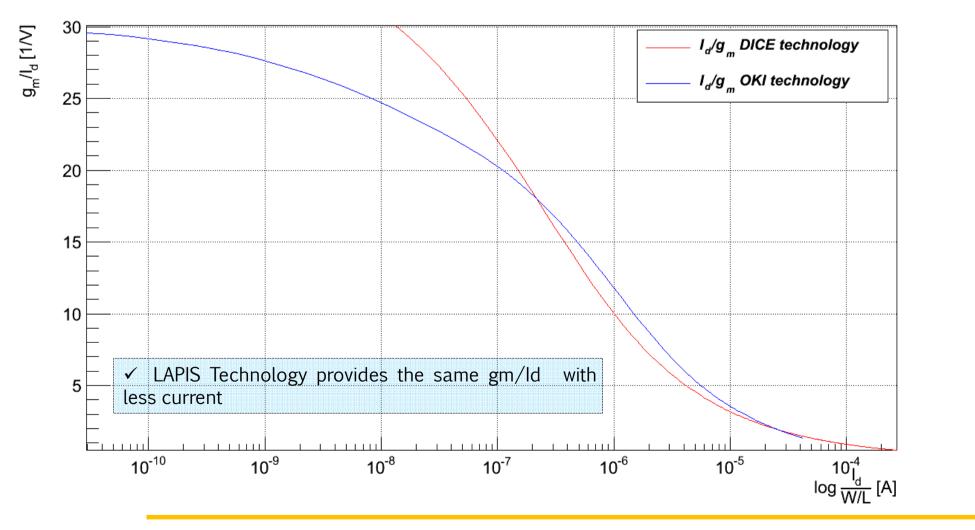

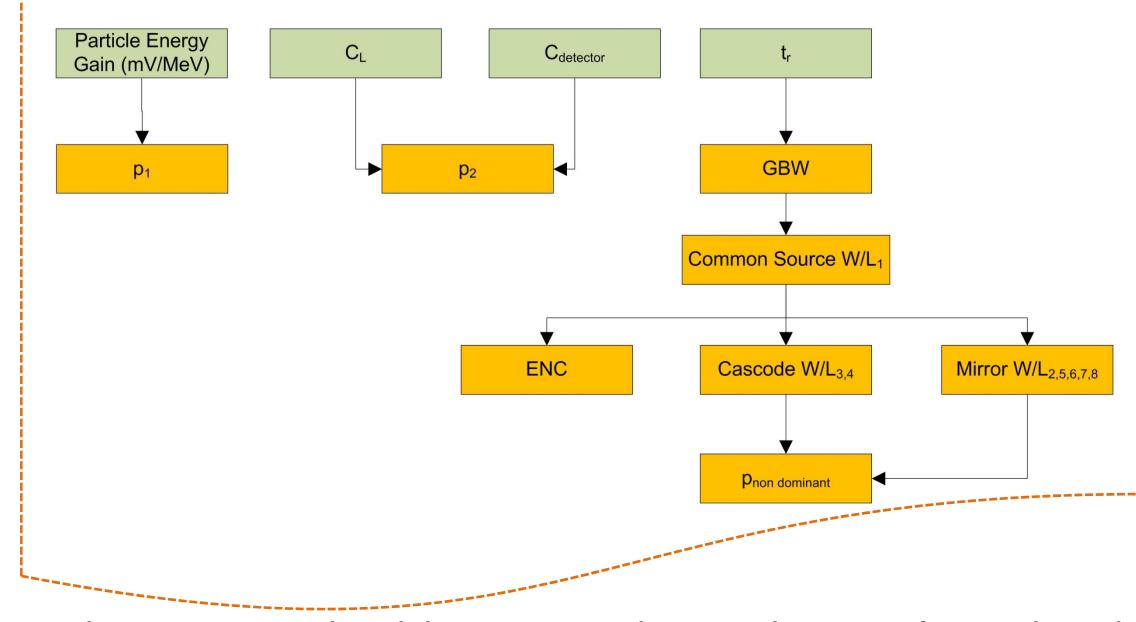

#### gm/Id Design Methodology and Test

Standard folded cascode core with feedback

**Comparison of gm/Id curves for DICE and LAPIS Technology**

#### **Specifications:**

Particle Energy= 1MIP (24ke-), Gain=20mV/MIP, CF=0.2pF, Cdetector=5pF, tr=100ns

## Conclusions

- Charge amplifiers were developed in DICE and LAPIS technologies using a gm/Id methodology. Testing was performed on test structures with particular attention to the effect of varying the back side voltage as these amplifiers are to be used in the TRAPPISTe monolithic pixel detector. The charge injection curves exhibit degradation due to increasing back voltage. Variation of circuit parameters can recover charge curve functionality up to a certain point.

- Future development of the amplifier would involve techniques to mitigate the back gate effect, such as buried p-well process technology foreseen for TRAPPISTe-3.

Pixel2012, International Workshop on Semiconductor Pixel Detectors for Particles and Imaging

September 3 – 7, 2012 Inawashiro, Japan