# The Belle II pixel detector

Carlos Marinas University of Bonn

On behalf of the DEPFET Collaboration

#### Outline

#### SuperKEKB

- KEKB machine upgrade

- Belle II DEPFET pixel detector (PXD)

- DEPFET

- Fundamentals

- System elements

- Belle II PXD Recent progress

- PXD6 production

- Lab and beam tests

- Radiation hardness

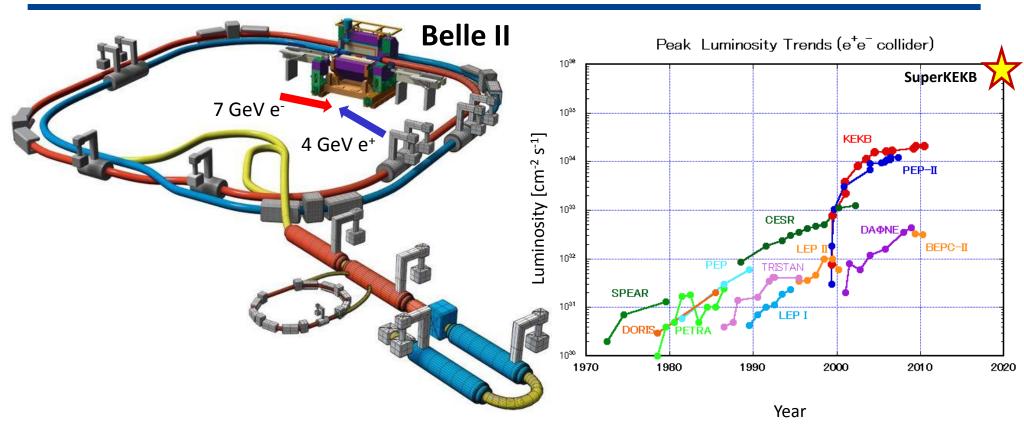

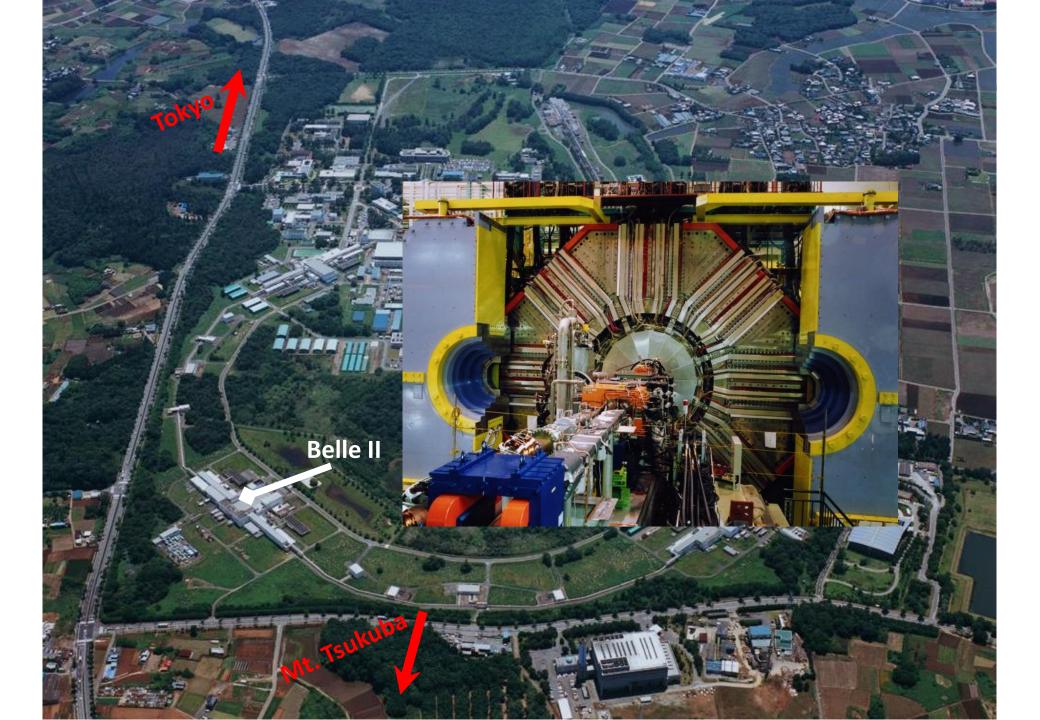

## **KEKB upgrade plan: SuperKEKB Flavour Factory**

universität**bonn**

- Asymmetric energy (4 GeV, 7 GeV)  $e^+e^-$  collider at the  $E_{cm}=m(Y(4S))$  to be realized by upgrading the existing KEKB machine (Tsukuba, Japan)

- Collisions with very small spot-size beams (nano beam) and higher currents

- Final luminosity 8.10<sup>35</sup> cm<sup>-2</sup> s<sup>-1</sup>, 40 times higher than the existing KEKB Factory

- Start of the machine commissioning in 2014

- Start of the physics run in 2015

## KEK High Energy Accelerator Research Organization

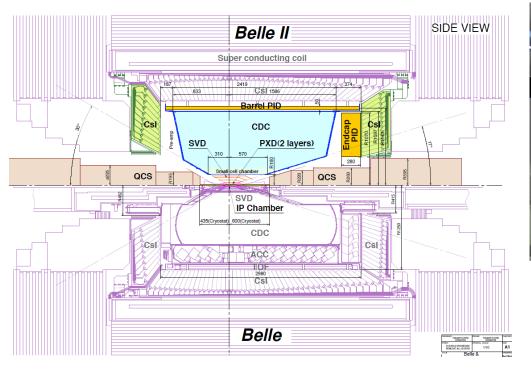

## **Belle II Silicon Vertex Detector**

- Critical issues at ultra high luminosity  $\mathcal{L}$  = 8.10<sup>35</sup> cm<sup>-2</sup> s<sup>-1</sup>:

- Higher background

- ightarrow Radiation damage , large occupancy, fake hits

- Higher event rate

- ightarrow Higher rate trigger, DAQ and computing

$\rightarrow$  Significant upgrade!

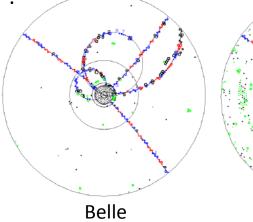

- New: The Belle II Collaboration decided on DEPFETs for the two innermost layers

- ✓ More robust tracking (6 layers)

- ✓ Better vertex resolution (closer to IP)

Belle I

## **Belle II PXD detector requirements**

|                | Belle II PXD                 |  |

|----------------|------------------------------|--|

| Occupancy      | 0.1 hits/µm²/s               |  |

| Radiation      | 1.5 Mrad/year                |  |

| Frame time     | 20 μs (continuous r.o. mode) |  |

| Momentum range | Low momentum (< 1GeV)        |  |

| Acceptance     | 17º-155º                     |  |

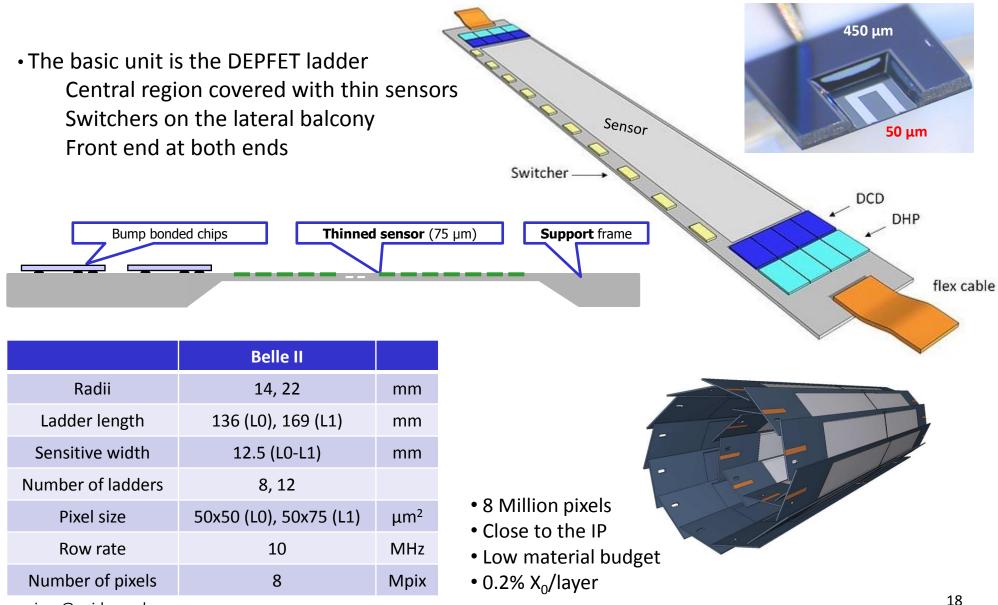

The combination of resolution, mass and power dissipation is a substantial challenge

- Belle II is dominated by low momentum tracks

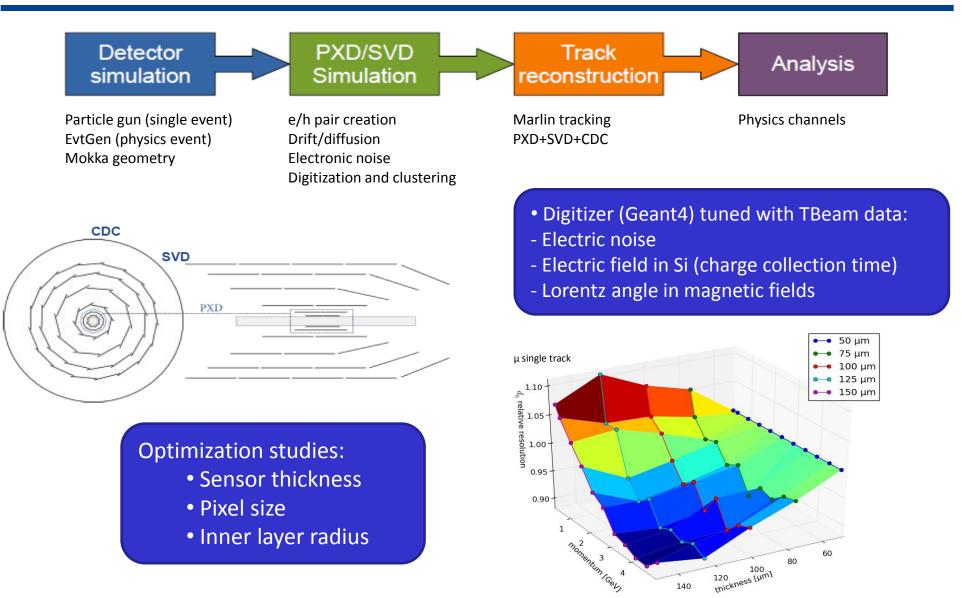

- > Modest intrinsic resolution (10  $\mu$ m), dominated by m.s.  $\rightarrow$  Moderate pixel size (50 x 75  $\mu$ m<sup>2</sup>)

- > Lowest possible material budget (0.2%  $X_0$ /layer\*\*)

$\rightarrow$  The DEPFET technology can cope with these challenging requirements

Tight schedule to develop a complete detector system by 2015

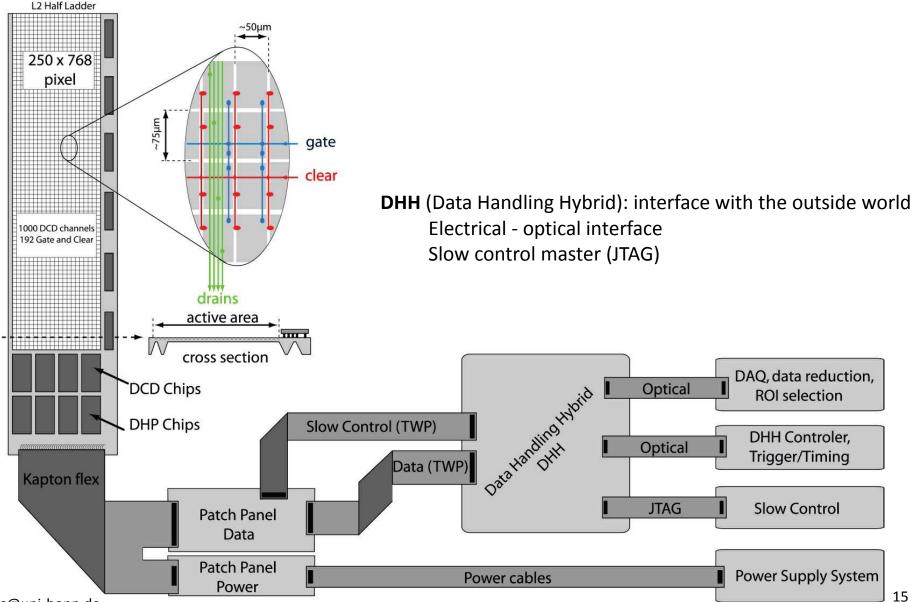

#### **DEPFET – DEpleted P-channel Field Effect Transistor** universität

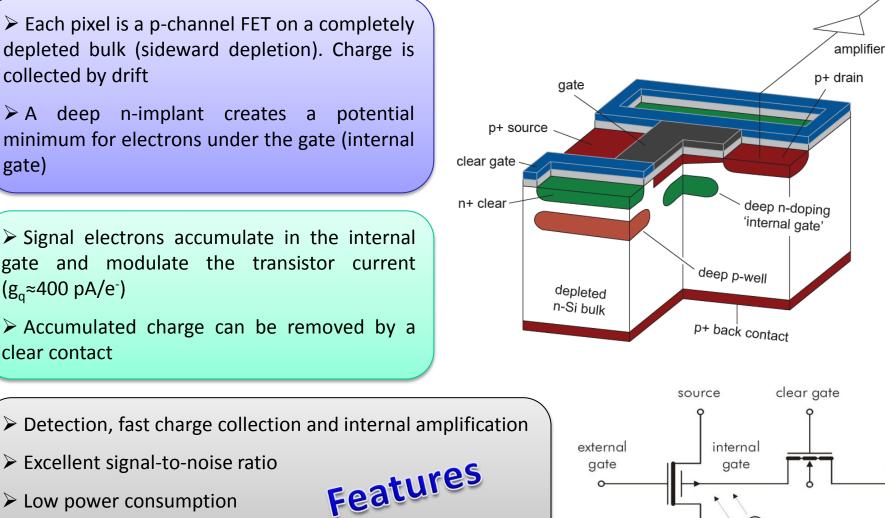

Each pixel is a p-channel FET on a completely depleted bulk (sideward depletion). Charge is collected by drift

> A deep n-implant creates a potential minimum for electrons under the gate (internal gate)

Signal electrons accumulate in the internal gate and modulate the transistor current (g<sub>a</sub>≈400 pA/e<sup>-</sup>)

Accumulated charge can be removed by a clear contact

drain

Excellent signal-to-noise ratio

Thin detectors

cmarinas@uni-bonn.de

clear

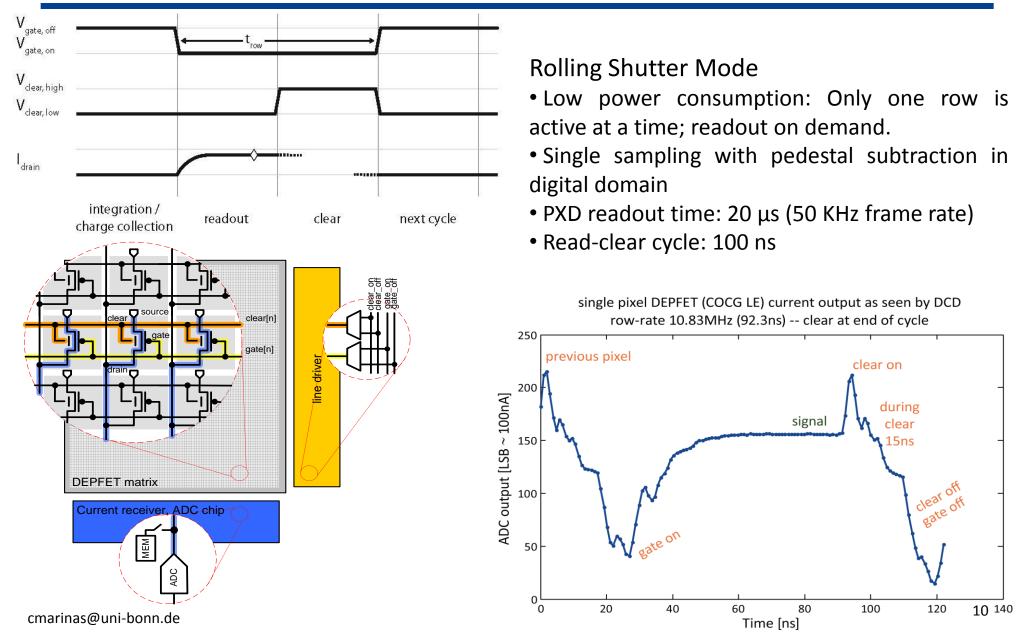

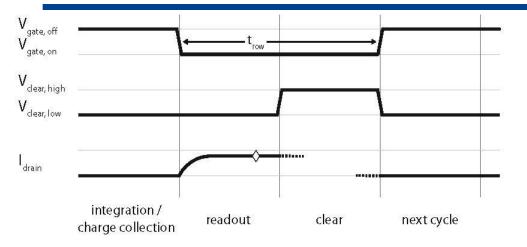

#### **Operation mode: Row-wise readout**

#### **Operation mode: Row-wise readout**

#### cmarinas@uni-bonn.de

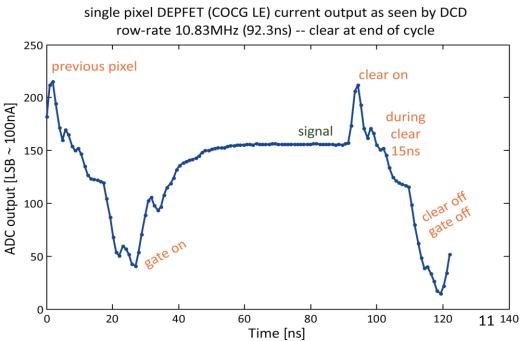

#### **Rolling Shutter Mode**

- Low power consumption: Only one row is active at a time; readout on demand.

- Single sampling with pedestal subtraction in digital domain

- PXD readout time: 20 µs (50 KHz frame rate)

- Read-clear cycle: 100 ns

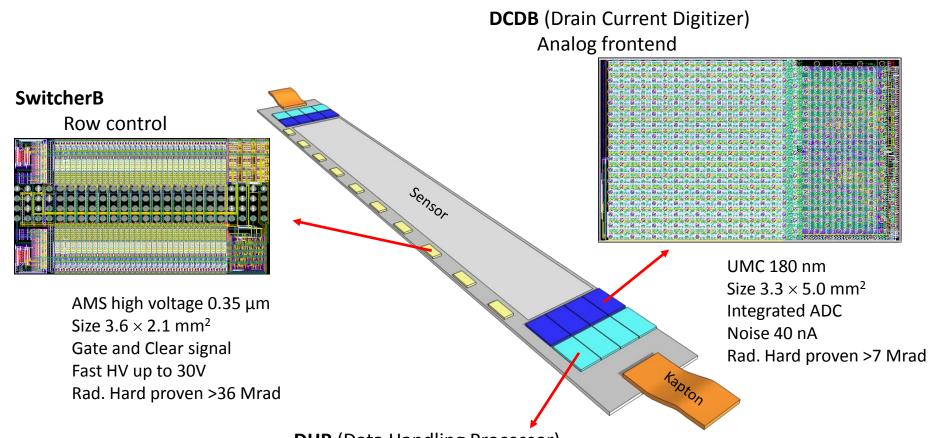

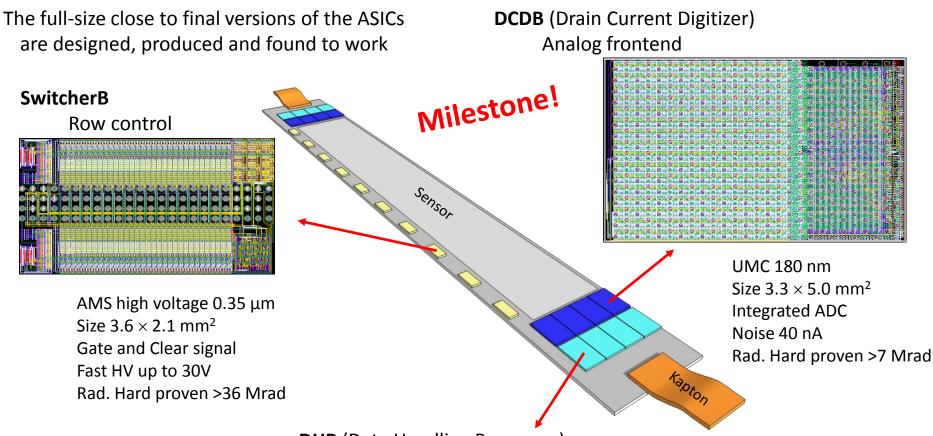

#### **DEPFET auxiliary ASICs**

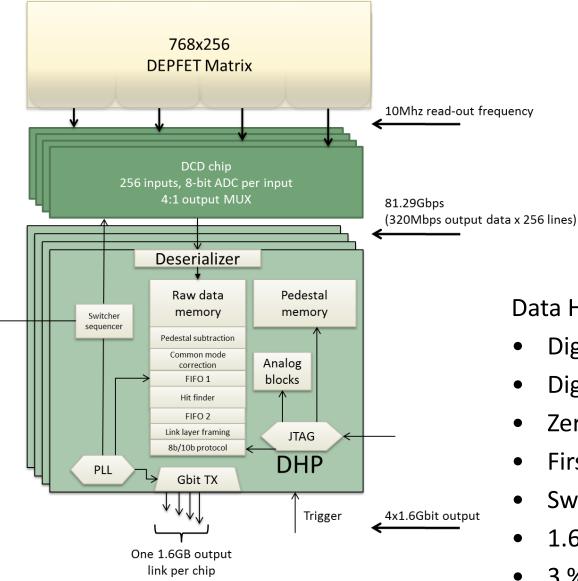

#### **DHP** (Data Handling Processor)

Processor

| 1 |                  |               |  |

|---|------------------|---------------|--|

|   |                  |               |  |

|   |                  |               |  |

|   | (interpretation) | in the second |  |

|   |                  |               |  |

|   |                  |               |  |

IBM CMOS 90 nm (TSMC 65 nm) Stores raw data and pedestals Common mode and pedestal correction Data reduction (zero suppression) Timing signal generation Rad. Hard proven >10 Mrad 12

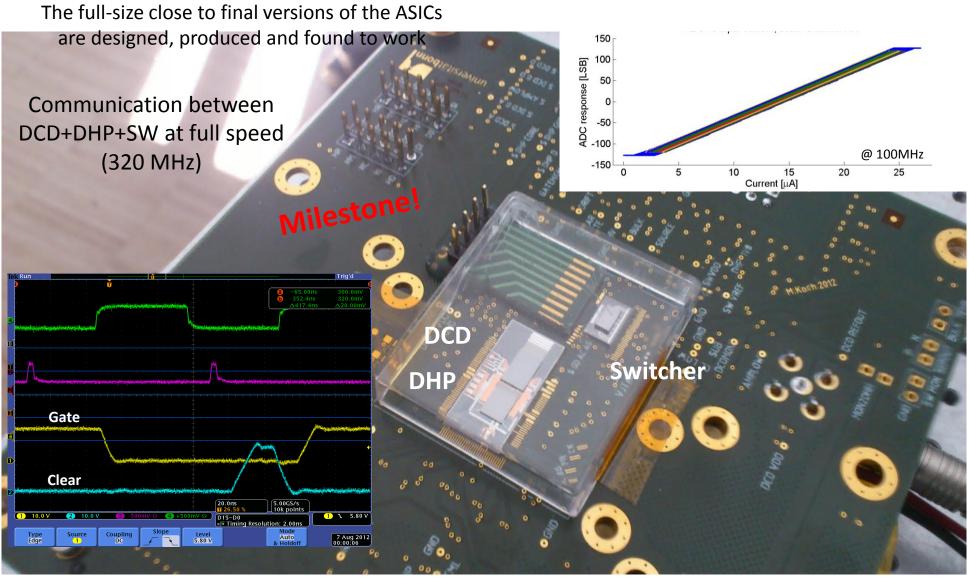

## **DEPFET auxiliary ASICs**

#### **DHP** (Data Handling Processor)

Processor

IBM CMOS 90 nm (TSMC 65 nm) Stores raw data and pedestals Common mode and pedestal correction Data reduction (zero suppression) Timing signal generation Rad. Hard proven >10 Mrad 13

The layout of the module periphery is ready as well

## **DEPFET** auxiliary ASICs

#### **Off-module signal flow**

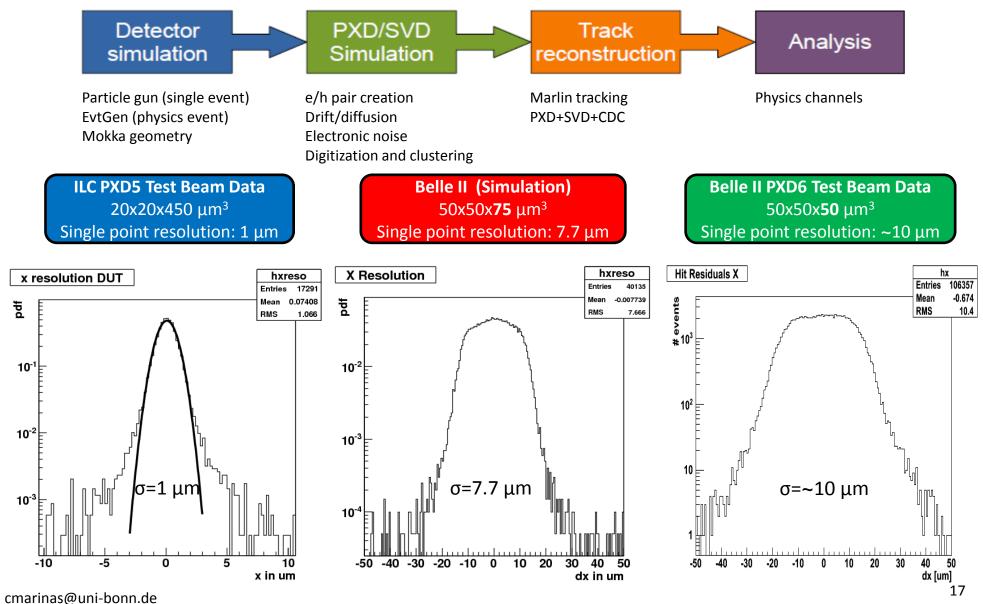

## **Optimization: Full simulation chain**

### **Optimization: Full simulation chain**

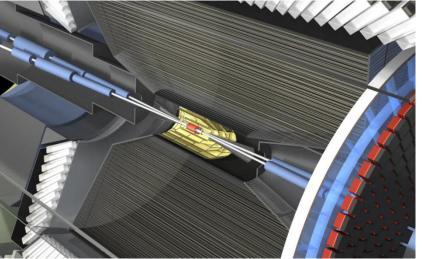

## **General layout of a DEPFET detector**

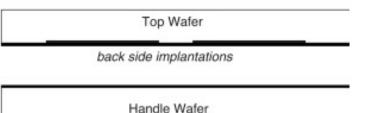

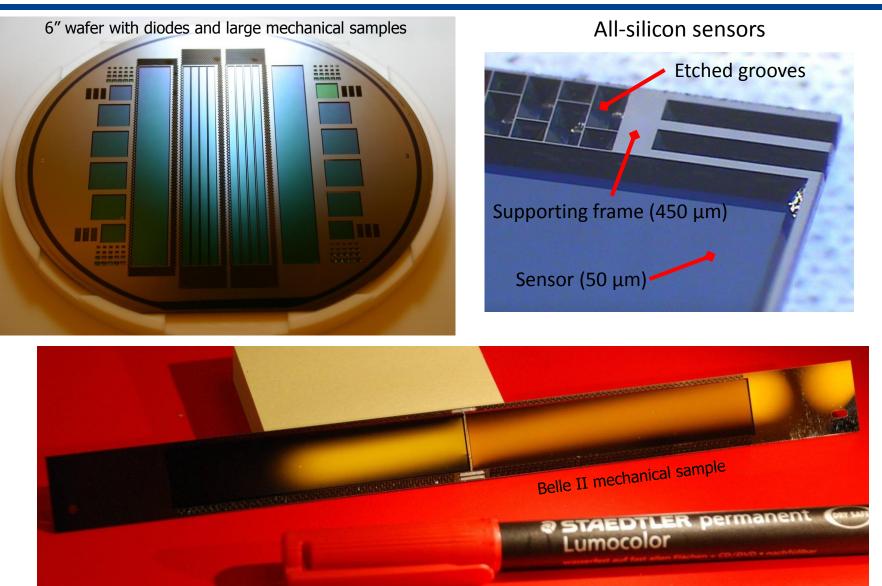

## **Thinning technology: All silicon sensors**

Use anisotropic etching on bonded wafers to create a thin, self-supporting sensor

$\rightarrow$  One material uniform and small thermal expansion

• Oxidation and back side implant on sensor wafer

- Wafer bonding (with SiO<sub>2</sub> in between) and grinding/polishing of top wafer. Thin sensor side to the desired thickness

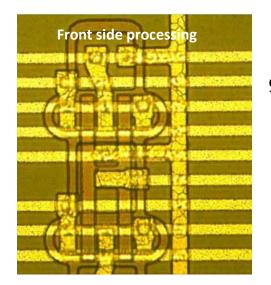

- Process DEPFET on top side  $\rightarrow$  passivation

• Anisotropic deep etching opens "windows" in the handle wafer. Etch backside up to oxide/implant (etch stops SiO<sub>2</sub>)

## **Thinning technology**

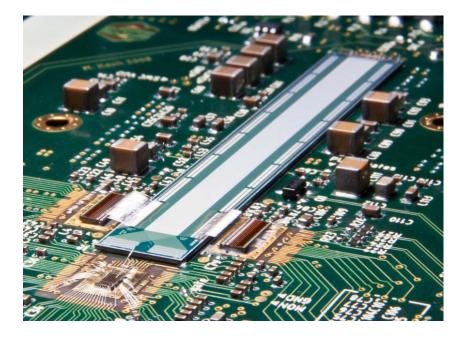

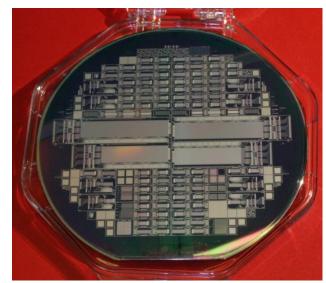

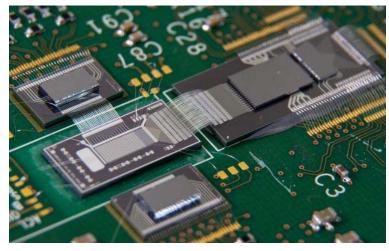

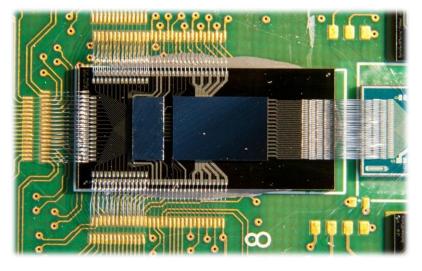

#### **PXD6 prototype production**

8 wafers with 50  $\mu m$  thin sensors

- Small test matrices to test different pixel sizes (50-200 μm)

- Design variations: short gate lengths, clear structures, drift

- Full size sensors –half ladders for prototyping

- Technology variations on the wafer level

90 steps fabrication process: 25 mask steps 9 Implantations 19 Lithographies Double Poly layers 3 Metal layers Back side processing

First thin DEPFET sensors produced!

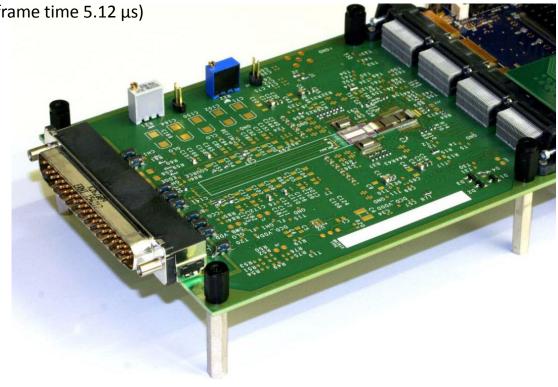

#### **PXD6 - Beam Tests**

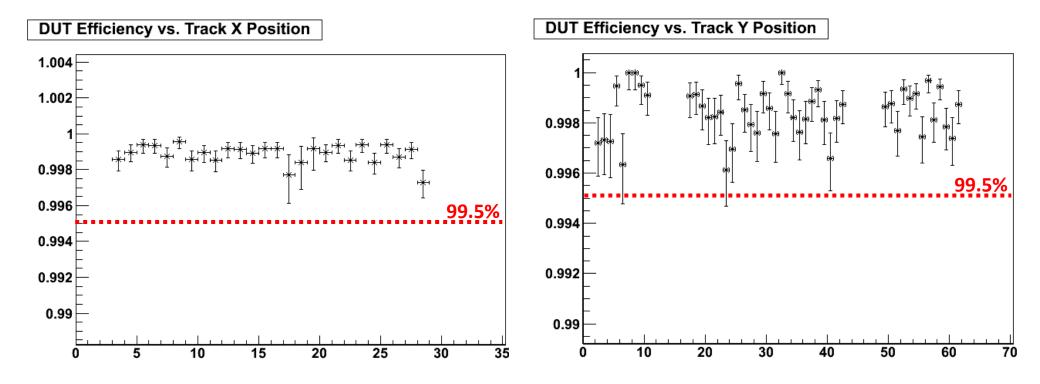

Measurement in 120 GeV Pion beam at CERN SPS

- PXD6 Standard Design **Belle II Type**

- SwitcherB and DCDBv2 (100 MHz\*, frame time 5.12 μs)

- Pixel size 50x75x50 μm<sup>3</sup>

- Gate Length 5 µm

- Thick oxide\*

#### **Close to final specs!**

Based on the valuable information obtained with the PXD6, the final Belle II production (PXD9) is already launched

#### Electrically precharacterized in the lab

#### cmarinas@uni-bonn.de

#### \* 320 MHz and thin oxide in the final production

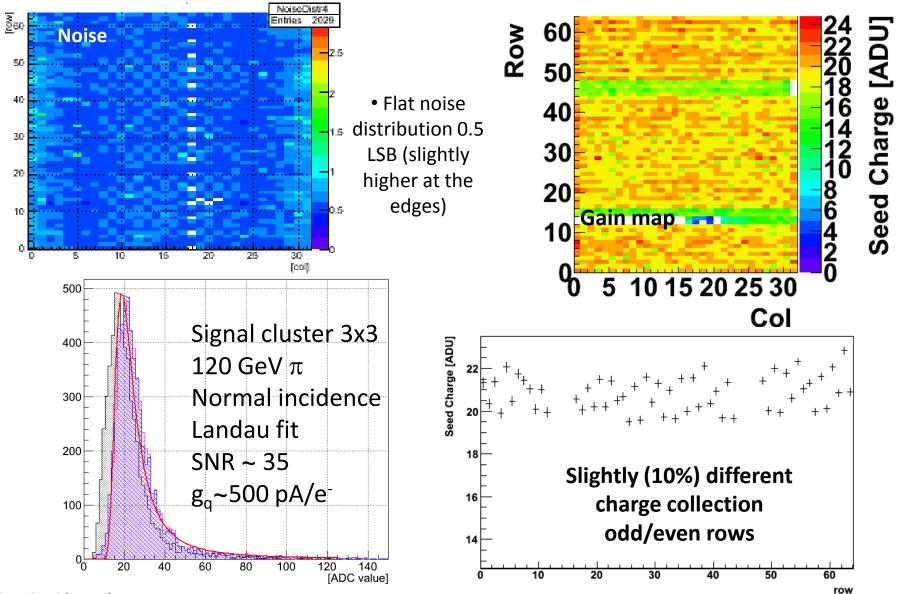

#### Signal, noise and pixel gain

23

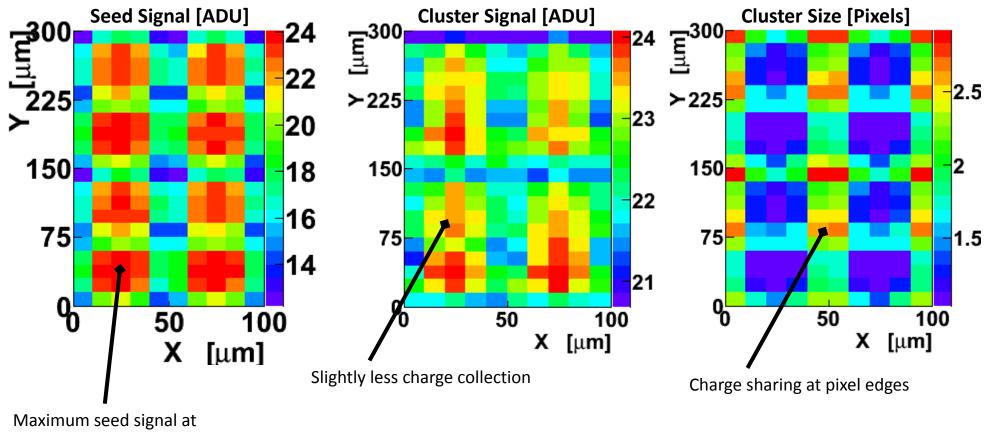

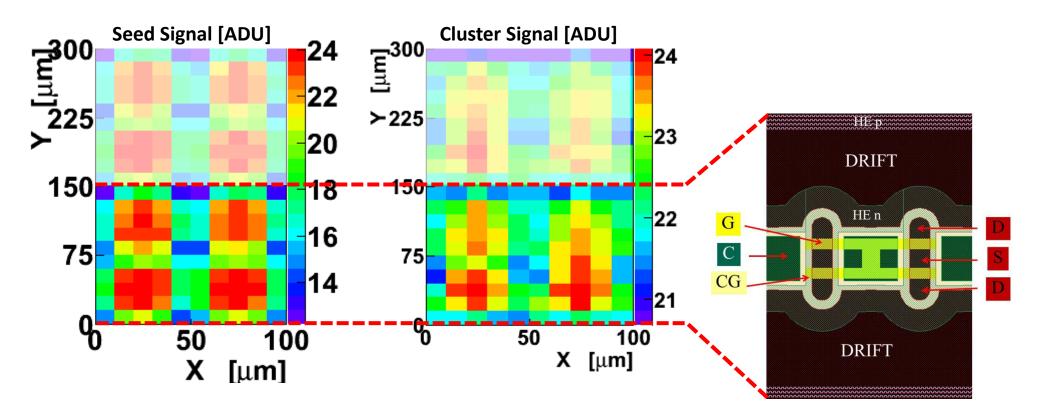

## In pixel studies

universität**bonn**

#### In pixel studies on a 2x4 pixels area of the matrix

the pixel center

## In pixel studies

In pixel studies on a 2x4 pixels area of the matrix

Slightly different charge collection odd/even rows Under investigation Efficiency

$\rightarrow$  The efficiency is higher, both column and row wise, than 99.5%

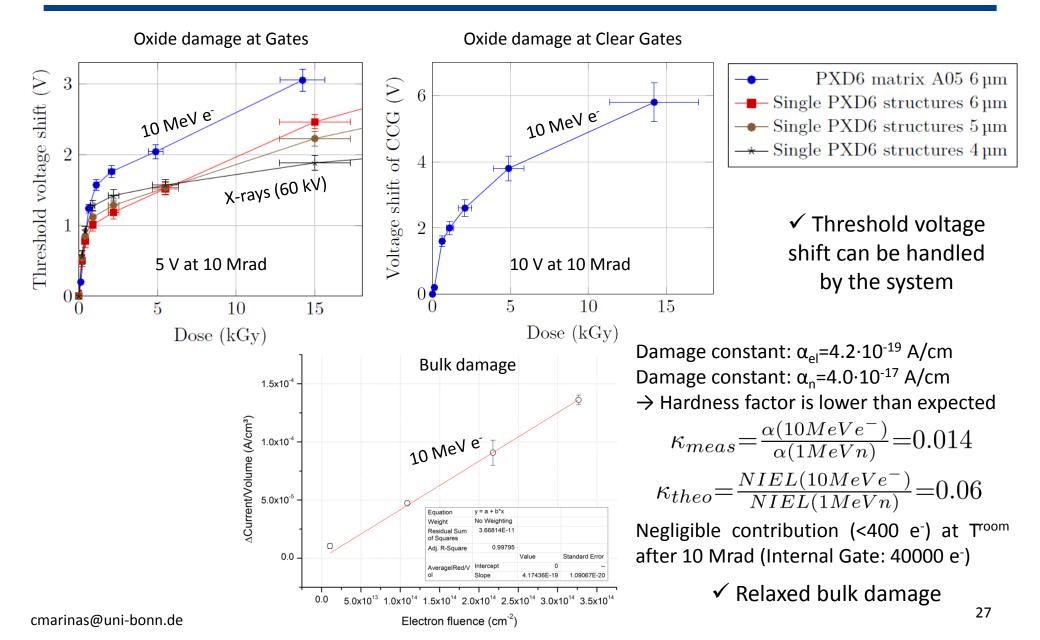

#### **Radiation hardness**

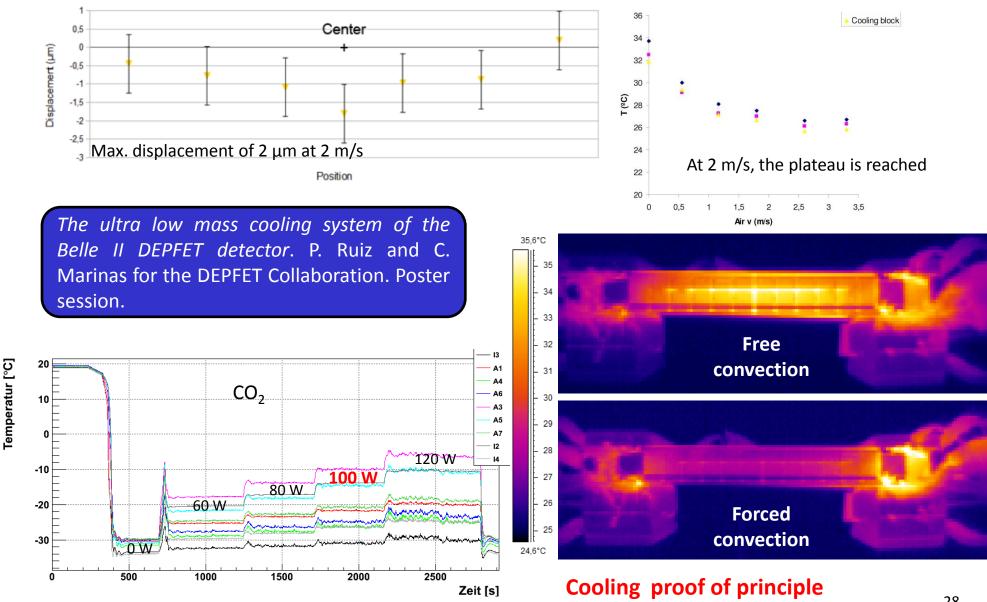

#### **Thermo-mechanical measurements**

- A new super flavour factory, SuperKEKB, is currently being built at KEK (Japan)

- To fully exploit the high luminosity, the detector will be upgraded (Belle II)

- The pixel detector will be made of DEPFET sensors

$\rightarrow$  Excellent single point resolution (10 µm), high SNR (>35), low power consumption (<0.1 W/cm<sup>2</sup>), low material budget (<0.2X<sub>0</sub>/layer), radiation hardness (10 Mrad)

- The DEPFET PXD entered the construction phase

- All readout ASICs and radiation hard sensors are produced and being operated in a close to final version

- Many aspects not covered in this talk, though in development by the Collaboration

## Thank you

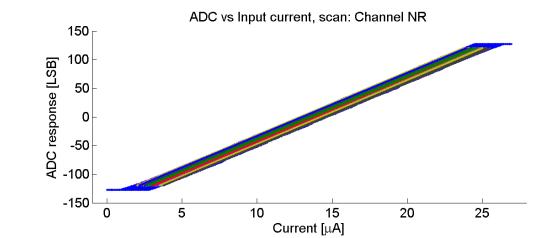

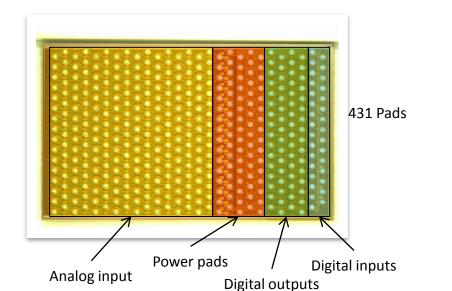

#### DCDB

31

Drain Current Digitizer for Belle II

- 512 ADCs

- Cyclic conversion

- 320 MHz clocked

- 100 ns conversion time

- Mean INL < 1.5LSB (Max < 2.2 LSB)

- Gain variation < 5% (peak to peak)

DHP 0.2

Data Handling Processor

- Digital common mode subtraction

- Digital pedestal compensation

- Zero suppression

- First full size chip

- Switcher control

- 1.6 Gb serial link

- 3 % occupancy with <1% data loss