## Wir schaffen Wissen – heute für morgen

Paul Scherrer Institut Roberto Dinapoli

roberto.dinapoli@psi.ch

**EIGER characterization results**

## Chip design at the SLS Detector Group

Low energy detectors Small pitch bump-bonding

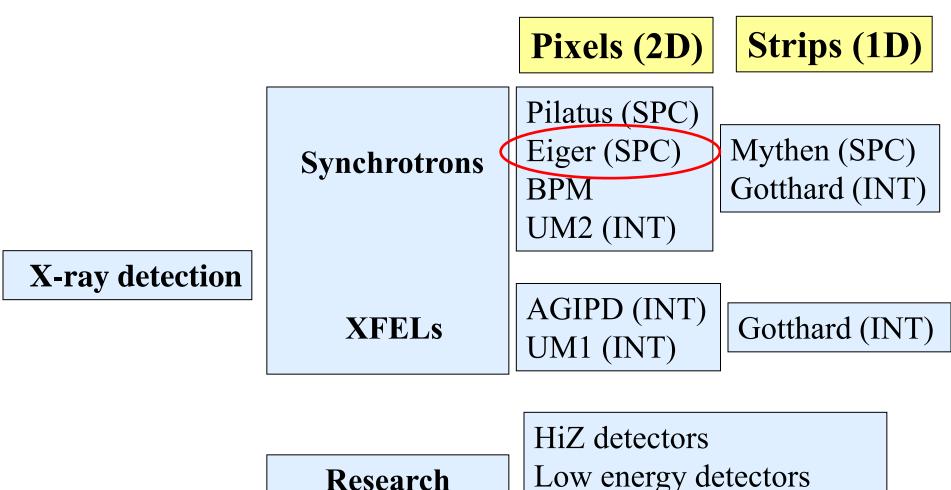

SPC= single photon counting; INT=charge integration UM=unknown mountain, BPM= beam position monitor

PAUL SCHERRER INSTITU

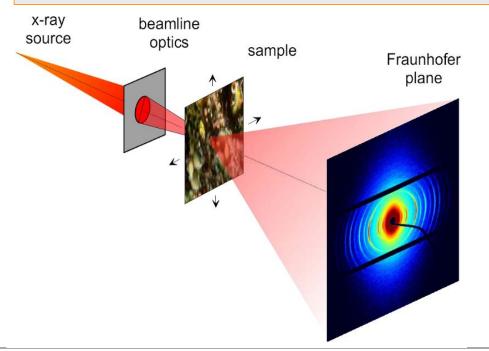

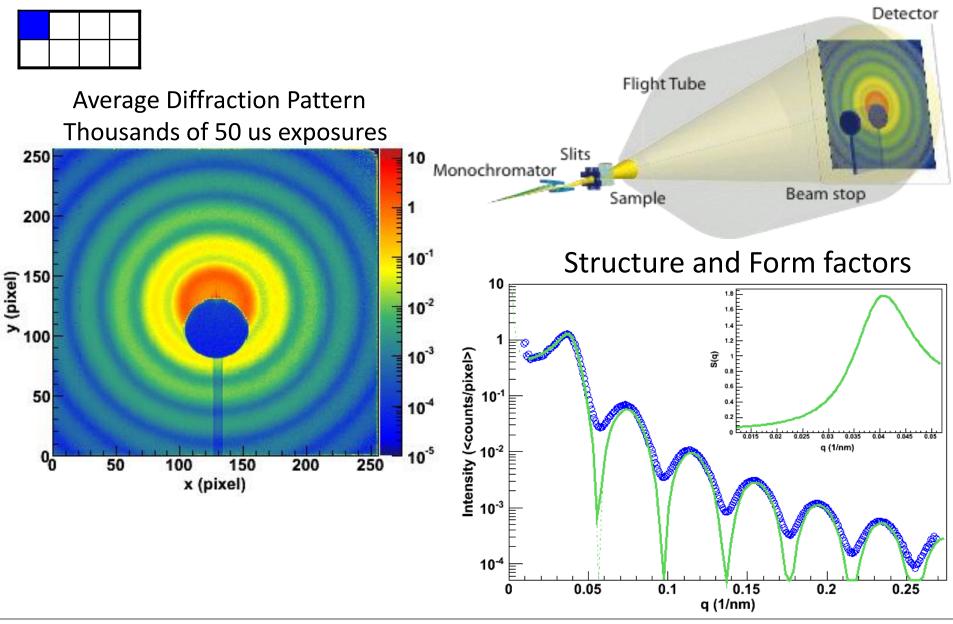

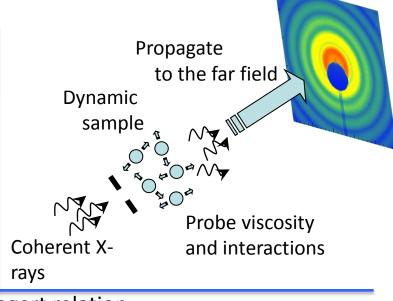

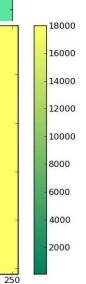

Single photon counting hybrid pixel detectors for synchrotron applications are aimed towards diffraction experiments

- Applications at CSAXs:

- Scanning Coherent Small Angle X-ray Scattering

- Coherent Diffractive Imaging

- X-ray Photon Correlation Spectroscopy

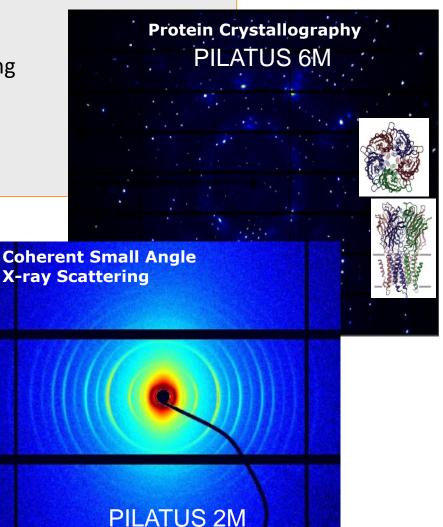

- Protein Crystallography

#### **No of Modules** 60 Module size 487 x 195 pixels (90k) **Detector Size** 431 x 448 mm<sup>2</sup> No of Pixels 2527 x 2463 pixels (6.2 \* 10<sup>6</sup> pixels) Spatial resolution 0.172 x 0.172 mm<sup>2</sup> **Dynamic range:** 20bits **Readout time** ~2ms Frame rate 5-10 Hz Rate 1 MHz/pixel Spatial distortion Flat geometry **Dead area** ~8.4 %

Large area

Single photon resolution

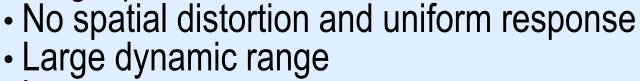

## Requirements for an ideal detector

Ρ

L

Α

Т

U

S

# EIGER main features (I)

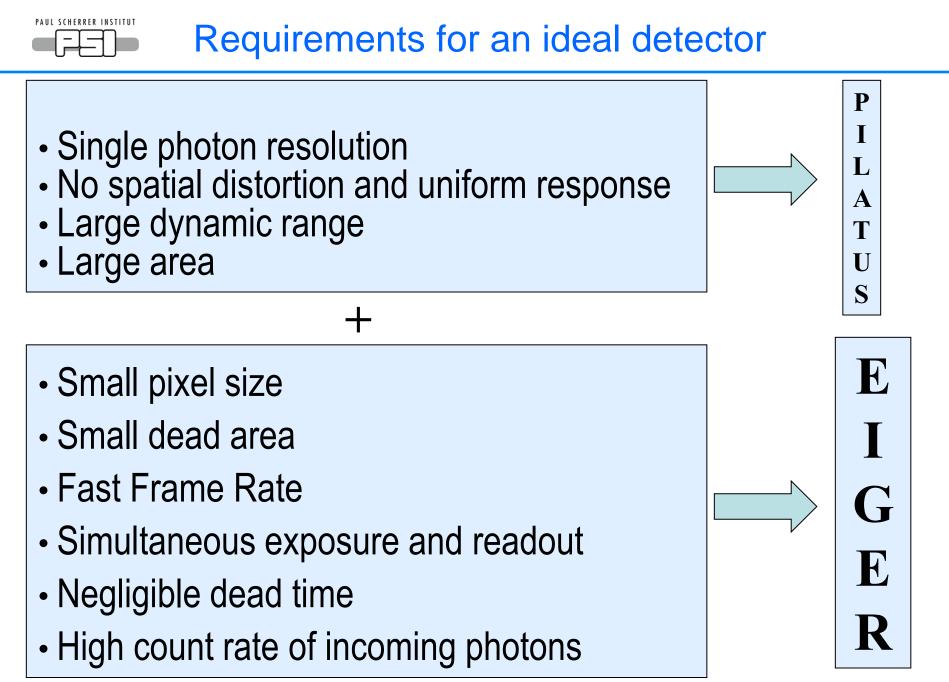

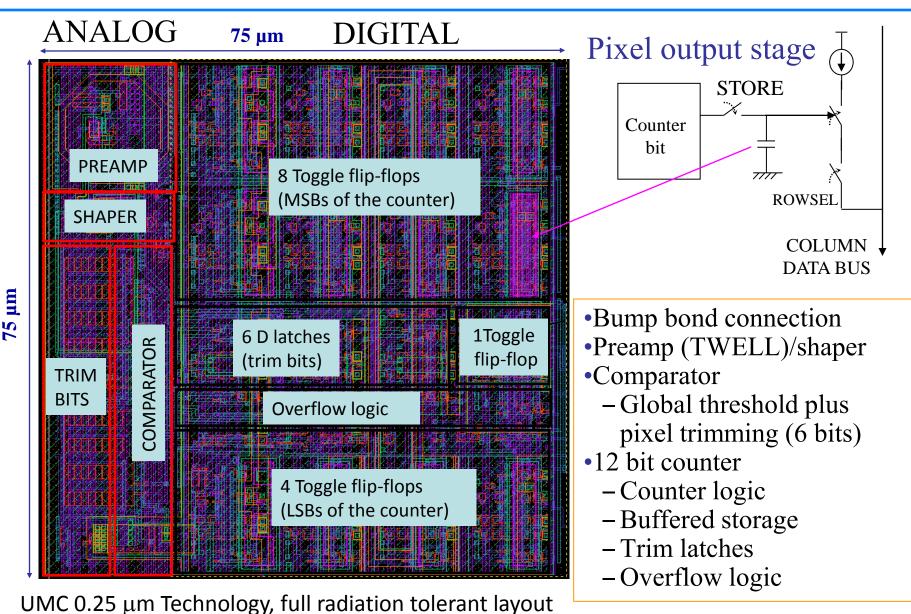

| Technological process                                      | UMC 0.25 μm                                                                         | In red:                    |  |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------|--|--|

| Radiation tolerance                                        | Full radiation tolerant design (>4Mrad)                                             | Improvement<br>factor with |  |  |

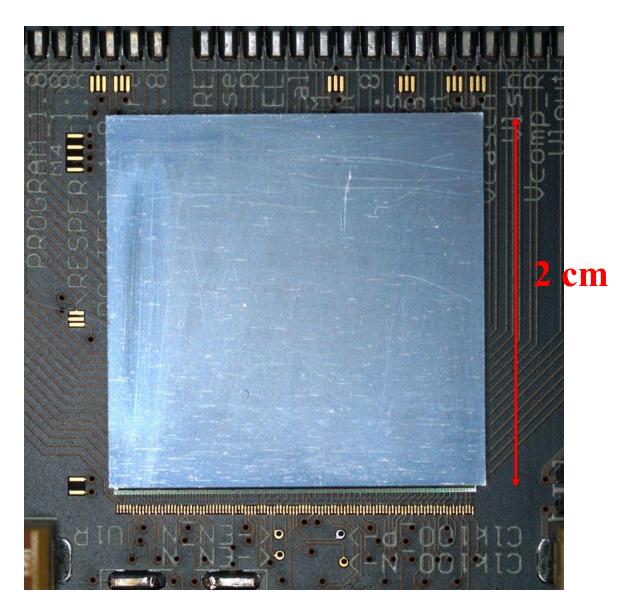

| Analog Parameters                                          | 30 ns peaking time<br>~150 ns ret. Zero<br>8.8 μW/pixel = 2.3 /<br>Gain: 44.6 μV/e- | respect to<br>PILATUS      |  |  |

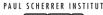

| Chip size                                                  | 19.3 x 20.1 mm <sup>2</sup> (active 19.2x19.2mm <sup>2</sup> )<br>> 2 x             |                            |  |  |

| Pixel size                                                 | 75 x 75 μm <sup>2</sup><br>= / 5.3                                                  |                            |  |  |

| Pixel array                                                | 256 x 256 = 65536<br>= 11.3 x                                                       |                            |  |  |

| Count rate                                                 | 3.4 x 10 <sup>9</sup> x-rays/mm <sup>2</sup> /s = 5.3 x<br>(1-2 Mcounts/pixel/s)    |                            |  |  |

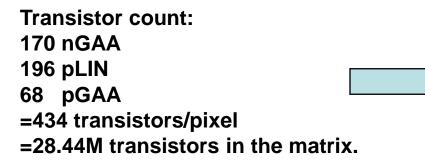

| Transistors, Matrix:<br>Periphery:<br>Transistors density: | 28.44M = 9.5 x<br>>120 000<br>430/pixel, ~5 x                                       |                            |  |  |

# EIGER main features (II)

| Nominal power supplies                | 1.1 V (analog), 2V (digital), 1.8V (I/O)                                                                     |  |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

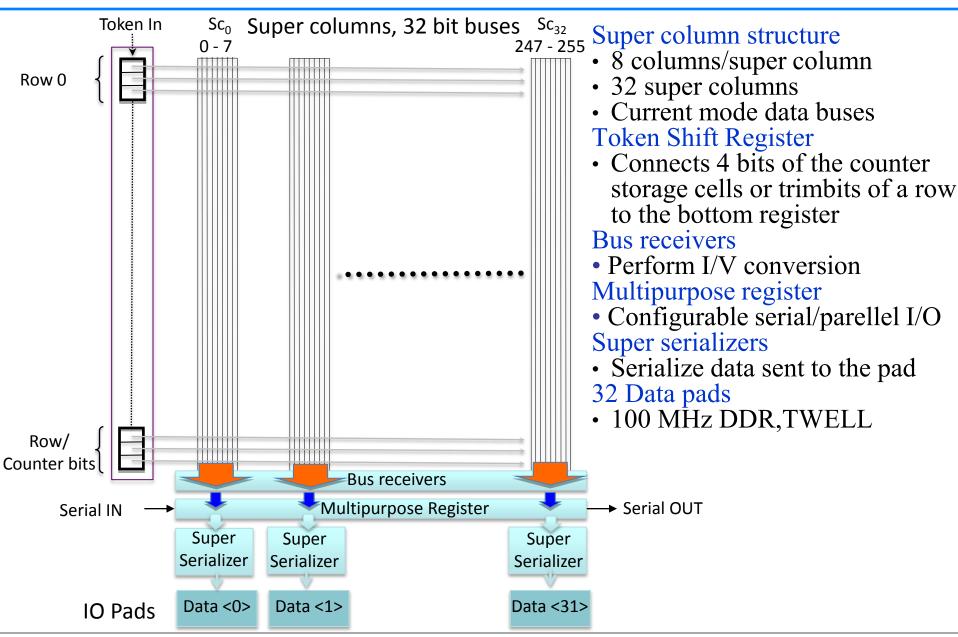

| Counter                               | <b>12 bits, binary, configurable (4,8,12 bit mode), double buffered</b>                                      |  |  |  |

| Continuous readout                    | yes                                                                                                          |  |  |  |

| Detector readout speed                | ~11 KHz @ 8 bit mode, (22 @ 4 bit)<br>Detector size doesn't matter<br>= up to ~2000 x<br>(Clock=100 MHz DDR) |  |  |  |

| Threshold adjustment                  | 6 bit DAC                                                                                                    |  |  |  |

| XY-addressable analog out for testing | yes                                                                                                          |  |  |  |

| Overflow control                      | yes                                                                                                          |  |  |  |

Both the chip and the readout electronics were totally redesigned, and almost all chip blocks are on silicon for the first time.

Project start: 02.2005, chip design as a one man project

# The EIGER pixel

V

The EIGER pixel on silicon

Roberto Dinapoli, PIXEL 2012

PAUL SCHERRER INSTITUT

PAUL SCHERRER INSTITUT

## **EIGER readout architecture**

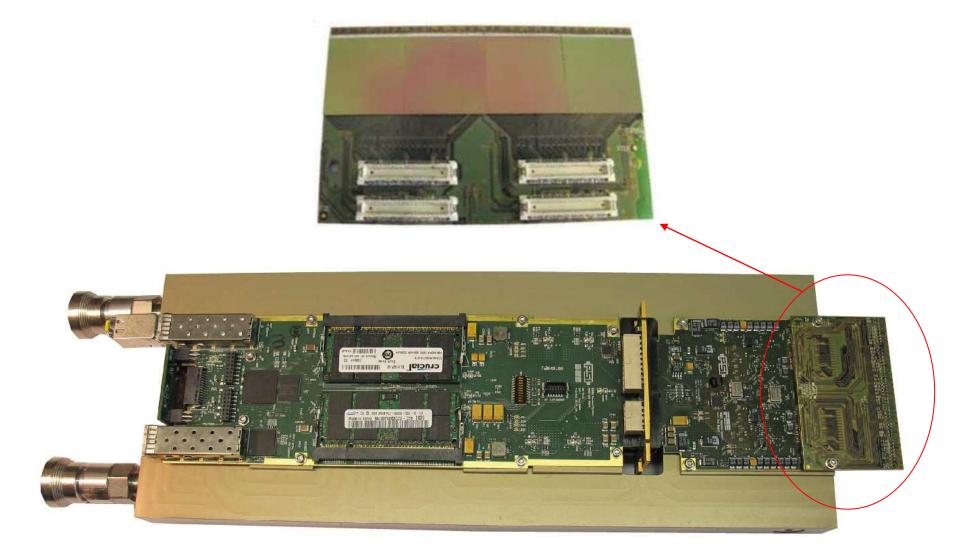

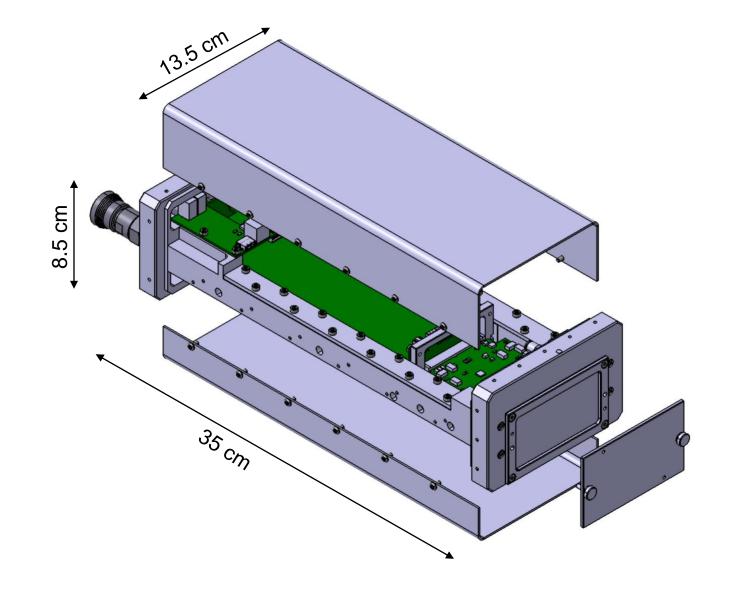

## Single chip test setup

• Pattern generator • Python scripts **1Gb Ethernet Data Link** • Full Detector control GUI ...... **Chip Adapter Board** EGE **IPG**

ALL WAFERS FROM FIRST FOUNDRY LOT WERE OFF SPECS! Vth-P +100mV off, Vth-N +60mV off the nominal value. We received 4 replacement wafers (for free, LOT 2) which meet the specs (and work much better) PAUL SCHERRER INSTITUT

# Single chip calibration plan

## The samples

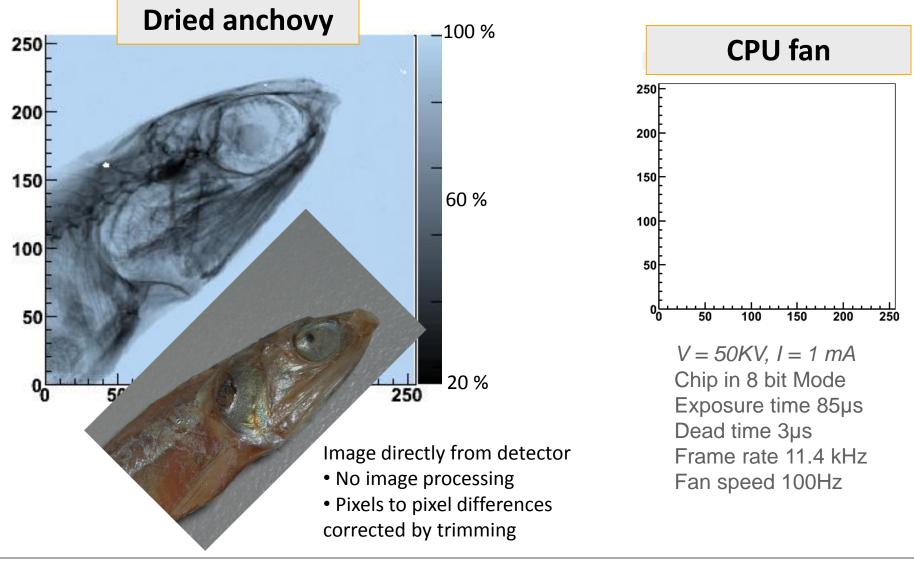

several single chips tested with an XRay tube and Fluorescence samples for Trimming and Calibration.

1 chip tested at the PSI-Optics

beam line in two different periods (25-27/02/2011 and 17-21/03/2011). E=10-16KeV

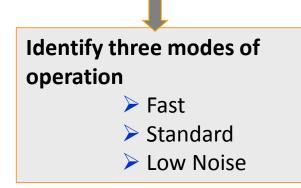

Start with DACs settings from simulation Optimize the DACs Define a threshold trimming procedure Measure different detector characteristic

Single Chip Calibration Plan

- Energy calibration

- Noise

- Threshold dispersion

- Rate Capability

- Minimum Energy

- Radiation tolerance

**Irradiation tests** performed at the beam line with LOT 2 show that the chip is still operational after several tens of Mrad with minor re-biasing

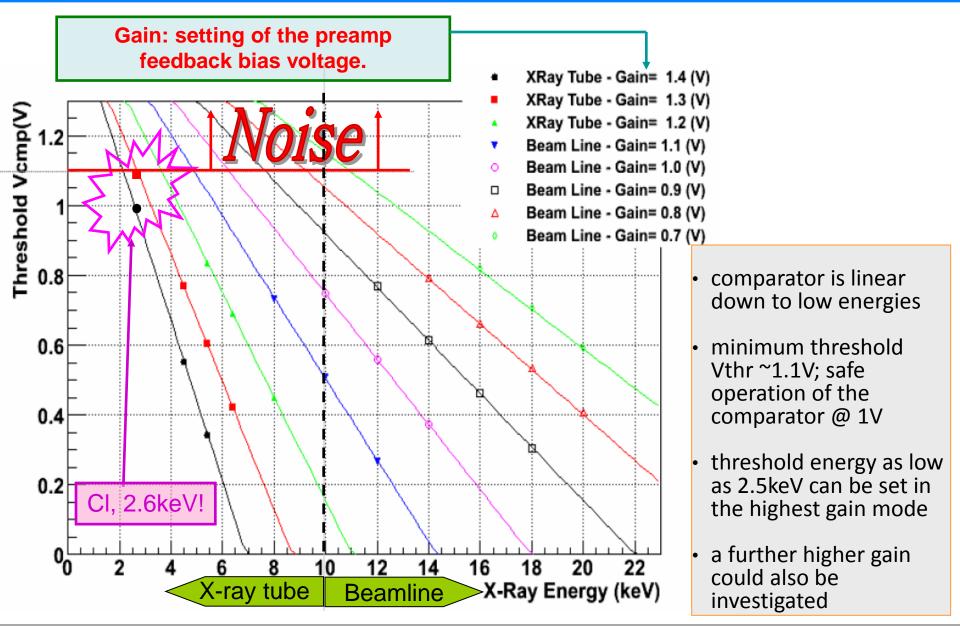

## Threshold calibration and low energy operation

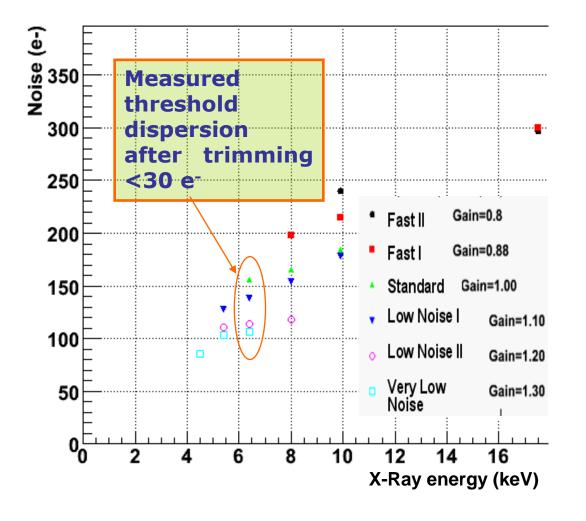

The plot shows the noise performance as a function of the photon energy for different preamp settings. In "very low noise" mode the chip has a noise of ~100 e-. Threshold dispersions of <30 ewere also measured. PAUL SCHERRER INSTITUT

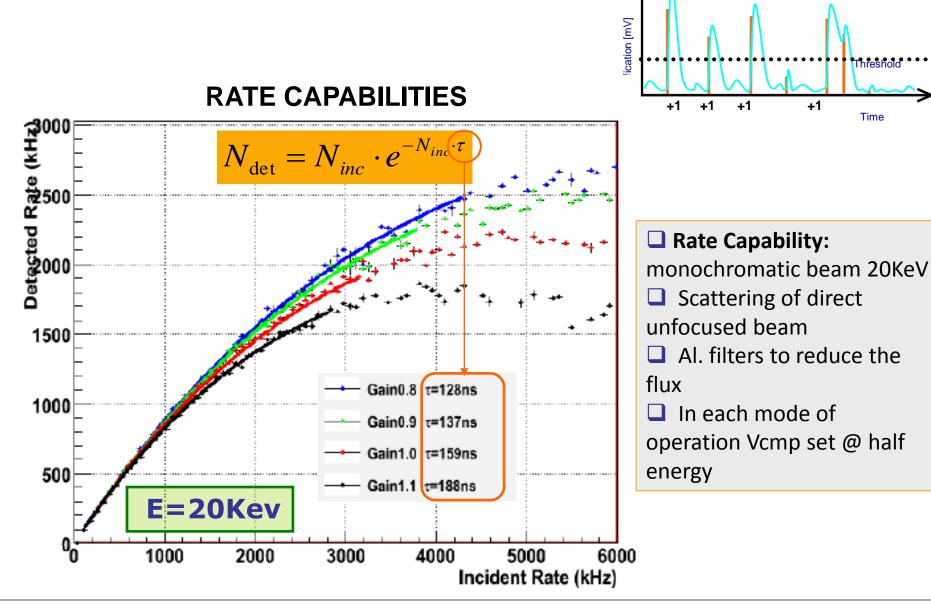

## **Rate Capability**

## **Eiger Calibration**

PAUL SCHERRER INSTITUT

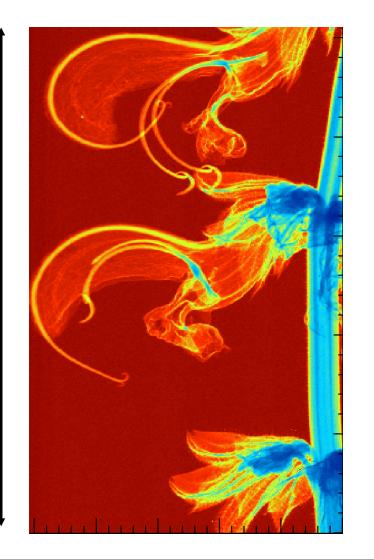

# Investigating colloidal suspensions with Eiger

Roberto Dinapoli, PIXEL 2012

Analysis: Ian Johnson <sup>19</sup>

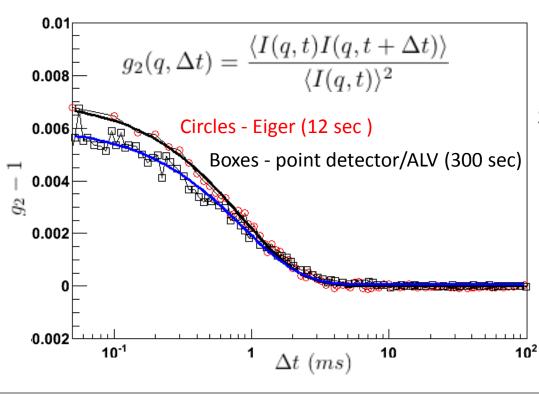

# Probing the dynamics, Photon Correlation Spectroscopy

Eiger fast frame rate:

Second long exposure series @ 20 kHz 45 us exposure and 5 us dead time between frames

Intensity Fluctuations to probe the dynamics Intensity-Intensity Auto Correlation Function

$$g_2(q,\Delta t) = 1 + \beta |g_1(q,\Delta t)|^2$$

Normalized field correlation function

$$g_1(q,\Delta t) = e^{Dq^2\Delta t}$$

Brownian motion,

$$D = D_0 = \frac{kT}{6\pi\eta r}$$

PAUL SCHERRER INSTITUT

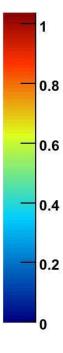

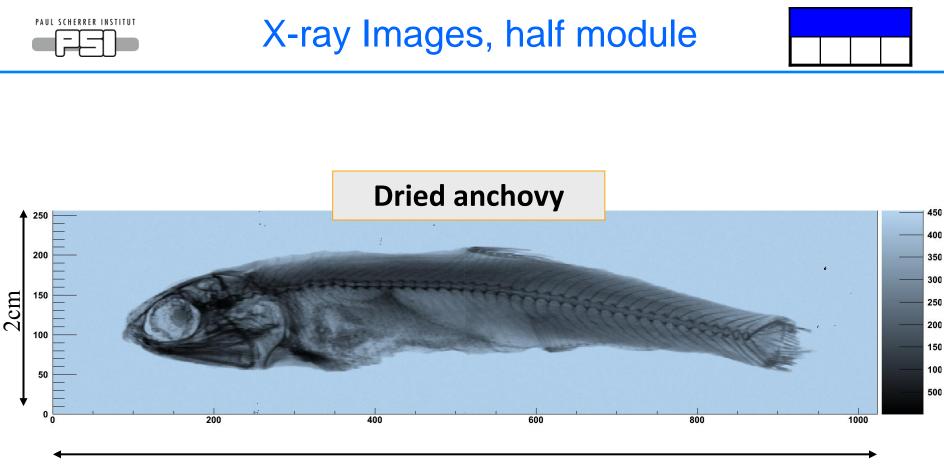

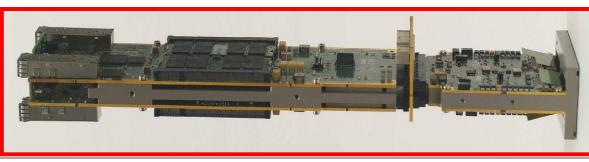

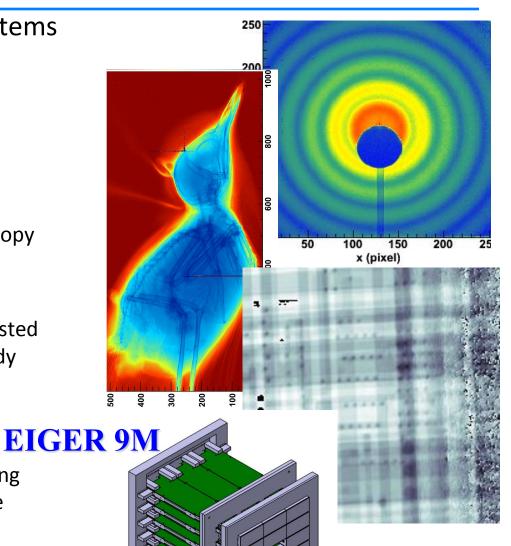

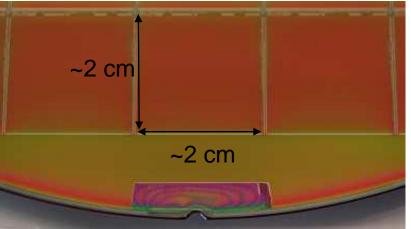

## Half Module System

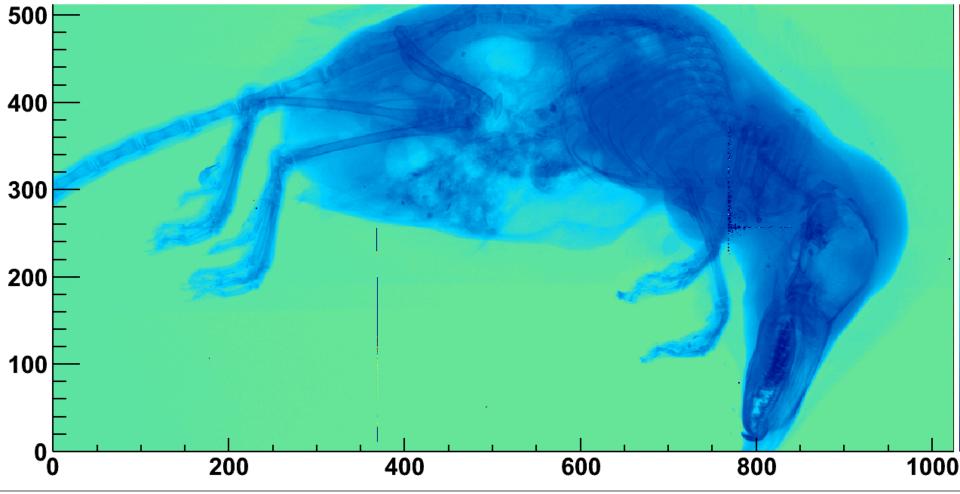

## Wild flower

#### No stitching, no trimming, with background correction

4cm

8cm

#### No stitching, no trimming, with background correction

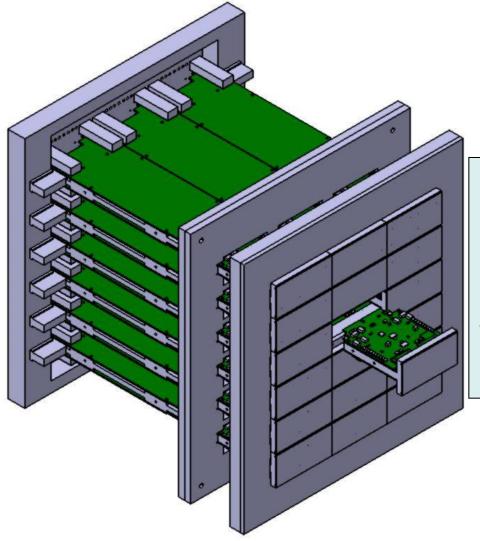

# **Full module**

500 k pixel Modules

- 38 X 77 mm<sup>2</sup> Sensitive area (Pilatus size)

- Parallel readout on half module base

- 8 GB on module data storage

- Front and Backend Boards

- Boards have been produced and tested

- Firmware and software is under development, almost ready

- Full Module High Density Interconnect

- Flex PCB received and working

- Full module working!

- Bump bonding issues being addressed

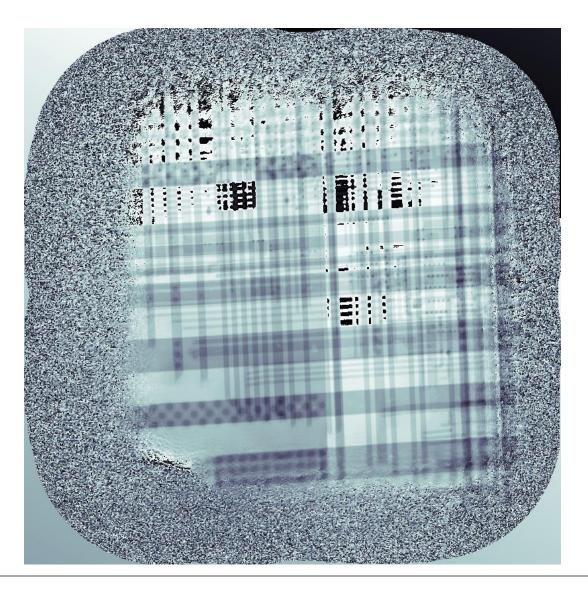

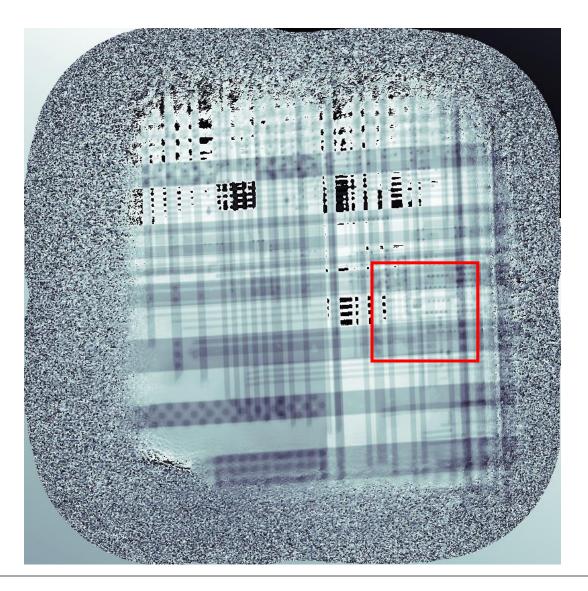

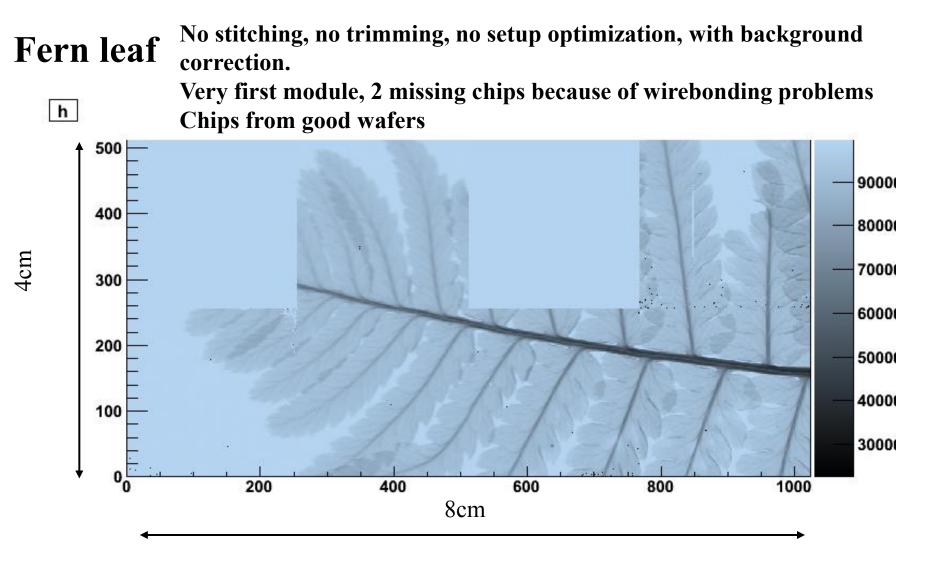

First working module after recovery from bump-bonding disaster.

No stitching, no trimming, no setup optimization, with background correction. New module.

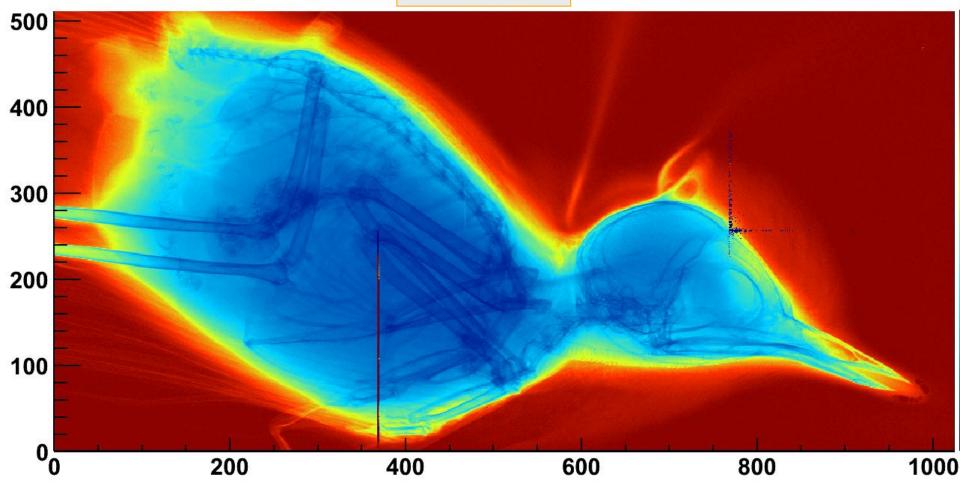

Shrew

First working module after recovery from bump-bonding disaster.

No stitching, no trimming, no setup optimization, with background correction. New module.

## Robin

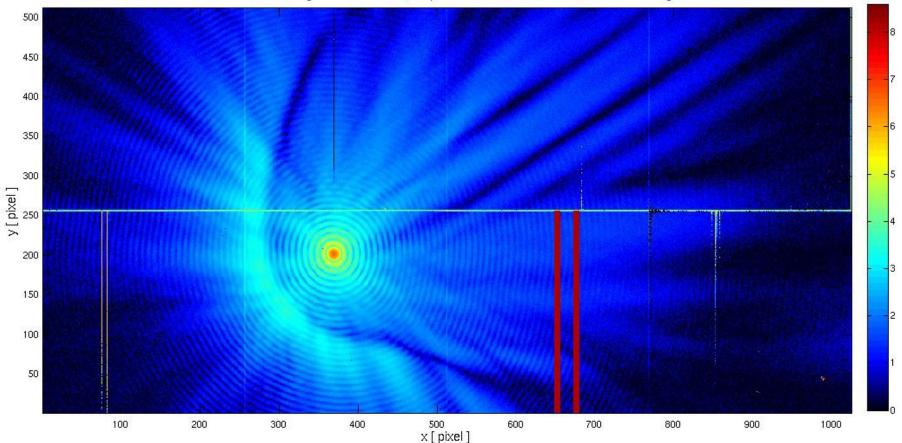

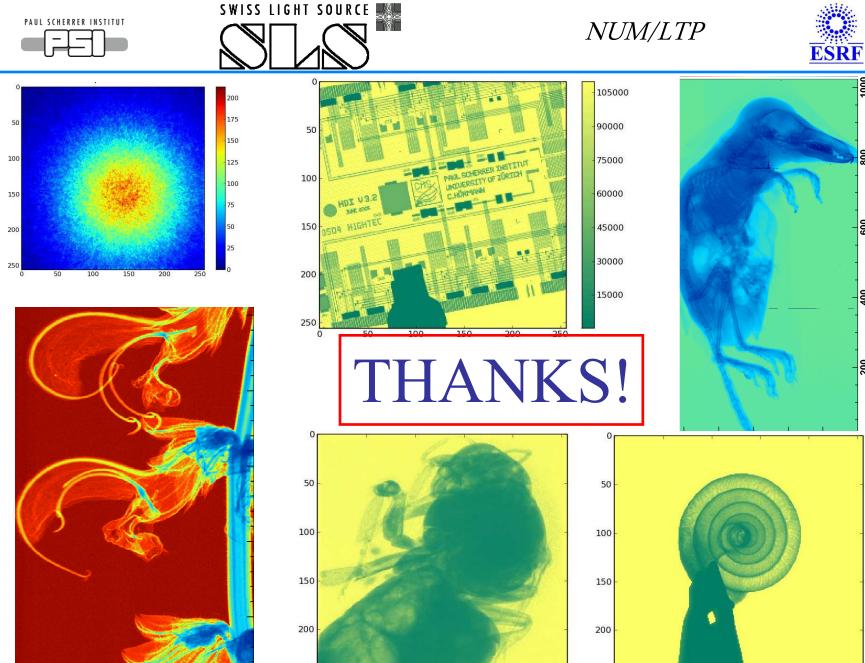

## Full module: first CSAXS experiment

#### **RAW DATA**

~/Data10/eiger/ct/e14169\_1\_ct\_000031.h5 (log.) 19:22:47 file date: 15-Aug-2012 19:20:43, exposure time = 1.000 sec, frame average

## **Full module: first CSAXS experiment**

## Phase contrast image of a small area of a Pentium IV

## **Full module: first CSAXS experiment**

## Phase contrast image of a small area of a Pentium IV

## Phase contrast image of a small area of a Pentium IV

PAUL SCHERRER INSTITUT

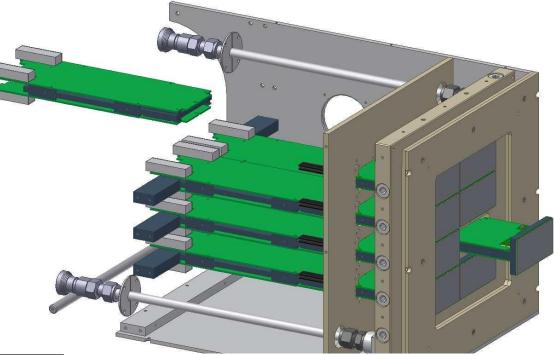

# EIGER 500k

Area: 23x23cm<sup>2</sup>

Number of pixels: 9 million

Frame rate: up to 23 kHz

Developed for SLS cSAXS

beamline

Total (raw) data rate: 900Gb/s

# Conclusions

- We have a few Single chip test systems

- High bump bond yield

- The Eiger chip is operational

- First x-ray images

- Achieved a 22 kHz frame rate

- First experiments

- Time resolved

- X-ray Photon Correlation Spectroscopy

- We are working towards modules

- Front and Backend Boards

- Boards have been produced and tested

- Firmware and software almost ready

- Half module system

- Half module system is working

- Full Module

- Flex PCB (HDI) produced and working

- First images taken with a prototype

- First CSAXS experiment done

- Bump bonding problems being addressed

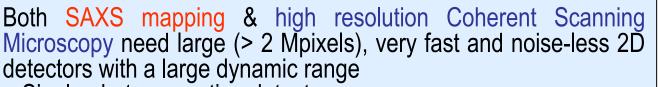

- EIGER 9M prototype in early production phase

Roberto Dinapoli, PIXEL 20

# ACKNOWLEDGMENTS

#### Many thanks to:

Anna Bergamaschi, Heiner Billich, Beat Henrich, Dominic Greiffenberg, Roland Horisberger, Ian Johnson, Dhanya Maliakal, Beat Meier, Aldo Mozzanica, Peter Oberta, Lukas Schaedler, Nick Schlumpf, Elmar Schmid, Bernd Schmitt, Xintian Shi, Akos Schreiber, Anja Schubert, Silvan Streuli, Dominic Suter, Valeria Radicci, Gerd Theidel.

**SLS Detector Group**

Roberto Dinapoli, PIXEL 2012

# **BACKUP SLIDES**

•Count rate: 1MHz/pixel (1.8 x 10<sup>8</sup> x-rays/mm<sup>2</sup>/s) •100 MHz DDR readout (PII:100 MHz) Max. frame exposure time before overflow: • $T_{ro}$  @ 4 bit mode = 40.96 µs • $T_{ro} @ 8 bit mode = 81.92 \ \mu s$ • $T_{max}$  @ 4 bit mode = 16 µs •T<sub>max</sub> @ 8 bit mode = 256 µs • $T_{ro}$  @ 12 bit mode = 122.9 µs • $T_{max} @ 12 bit mode = 4 ms$ •In continuous readout mode, max. frame rate=1/readout time; 12.5 KHz @ 8 bit mode **Pilatus II: Pilatus II:** •100 MHz LVDS readout •Same count rate  $\cdot T_{ro} = 1.2 \text{ ms}$ •T<sub>max</sub> is about a second •BUT: Detector frame rate 5-10 Hz (but no continuous readout!)

>1000!!

# Requirements for an ideal detector

- Single photon counting detector

- Modular detector system

- Parallel data transfer architecture

Smaller pixels will allow larger aperture and better statistical sampling

of coherent diffraction patterns (172 micron pixel are 'at the edge')

- Small pixel size

- No spatial distortion and uniform response

Scanning now usually done with a dead time of 50%

- Fast Frame Rate

- Simultaneous exposure and readout

- Negligible dead time

There is enough flux to go 10 to 100 times faster (depending on sample)

High count rate of incoming photons

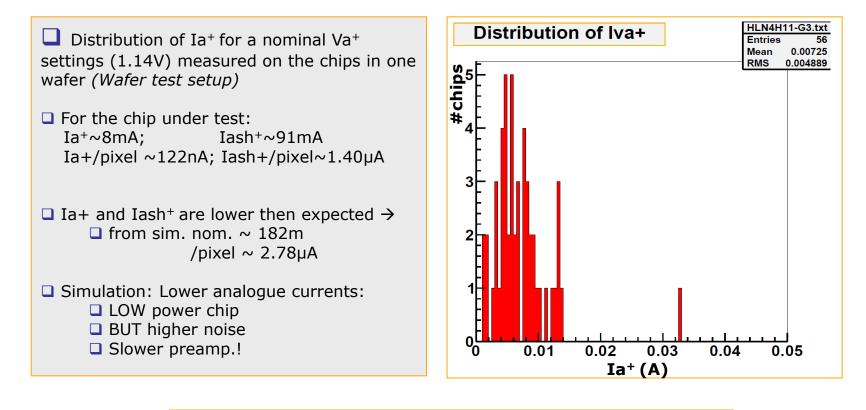

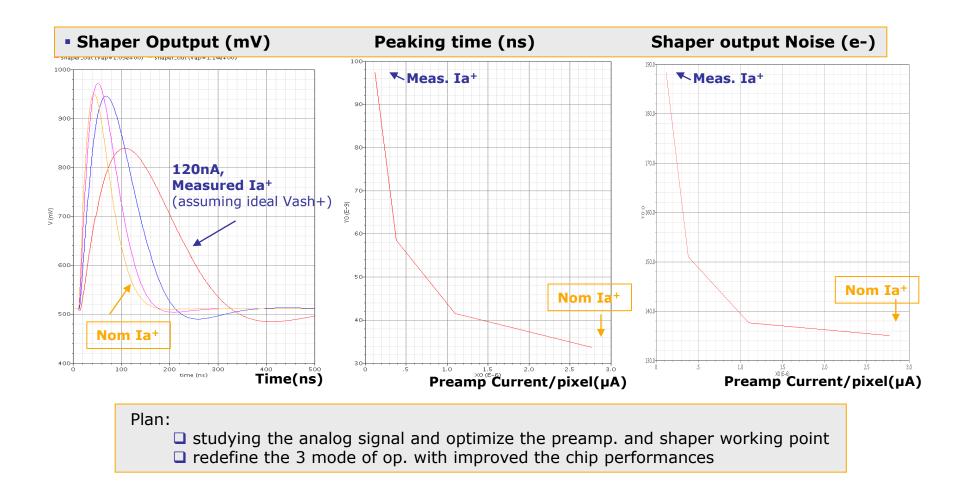

The present configuration can be defined as "LOW POWER" chip!

- EIGER: 2.8+1.4+1.4 uA \*256\*256 = 5.6 uA \* 65536 = 0.367 A (=1.43 mA/col) 2.8\*1.14+(1.4+1.4)\*2 \*256\*256 = 8.8 uW \*65536 = 0.576 W (=0.156 W/cm<sup>2</sup>)

- PII: 4.6+4.6+3.6 uA \*60\*97 = 12.8 uA \* 5820 = 75.5 mA (=1.26 mA/col) (4.6+4.6)\*1.2 +3.6\*2.5 \*60\*97= 20 uW \* 5820 = 0.117 W (=0.068 W/cm<sup>2</sup>)

PII: 517 transistors/pixel 3M transistors in the matrix Transistor density: ~13um<sup>2</sup>/transistor (with TWELL) (~12um<sup>2</sup> in the digital section)

PII: 57.2 um<sup>2</sup>/transistor (without TWELL) Actual transistor density improvement: 4.4x+TWELL

## Short EIGER history

Design started: 02.2005

- $\rightarrow$ Design supervision: almost none

- →Software and system management support: almost none

Tape-out to EUROPRACTICE: 26.02.09

->>Almost all chip blocks are on silicon for the first time

•First wafer (with some parameters off-specs) received back from foundry: 03.06.09 •Testing started: 10.06.09, the chip is not "smoking" •First image with a Strontium source: 24.08.09 •First "high quality" image: 02.09.09 •First time at a beamline: 11.09.09 •First maximum speed x-ray movie: 28.09.09 •First wafer map: 23.08.10 •First real experiment at a beamline: xx.xx.11 •First 2 chip image:17.05.11 •First half module image •First full module image: 21.10.11 •First experiment at a beamline with a module: 15.08.12

## First conference proceeding paper (ELBA '09):

#### "A new family of pixel detectors for high frame rate X-ray applications" Nuclear Inst. and Methods in Physics Research, A

#### DOI information: 10.1016/j.nima.2009.10.043

## **EIGER 4M**, four million pixel detector

|           | Chip Specification |  |  |  |  |

|-----------|--------------------|--|--|--|--|

| Columns   | 256 per Chip       |  |  |  |  |

| Rows      | 256 per Chip       |  |  |  |  |

| Bits      | 8 per Pixel        |  |  |  |  |

| Framerate | 12 000 Hz          |  |  |  |  |

<sup>1)</sup> 1 Gbit / s = 10<sup>9</sup> bit / s <sup>2)</sup> 1 MByte / s = 1024 \* 1024 \* 8 bit / s

|             | Detector Specification |       | Data Size |            | Data Rate |                        |                         |

|-------------|------------------------|-------|-----------|------------|-----------|------------------------|-------------------------|

|             | Modules                | Chips | Pixel     | Bit        | Byte      | Gbit / s <sup>1)</sup> | MByte / s <sup>2)</sup> |

| Chip        |                        | 1     | 65 536    | 524 288    | 65 536    | 6.3                    | 750                     |

| Half-Module | 0.5                    | 4     | 262 144   | 2 097 152  | 262 144   | 25.2                   | 3 000                   |

| Module      | 1                      | 8     | 524 288   | 4 194 304  | 524 288   | 50.3                   | 6 000                   |

| 4M Detector | 8                      | 64    | 4 194 304 | 33 554 432 | 4 194 304 | 402.7                  | 48 000                  |

| 9M Detector | 18                     | 144   | 9 437 184 | 75 497 472 | 9 437 184 | 906.0                  | 108 000                 |