## Micron Pixel sensors for HL-LHC

The University of Liverpool, UK

Phil Allport, Gianluigi Casse, Paul Dervan, Dean Forshaw,

Ilya Tsurin

The University of Glasgow, UK

Richard Bates, Craig Buttar

#### **OUTLINE**

- First results with ATLAS upgrade FE-I4 sensors produced at Micron Semiconductor

Ltd

- Over view of FE-I4 chip

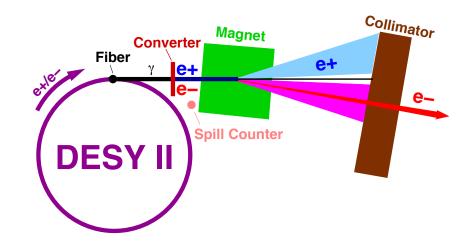

- DESY test beam setup

- Test beam results look at efficiency as a function of sensor threshold and sensor bias voltage

- look at cluster size and ToT (Time over Threshold) distributions

#### FE-I4 Motivation

#### HL-LHC two-fold upgrade:

Phase0 (IBL)- Insertable B-Layer

Radiation Hard up to 5<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>

IBL installation 2013-2014

The FE-I4 chip is important for ATLAS's continued operation for HL-LHC. Due to the higher data transfer rates to deal with increasing pile up, increased radiation tolerance and increased granularity in the inner detectors pixels layers

ATLAS Insertable B-Layer Technical Design Report - http://cdsweb.cern.ch/record/1291633/files/ATLAS-TDR-019.pdf

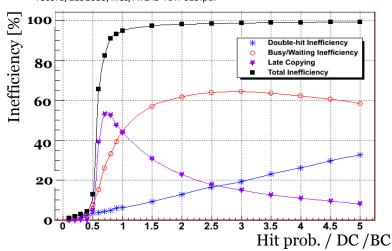

FE-I3 is unsuitable for IBL and HL-LHC due to high hit inefficiency's shown above,

The expected occupancy in the Blayer central module at  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>

is 0.6 hits/DC/BC at IBL radii

inefficiency increases to >90%

# FE-I3 vs FE-I4 comparison

Target specifications

FE-I4 advantages are:

Reduced cost of sensor to FE chip bump bonding

Smaller feature size means more space for more complex circuit redundancy and therefore more radiation hard, important for HL-LHC operation

|                         | FE-I3                      | FE-14                     |

|-------------------------|----------------------------|---------------------------|

| Pixel Size              | 50 x 400μm²                | 50 x 25μm²                |

| Pixel Array             | 18 x 160                   | 80 x 336                  |

| Chip size               | 7.6 x 10.8 mm <sup>2</sup> | 20 x 18.6 mm <sup>2</sup> |

| Active fraction         | 74%                        | 89%                       |

| Analogue Current        | 16μA/pixel                 | 10μA/pixel                |

| Digital Current         | 10μA/pixel                 | 10μA/pixel                |

| Analogue supply voltage | 1.6V                       | 1.5V                      |

| Digital supply voltage  | 2.0V                       | 1.2V                      |

| Data rate               | 40Mb/s                     | 160Mb/s                   |

[1] Development of the ATLAS FE-I4 pixel readout IC for b-layer Upgrade and Super-LHC, http://siliconlab.physik.uni-bonn.de/fileadmin/Publications/ATLAS\_Pixels/Karagounis\_FE-I4\_p70.pdf

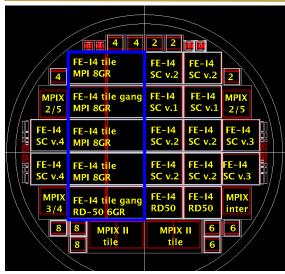

#### Micron FE-I4 sensor wafers

# 8 tile tile 6 8 gang. pix. 400um edge 2x2 2x2 2x2 2x2 300um edge 400um edge 400um edge 2x2 2x2

#### Micron pixel II

Has multiple versions of FE-I4 compatible sensors:

FE-I4 SC v.4 = Live FEI4 MPI Guard IBL Slim Edge

FE-I4 SC v.3 = Live FEI4 MPI Guard IBL Slim Edge ganged pixels

FE-I4 SC v.2 = Live FEI4 MPI Guard IBL ganged pixels

FE-I4 SC v.1 = Live FEI4 MPI Guard IBL

FE-I4 RD50 = Live FEI4 RD50 Guard IBL ganged pixels

#### Micron pixel IV

Has HL-LHC FE-I4 variant designs

Quad FE-I4 large area sensors, with 4-8 ganged pixels and slim edge variants

Surrounded by FE-I4 single area sensors, variants include 500x25um pixel sensors, ganged pixels and slim edge devices

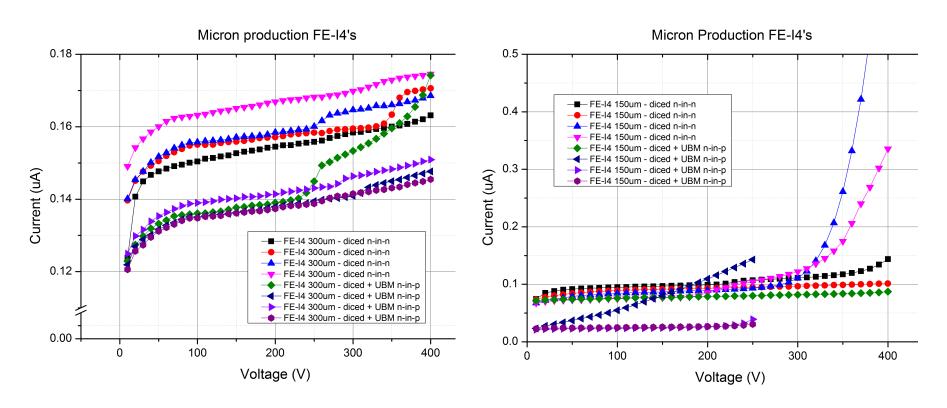

# Micron production sensor IV's

Un-diced standard FE-I4 IBL GR 450um edge sensors tested on wafer at Micron, and devices with UBM tested at VTT.

All 300um devices look good, handling issues with 150um silicon causes higher leakage currents with sensors around outside of wafer.

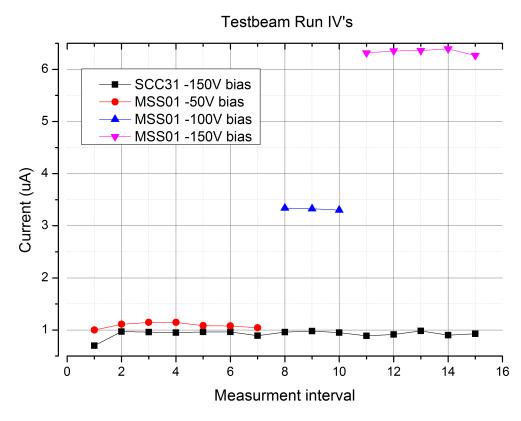

# SCC31 vs MSS01 leakage currents

This is still well below the 100nA per pixel for upgrade purpose's but pre selected sensors will provide better IV's in future

The sensor used for MSS01 was not pre selected for best IV characteristics

MSS01 has a consistantly higher leakage current than SCC31.

MSS01's leakage current is stable at all voltages

At -50V MSS01 leakage current per pixel is ~3.7-3nA using 1uA total leakage current

At -100V MSS01 leakage current per pixel is ~ 1.2nA on average

At -150V MSS01 leakage current per pixel is ~ 2.2nA on Average

#### Test beam information

Test beam performed using the EUDET telescope at DESY, Hamburg, Germany

EUDET telescope features 6 CMOS pixel tracking planes

4GeV Positron beam used, maximum of 6GeV with low trigger rate

Only 2 DUT's mounted within the telescope due to large multiple scattering effects

Telescope trigger rate ~1kHz

See Link for more information:

http://adweb.desy.de/home/testbeam/WWW/Description.html

# Sensors being discussed

#### Sensors we are going to discuss:

- 1x n-in-n assembly from Dortmund used as a reference to compare operation to an existing working device from a different vendor (CiS).

- 1x n-in-n assembly, sensor produced by Micron, FE chip and sensor bumped by IZM

#### Other sensors from test beam:

- 1x n-in-n assembly, sensor produced by Micron,

FE chip and sensor bumped by IZM

- 1x n-in-p assembly, Sensor produced by Micron,

FE chip and sensor bumped by IZM

Data has not been reconstructed for these devices

#### **Run Conditions**

Threshold and bias scans had preference over tilting the sensor in R and Phi because of large multiple scattering of positron beam due to material budget of sensor support and EUDET telescope, as well as the low energy of beam.

Over 2 million events were collected for each run condition

Tilted runs for all sensors in R and Phi still being reconstructed

SCC31 – Borrowed from Dortmund, was ran at 3200e and -150V for all run conditions.

MSS01 – Micron assembly, was ran with the following run conditions

- Thresholds measured were: 3200e, 1600e, 1400e, 1200e, 1000e (1600e runs have not been reconstructed, and won't be discussed)

- Bias Voltages: -50V, -100V, -150V were ran for each Threshold listed above.

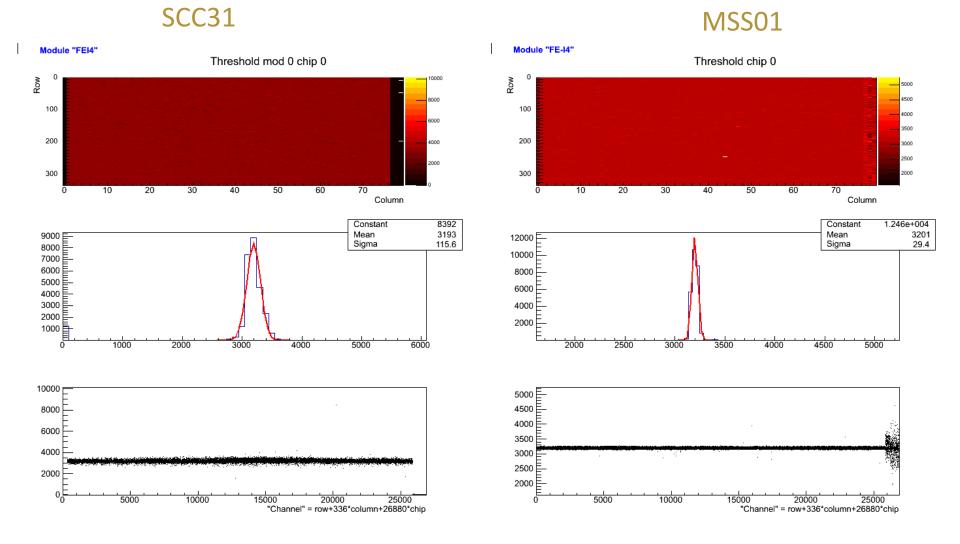

# SCC31 vs MSS01 3200e tuning

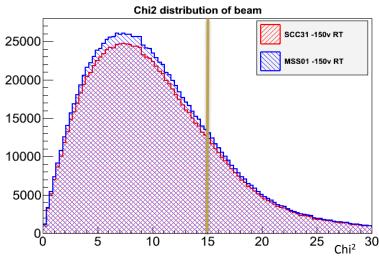

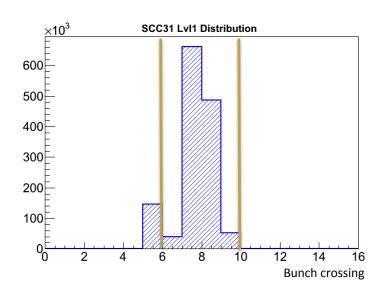

## Important Analysis cuts

#### Cut of 15 applied to the chi<sup>2</sup> of all tracks

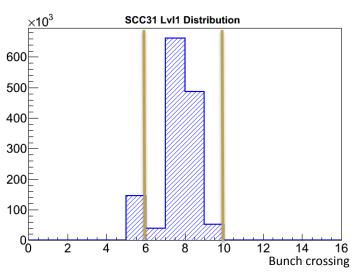

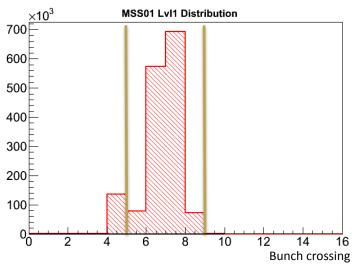

Different LVL1 windows where used because the peaks were not in the same position for each DUT, choosing a window 1-2 bins either side of the center of the distribution means that fewer noisy pixels are included in clustering

SCC31 – cuts applied to LVL1 distribution of matched hits, between 6-10 bunch crossings

MSS01 – cuts applied to LVL1 distribution of matched hits, between 5-9 bunch crossings

50

10

20

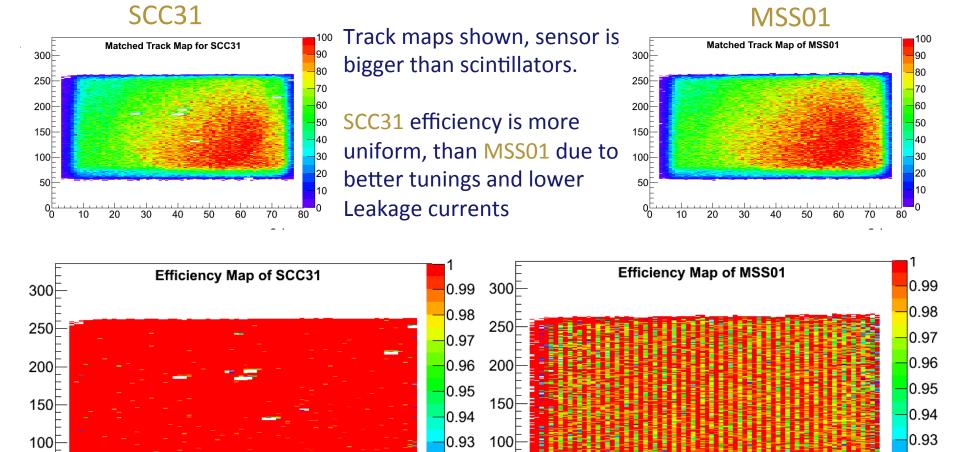

## SCC31 vs MSS01 3200e -150V

0.92

0.91

0.9

80

60

50

0.92

0.91

0.9

70

60

50

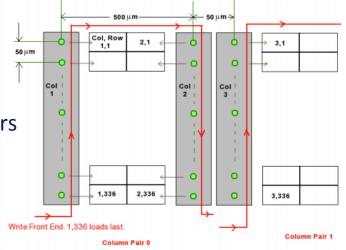

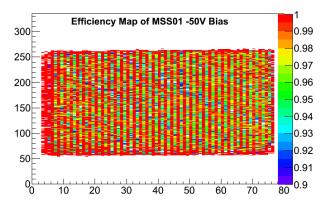

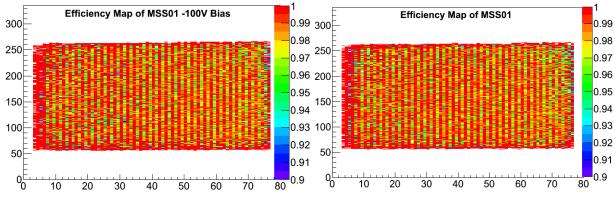

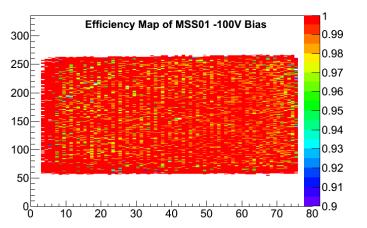

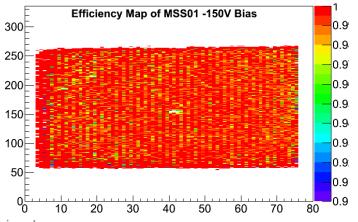

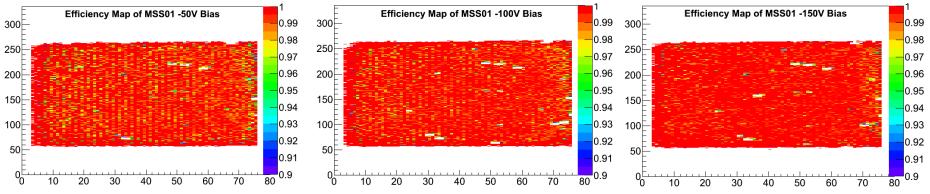

# MSS01 double column efficiency issue

As seen in previous slide, MSS01's efficiency map has a strange regular pattern constant, throughout the pixel structure. This structure is seen in all Efficiency maps for MSS01 we will be talking about in this talk, and the pattern is not seen on the efficiency map for SCC31.

The regularity of this pattern suggests that the issue is coming from the FE side rather than the sensor side.

The FE-I4 is read out in double columns using shift registers

This effect has been seen in previous test beams by other institutes, this effect is rare and is poorly understood.

This effect has been found to be HV and threshold independent, with an efficiency drop of about 2-4% in the last of the 2 columns.

Effect is likely caused by the FE chip itself, the readout (USBpix) or a combination of both. The most likely cause is a miscommunication between the FE and readout, where the low voltage supplied to the FE chip is too low.

This effect has gone away in previous test beam data where the USBpix has been restarted and power cycled.

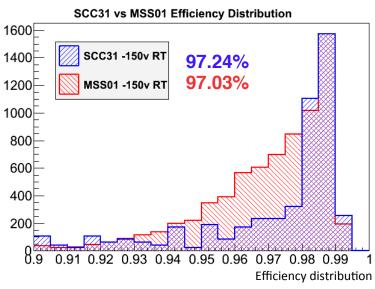

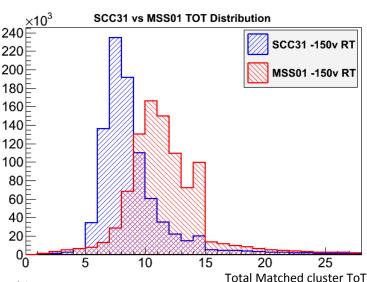

#### SCC31 vs MSS01 3200e

DUT's tuned to different specifications, because of this the efficiency distribution histogram has been scaled so that the efficiency distribution of both DUT's is easy to see, this has not impacted on the quoted efficiency values.

MSS01 shows a broader range of efficiencies across all active pixels >92% but has fewer pixels with Efficiencies <92% across full range

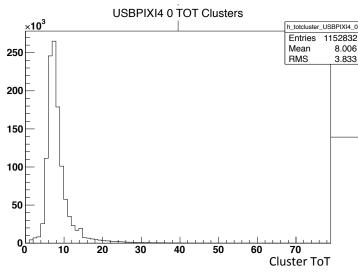

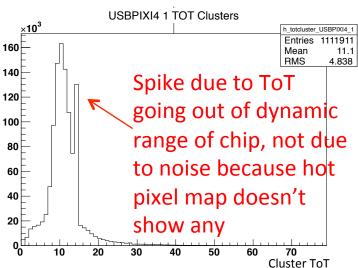

TOT distribution shows the TOT of Matched Clusters with tracks through EUDET

SCC31 Tuned to 8 TOT = 20,000e MSS01 Tuned to 10 TOT = 20,000e

ToT (Time over Threshold) value is calibrated the full expected charge collected by 300um thick silicon for a mip.

20

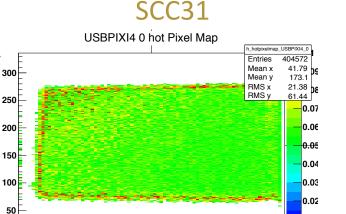

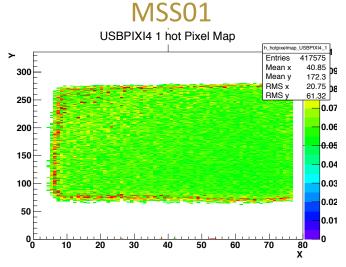

# SCC31 vs MSS01 online monitor

Where a 'hot pixel' is a pixel that has high noise, and will have considerably more hits than other pixels on average, this will display as bright red regions with an increased scale

0.01

80

MSS01's hot pixel map doesn't show any more noise than SCC31

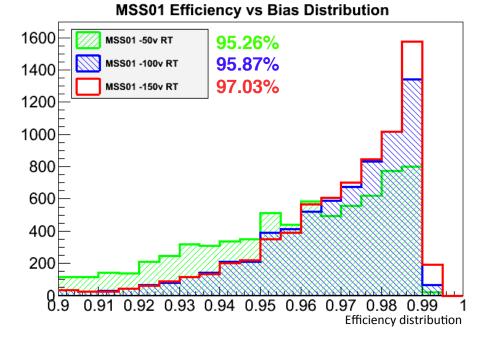

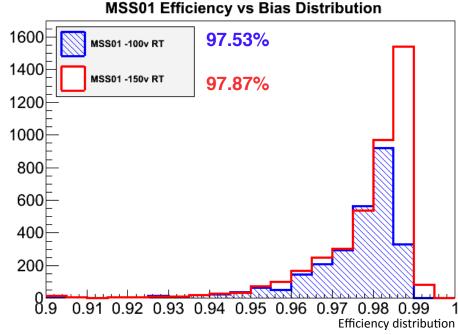

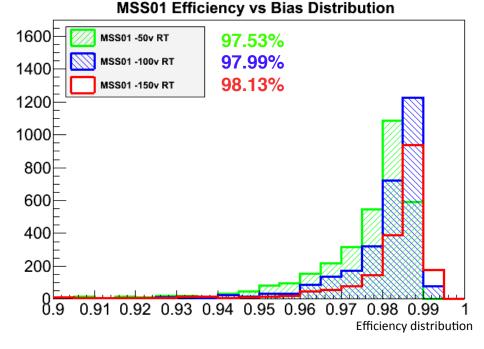

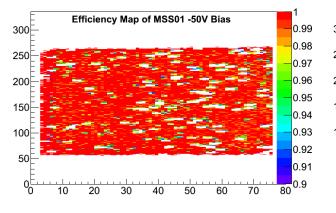

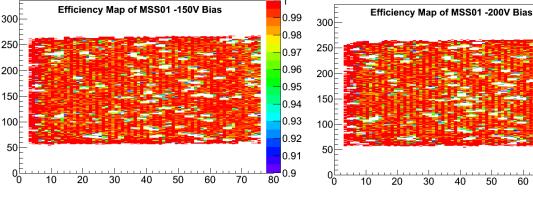

# MSS01 Efficiency vs Bias 3200e

- -50V MSS01 is under depleted

- -100V MSS01 is fully depleted (just)

- -150V MSS01 is over depleted, increased carrier mobility shows increase in efficiency

Efficiency maps (bottom) show increased pixel uniformity with increased Bias Voltage. Better tunings will show bigger differences

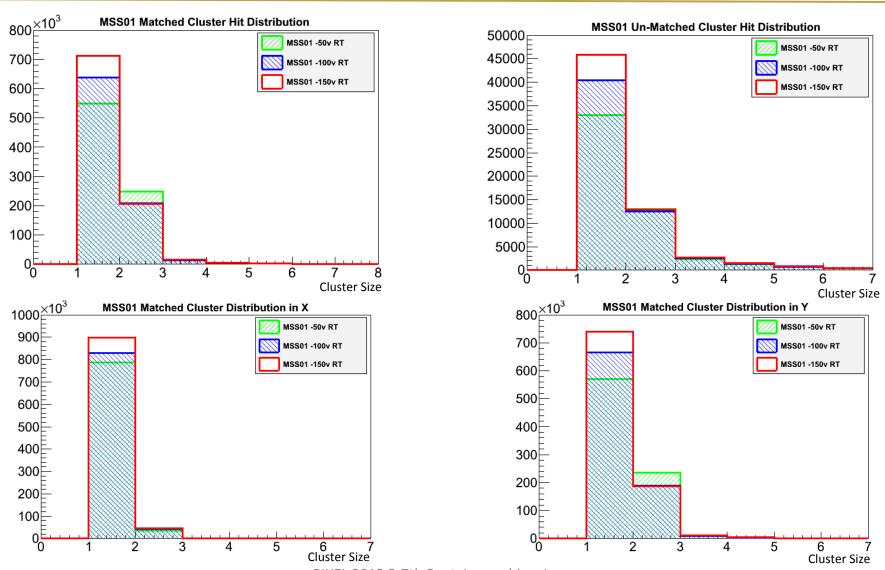

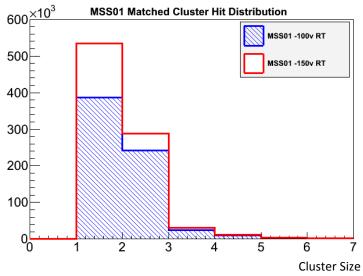

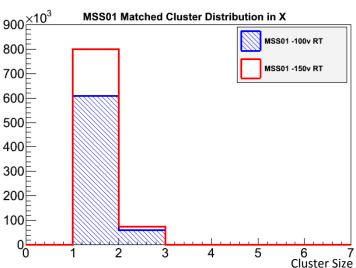

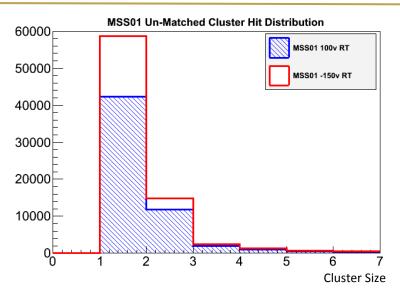

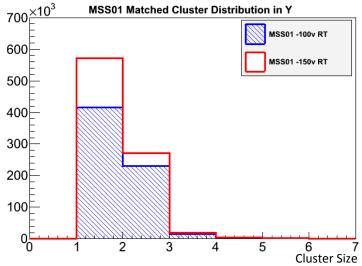

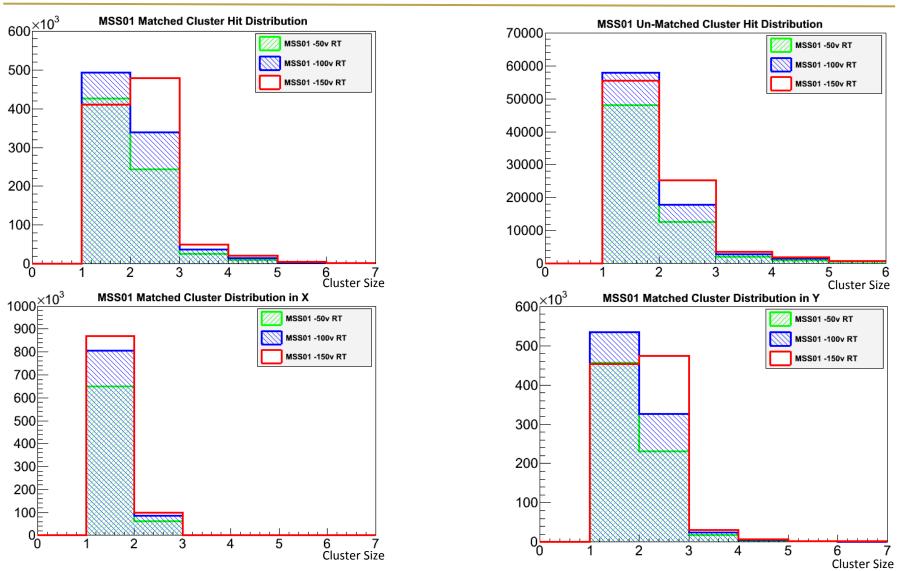

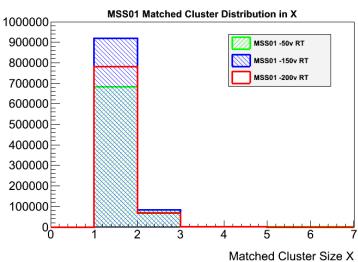

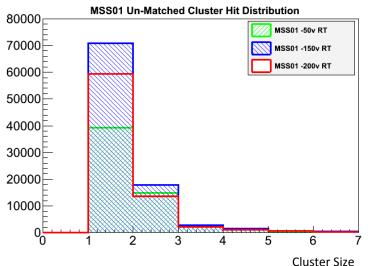

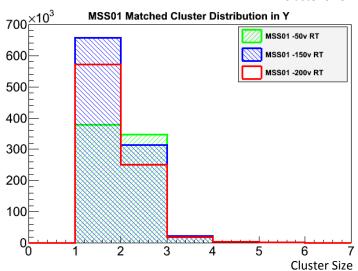

## MSS01 Cluster's vs Bias 3200e

PIXEL 2012 3-7th Sept, Inawashiro, Japan

# MSS01 Efficiency vs Bias 1400e

-50V data is still being reconstructed

MSS01 shows a smaller spread of pixel efficiencies than at 3200e

Noisy pixels don't appear to cause problems at this low efficiency, there are few masked pixels, and cluster distributions aren't adversely affected. Sensor appears to have a reasonable uniform efficiency.

PIXEL 2012 3-7th Sept, Inawashiro, Japan

## MSS01 Cluster's vs Bias 1400e

# MSS01 Efficiency vs Bias 1200e

MSS01 shows excellent efficiency at 1200e threshold, even under depleted

More hot pixels are masked as can be seen in Efficiency maps, number of masked pixels is negligible compared to the total number of active pixel 's

PIXEL 2012 3-7th Sept, Inawashiro, Japan

#### MSS01 Cluster's vs Bias 1200e

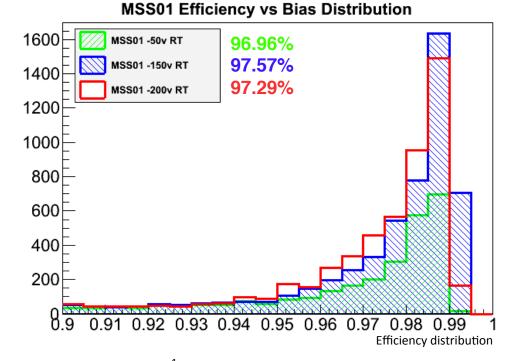

## SCC31 vs MSS01 1000e

MSS01 has more noisy pixels masked at 1000e Threshold

Efficiency still above 95% even when only half depleted at -50V

At -200V efficiency is reduced due to more noise in pixels at over double the depletion Voltage, and more noisy pixels masked

0.99

0.98

0.97

0.96

0.95

0.94

0.93

0.92

0.91

PIXEL 2012 3-7th Sept, Inawashiro, Japan

## MSS01 Cluster's vs Bias 1000e

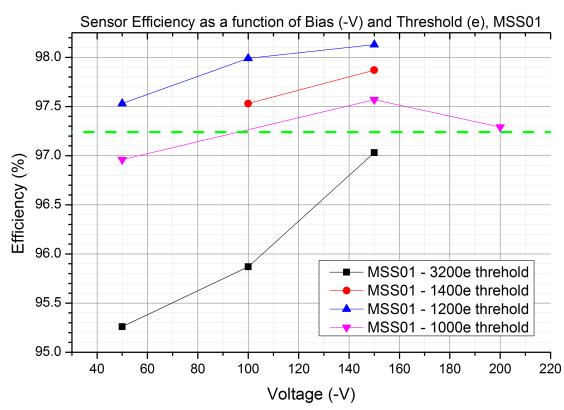

# **MSS01 Efficiency Overview**

Total sensor efficiency, has been shown to be very good.

Green line shows sensor efficiency for SCC31 at -150V and 3200e Threshold, used as a benchmark.

MSS01 efficiency is much lower than SCC31 at Depletion of 100V, over voltage (-150V) causing increased carrier velocity helps compensate.

Overall sensor performed with efficiencies over 95% even when under depleted (n-in-n)

Sensor efficiency can only improve, with future test beam data using high energy hadrons and with no readout issues causing poor double column efficiency

#### **Future And Conclusions**

Reconstruction of tilted runs in R, Phi and both for the samples discussed, as well as first fully functioning n-in-p Assemblies from Micron-IZM.

Assemblies where sent for Irradiation at CERN PS, characterization will begin when they are shipped back to us.

New pixel geometries have been tested in test beam, waiting for data reconstruction, pixel size 500x25um and slim edge devices <250um edges.

New Vendor (VTT) being trialed on newer production sensors

First Quad module going into test beam late September

First Micron Sensors have been tested in the test beam and preform well

# Backup – LVL1 distribution

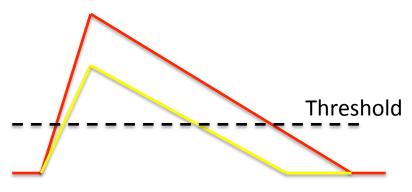

#### Injected charge dependence

When a trigger arrives 16 trigger windows, LVL-1-trigger signal will be read out in order to make sure that the entire signal is collected. The size of the signal influences the time the signal needs to rise above the threshold. The slope of a small signal is smaller than the slope of a larger signal. Therefore, a small signal appears to be a bit later than a large signal.

So signal outside the gold bands is most likely due to noise.