# 3D Electronics Development for Pixel Detectors

Marcel Trimpl, FNAL for the Fermilab microelectronics group

## <u>Outline</u>

- Motivation 3D

- Overview MIT-LL (VIP chip) and oxide bonding

- Present Tezzaron 3D Run

VICTR & VIPIC chip results

- Towards large arrays (Active Edge, Tiling)

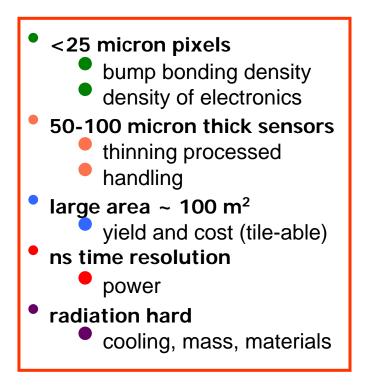

## Future Challenges for Pixel Detectors

We believe that technologies related to 3D integration can address many of these issues and enable a new generation of uniquely capable sensor systems

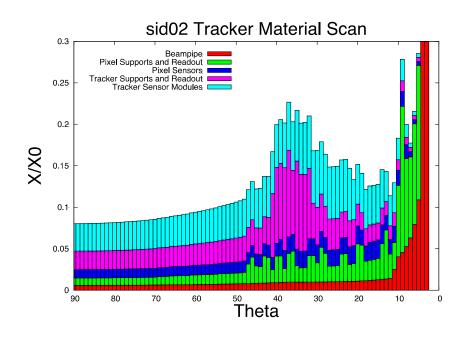

- Lepton Collider Vertex Detector precision

- Superb impact parameter resolution (  $5\mu m \oplus 10\mu m/(p \sin^{3/2}\Theta)$  )

- Transparency ( ~0.1% X0 per layer )

- • • Muon Collider processing to deal with harsh background environments

- 1-3 TeV muon collider on FNAL site

- Substantial Huge detector and radiation backgrounds

- Fast timing and high precision for background rejection

- • CLIC speed and precision

- ILC + ~ns time resolution

- • SLHC large scale, high speed, harsh environment

- 100-200 int/25 ns crossing, track trigger required

- On-detector background rejection

- • X-Ray Imaging speed and density

- Variety of challenges timing

- • • Intensity frontier

- Thin, fast electronics

## Fusion vs. Bump Bonding - Cost and Yield

#### fusion bonding

In our studies the most promising fine pitch bonding technology is the direct bond interconnect (DBI) process from Ziptronix:

- very fine pitch:

- 4 microns used for 3D Tezzaron wafers

- mechanical strength enables aggressive post-bond procedures: thinning, back implantation, laser annealing

- uses standard IC processes CMP and metallization

- can withstand high temperatures

- in principal: low cost

# p-substrate

[R.Ballabriga, CERN]

Current and projected costs and yields for sensor/readout integration technologies [1]

| Component             | Current or projected cost | Yield      | Comment                           |

|-----------------------|---------------------------|------------|-----------------------------------|

| Readout IC            | \$8/cm <sup>2</sup> [6]   | 65-70% [7] | Current 3D wafers and FEI4        |

|                       |                           |            | prototype yield                   |

| Active Edge Sensors   | \$53/cm <sup>2</sup>      | -          | Current cost for prototype        |

|                       |                           |            | 150 mm wafers                     |

| Silicon Strip Sensors | \$10/cm <sup>2</sup>      | 100%       | CMS tracker costs                 |

| Bump bonding          | \$213/cm <sup>2</sup>     | 98%[8]     | CMS forward pixel costs (2007)    |

|                       |                           |            | Yield $\equiv <20$ bad bumps/chip |

| DBI bonding           | 0.04/cm <sup>2</sup>      | 90%        | Projected by Yole Development [9] |

|                       |                           |            | for high volume production        |

| Target Costs (2020s)  | \$10/cm <sup>2</sup>      | 90%        | Assuming 200 mm sensor wafers     |

|                       |                           |            | and batch active edge process     |

#### classical bump bond

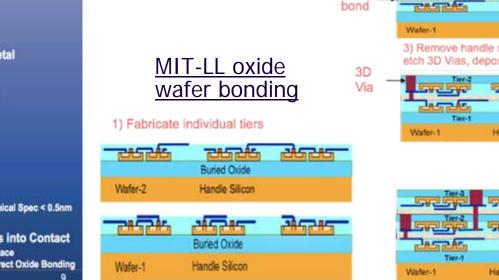

# Processes Explored

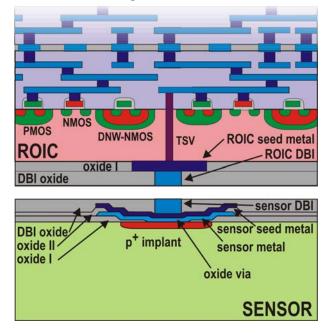

## Ziptronix Oxide Bonding

#### Tezzaron cu-cu bonding

#### 2) Invert, align, and bond wafer 2 to wafer 1

|               | S-helteW          | noolis2 elbneH                           |  |

|---------------|-------------------|------------------------------------------|--|

| Oxide<br>bond |                   | Buried Oxide                             |  |

|               | Wafer-1           |                                          |  |

| 3D            |                   | ndle silicon from w<br>deposit and CMP t |  |

| Via           |                   | - THE STR                                |  |

|               | Tier-1<br>Wafer-1 | Handle Sacon                             |  |

| Ter-3   |                | _ syassa_ |

|---------|----------------|-----------|

| STE STE | spiles -       | - 592572  |

| Tier-1  | TEASTEAS       | 245 245   |

| Wafer-1 | Handle Silicon |           |

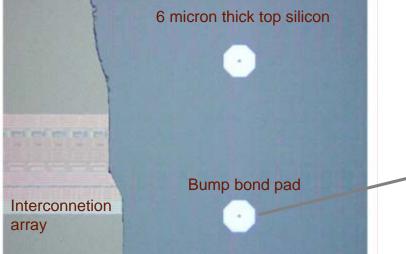

# Oxide Bond Demonstration

- Initial work was based on existing ROIC wafers from BTeV and sensor wafers from MIT-LL

- chip (sensor) to wafer (FPIX) bond

- Sensors thinned to 100 microns

-> 8 V depletion

- 100% connectivity on sensors without obvious bond voids

- No degradation in S/N

- Radiation hard to >10 MRad

- Process used with 3D wafers (iphone camera), planned for track trigger, active edge and x-ray imaging projects

# MIT-LL 3D Technology

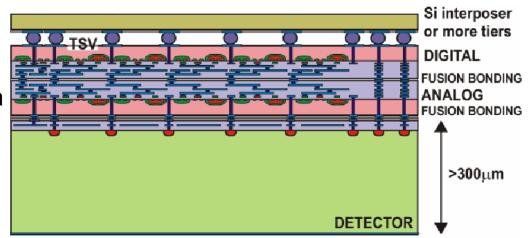

- MIT-LL had developed a 3D technology which seemed an excellent match to ILC needs

- Demonstrated 50 micron thick bonded sensor/readout (~0.1% radiation length/layer)

- 3 Tiers of 0.18 micron SOI CMOS

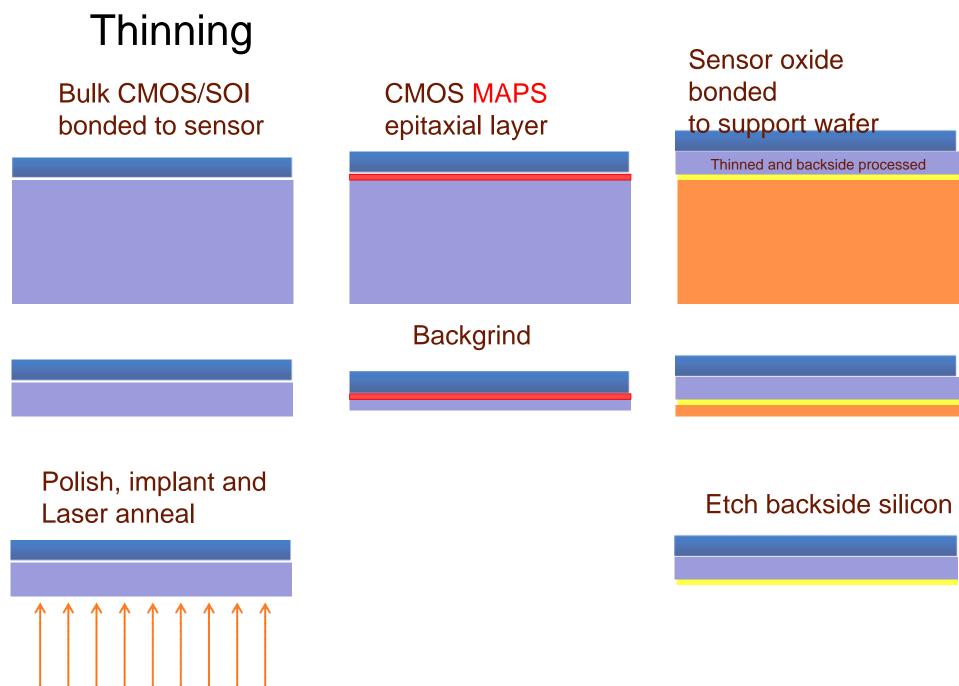

- Bonding, thinning and detector laser anneal technology

- We participated in 2 DARPA-sponsored 3D runs (2006/2009)

- Submitted the VIP ILC- vtxd chips (participated in improving the design kit)

## Micro Magic Pixel Layout

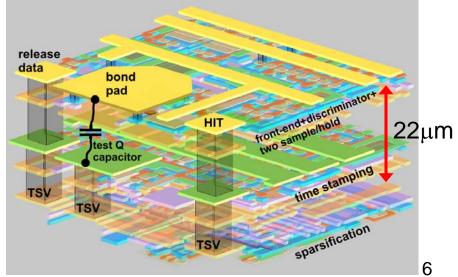

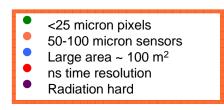

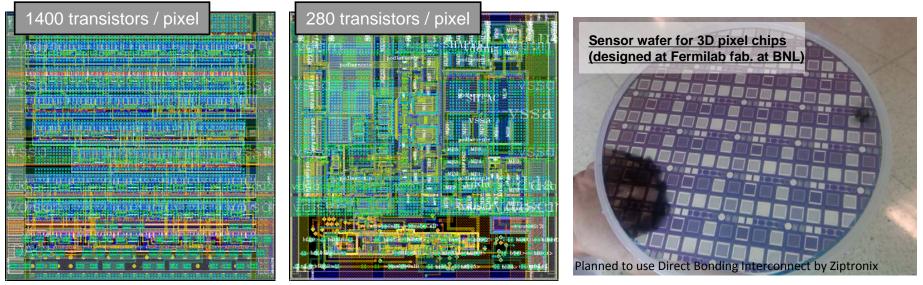

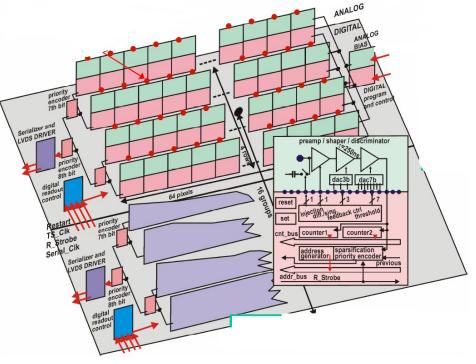

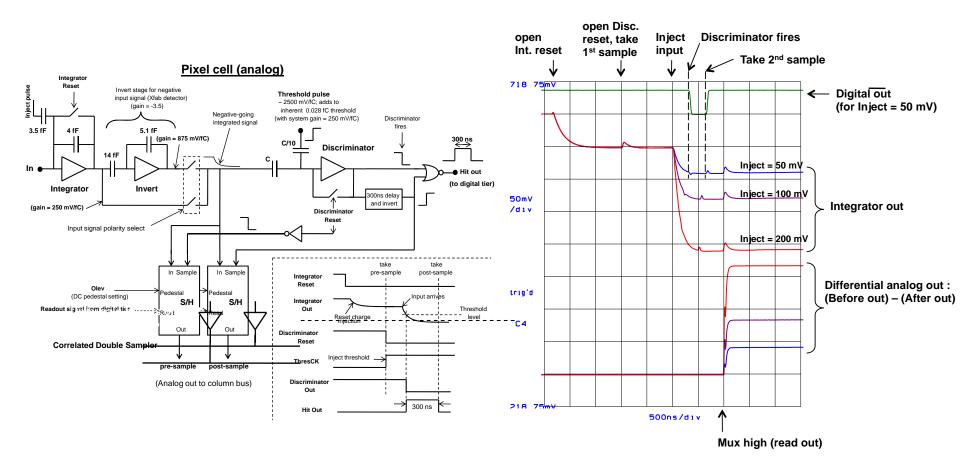

## VIP Chip (MIT-LL & Tezzaron)

- Chip designed for ILC Vertex

- Low power front end

- Digital and analog time stamp (~3-200 BX resolution)

<25 micron pixels

ns time resolution Radiation hard

50-100 micron sensors

Large area ~ 100 m<sup>2</sup>

- Sparsified readout

- 20(VIP1), 24(VIP2a) micron pitch

- Initial submission had low yield and marginal functionality due to MIT-LL process issues.

- Second submission (SOI->CMOS) with a more conservative design worked well. Converted to 0.18 micron CMOS for 3D Tezzaron run VIP2b. Analog performance of the 2D VIP was tested and reported last year.

- Full 3D VIP2b is received at Fermilab expect begin testing in October

## Data readout out using data sparsification scheme.

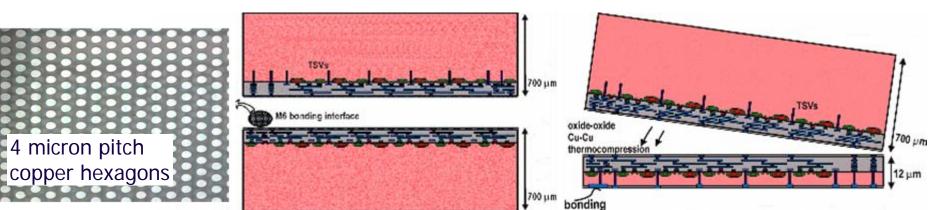

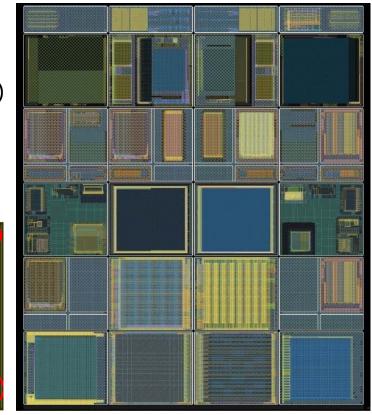

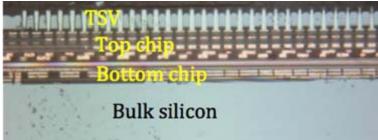

# Tezzaron 3D Run

- 3D consortium formed in late 2008

- 17 member groups from 6 countries (France, Italy, Germany, Poland, Canada, USA)

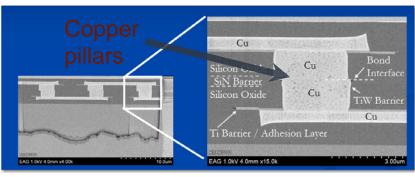

- Tezzaron Process

- Two tiers, 0.13 micron CMOS, TSVs

- Single set of masks to reduce cost

- Cu/Cu thermo compression

- face to face bonding

- wafers thinned to 12 um

- More than 25 two tier designs

- ATLAS pixels

- CMS strip ROIC for track trigger

- X-ray imaging

- B-factory and Linear Collider pixels

- Test circuits

- Frame divided into 24 subreticules

- 12 for top tier

- 12 for bottom tier

TYRITXF

AR

CR

ER

BR

DR

HR

BL

DL

AL

CL

# 3D Run History

- Design Issues (2008/2009)

- Designers did not use the same design kit (Top Metal, MIM Caps, SRAM)

- Some design rules were interpreted incorrectly

- Conversion issues Cadence -> Micro Magic (off grid rounding)

- Submission Issues (2009)

- wrong frame size (street size, labels, 3 revisions)

- incorrect mirroring by the mask house

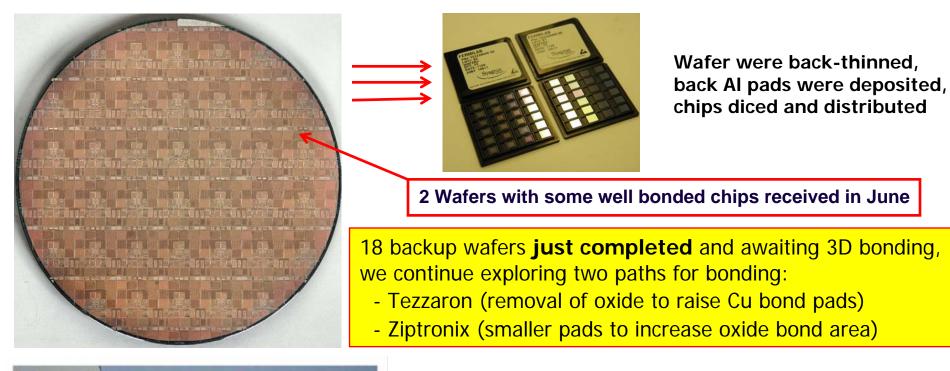

- Fabrication Issues (2010)

- Global/Chartered did not properly place frames on wafers, symmetry violated (rerun 31 wafers, no cost to users)

- Bonding issues (2011)

- equipment being relocated / staff changed

- Improper removal of 400nm of protective nitride (-> unbonded areas, insufficient bonding strength for grinding)

- Misalignment in bonding (1.2mm)

- Wafer Recovery (2012)

- Wafer resurface and bonding using Tezzaron Cu-Cu as well as Ziptronix DBI

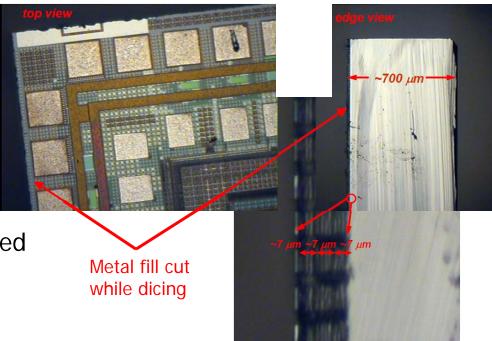

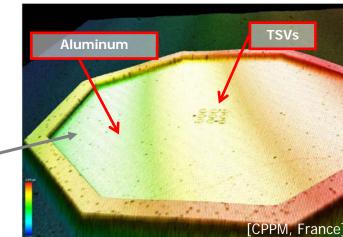

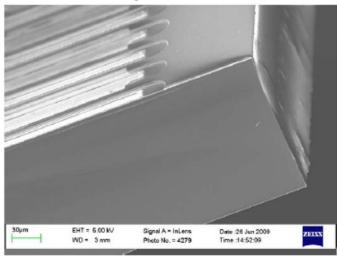

## Status of Tezzaron/GF 3D run

#### Exposure of TSV tips at AL pad

#### Key 3D steps:

- Backside processing,

- TSV formation and

- TSV exposure,

- Metallization

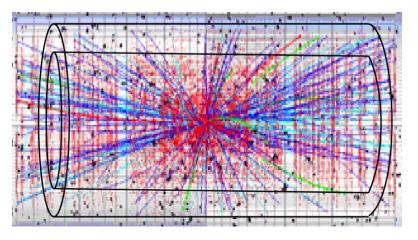

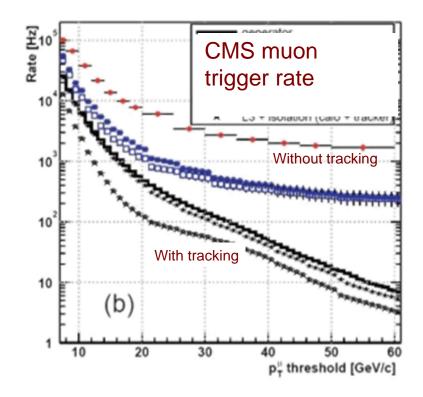

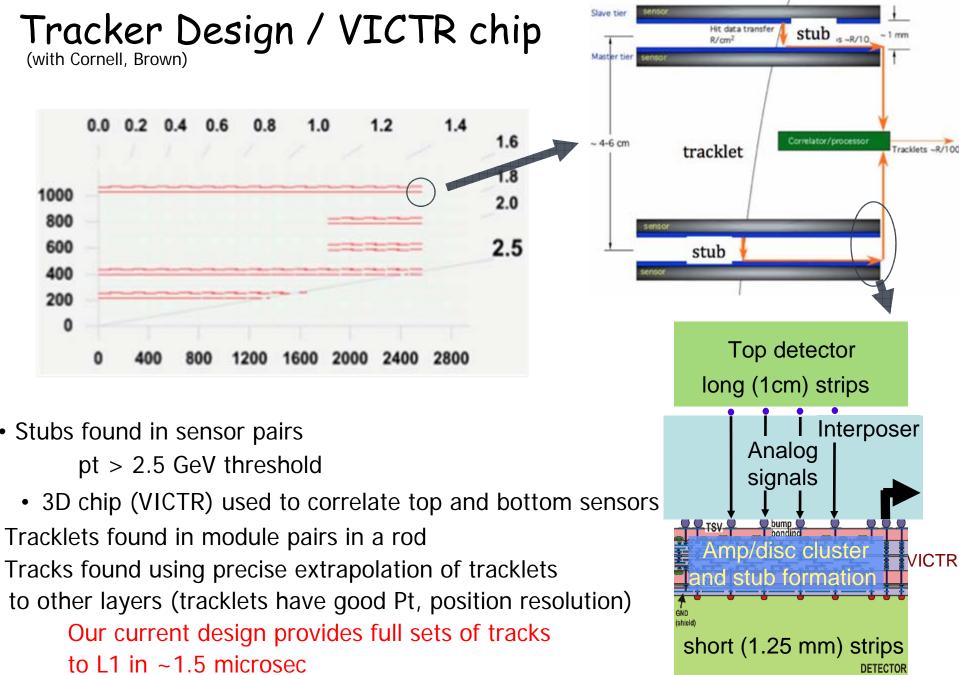

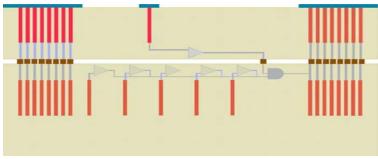

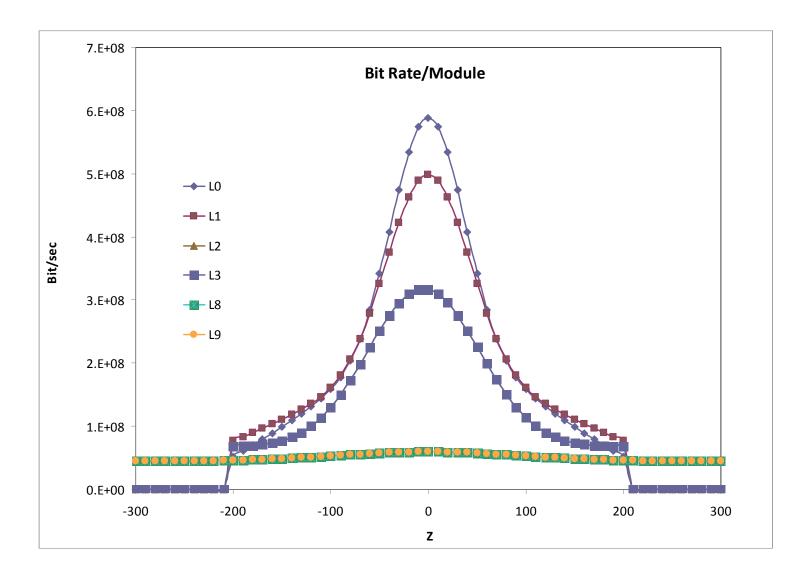

## Track Trigger for CMS (~2020ies)

- It has become increasingly clear (since 2009) that CMS will need a L1 trigger for HL-LHC:

- Must be (40MHz/100kHz) = 400 times faster than a L2 trigger like FTK or SVT

- Good Z resolution to reduce background event candidates. Minimize the tracks used for isolation.

- Limit rate at the front end by using correlated layers (x200 rate reduction)

- 3D is a key enabling technology for a "local" design (minimizing data transmission)

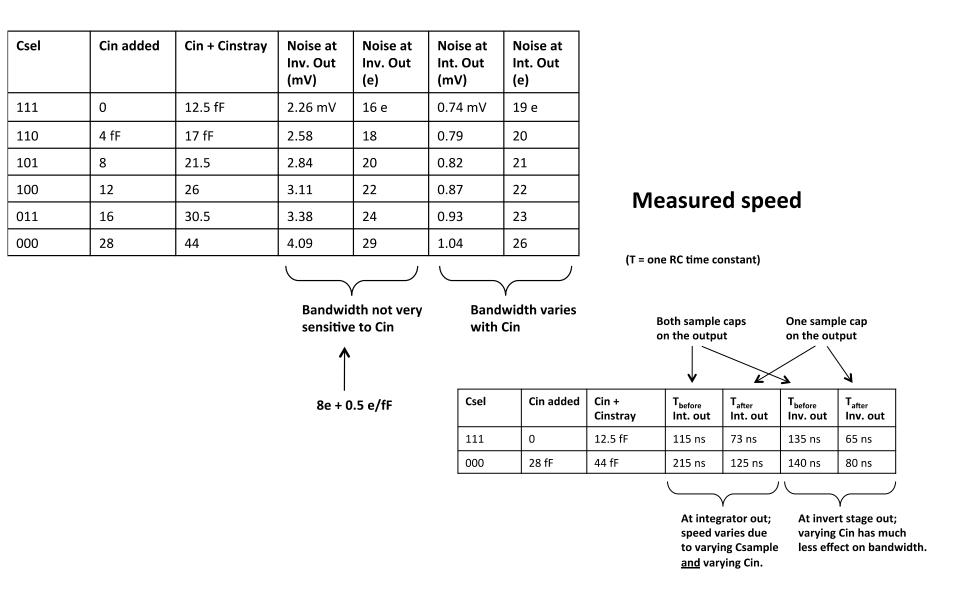

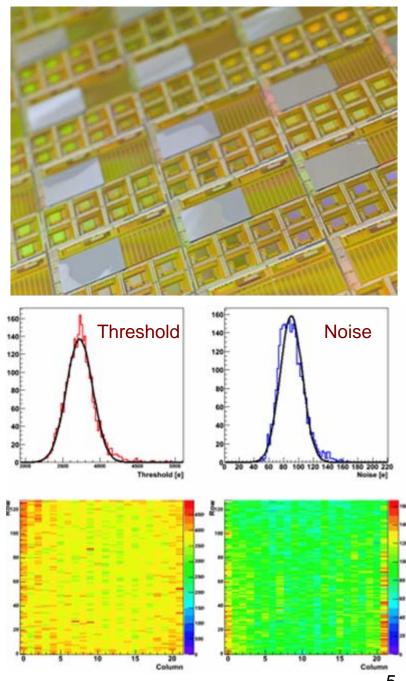

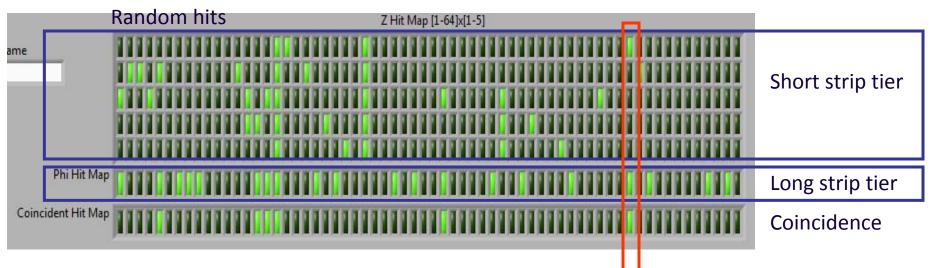

## VICTR Test results

Observing top and bottom tier fast and slow outputs as well as coincidences between tiers -> indicates successful 3D bonding

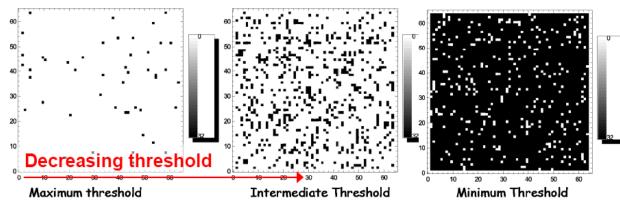

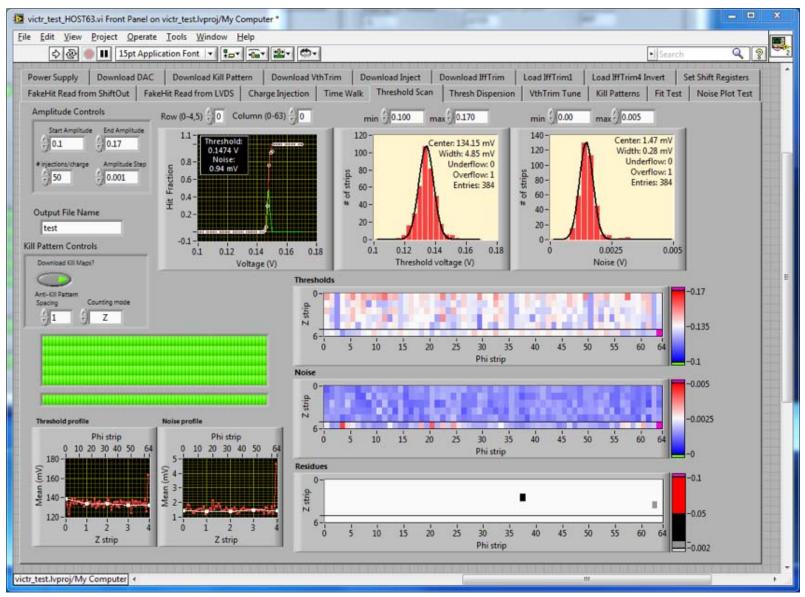

# VICTR DAQ (Threshold scans)

Analog Portion (modified version of LBNL's ATLAS FEI-4) of the chip tested and correspond to expected performance (noise, threshold dispersion)

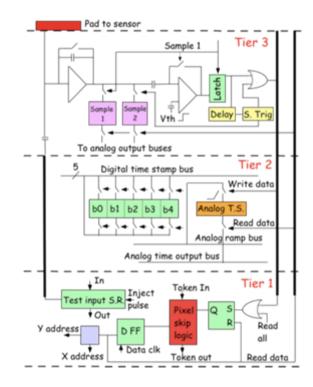

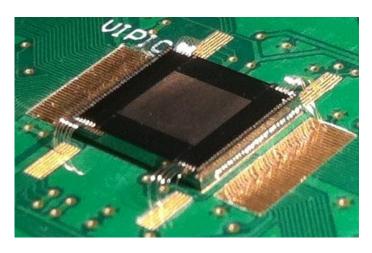

## • • VIPIC - Xray Imaging (Tezzaron 3D) (with AGH Krakow, BNL)

<25 micron pixels 50-100 micron sensors Large area ~ 100 m<sup>2</sup> ns time resolution Radiation hard

- XPCS light source applications (2D autocorrelation)

- 64  $\times$  64 array of 80 um² pixel, shaping time  $t_p{=}250$  ns, power  ${\sim}25$  mW, analog pixel noise  ${<}150$  e- ENC

- dead-time-less operation

- Data sparsified readout with priority encoder circuit

- Imaging: counting of events (2x 5bit counter) at frame rates ~10ms

- Present Development: featuring TOA mode (10ns timing) and cluster reconstruction to compensating charge sharing (2D prototype fabricated)

Digital part of pixel

Analog part of pixel

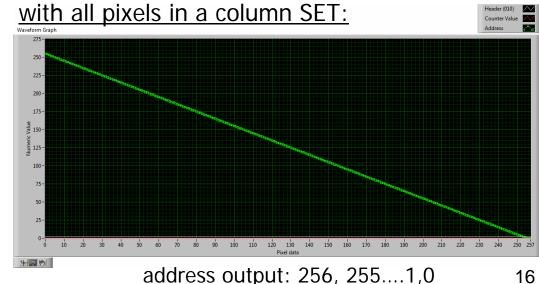

# **VIPIC - First Results**

Initial tests results:

- program all pixels to be set

- read out all 16 column blocks with each 4 x 64 addresses through the sparsification system

- observing noise hits counters respond proportional to threshold settings

- DACs work -> 25 connections between analog and digital tiers of each pixel are working!!

- More detailed tests soon!

Output of full sparsified readout chain

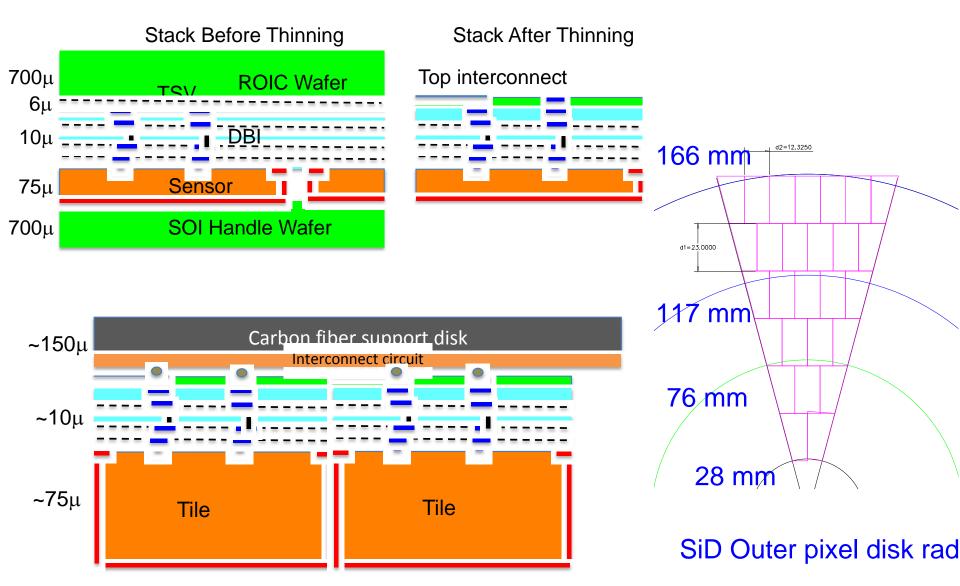

# <u>3D Outlook:</u> Towards large scale / 'edgeless' detector systems

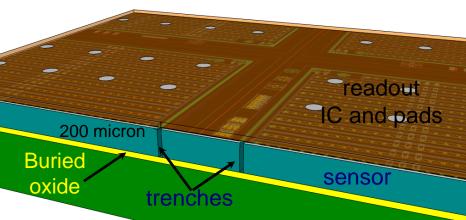

# Active Edge Project

(with Cornell, SLAC, Hawaii, Brown, UCSC, NRL)

- We are building a demonstration array including active edge sensors, oxide bonded wafers, and "damascene" dummy readout wafers:

- Sensors (fabricated at VTT) match the geometry for CMS track trigger long (1 cm) and short (1.25 mm) strip sensors.

- Top tungsten plug "damascene" wafer is being fabricated at Cornell - designed to readout either long or short strips with single reticule.

- Wafer bonding top thinning, etch and interconnect at Ziptronix

- Singulation and handle wafer removal will be done at Stanford in collaboration with SLAC

- There are no trenches on the edge reticules to allow test of the UCSC/NRL "slim edge" process

- Processing of the VTT and Cornell wafers is underway Ziptronix interface design is complete - should get results next year.

- Next step move to 8" sensor wafers

VTT Active Edge sensor

Handle wafer

# •••• Towards large scale detectors (hep and imaging)

<u>The Problem:</u> Build large area arrays of highly pixelated detectors with minimal dead area and reasonable cost

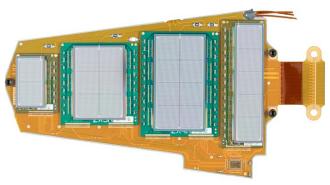

Current pixel detectors have dead areas arising from Sensor Edges Wirebond connections for Readout Integrated Circuits (ROICs) CMS forward pixel plaquette

## A solution:

- 3D or vertically integrated electronics provides path for extraction of signals,

- Active edge sensors remove dead area at the edges

## Combine:

- active edge technology with

- 3D electronics and

- oxide bonding with Through-Silicon-Vias to produce fully active tiles

Tiles can be used to build large area pixelated arrays with good yield and reasonable cost (e.g. SiD forward disks) 19

# Summary

- 3D technology offers unique opportunities for pixel detectors

- For many future hep/imaging challenges 3D integration is appropriate solution

- Tezzaron run finally provided useful chips; final batch of wafers still to be delivered

- First test of 'recovery lot' shows successful 3D bonding (VICTR tested, VIPIC tested, VIP tests scheduled)

4 years

- Exploring new paths (like 3D) is challenging and requires time

- FNAL continues/starts new projects facilitating 3D (VICTR, VIPRAM: tracking using Associative Memory, VIPIC2: 10ns time of arrival, charge sharing compensation)

# Footnotes / references

- [1] R.Lipton, 'Combining the Two 3Ds', WIT2012 proceedings

- [6] Current cost for 0.18 micron CMOS wafers with through-silicon vias, Yole Development Study

- [7] M. Barbero, Vertex 2011 Workshop, Rust Austria, June 19th 24th 2011

- [8] P. Merkel et. al. NIM A 582 771 (2007)

# **Backup Slides**

# ILC Vertex Sensor Development

•Our initial work on 3D electronics was motivated by the extraordinary requirements for ILC vertex detectors

- ~0.1% radiation length/layer

- time stamping

- 5 micron resolution

•We realized that emerging IC technologies which offer a high density of electronics, fine pitch interconnects, and wafer thinning could offer a solution to the ILC vertex problem.

- This led to work with:

- MIT-LL on SOI based 3D ICs

- Tezzaron on bulk CMOS based 3D ICs

- Ziptronix on detector/sensor integration with oxide bonding

- Cornell on thinning and laser annealing

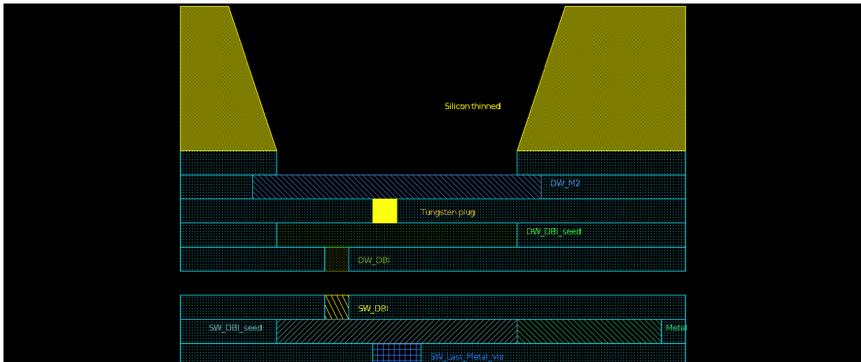

# Layer Stack (active edge)

# Tiling sensors -ILC forward disk example

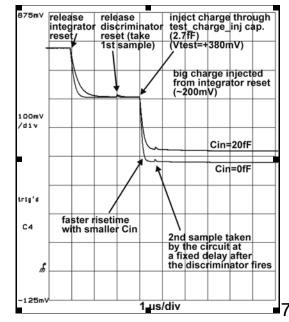

# VIP2b (Tezzaron 3D) tests

#### Measured response with charge injection

## **Measured noise (DCS)**