## **BISv2 Global Model**

## **BISv2** Reliability Study Progress Meetings #7

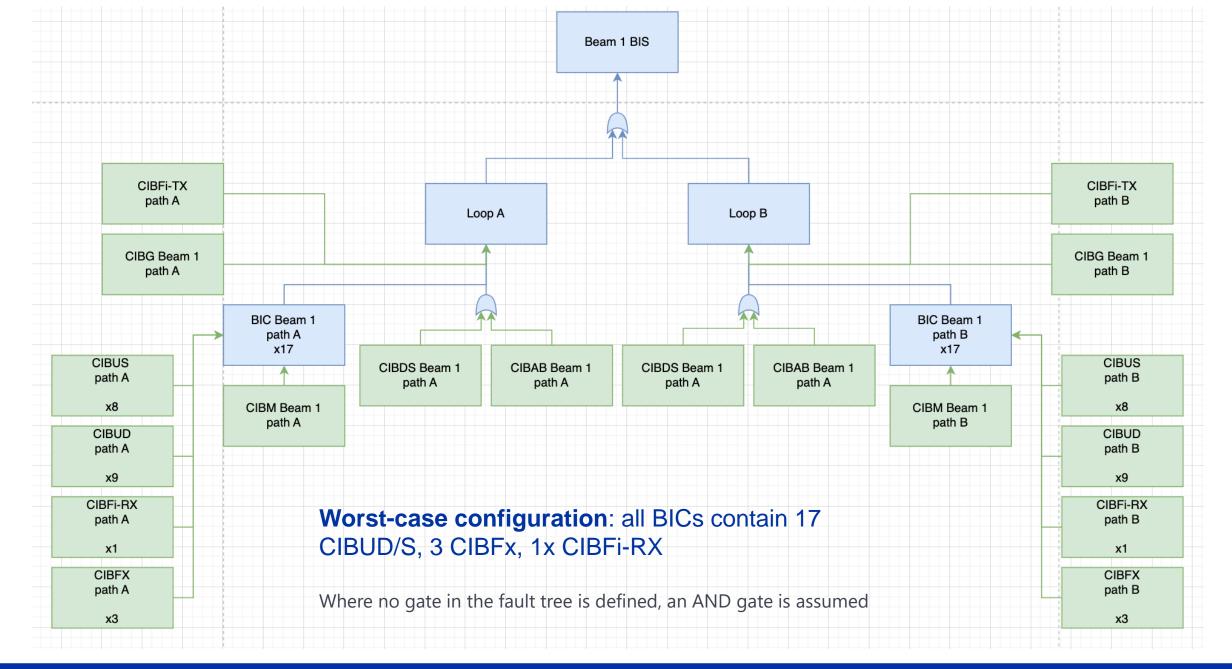

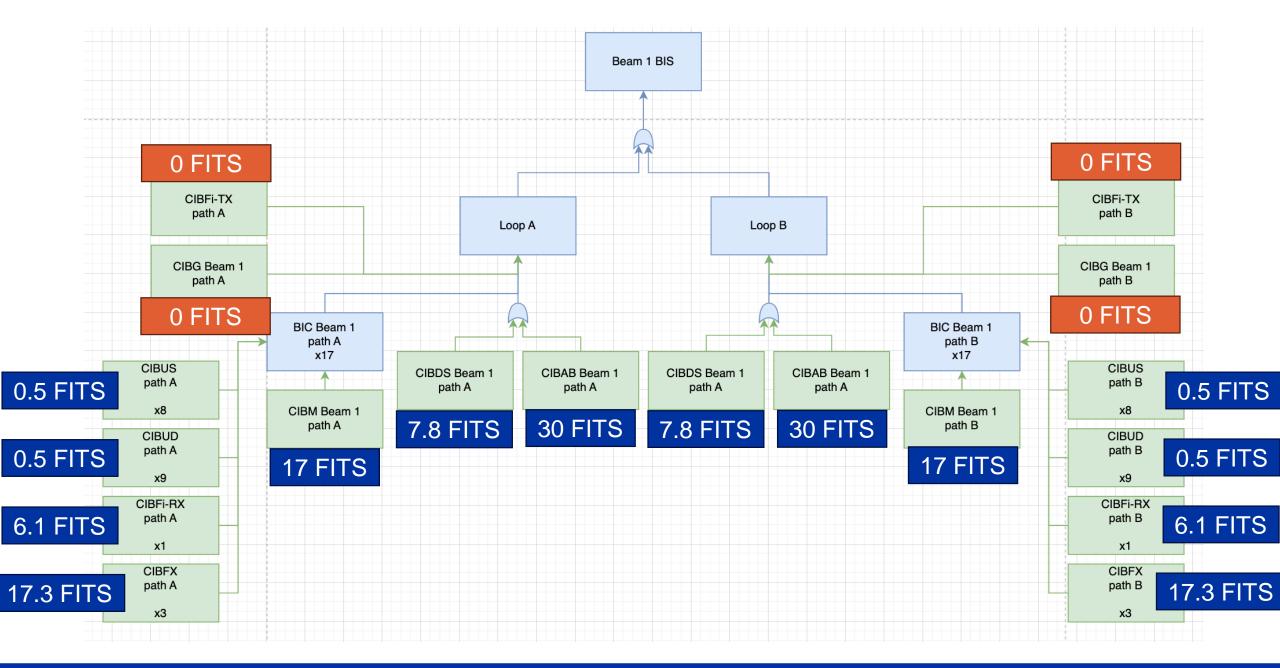

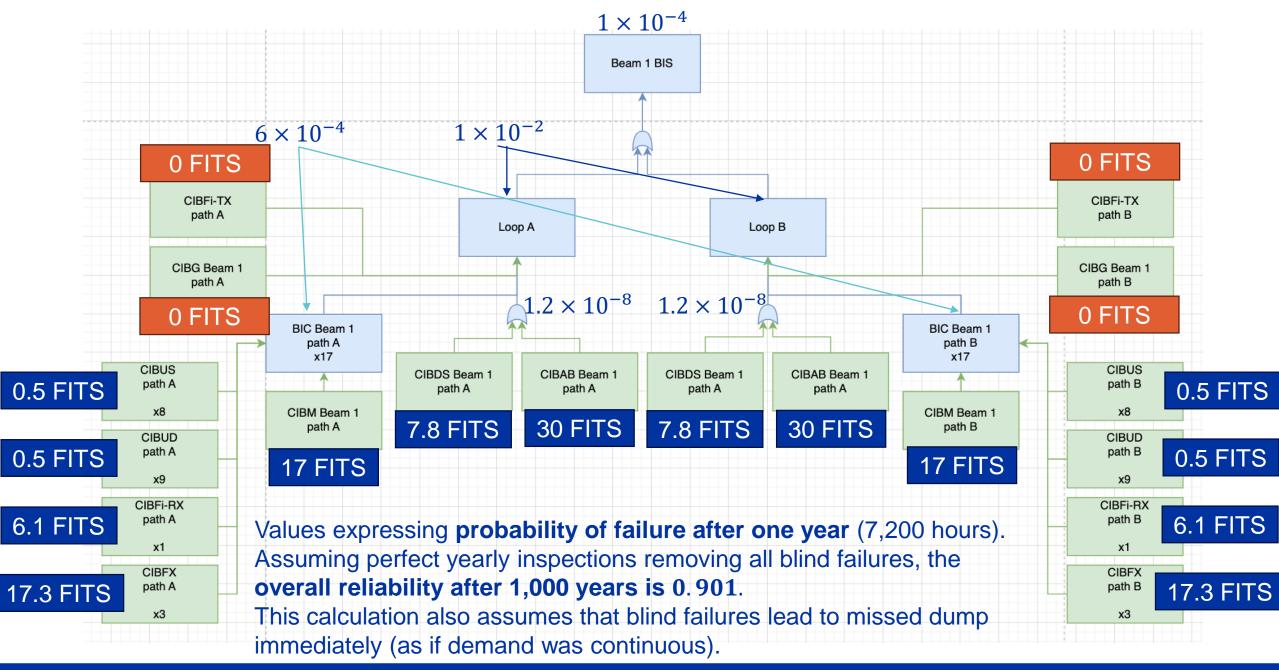

**CIBM:** 1 per path, in total 2 beams x 17 BICs x 2 loops (68 boards).

**CIBUS & CIBUD:** mulitple in each BIC, up to 17. Failure rate calcluated from "CIBU Channel". (total – 160 boards)

**CIBF & CIBFX**: max 3 in a BICs (total 8 boards).

**CIBAB:** 1 per path, in total 2 beams x 2 loops (total 4 boards).

**CIBDS:** one shared across two loops, however: two independent paths inside (total – 2 boards).

7.8 FITS per path from an oscillator in ARTIX 7 IO page "FPGA wouldn't meet timing requirements, could potentially lead to a blind failure"

**CIBG:** one per beam; regardless: 0 FITS in blind failures (2 boards).

**CIBFi-Rx:** 3 x A&B (total – 4 boards)

home.cern