# UVVM – An introduction to the world's fastest growing FPGA verification methodology

FDF-2024, CERN

(by Espen Tallaksen, CEO EmLogic)

The leading FPGA design centre in Norway and Scandinavia (www.emlogic.no/leading)

EmLogic.no

The Norwegian Embedded Systems and FPGA Design Centre

- Independent Design Centre for Embedded Systems and FPGA

- Established 1<sup>st</sup> of January 2021. Extreme ramp up

- January 2021: 1 person

- June 2023:  $\rightarrow$  43 persons (SW:19, HW:4, FPGA:18, DSP:1+)

- Continues the legacy from bitvis

- All previous Bitvis technical managers are now in EmLogic

- Verification IP and Methodology provider UVVM

- Course provider within FPGA Design and Verification

- Accelerating FPGA Design (Architecture, Clocking, Timing, Coding, Quality, Design for Reuse, ...)

- Advanced VHDL Verification Made simple (Modern efficient verification using UVVM)

- A potential partner for ESA projects for European companies

- Increased opportunities due to Norway's low geo return

### What is UVVM?

UVVM = Universal VHDL Verification Methodology

- VHDL Verification Library & Methodology

- Free and Open Source

- Very structured infrastructure and architecture

- Significantly improves Verification Efficiency

- Assures a far better Design Quality

- Recommended by Doulos for Testbench architecture

- ESA projects to extend the functionality

- IEEE Standards Association Open source project

SIEMENS Mentor

Runs on any VHDL-2008 compliant simulator

ASIC

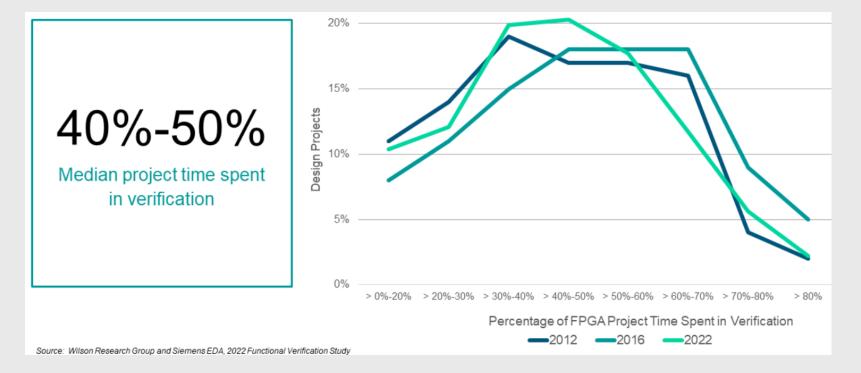

### The 2022 Wilson Research Group Functional Verification Study (1)

#### Nearly half the project time is spent in verification

#### Could verification time be reduced without reducing the quality?

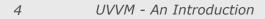

### The 2022 Wilson Research Group Functional Verification Study (2)

#### Half the verification time is spent on debugging

2022 WILSON RESEARCH GROUP, FUNCTIONAL VERIFICATION STUDY FPGA FUNCTIONAL VERIFICATION TREND REPORT

We can definitely be more efficient! - structured!

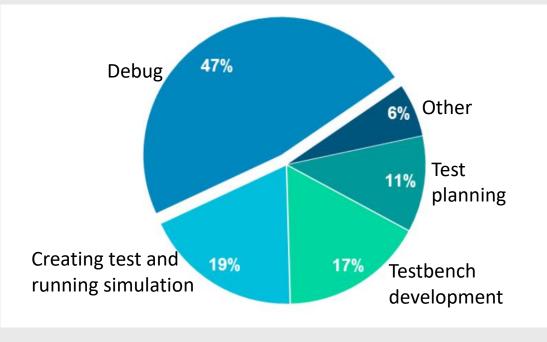

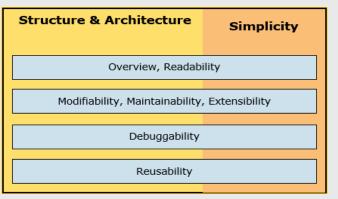

### What enables Quality and Efficiency

Huge improvement potential for more structured FPGA verification

#### UVVM targets all of this

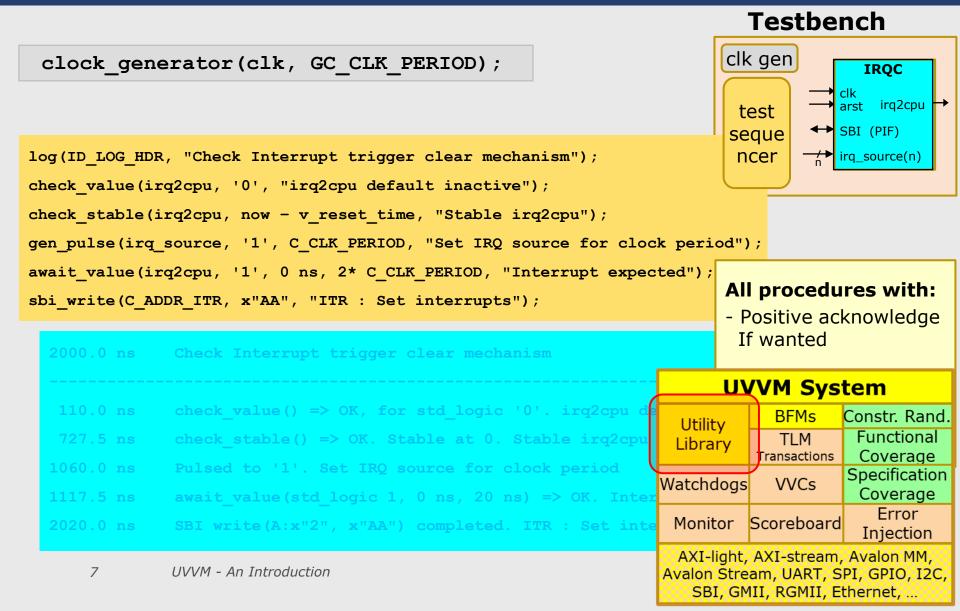

# Example on test sequencer code and transcript/log

### UVVM Utility Library for simple **and** advanced testbenches

- check\_stable(), await\_stable()

- clock\_generator(), adjustable\_clock\_generator()

- random(), randomize()

- gen\_pulse()

- block\_flag(), unblock\_flag(), await\_unblock\_flag()

- await\_barrier()

- enable\_log\_msg(), disable\_log\_msg()

- to\_string(), fill\_string(), to\_upper(), replace(), etc...

- normalize\_and\_check()

- set\_log\_file\_name(), set\_alert\_file\_name()

- wait\_until\_given\_time\_after\_rising\_edge()

• etc...

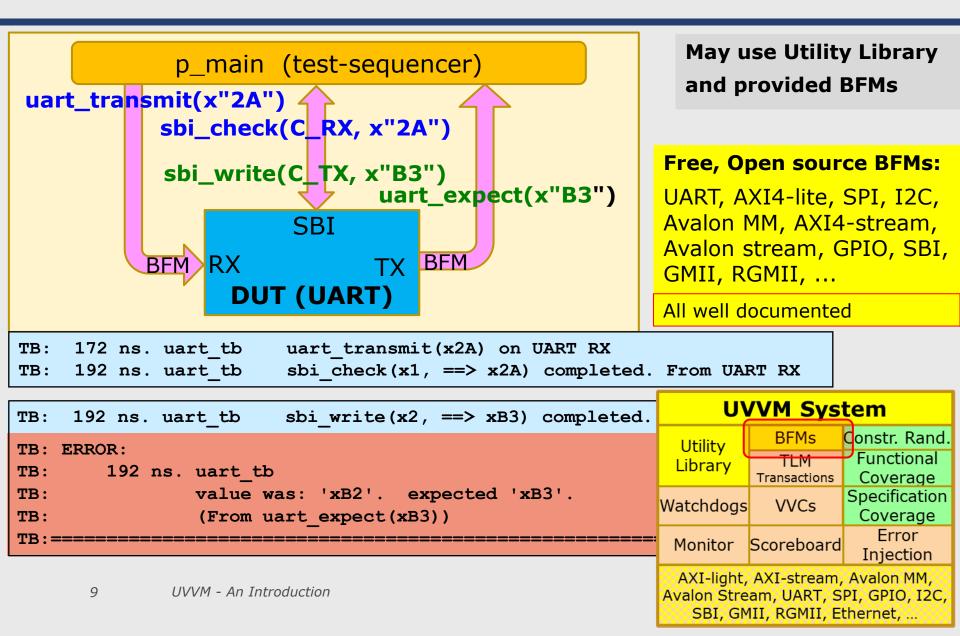

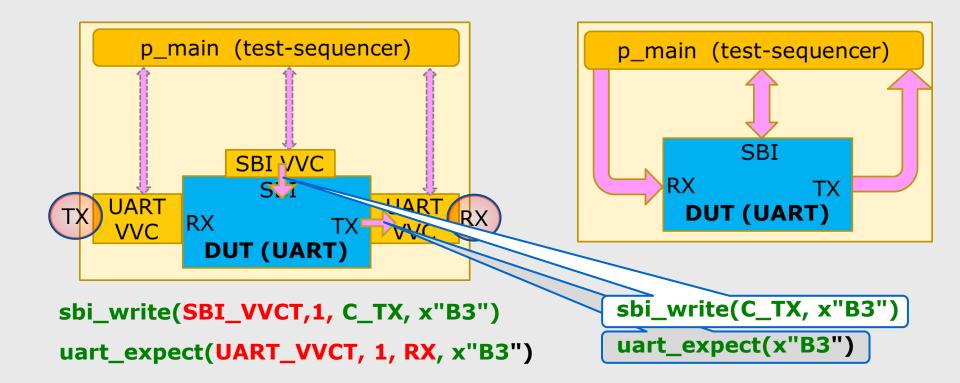

## Simple data communication

### BFM procedures are not sufficient

#### BFM: Defined here as a procedure only

- BFMs are great for simple testbenches

- Dedicated procedures in a simple package

- Just reference and call from a process

- BUT

- A process can only do one thing at a time

- Either execute that BFM

- Or execute another BFM

- Or do something else

- To do more than one thing:

→ Need an entity (or component)

(VC = Verification Component)

sbi\_write(C\_TX, x"B3")

uart\_expect(x"B3")

VVC: VHDL Verification Component (UVVM VC with extended functionality)

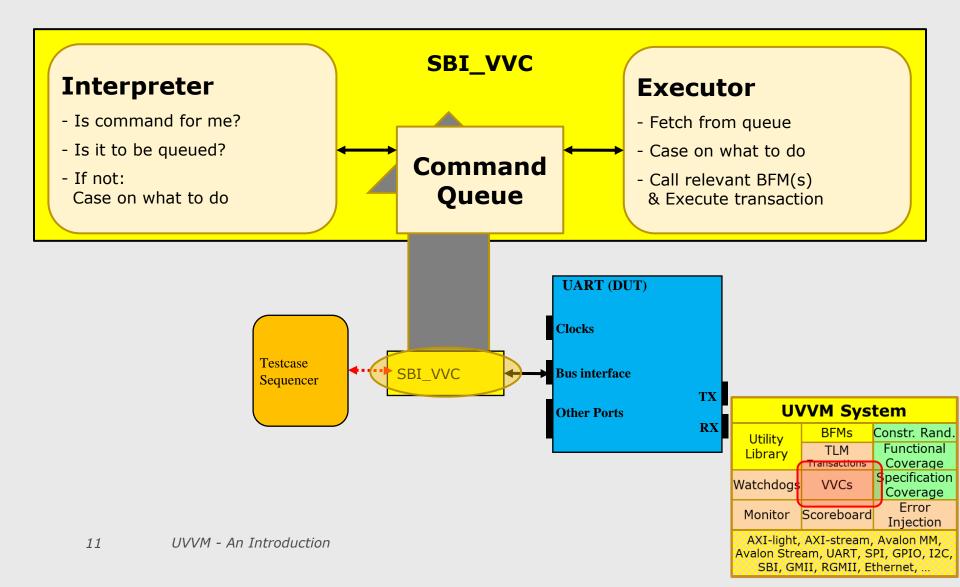

### **VVC: VHDL Verification Component**

### BFM to VVC: How?

#### **UVVM VVCs also include:**

Delay-insertion, command queuing, completion detection, activity registration, multicast & broadcast, termination, set-up, data fetch, multi-channel support, interface checkers, scoreboards, transaction info, local sequencers, etc ...

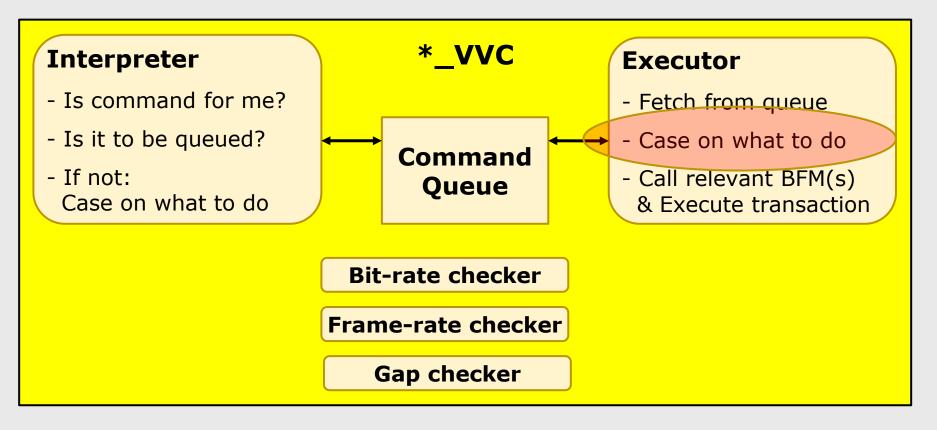

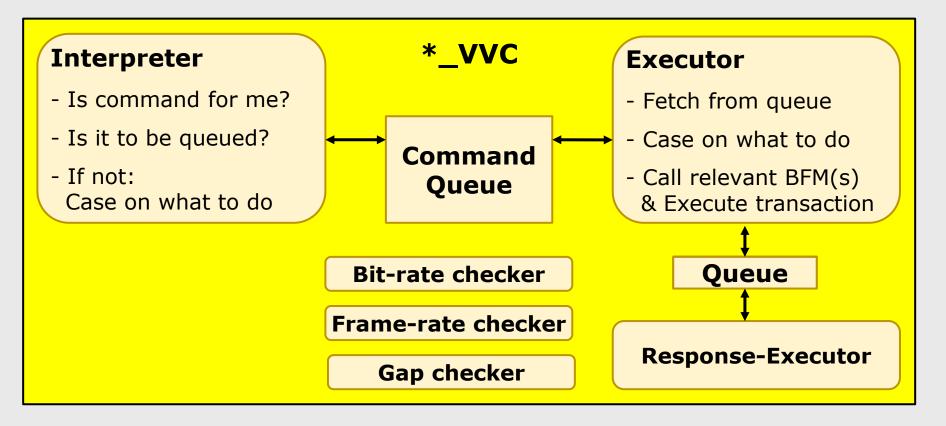

## VVC: Easy to extend (1)

- Easy to add local sequencers

- Easy to add checkers/monitors/etc

## VVC: Easy to extend (2)

- Easy to handle split transactions

- Easy to handle out of order execution

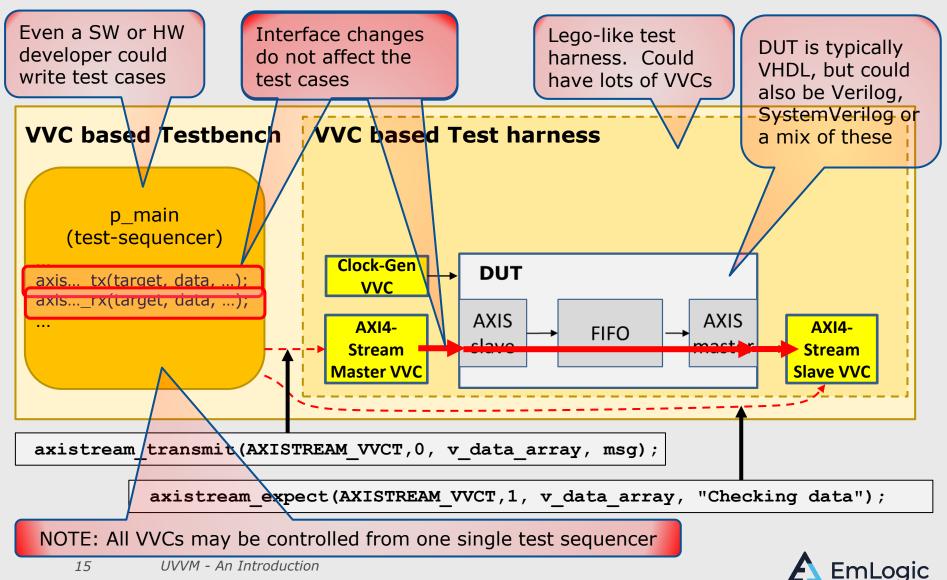

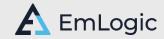

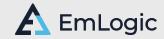

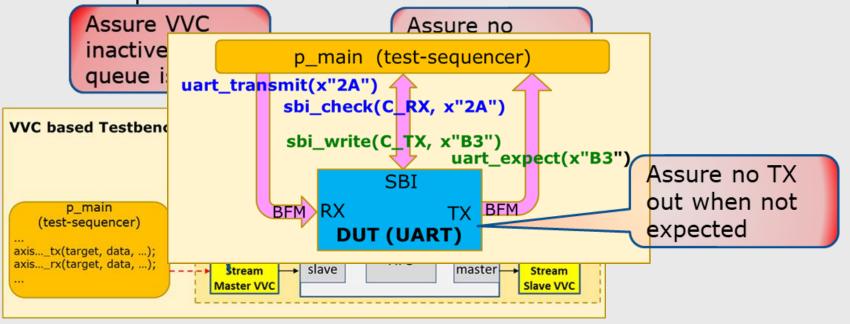

### VVC based TB

UVVM - An Introduction

### VVC Advantages

- Simultaneous activity on multiple interfaces

- Encapsulated  $\rightarrow$  Reuse at all levels

- Queue  $\rightarrow$  May initiate multiple high level commands

- Local Sequencers for predefined higher level commands

### Unique for UVVM VVCs:

- Fully control **and** align all VVCs from a single sequencer!

- May insert delay between commands from sequencer

→ The only system to target cycle related corner cases

- Simple handling of split transactions and out of order protocols

- Common commands to control VVC behaviour

- Simple synchronization of interface actions from sequencer

- May use Broadcast and Multicast

#### Better Overview, Maintenance, Extensibility and Reuse

### Lot's of free UVVM BFMs and VVCs

- AXI4-lite

- AXI4 Full

- AXI-Stream Transmit and Receive

- UART Transmit and Receive

- SBI

- SPI Transmit and Receive

- I2C Transmit and Receive

- GPIO

- Avalon MM

- Avalon Stream Transmit and Receive

- RGMII Transmit and Receive

- GMII Transmit and Receive

- Ethernet Transmit and Receive

- Wishbone

- Clock Generator

- Error Injector

#### VVC: VHDL Verif. Comps.

- Includes the corresponding BFM Allows:

- Simultaneous interface handling

- Synchronization of interfaces

- Skewing between interfaces

- Additional protocol checkers

- Local sequencers

- Activity detection

- Simple reuse between projects

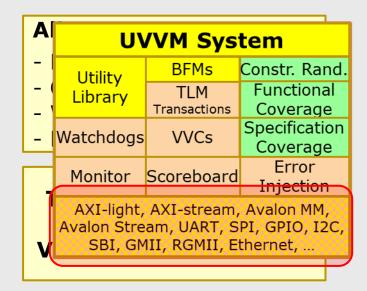

### Added 2017-19 – in cooperation with ESA

#### ESA Extensions in ESA-UVVM-1

- Scoreboards

- Monitors

- Controlling randomisation and functional coverage

- Error injection (Brute force and Protocol aware)

- Local sequencers

- Controlling property checkers

- Transaction info

- Watchdog (Simple and Activity based)

- Hierarchical VVCs And Scoreboards for these

- **Specification Coverage** (Requirement/test coverage)

#### ESA is helping VHDL designers speed up FPGA and ASIC development and improve their product quality!

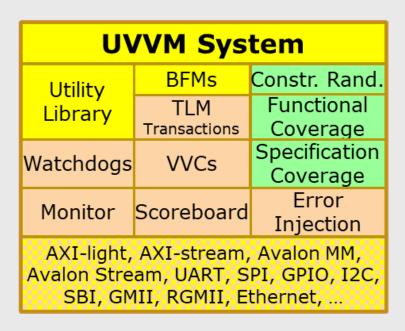

|                  | UVVM System                                                               |              |               |  |  |

|------------------|---------------------------------------------------------------------------|--------------|---------------|--|--|

|                  | Utility<br>Library                                                        | BFMs         | Constr. Rand. |  |  |

|                  |                                                                           | TLM          | Functional    |  |  |

|                  |                                                                           | Transactions | Coverage      |  |  |

| $\left( \right)$ | Watchdogs                                                                 | VVCs         | Specification |  |  |

|                  |                                                                           |              | Coverage      |  |  |

| ſ                | Monitor                                                                   | Scoreboard   | Error         |  |  |

| U                |                                                                           | Scoreboard   | Injection     |  |  |

|                  | AXI-light, AXI-stream, Avalon MM,<br>Avalon Stream, UART, SPI, GPIO, I2C, |              |               |  |  |

|                  | SBI, GMII, RGMII, Ethernet,                                               |              |               |  |  |

### **Generic Scoreboard**

generic data type

- logging/reporting

- flushing queue

- clearing statistics

**Configuration record:**

- allow\_lossy

- allow\_out\_of\_order

- mismatch\_alert\_level

#### insert, delete, fetch

- ignore\_initial\_mismatch

- indexed on either entry or position

- optional source element (in addition to expected + actual)

#### **Counting:**

- entered

- pending

- matched

- mismatched

- dropped

- deleted

- initial garbage

UVVM - An Introduction

Expensive tools exist...

Coverage per requirement

**1.**Specify all requirements

**3.**Generate summary report

- Test cases covering each requirement

- Requirements covered by each Test case

Strongly recommended for good quality assurance

Specification Coverage

2.Report coverage from test sequencer(s) (or other TB parts)

Mandatory for Safety and Mission Critical (Strictly required by ESA)

Assure that all requirements have been verified

- Accumulate over multiple Test cases

Library

Watchdogs

em

TLIM

Transactions

**VVCs**

AXI-light, AXI-stream, Avalon MM,

Avalon Stream, UART, SPI, GPIO, I2C, SBI, GMII, RGMII, Ethernet, ...

Monitor Scoreboard

bnstr. Rand.

Functional

Coverage

Specification

Coverage Error

Injection

### The 2<sup>nd</sup> ESA project – 2020-22

- Enhanced Randomisation

- Advanced randomisation in a simple way

- Optimised Randomisation

- Randomisation without replacement

- Weighted according to target distribution AND previous events

- $\rightarrow$  the lowest number of randomisations for a given target

- Functional Coverage

- Checking that given scenarios have been verified

| U۱                                                                  | UVVM System  |               |  |  |  |

|---------------------------------------------------------------------|--------------|---------------|--|--|--|

| Utility                                                             | BFMs         | Constr. Rand  |  |  |  |

| Library                                                             | TLM          | Functional    |  |  |  |

| Library                                                             | Transactions | Coverage      |  |  |  |

| Watchdogs                                                           | VVCs         | Specification |  |  |  |

| watchuogs                                                           |              | Coverage      |  |  |  |

| Monitor                                                             | Scoreboard   | Error         |  |  |  |

| Monitor                                                             | Scoreboard   | Injection     |  |  |  |

| AXI-light, AXI-stream, Avalon MM,                                   |              |               |  |  |  |

| Avalon Štréam, UART, SPI, GPIO, I2C,<br>SBI, GMII, RGMII, Ethernet, |              |               |  |  |  |

23 UVVM - An Introduction

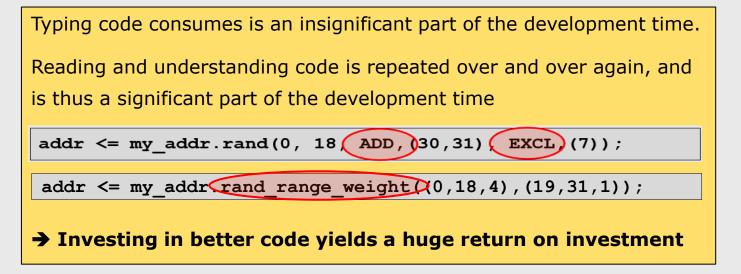

### **UVVM Enhanced Randomisation**

- Well integrated with UVVM

- Alert handling and logging in particular

- Strong focus on Overview & Readability

- Adding keywords to ease understanding

- Easy to Maintain and Extend

```

Quality & Efficiency enablers

```

### Functional Coverage (FC) – Typical Sequence

2-254

Define a variable of type t\_coverpoint

variable cp\_payload\_size : t\_coverpoint;

Add the bins

cp\_payload\_size.add\_bins(bin(0)); cp\_payload\_size.add\_bins(bin(1)); cp\_payload\_size.add\_bins(bin\_range(2,254,1)); cp\_payload\_size.add\_bins(bin(255,256,2));

Tick off bins as their corresponding payload size is used

cp\_payload\_size.sample\_coverage(payload\_size);

Continue sending packets until coverage target is reached

while not cp\_payload\_size.coverage\_completed(VOID);

#### **UVVM** also has transition coverage

### Some FC reports – out of many

**E**mLogic

| UVVM:                           |                                                                                                                                                                                |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UVVM:                           | 0 ns *** COVERAGE SUMMAR                                                                                                                                                       | Y REPORT (NON V                                                                 | ERBOSE): TB se                                                     | q. ***                                                                                                                          |                                                                                                                                        |                                                                                                                                                            |

| ŧ UVVM:                         |                                                                                                                                                                                |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

| UVVM                            |                                                                                                                                                                                | Covpt_1                                                                         |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

| UVVM:                           | Coverage (for goal 100):                                                                                                                                                       | Bins: 60.00%,                                                                   | Hits: 76.47%                                                       | )                                                                                                                               |                                                                                                                                        |                                                                                                                                                            |

| UVVM:                           |                                                                                                                                                                                |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

| UVVM:                           | BINS                                                                                                                                                                           | HITS                                                                            | MIN HITS                                                           | HIT COVERAGE                                                                                                                    |                                                                                                                                        | ILLEGAL/IGNORE                                                                                                                                             |

| UVVM:                           | (256 to 511)                                                                                                                                                                   | 1                                                                               | N/A                                                                | N/A                                                                                                                             | illegal_addr                                                                                                                           | ILLEGAL                                                                                                                                                    |

| UVVM:                           | (0 to 125)                                                                                                                                                                     | 6                                                                               | 8                                                                  | 75.00%                                                                                                                          | mem_addr_low                                                                                                                           | -                                                                                                                                                          |

| UVVM:                           | (126, 127, 128)                                                                                                                                                                | 3                                                                               | 1                                                                  | 100.00%                                                                                                                         | mem_addr_mid                                                                                                                           | -                                                                                                                                                          |

| UVVM:                           | (129 to 255)                                                                                                                                                                   | 14                                                                              | 4                                                                  | 100.00%                                                                                                                         | mem_addr_high                                                                                                                          | -                                                                                                                                                          |

| UVVM:                           | (0->1->2->3)                                                                                                                                                                   | 0                                                                               | 2                                                                  | 0.00%                                                                                                                           | transition_1                                                                                                                           | -                                                                                                                                                          |

| UVVM:                           | transition_2                                                                                                                                                                   | 2                                                                               | 2                                                                  | 100.00%                                                                                                                         | transition_2                                                                                                                           | -                                                                                                                                                          |

| UVVM:                           |                                                                                                                                                                                |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

| # UVVM:<br># UVVM:              | transition_2: (0->15->12                                                                                                                                                       | /->248->249->250                                                                | 0->251->252->2                                                     | 53->254)                                                                                                                        |                                                                                                                                        |                                                                                                                                                            |

|                                 |                                                                                                                                                                                |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

|                                 |                                                                                                                                                                                |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

|                                 | UVVM:                                                                                                                                                                          |                                                                                 |                                                                    |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

| #                               | UVVM:                                                                                                                                                                          | OVERAGE REPORT (                                                                | /ERBOSE): TB s                                                     |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                            |

| #                               |                                                                                                                                                                                |                                                                                 |                                                                    | eq. ***<br>73.68%, Hits: 76.                                                                                                    | 00%                                                                                                                                    |                                                                                                                                                            |

| #<br>#<br>#                     | UVVM: 0 ns *** OVERALL C                                                                                                                                                       |                                                                                 |                                                                    | 73.68%, Hits: 76.                                                                                                               |                                                                                                                                        |                                                                                                                                                            |

| #<br>#<br>#                     | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for goal<br>UVVM: ========                                                                                                         |                                                                                 |                                                                    | 73.68%, Hits: 76.                                                                                                               |                                                                                                                                        |                                                                                                                                                            |

| #<br>#<br>#<br>#                | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for goal<br>UVVM: ========                                                                                                         | 100): Covpts: 5                                                                 | 60.00%, Bins:                                                      | 73.68%, Hits: 76.                                                                                                               | TS) GOAL(BINS HITS)                                                                                                                    |                                                                                                                                                            |

| #<br>#<br>#<br>#                | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for goal<br>UVVM:                                                                                                                  | 100): Covpts: 5<br><br>COVERAGE WEIGHT                                          | 0.00%, Bins:<br>COVERED BINS                                       | 73.68%, Hits: 76.                                                                                                               | TS) GOAL(BINS HITS)<br>% 50%   100%                                                                                                    | % OF GOAL(BINS HITS)                                                                                                                                       |

| #<br>#<br>#<br>#<br>#           | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for goal<br>UVVM: COVERPOINT<br>UVVM: COVERPOINT<br>UVVM: Covpt_1                                                                  | 100): Covpts: 5<br><br>COVERAGE WEIGHT                                          | 0.00%, Bins:<br>COVERED BINS<br>3 / 5                              | 73.68%, Hits: 76.<br>COVERAGE(BINS HI<br>60.00%   76.47                                                                         | TS) GOAL(BINS HITS)<br>% 50%   100%<br>0% 100%   100%                                                                                  | % OF GOAL(BINS HITS)<br>100.00%   76.47%                                                                                                                   |

| #<br>#<br>#<br>#<br>#<br>#      | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for geal<br>UVVM: COVERPOINT<br>UVVM: COVERPOINT<br>UVVM: Covpt_1<br>UVVM: Covpt_2                                                 | 100): Covpts: 5<br><br>COVERAGE WEIGHT                                          | COVERED BINS<br>3 / 5<br>3 / 3                                     | 73.68%, Hits: 76.<br>COVERAGE(BINS HI<br>60.00%   76.47<br>100.00%   100.0                                                      | TS) GOAL(BINS HITS)<br>% 50%   100%<br>0% 100%   100%<br>0% 100%   100%                                                                | % OF GOAL(BINS HITS)<br>100.00%   76.47%<br>100.00%   100.00%                                                                                              |

| #<br>#<br>#<br>#<br>#<br>#<br># | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for goal<br>UVVM: COVERPOINT<br>UVVM: COVERPOINT<br>UVVM: Covpt_1<br>UVVM: Covpt_2<br>UVVM: Covpt_3                                | 100): Covpts: 5<br><br>COVERAGE WEIGHT                                          | COVERED BINS<br>3 / 5<br>3 / 3<br>6 / 6                            | 73.68%, Hits: 76.<br>COVERAGE(BINS HI<br>60.00%   76.47<br>100.00%   100.0<br>100.00%   100.0                                   | TS) GOAL(BINS HITS)<br>% 50%   100%<br>0% 100%   100%<br>0% 100%   100%<br>100%   100%                                                 | % OF GOAL(BINS HITS)<br>100.00%   76.47%<br>100.00%   100.00%<br>100.00%   100.00%                                                                         |

| # # # # # # # #                 | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for goal<br>UVVM: COVERPOINT<br>UVVM: COVPt_1<br>UVVM: Covpt_2<br>UVVM: Covpt_3<br>UVVM: Covpt_4                                   | 100): Covpts: 5<br>COVERAGE WEIGHT<br>1<br>1<br>1<br>1                          | COVERED BINS<br>3 / 5<br>3 / 3<br>6 / 6<br>0 / 4                   | 73.68%, Hits: 76.<br>COVERAGE(BINS HI<br>60.00%   76.47<br>100.00%   100.0<br>100.00%   100.0<br>0.00%   0.00%                  | TS) GOAL(BINS HITS)<br>% 50%   100%<br>0% 100%   100%<br>0% 100%   100%<br>100%   100%<br>100%   100%                                  | <pre>% OF GOAL(BINS HITS)<br/>100.00%   76.47%<br/>100.00%   100.00%<br/>100.00%   100.00%<br/>0.00%   0.00%</pre>                                         |

| # # # # # # # # #               | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for geal<br>UVVM: COVERPOINT<br>UVVM: COVPt_1<br>UVVM: Covpt_2<br>UVVM: Covpt_3<br>UVVM: Covpt_4<br>UVVM: Covpt_5                  | 100): Covpts: 5<br>COVERAGE WEIGHT<br>1<br>1<br>1<br>1<br>1<br>1                | COVERED BINS<br>3 / 5<br>3 / 3<br>6 / 6<br>0 / 4<br>0 / 1          | 73.68%, Hits: 76.<br>COVERAGE(BINS HI<br>60.00%   76.47<br>100.00%   100.0<br>100.00%   100.0<br>0.00%   0.00%<br>0.00%   0.00% | TS) GOAL(BINS HITS)<br>% 50%   100%<br>0% 100%   100%<br>0% 100%   100%<br>100%   100%<br>100%   100%<br>0% 100%   100%                | % OF GOAL(BINS HITS)<br>100.00%   76.47%<br>100.00%   100.00%<br>100.00%   100.00%<br>0.00%   0.00%<br>0.00%   0.00%                                       |

| # # # # # # # # # #             | UVVM: 0 ns ** OVERALL CO<br>UVVM: Coverage (for geal<br>UVVM: COVERPOINT<br>UVVM: COVPt_1<br>UVVM: Covpt_1<br>UVVM: Covpt_3<br>UVVM: Covpt_4<br>UVVM: Covpt_5<br>UVVM: Covpt_6 | 100): Covpts: 5<br>COVERAGE WEIGHT<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | COVERED BINS<br>3 / 5<br>3 / 3<br>6 / 6<br>0 / 4<br>0 / 1<br>4 / 4 | COVERAGE(BINS HI<br>60.00%   76.47<br>100.00%   100.0<br>100.00%   100.0<br>0.00%   0.00%<br>0.00%   0.00%<br>100.00%   100.0   | TS) GOAL(BINS HITS)<br>% 50%   100%<br>0% 100%   100%<br>0% 100%   100%<br>100%   100%<br>100%   100%<br>0% 100%   100%<br>100%   100% | <pre>% OF GOAL(BINS HITS)<br/>100.00%   76.47%<br/>100.00%   100.00%<br/>100.00%   100.00%<br/>0.00%   0.00%<br/>0.00%   0.00%<br/>100.00%   100.00%</pre> |

### The 3<sup>rd</sup> ESA project – 2024

- Started March 2024

- First new features to be released in June

- Completion detection

- Detection of unwanted/unexpected interface activity

- More improvements to come

### Sources of learning

- Very well documented

- In transition from PDF to html

- Lots of free webinars available

- From Siemens, Aldec, Trias, Verification Futures, etc

- New free introduction videos

- Siemens' Xcelerated Academy

- EmLogic courses: <u>https://emlogic.no/courses/</u>

- 'Advanced VHDL Verification Made simple'

- First planned live online course: November 2024

- Testbench examples

- Note: Provided under the 'UVVM supplementary' repo

- New: Sharing training material with universities for free

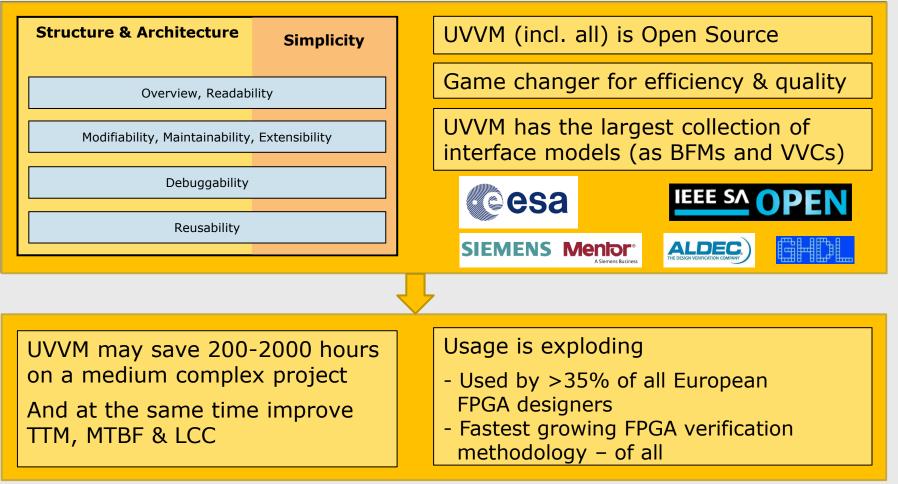

### UVVM in a nutshell

Huge improvement potential for more structured FPGA verification

### Thank you for attending

### UVVM – An introduction to the world's fastest growing FPGA verification methodology

| Structure & Architecture Simp                                                                        | plicity | UVVM (incl. all) is Open Source                                                                                                       |         |

|------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|---------|

| Overview, Readability                                                                                |         | Game changer for efficiency & quality                                                                                                 |         |

| Modifiability, Maintainability, Extensibili                                                          | ity     | UVVM has the largest collection of interface models (as BFMs and VVCs)                                                                |         |

| Debuggability<br>Reusability                                                                         |         | Cesa  IEEE SA OPEN    SIEMENS Mentor:  ALDEC                                                                                          | EmLogio |

|                                                                                                      | Z       | -                                                                                                                                     |         |

| UVVM may save 200-2000<br>on a medium complex proje<br>And at the same time impro<br>TTM, MTBF & LCC | ect     | Usage is exploding<br>- Used by >35% of all European<br>FPGA designers<br>- Fastest growing FPGA verification<br>methodology – of all |         |

### Feel free to connect on LinkedIn