# The testing and performance of the ETROC2 for CMS MTD Endcap Timing Layer (ETL)upgrade

Ted Liu (Fermilab)

Oct 1, 2024, TWEPP

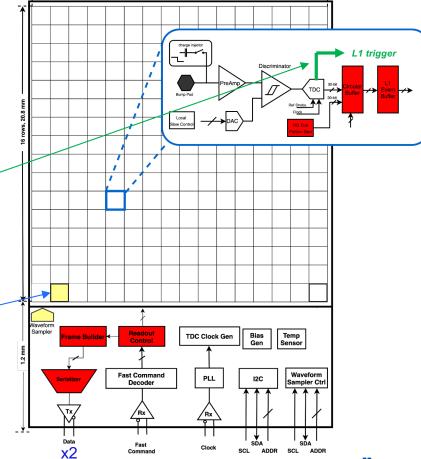

ETROC is designed to process LGAD signals with time resolution

~ 50ps per hit,

~ 35 ps per track with 2 hits.

- O Measuring arrival time of LGAD signal

- O Front-end: PA + Discriminator + TDC

- O L1 latency circular buffer

- O L1A-driven readout with zero suppression

- O A coarse map of (*delayed*) hits for L1 trigger, monitoring or luminosity

- O Interface of ETROC2

- O 40 MHz reference clock

- O I2C-based slow control

- O 320 Mbps fast control

- O Serial data link 320/640/1280 Mbps with two outputs

- O Waveform Sampling of preamp output (only 1 pixel)

- For monitoring purpose

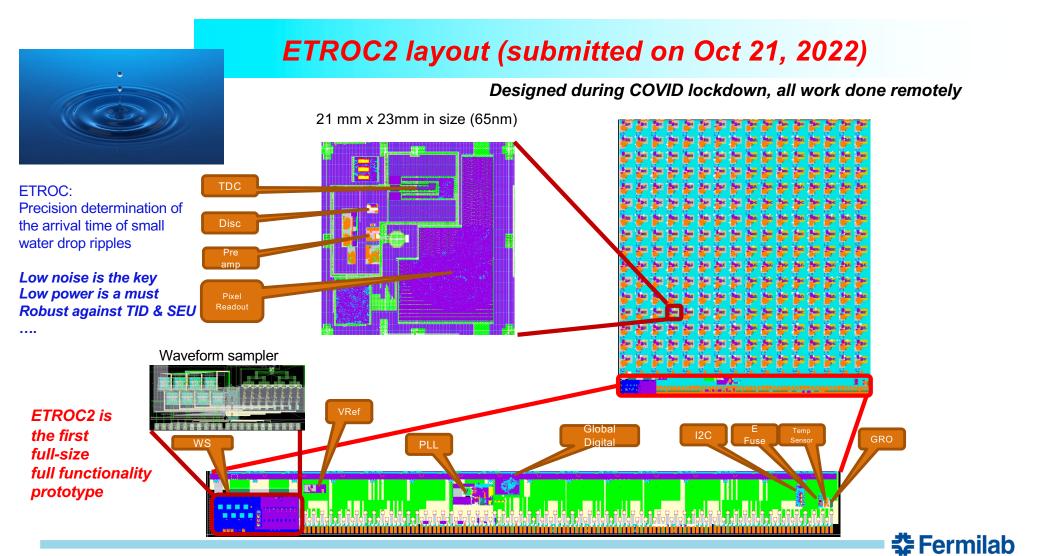

ETROC2 is designed in such a way as if it is the final design, very first full-size prototype, with full functionalities

(with extra flexibilities for performance study purposes)

#### Some of ETROC2 key features: from user point of view

- Each pixel has a low power high performance TDC, automatically self-calibrated for every hit recorded

- Important for precision timing performance and uniformity across 16x16 array

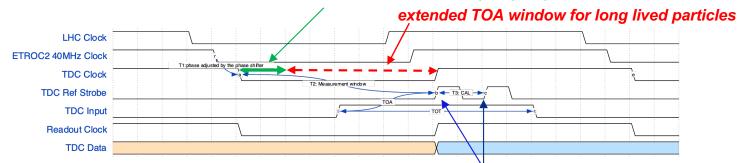

- Has large TOA window (effectively up to 11.4ns), can detect long lived or late arriving particles

Paper: https://ieeexplore.ieee.org/document/9446843

- Each pixel has auto-threshold scan capability to quickly determine preAmp baseline and noise width

- User-friendly, save a lot time for manual calibration during detector operation

- Paper: https://iopscience.jop.org/article/10.1088/1748-0221/16/09/T09006

- Flexible readout design

- user-defined window for TOA, TOT and CAL to filter/suppress hits before readout for each pixel

- user adjustable TOA measurement window (up to 12.5ns, 11.4ns effective)

- each pixel can be enabled or disabled for DAQ readout

- Two outputs for readout, each user configurable for 320/640/1280Mbps bandwidth

- L1 Trigger path (for monitoring, luminosity measurements or L1 trigger)

- a coarse map (user defined) hits continuously sent out every BC (on the same fiber as DAQ readout)

- user-defined window for TOA, TOT and CAL for triggered hit, can trigger on long lived or delayed particles

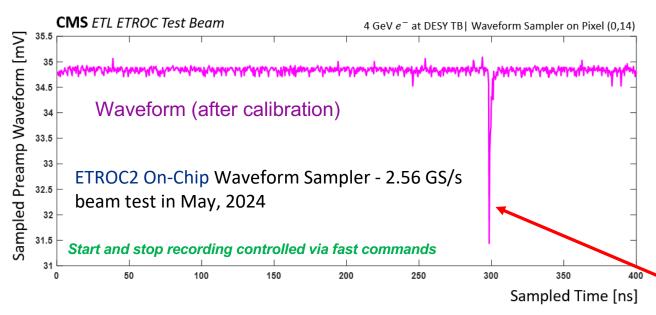

- On-chip 2.56 GSPS Waveform Sampler

- record waveform for one pixel up to 16 BC (400 ns), start/stop controlled via fast command, readout via I2C

- power-down when not used, intend for monitoring purpose during detector operation

- ETL has ~ 30k ETROC chips: this means 30k oscilloscope channels available

Paper: IEEE Transactions on Very Large Scale Integration Systems (TVLSI), Volume: 30, Issue: 2, Feb. 2022) Page(s): 123 133

- Charge injection and self-test pattern generator, on-chip PLL (lpGBT), temp sensor, efuse etc

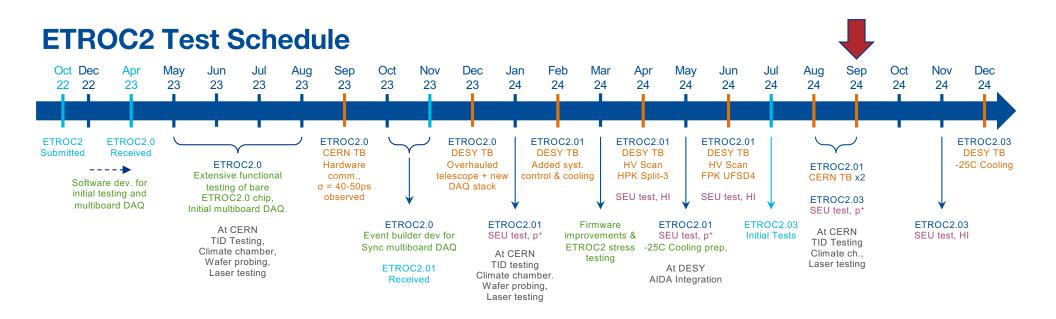

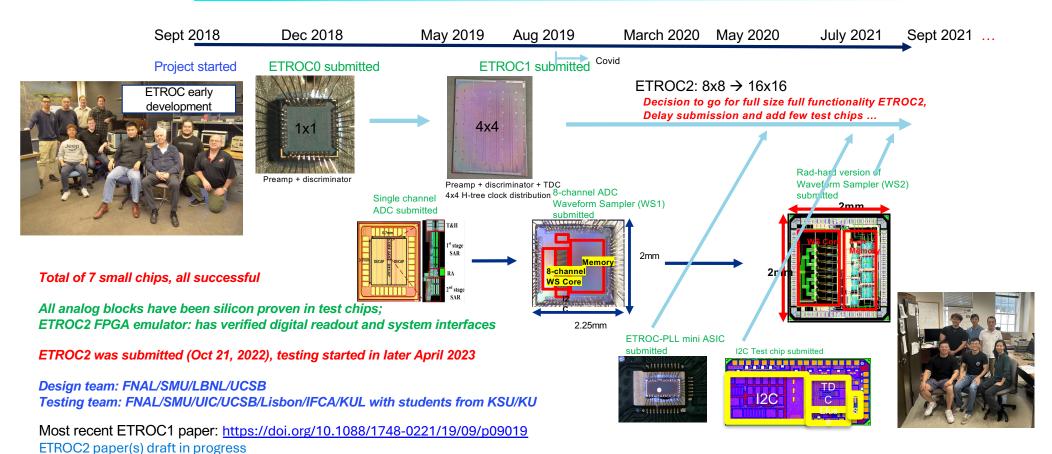

# ETROC2 Engineering Run at TSMC

TINOUZ Eligineering Run at Tolvio

N60R91:

6 corner wafers

(3 FFF + 3 SSS)

ETROC2.00

ESD defects

observed by

TSMC

8 wafers

released:

ETROC2.00

2 FFF diced for

testing

2 diced for

testing

20 wafers split in 2 lots (ETROC2)

works well

*lower yield (~70%)*

due to ESD issue Extensively tested

with

2 FFF diced for testing works well with very high yield Extensively tested 6 wafers on hold at TSMC. TSMC used them for investigation, and TSMC replaced them with a new lot TMSI07B-T1EAZN (for free)

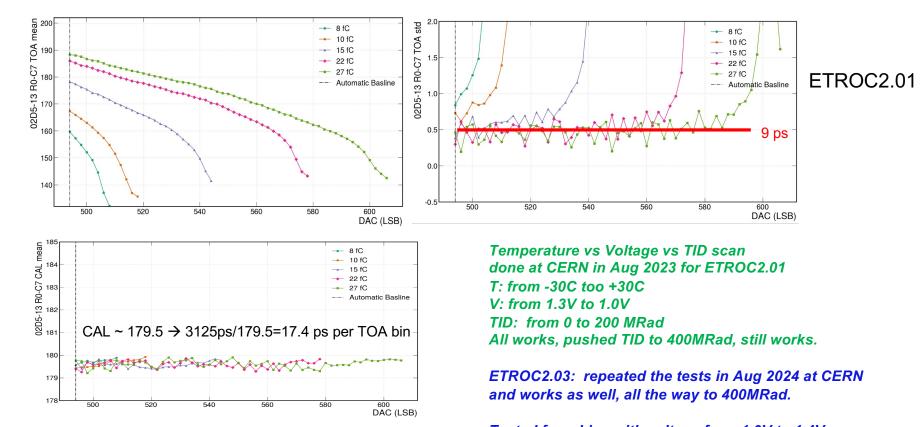

ETROC2.01 (N9VX36): extensively tested

2 wafers (7&8) released in July 2023 (with high yield: 97%)

(H-tree shielding grounded at metal 3: ESD issue solved)

processed at Pactech for UBM & bumps

ETROC2.03 (N9VX61): rapid progress in testing since July 2024 released at TSMC in May 2024 fixed three known minor issues from ETROC2.00 added optional dummy bump pads per pixel One wafer thinned and diced for testing (received July 2024) One wafer processed at Winstek (UBM&bump) (received Sept 2024)

2 more wafers still on hold at TSMC

Submitted

Oct 2022.

received

late April

2023

Diced chips

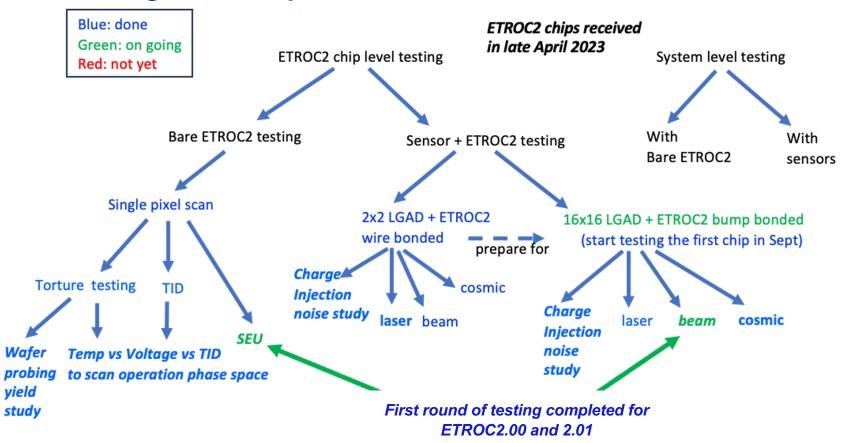

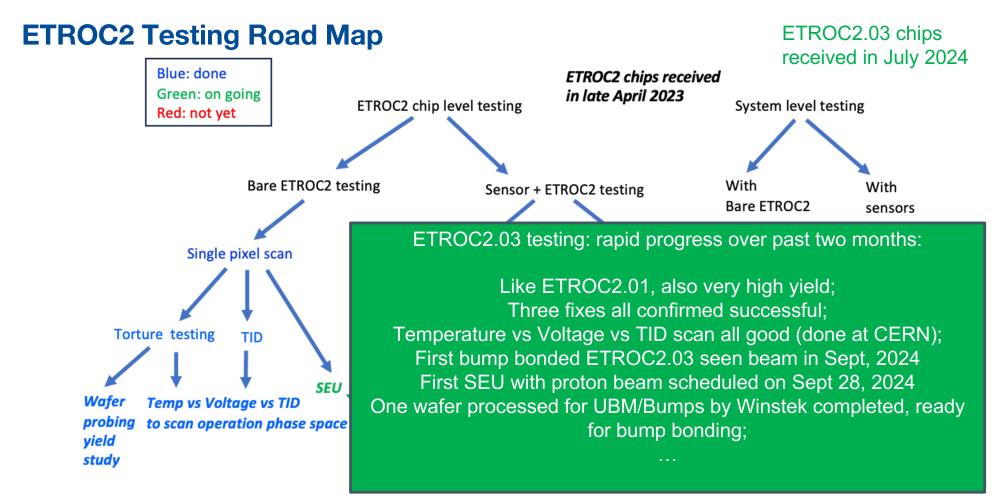

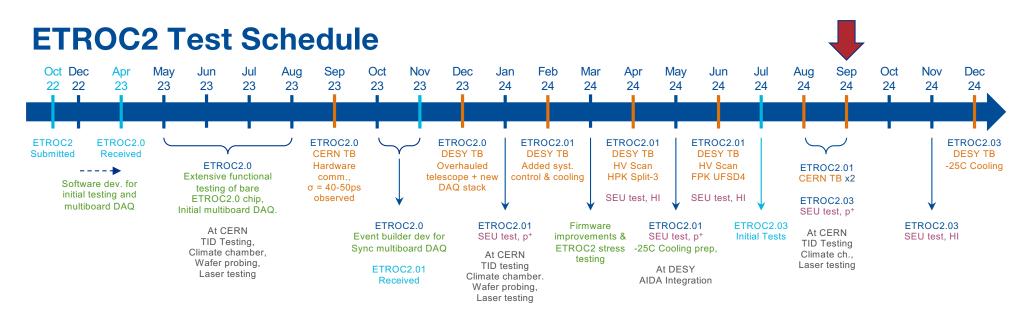

### **ETROC2 Testing Road Map**

ETROC2.00/2.01 have been extensively tested, ETROC2.03 is being tested as if it is the final version Fermilab

10/1/2024

ETROC2.00 and 2.01 have been extensively tested over the past year ETROC2.03 testing on going, so far so good (all three fixes confirmed successful)

To be done: testing in cold, with irradiated sensors Improve SEU test setup for one more round of testing Improve bump bonding yield

Only a few highlights of the test results in this talk

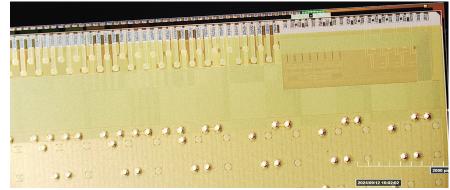

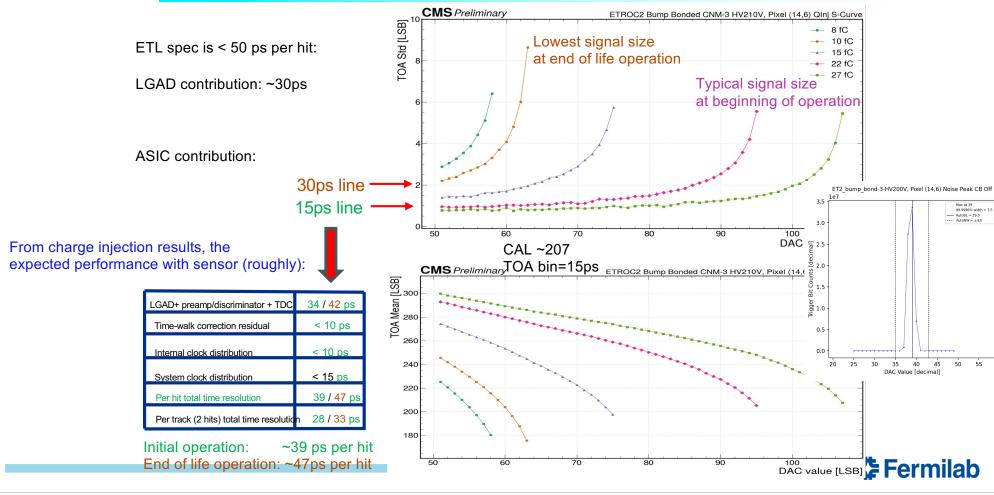

### Bump bonded ETROC2 performance with charge injection

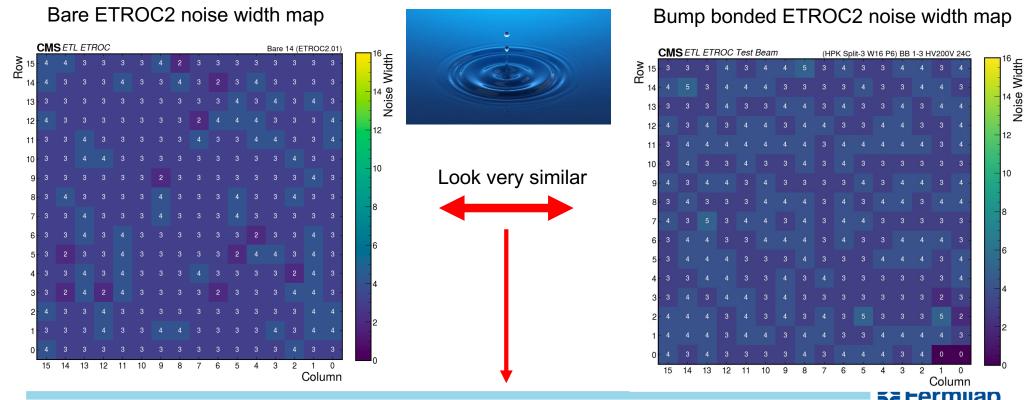

ETROC2 has in-pixel automatic threshold scan capability (through I2C command), to determine the baseline and noise width for each pixel (very fast, to map out 16x16 array), see paper below:

https://iopscience.iop.org/article/10.1088/1748-0221/16/09/T09006

The bump bonded ETROC2 noise is so low that it is NOT easy to tell if a pixel is bump bonded with sensor

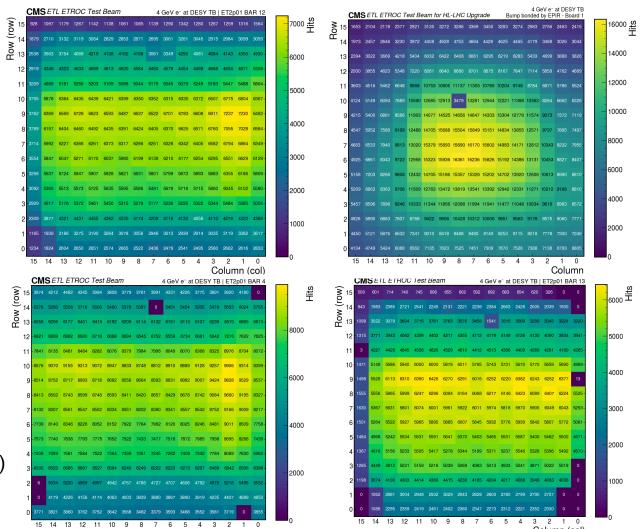

Beam spot (hits occupancy map) on ETROC2 bump bonded with sensor

# All pixels are connected (100% bump bonding)

Left: done at Barcelona Right: fully processed by EPIR (sensor/ASIC)

Just some examples used in beam tests

some chips with pixels not fully connected

(some poorly connected, not shown here)

Bump bonding yield to be improved

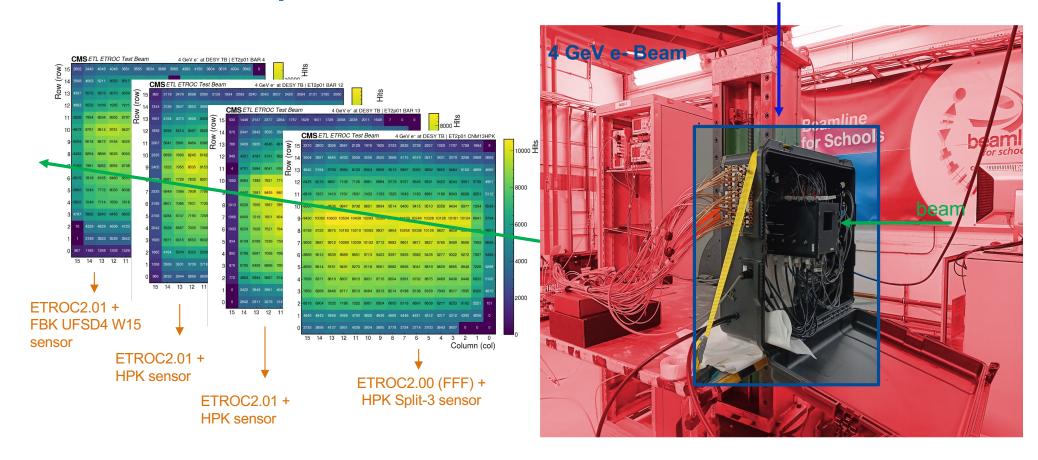

## ETROC2 Telescope at DESY Jun 2024

#### ETROC2 suitcase telescope

## Board information inside telescope at DESY in May-June 2024

Name: Barcelona 4

• ETROC2.01

Sensor UBM: PacTech

ETROC UBM/Bumps: Pactech

Bump bonding: Barcelona

• LGAD: FBK UFSD4 W15 2-3

• Name: Barcelona 13

ETROC2.01

Sensor UBM: HPK

ETROC UBM/Bumps: Pactech

• Bump bonding: Barcelona

LGAD: HPK P6

• Name: Barcelona 12

• ETROC2.01

Sensor UBM: HPK

• ETROC UBM/Bumps: Pactech

• Bump bonding: Barcelona

• LGAD: HPK P5

Reference board

100% pixels connected

Name: BB 1-3

• ETROC2.00 FFF corner

• Sensor UBM: HPK

ETROC UBM: CNM; Bumps: Barcelona

Bump bonding: Barcelona

LGAD: HPK W16 P6 - Split3

Reference

board

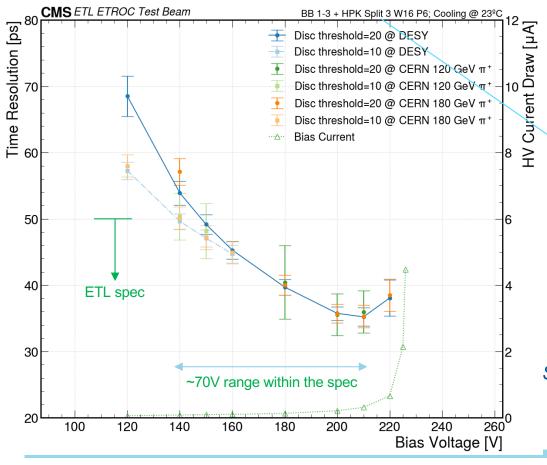

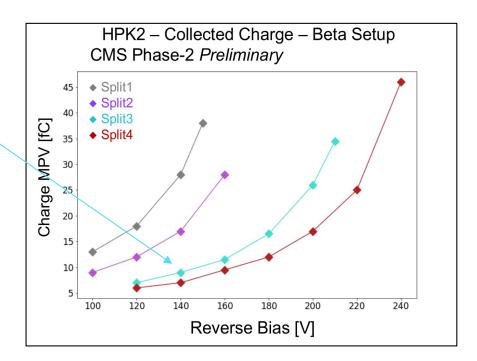

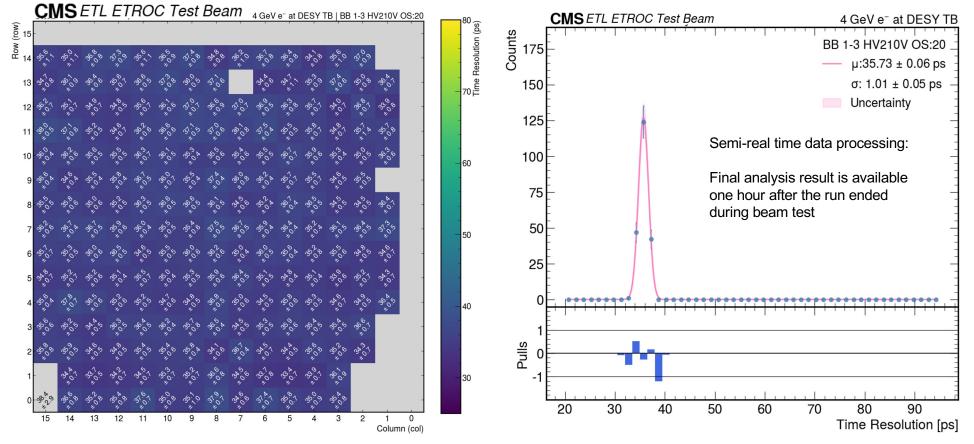

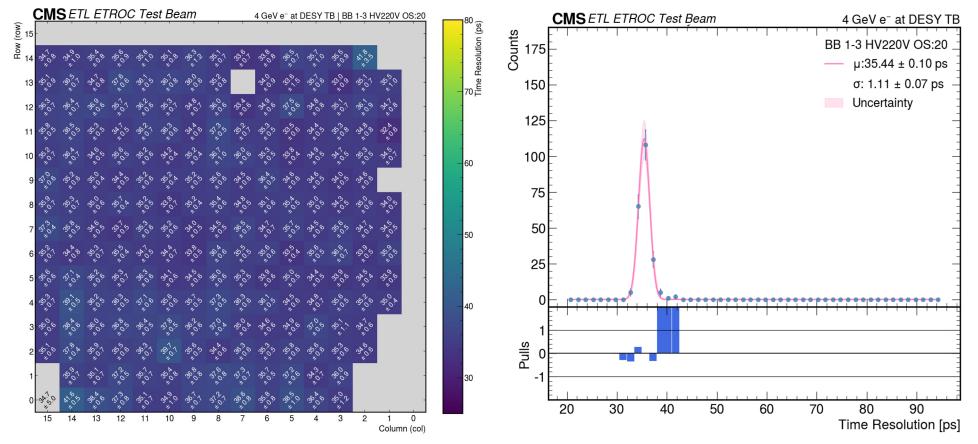

### ETROC2 beam test at DESY (June) and CERN (Aug and Sep 2024)

Successfully reproduced ~35ps res. with this board. Results from CERN 120-180 GeV  $\pi^+$  beams agree with those from DESY 4GeV e-beam

To be done: test in cold, and w/ irradiated sensors

10/1/2024

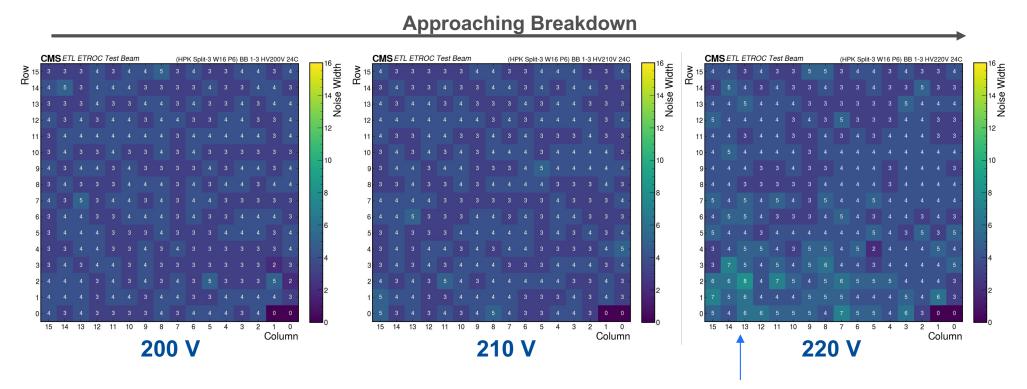

### 210V HV point for HPK Split-3 + ETROC2.00

Pixel resolution map over 16x16 array

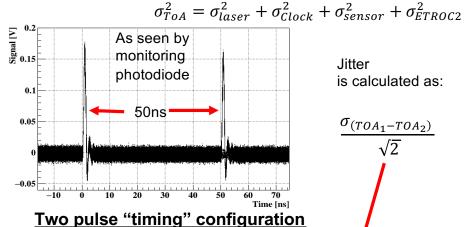

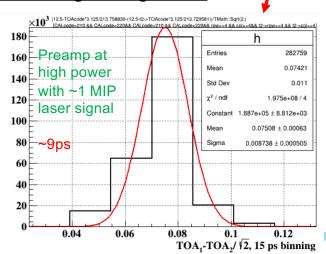

#### **Bump bonded ETROC2 performance with a double pulse IR laser at CERN-SSD**

ETROC2 bump bonded with 16x16 HPK sensor

## **ETROC2 Waveform Sampler**

WS Paper: IEEE Transactions on Very Large Scale Integration Systems (TVLSI), Volume: 30, Issue: 2, Feb. 2022) Page(s): 123 – 133

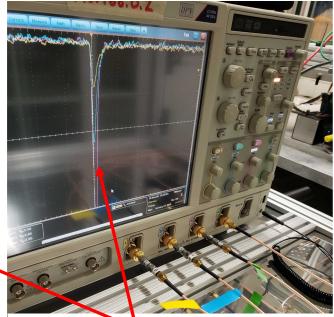

4 years after the recording of ETROCO preamp waveforms using high speed Oscilloscope, we can now use ETROC2 on-chip waveform sampler to do the same with ETROC2 self-triggering capability

ETROCO Preamp output waveform by Oscilloscope (40GS/s) in Jan, 2020 (beam test at Fermilab)

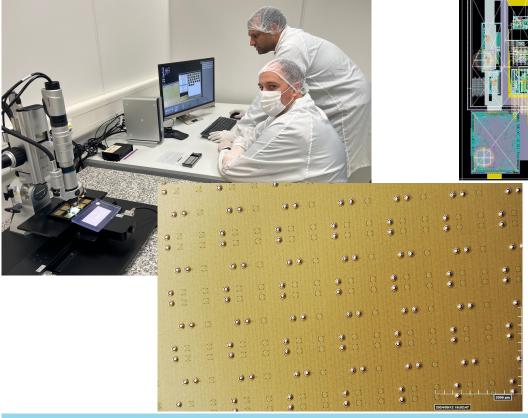

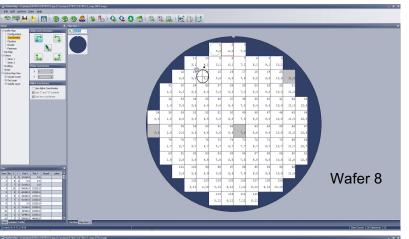

## Wafer probe testing for ETROC2 wafers

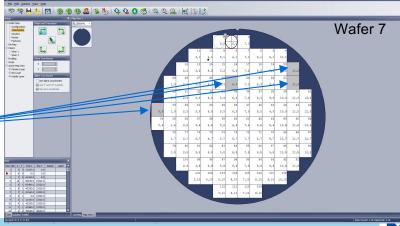

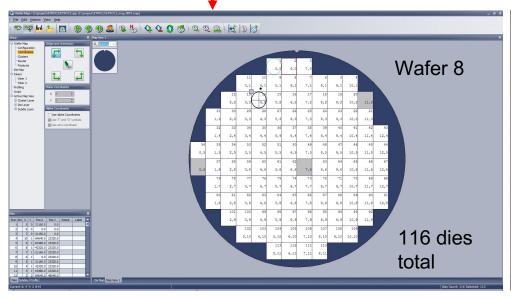

Two new ETROC2.01 wafers from TSMC Arrived CERN in Aug 2023

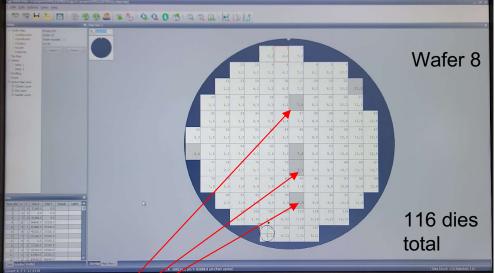

probe testing shows only 4 bad dies (out of 116 dies) per wafer in each case

Production QC procedure developed and established for wafer probe testing.

Wafer 7 & 8 processed at Pactech for UBM and bumps, wafer 7 was thinned and diced for testing, while wafer 8 is not diced as a control sample.

Wafer probing testing results for wafer 8, before and after Pactech UBM/bump processing

Last Aug 2023 → Pactech UBM/bumping at wafer level → Jan 2024 (Jan 13-14 weekend at CERN)

Three new dies with power shorts, the rest all passed testing Fermilab (yield is still high, Pactech informed)

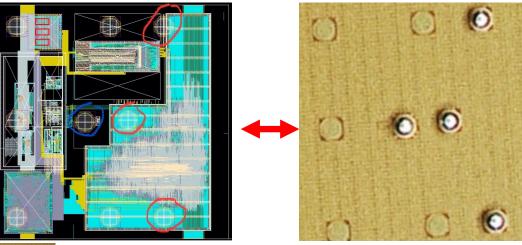

#### ETROC2.03: three minor modifications at metal layers with wafers on hold at TSMC

Three minor modifications at metal layers implemented in ETROC2.02 in late 2023 (not submitted) In early 2024, added dummy pads for each pixel, submitted as ETROC2.03 for two wafers on hold at TSMC

8 dummy/optional pads added, to study bump density vs yield, plan to test with 3 (circled in red)

ETROC2.00/2.01 have been extensively tested, ETROC2.03 is being tested as if it is the final version

10/1/2024

#### Charge vs DAC scan after 200 Mrad. (ETROC spec is 100MRad)

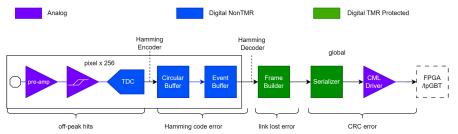

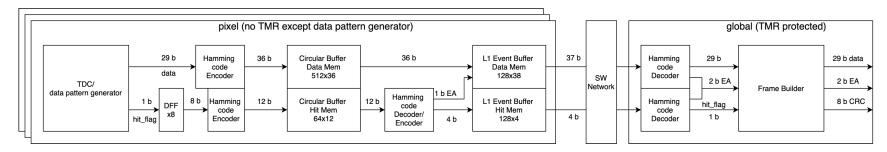

# Overview of SEU protection strategy for ETROC2

- Overall readout operation

- Global readout: heavily TMR protected, because it is critical for detector operation

In addition, CRC code is used for each data frame/package.

- Pixel readout: No need for TMR

- Because the readout architecture is such that all readout is globally coordinated/controlled

- Save digital power, footprint, and easy for place and route

- Instead, we use Hamming code for each TDC hit data for error detection and correction

- Configuration registers

- Some configuration bits are critical for detector readout operation

- Global register could affect whole chip

- Pixel register would affect only one pixel

- All configuration bits are heavily TMR protected (global and pixel)

- Bit-flip should be kept at a minimum level

- SEU test should pay special attention to them (esp. global configuration bits)

- Status registers

- Mostly are not used during detector operation

- Except of PLL capacitor array configuration and pixelID.

- They do not affect operation if flipped.

- Nevertheless, they are TMR protected but can be disabled by user

This feature can be used to monitor beam spot during beam testing(16x16 pixels)

ETROC2 design: everything should be TMRed has been TMRed, and carefully checked/verified at block level.

However, due to lack of person power and expertise, we did not have time to perform full blown TMR verification before submission.

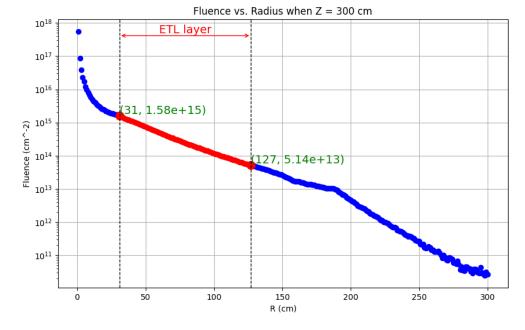

# Weighted average fluence for ETL layer

$$F_{avg} = \sum_{i=31}^{127} \frac{F_i \times R_i}{\sum_{k=31}^{127} R_k}$$

- The larger radius area has more pixels thus has larger weight in calculation the average fluence.

- The weighted average fluence is 2.86×10<sup>14</sup> h/cm<sup>2</sup>

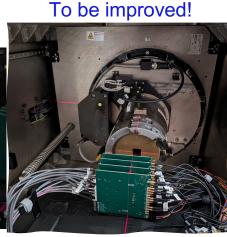

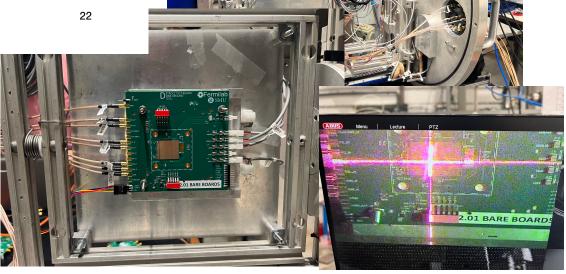

# The proton beam SEU campaign

ET2 Bare 12 ET2 Bare 11

ET2 Bare 15

The weighted average ETL fluence is 2.86×10<sup>14</sup> h/cm<sup>2</sup>

Beam

#### Beam:

- Northwestern Medicine Proton Center in Chicago, May 11<sup>th</sup>, 2024

- Proton beam @ 217 MeV

- Beam size 2x2 cm² Measured about 3x3 cm²

#### Setup:

- 4 "Bare" ETROC chip boards were configurated in Qinj mode. Fixed time delayed L1A commands were sending to ETROC chips during irradiation.

- ETROC chip was reconfigured before all runs. The I2C configuration/status change were checked for each run

4 "Bare" ETROC chips were irradiated up to  $6.82 \times 10^{13}$  p/cm<sup>2</sup> over 17 runs

ET2 Bare 14

The setup is rather involved with many long cables ...

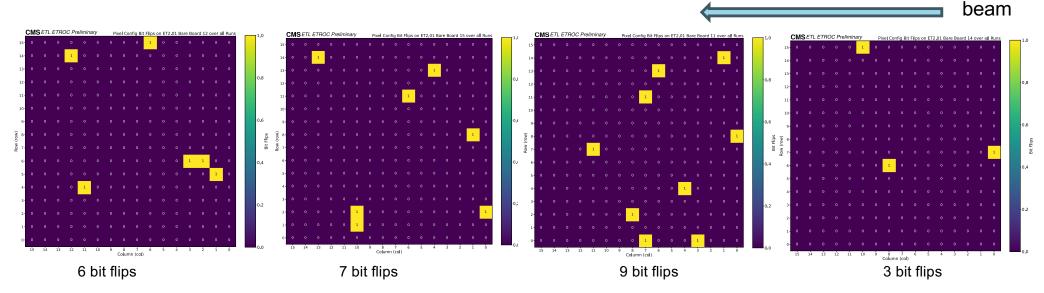

# Bit flips of configuration registers

Zero global configuration bit flipping observed (out of 4x32x8 ~ 1024 bits), this is good.

Total of 25 pixel configuration bits flipping observed, only 11 would affect data quality during operation.

- The bit flips are randomly distributed on each board

- There is no pixel gets two or more bit-flips for a given upset.

- The pixel is identical at layout level by design.

Overall 4x256x32x8= 262144 bits of memory cells are exposed to the beam with fluence 6.82x10<sup>13</sup> p/cm<sup>2</sup>.

- One lpGBT has ~494x8 = ~3952 bits

**‡** Fermilab

ETL operation per 24 hours run:

~ 3.22×10<sup>11</sup> h/cm<sup>2</sup>

# Cross-section of SEU on pixel configuration

The potential impact on all pixels (7.68 Millions) for ETL is at 10^-5 level for a 24 hours run. All configuration bits will be reconfigured at the beginning of each run, and can be read-back end of run

| Index | Name                                                     | Number                                           | Source                   |

|-------|----------------------------------------------------------|--------------------------------------------------|--------------------------|

| 1     | Pixels impacted in 4 boards (or 1024 pixels)             | 11                                               | Measurement in beam test |

| 2     | Total fluence in proton beam test                        | 6.82×10 <sup>13</sup> p/cm <sup>2</sup>          | Measurement in beam test |

| 3     | Cross section per pixel                                  | (1.575±0.475) ×10 <sup>-16</sup> cm <sup>2</sup> | Compute from 1 and 2     |

| 4     | Levelled Luminosity                                      | 5.00×10 <sup>34</sup> /cm <sup>2</sup> /sec      |                          |

| 5     | Operation time per run (24 hours)                        | 9×10 <sup>4</sup> sec                            |                          |

| 6     | Integrated luminosity per run (24 hours)                 | 4.5 fb <sup>-1</sup>                             | Compute from 4,5         |

| 7     | ELT layer fluence (> 20 MeV hadron),4000fb <sup>-1</sup> | 2.86×10 <sup>14</sup> h/cm <sup>2</sup>          | CMS detector simulation  |

| 8     | Fluence per run (> 20 MeV hadron)                        | 3.22×10 <sup>11</sup> h/cm <sup>2</sup>          | Compute from 6,7         |

| 9     | Probability a pixel affected by SEE (pixel only)         | (5.07±1.53)×10 <sup>-5</sup>                     | Compute from 3 and 8     |

| 10    | Total ETL pixels (30 K chips)                            | 7.68×10 <sup>6</sup> ~ 5x10^-5                   | level pixels per run     |

| 11    | SEE affected pixels per run                              | 389±117                                          | Compute from 9 and 10    |

## SEU test for readout chain

#### What types of errors to look for during SEU testing:

- Off peak hits: Qinj events are expected to have a fixed TOA and TOT codes. Defines the hits beyond 4 STD deviation of TOT/TOA/CAL code distribution as off-peak hits.

- Hamming code error: Check two bits of EA for each TDC data. 00: No error. 01: 1 bit Error, self-corrected in frame builder. 10: 2 bits error, no correction

- CRC errors: If the received data frame does not pass the 8bit CRC check, it is tagged as CRC error

- Link lost error: FPGA can not reconstruct data frames or no data frame received.

# Readout error counts during SEU testing

| run   |    | duration(sec) | Fluence(p/cm2) | hits#     | Off-peak hits |    | Hamming code<br>Error (EA=01) | Hamming code<br>Error (EA=10) | Link Lost error |   | Reference runs,    |

|-------|----|---------------|----------------|-----------|---------------|----|-------------------------------|-------------------------------|-----------------|---|--------------------|

|       | 1  | 60            |                | ) (       |               |    | ` ′                           | 0                             | 0               | 0 | no beam            |

|       | 2  |               |                | 1954224   |               | 0  |                               | 0                             | 0               | 0 |                    |

|       | 3  |               |                |           |               | _  |                               | 0                             | 0               | 0 |                    |

|       | 4  | 6             |                |           |               | _  |                               | 0                             | 0               | 0 |                    |

|       | 5  | _             |                |           |               | U  |                               | 0                             | 0               | 0 | Runs with beam, no |

|       | 6  |               |                |           |               | 0  |                               | 1                             | 0               | 0 | CRC error          |

|       | 7  | 208           |                |           |               |    |                               | 0                             | 0               | 0 | Orto choi          |

|       | 8  |               |                |           | ·             | •  |                               | 0                             | 0               | 0 |                    |

|       | 9  |               |                |           |               | ·  |                               | 0                             | 0               | 0 |                    |

|       | 10 |               |                | 2 1043072 |               | 42 | \                             | 26                            | 0               | 0 |                    |

|       | 11 |               |                |           |               | 0  | \                             | 0                             | 0               | 0 |                    |

|       | 12 |               | 6.41E+10       |           |               | 0  | \                             | 0                             | 0               | 0 |                    |

|       | 13 |               |                |           |               |    | \                             | -                             | 0               | 0 | Runs with beam,    |

|       | 14 |               |                |           |               |    | \ \                           | 0                             | 0               | 0 | with CRC error     |

|       | 15 |               |                |           |               |    | \ \                           | 0                             | 0               | 0 |                    |

|       | 16 |               |                |           |               | 0  | \ \                           | 0                             | 0               | 0 |                    |

|       | 17 | 360           | 1.42E+1        | 3 80400   | 0             | 0  |                               | 0                             | 0               | 0 |                    |

| v cle | an | _             |                |           |               |    | 44                            |                               |                 |   |                    |

Mostly clean, except potential setup issues, to be improved.

Likely due to (complicated) setup issue (instability), being improved ....

# Heavy Ion SEU test at UC Louvain

Bits flipping pattern similar with proton beam

Next time: run additional HI with Al, Cr and Rh, with improved setup

| lon | LET<br>[MeV/mg/cm²] | Fluence<br>[p/cm²] | Time<br>[s] | Important<br>Peripheral Config<br>Bit Flips | Important Pixel<br>Config Bit Flips |

|-----|---------------------|--------------------|-------------|---------------------------------------------|-------------------------------------|

| Ar  | 9.9                 | 1.20E+08           | 8640        | 0                                           | 0                                   |

| Kr  | 32.4                | 4.00E+07           | 2880        | 0                                           | 1                                   |

| Хе  | 62.5                | 6.50E+07           | 4935        | 0                                           | 22                                  |

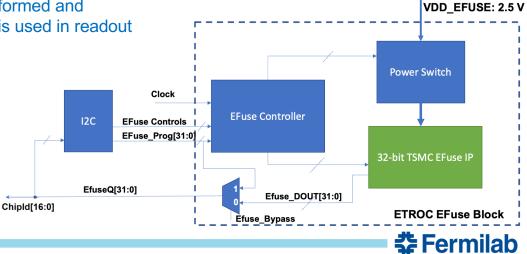

### eFuse module in ETROC2.03

- ETROC2 integrated a 32-bit TSMC eFuse IP block to store the chip ID to allow chip tracking from wafer probe testing to end of operation

- The eFuse input clock selection was wrong in ETROC2.00 and fixed in ETROC2.03.

- IpGBT group found that eFuse IP had reliability issue after radiation

- Less than 1% reading error rate when radiation dose less than 100 MRad

- About 1.26E-4/bit burning failure rate

- ETROC uses eFuse to store 17 bits of chipID. The remaining 15 bits can be used for FEC code to correct the potential bit error.

- The FEC code can be calculated and burned into 32 bit of eFuse as well as original chipID.

When we read the eFuse, the decoder algorithm is performed and the corrected chipID is written into I2C registers which is used in readout and TMR protected.

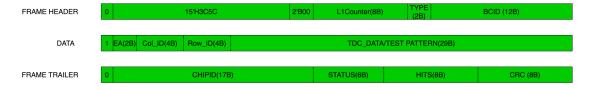

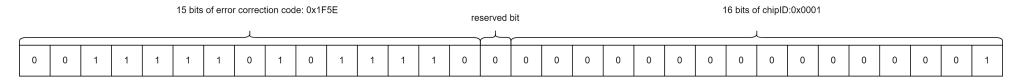

# ETROC2.03 eFuse register definition

- The codeword is stored in eFuse 32-bit register

- The 32 bits of the word is divided into ChipID(16 bits), reserved bit(1 bit) and error correction bits (15 bits)

- We can further define for production: batch#, wafer #, and chip location on each wafer

- For example: 3 bits 6 bits, 7 bits

- Would mark: 8 batch. 2x25=50 wafers ~120 chips per wafer

Efuse ChipID can help us to keep track each ETROC chips for production:

From cradle to grave

More importantly, helps us to keep track of which sensor is bump bonded with which ETROC From bonding to grave

### Initial experience: The first 12 ETROC2.03 chips with eFuse burned

First ETROC2 engineering run, from first ETROC2.03 wafer (for testing purpose)

| ChipID (16b) | Reserve bit(1b) | ECC(15b) | eFuse Word (32b) |

|--------------|-----------------|----------|------------------|

| 0x0001       | 0               | 0x0FAF   | 0x1F5E0001       |

| 0x0002       | 0               | 0x1F5E   | 0x3EBC0002       |

| 0x0003       | 0               | 0x10F1   | 0x21E20003       |

| 0x0004       | 0               | 0x3EBC   | 0x7D780004       |

| 0x0005       | 0               | 0x3113   | 0x62260005       |

| 0x0006       | 0               | 0x21E2   | 0x43C40006       |

| 0x0007       | 0               | 0x2E4D   | 0x5C9A0007       |

| 0x0008       | 0               | 0x7D78   | 0xFAF00008       |

| 0x0009       | 0               | 0x72D7   | 0xE5AE0009       |

| 0x000A       | 0               | 0x6226   | 0xC44C000A       |

| 0x000B       | 0               | 0x6D89   | 0xDB12000B       |

| 0x000C       | 0               | 0x43C4   | 0x8788000C       |

ChipID = 7 chip has been tested to 200MRad, no efuse bit changed during TID

ChipID = 9 chip has been tested to 200 and then 400MRad, no efuse bit changed during TID

# Number of ETROC2 chips tested so far

| sts              |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board Generation |                                                                                                            | Date                                                                                                                                                                                                                                                                                                                                                                           | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ET2.00, Typical  | 200 MRad                                                                                                   | 2023 Aug                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ET2.00, Typical  | 200 MRad                                                                                                   | 2023 Aug                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ET2.00, Typical  | 200 MRad                                                                                                   | 2023 Aug                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ET2.00, Typical  | 200 MRad                                                                                                   | 2023 Sep                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ET2.00, Typical  | 200 MRad                                                                                                   | 2023 Sep                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | 400 MRad                                                                                                   | 2024 Jan                                                                                                                                                                                                                                                                                                                                                                       | Wire-bonded                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ET2.03, Typical  | 200 MRad                                                                                                   | 2024 Aug                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ET2.03, Typical  | 400 MRad                                                                                                   | 2024 Aug                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Generation ET2.00, Typical ET2.00, Typical ET2.00, Typical ET2.00, Typical ET2.00, Typical ET2.00, Typical | Generation         TID           ET2.00, Typical         200 MRad           ET2.03, Typical         200 MRad           ET2.03, Typical         200 MRad | Generation         TID         Date           ET2.00, Typical         200 MRad         2023 Aug           ET2.00, Typical         200 MRad         2023 Aug           ET2.00, Typical         200 MRad         2023 Aug           ET2.00, Typical         200 MRad         2023 Sep           ET2.00, Typical         200 MRad         2023 Sep           ET2.00, Typical         200 MRad         2024 Jan           ET2.03, Typical         200 MRad         2024 Aug |

#### **SEU** tests

| Board          | Location              | Fluence (p/cm2) | Date     | Comment |     |

|----------------|-----------------------|-----------------|----------|---------|-----|

| ET2.01 Bare 1  | Northwestern hosptial | 4.75E+13        | 2024 Jan |         |     |

| ET2.01 Bare 4  | Northwestern hosptial | 4.75E+13        | 2024 Jan |         |     |

|                |                       | Xe: 1.1804E+8   |          |         |     |

| ET2.01 Bare 5  | UC Louvain            | Ar: 2.7E+7      | 2024 Apr |         |     |

|                |                       | Kr: 2.7E+7      |          |         |     |

| ET2.01 Bare 11 | Northwestern hosptial | 6.19E+13        | 2024 May |         | . H |

| ET2.01 Bare 12 | Northwestern hosptial | 6.19E+13        | 2024 May |         | i   |

| ET2.01 Bare 14 | Northwestern hosptial | 6.19E+13        | 2024 May |         |     |

| ET2.01 Bare 15 | Northwestern hosptial | 6.19E+13        | 2024 May |         |     |

|                |                       | Xe: 6.5E+7      | 2024 Jun |         |     |

| ET2.01 Bare 7  | UC Louvain            | Ar: 1.2E+8      | 2024 Jun |         |     |

|                |                       | Kr: 4.0E+7      | 2024 Jun |         |     |

|                |                       |                 |          |         |     |

In total,

8 ETROC2 wafers have been probe tested (~116 dies/wafer)

163 chips have been tested on ETROC test boards;

8 chips tested for TID (200-400MRad)

16 chips tested for SEU

+ 8 ETROC2.03 in proton beam for SEU on Sept 28, 2024.

# How does one travel with precision timing telescopes?

Many people involved in the ETROC tests (with strong support from CERN and DESY!)

### ETROC2 Testing Summary...

- ETROC2.00 and 2.01 have been extensively tested over the past year, performance meets/exceeds specifications

- ETROC2.03 testing on going, so far so good (all three minor fixes confirmed successful)

To be done: testing with irradiated sensors in beam; Improving SEU test setup for one more round of testing, improving bump bond yield.

Special thanks to the wonderful support provided by CERN/DESY for our testing

# **Backup slides**

### **ETROC** Early Prototyping Phase

#### ETROC power consumption estimate vs measurements

|          |                             |              |            |           | ETROC0/E   | TROC1 testing results |

|----------|-----------------------------|--------------|------------|-----------|------------|-----------------------|

|          | ETROC0/1 de                 |              |            |           |            |                       |

|          | Circuit component           | Power per ch | annel [mW] | Power per | ASIC [mW]  |                       |

|          | Preamplifier (low-setting)  | 0.67         | 0.76 0.74  | 171.5     | 189.4 (pre | amp low power)        |

| Table ◀  | Preamplifier (high-setting) | 1.25         | 1.31 1.27  | 320       | **         | the highest power)    |

| from TDR | Discriminator               | 0.71         | 0.87 0.84  | 181.8     | 215.0 `    | , ,                   |

|          | TDC                         | 0.2          | 0.07 0.1   | 51.2      | 25.6       |                       |

|          | SRAM (→ memory)             | 0.35         | 0.25 (sim) | 89.6      | 64.0       |                       |

|          | Supporting circuitry        | 0.2          | 0.2        | 51.2      | 51.2       |                       |

|          | Global circuitry            |              | (reserve)  | 200       | 234.5      |                       |

- Measurements agree with simulation of ETROC0 and 1 design Sum: ~780/915/980 mW (low/high/highest power)

- But should assume up to 20% variation with real production

Use 980mW & add 20% for worst case.

- Note: preamp highest setting (4<sup>th</sup> gear) power is 1.52mW (measured), the high-setting above is the 3<sup>rd</sup> gear.

#### ETROC2 measurements on three bump bonded chips (room temperature):

Earlier estimate during design stage:

Typical chip low power: 346/138 mA analog/digital → 581 mW

Corner FFF low power: 402/247 mA → 779 mW

780mW (preamp low power)

Typical chip high power: 477/138 mA analog/digital → 738 mW → 980mW (preamp high power)

Corner FFF high power: 525/247 mA → 926 mW

The ETROC2 power consumption meets ETL requirements (the original estimate was conservative enough)

Much of the power saving was due to extensive optimization of the digital activities (to minimize noise)

## Noise Widths during HV Scan for HPK Split-3 + ETROC2.00

Sensor getting close to break down, some pixel noise width gets "warm"

### 220V HV point for HPK Split-3 + ETROC2.00

Pixel resolution map over 16x16 array

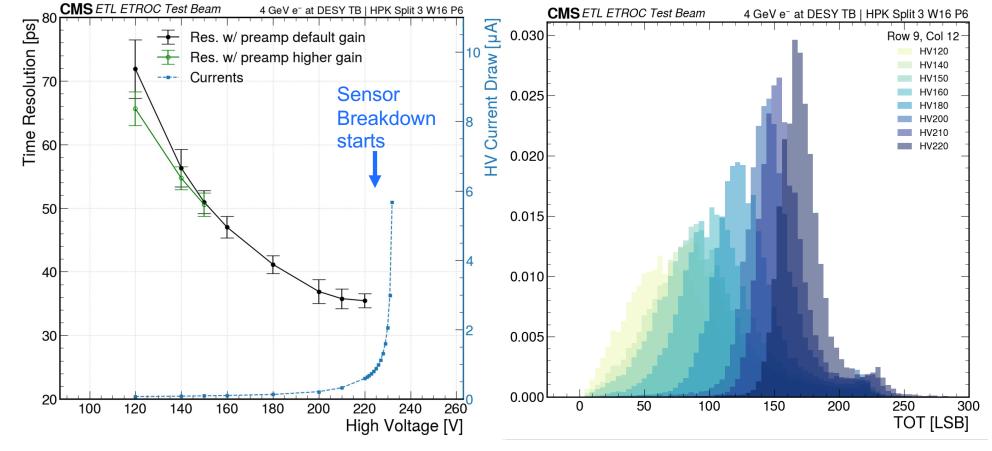

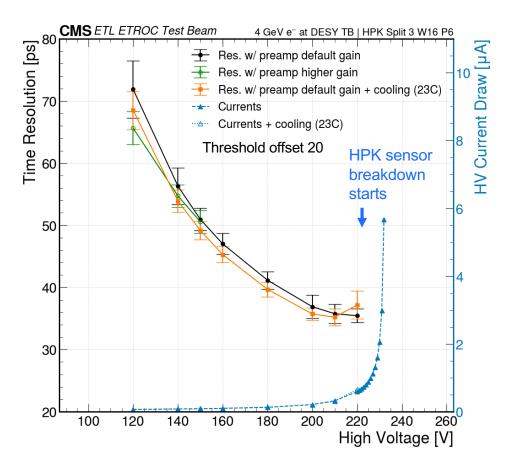

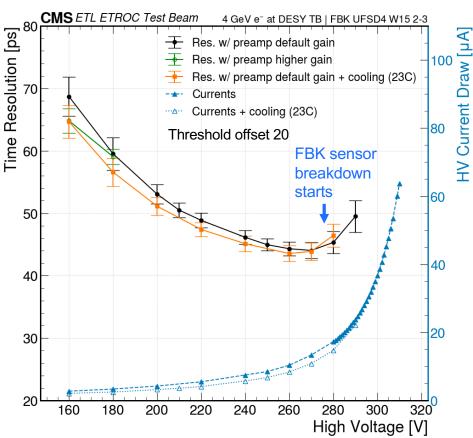

## HV Scan for HPK Split-3 + ETROC2.00: w/o temp control

### HV Scans for ETROC2: HPK vs FBK (preamp default vs high gain)

Temp control improves ~ few ps,

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 68, NO. 8, AUGUST 202

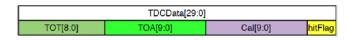

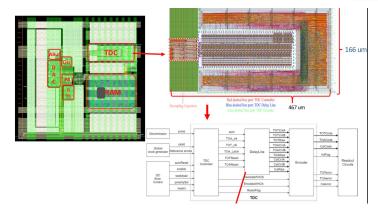

# ETROC TDC

A Low-Power Time-to-Digital Converter for the CMS Endcap Timing Layer (ETL) Upgrade

hitFlag: discriminator is fired or not

□ bin= T3/Cal\_code

☐ TOA=12.5 - bin\*TOA\_code

T3 is programable with 3.125 ns by default.

Normal TOA window for prompted particles from collisions

https://ieeexplore.ieee.org/document/9446843

Double time-stamps for self-calibration "on the fly", to calibrate TDC bin size in real time for every hit (very important feature of this TDC design)

**‡** Fermilab

## One ETROC2.03 wafer processed UBM/bumps/thinning/dicing

Chips received from Winstek on Sept 12, 2024