# HKROC: an integrated readout chip designed to facilitate the readout of a large number of photomultiplier tubes for the next generation of neutrino experiments

<u>conforti@omega.in2p3.fr</u> S. CONFORTI DI LORENZO,

Antoine Beauchêne, Sara Bolognesi, Florent Bouyjou, Denis Carabadjac, Frederic Dulucq, Miroslaw Firlej, Tomasz Andrzej Fiutowski, Franck Gastaldi, Fabrice Guilloux, Marek Idzik, Christophe de La Taille, Aleksandra Molenda, Jakub Moron, Jerome Nanni, Benjamin Quilain, Rudolph Rogly, Damien Thienpont

#### Organization for Micro-Electronics desiGn and Applications

#### A read-out for multi-ton neutrinos experiments

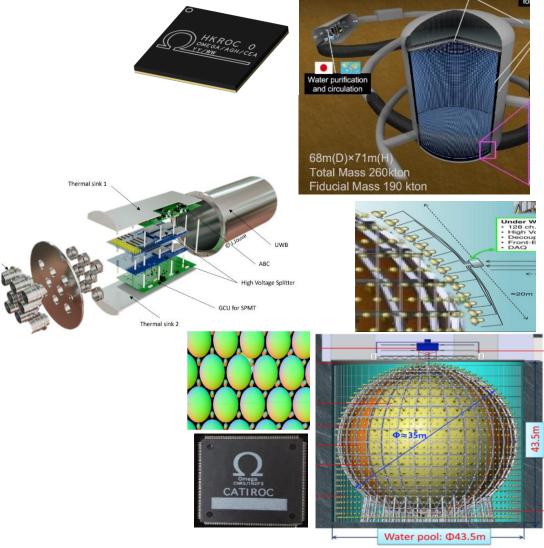

The HKROC ASIC was originally designed to read out Photomultiplier Tubes (PMTs) for the Hyper-Kamiokande experiment.

As next-generation neutrino experiments continue to expand in scale, with an increasing number of PMTs,

there is a growing need for fully integrated electronic systems.

- Multichannel

- Auto-trigger acquisition mode

- High speed

- Low noise

- Large dynamic range

- Precise charge and time measurements

Omega has extensive experience in ASIC design for neutrino physics,

having developed several ASICs in recent years:

| <b>PARIROC</b> 2007 | BiCMOS SiGe<br>350 nm | First ASIC that was a veritable SoC in auto-trigger mode                                                   |

|---------------------|-----------------------|------------------------------------------------------------------------------------------------------------|

| <b>CATIROC</b> 2015 | BiCMOS SiGe<br>350 nm | Based on the PARISROC ASIC, which will be installed in the <b>SPMT system of the JUNO detector</b> (China) |

| <b>HKROC</b> 2020   | CMOS 130 nm           | Based on the ASIC HGCROC for the CMS High Granularity Calorimeter                                          |

#### 1 p.e. = 2 pC

| Physics constraint                                                                                    | Impact on electronics requirementSelf triggering for each channel                                            |  |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Detect synchronous & asynchronous events (accelerator/atmospheric/solar/supernova neutrinos, p decay) |                                                                                                              |  |

| No event loss<br>(e.g. crucial for SN neutrino)                                                       | High hit rate<br>(e.g. 1 MHz)                                                                                |  |

| Low energy events detection<br>(e.g. SN or solar neutrino)                                            | Low threshold triggering<br>(e.g. <= 1/6 p.e.)                                                               |  |

| Charge reconstruction<br>from low to high energy physics                                              | Large dynamic charge range (1 - 1300 p.e.)<br>photoelectrons                                                 |  |

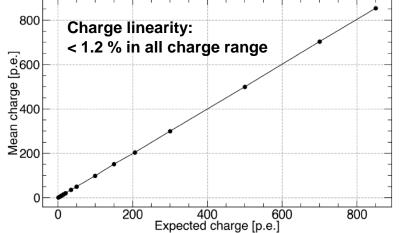

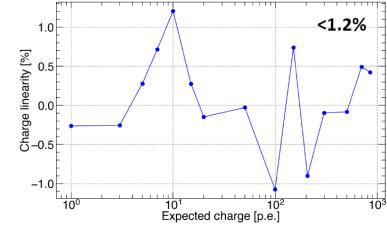

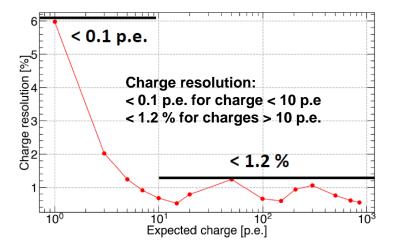

| Excellent charge reconstruction                                                                       | High linearity (~ 1%)<br>and resolution (~ 1%)<br>- 0.1 p.e. for < 10 p.e.<br>- < 1% for >10 p.e.            |  |

| Electronics time resolution < PMT time resolution (1.3 ns)                                            | Timing resolution (e.g. < 0.3 ns)<br><b>300 ps</b> for <b>1 p.e.</b><br><b>200 ps</b> for <b>&gt; 6 p.e.</b> |  |

| Low power consumption                                                                                 | 50 mW/ PMT channel                                                                                           |  |

#### **HKROC** architecture

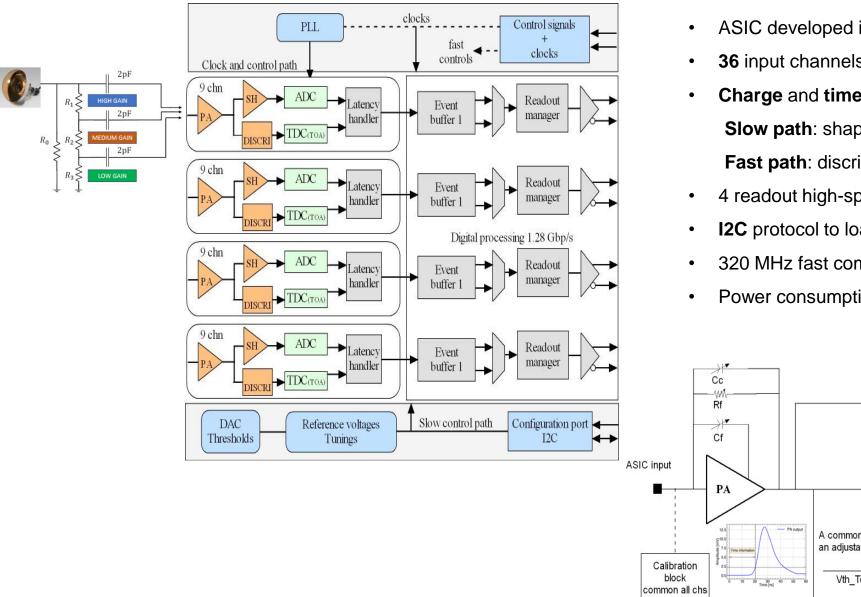

- ASIC developed in **130 nm CMOS** technology (1.2 Volts)

- **36** input channels  $\rightarrow$  **12** PMT channels

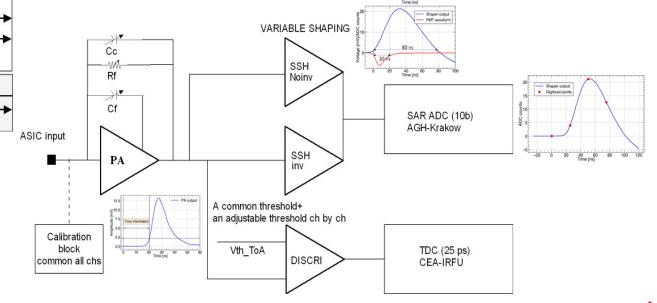

- Charge and time measurements: Slow path: shaper+10b SAR-ADC @ 40MHz, **Fast path**: discriminator + 10b TDC (LSB= 25 ps)

- 4 readout high-speed links (1.28 Gbps)  $\rightarrow$  1 read-out  $\rightarrow$  3 PMTs

- **I2C** protocol to load ASIC parameters

- 320 MHz fast commands

- Power consumption 10 mW / channel

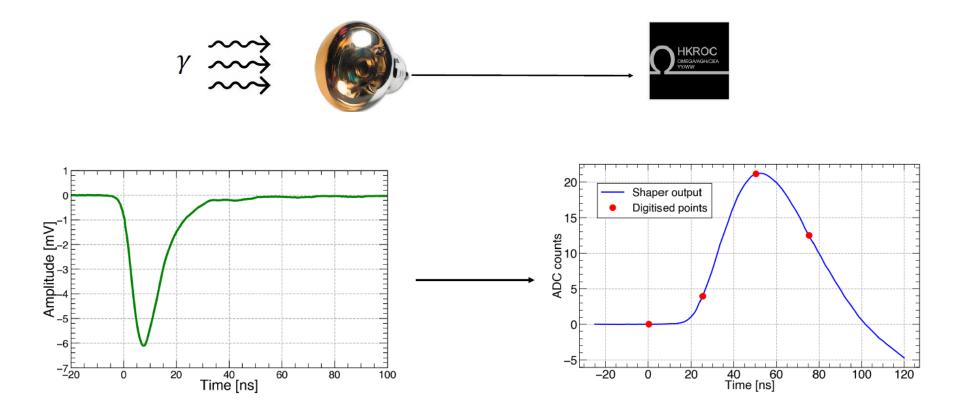

#### **HKROC** waveform digitizer

- The shaper signal digitized at 40 MHz by a 10 bits SAR (Successive Approximation) ADC (AGH-Krakow group) (boi 10.1088/1748-0221/18/11/P11013)

- For each trigger: a coarse time-stamp (24 bits) common for all channels (at 40 MHz) and a fine timestamp for each channel using a 10 bits TDC (LSB=25ps) (*CEA group*) (*DOI*: 10.1109/TNS.2023.3335657)

- The ASIC is a Waveform digitizer: when one trigger happens (ToA≠0) N sampling points separated by 25ns are captured and saved in the internal memory. N is variable by slow control (from 1 to 7)

**MEGA**

#### TWEPP 2024 30/09-4/10 2024

## crosstalk that affected the charge measurements.

HKROC1B, produced in 2022, was designed to reduce the crosstalk observed in HKROC0. It demonstrated good overall performance, with a significant reduction in crosstalk (see next slides).

HKROCO, produced in 2020 (to see TWEPP 2022), showed good performance that fitted well with the Hyper-K requirements, except for an extra

- HKROC1C was produced in 2023 and received a few months ago. It is currently under test

- ✓ Diffuse crosstalk is being tested

- ✓ Global test are ongoing

**HKROC** measurements

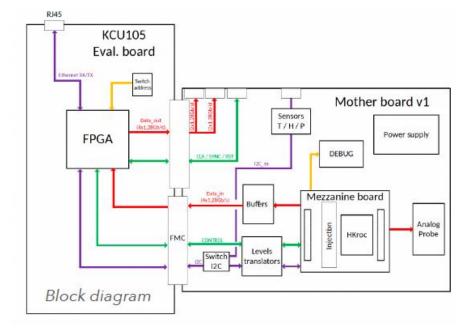

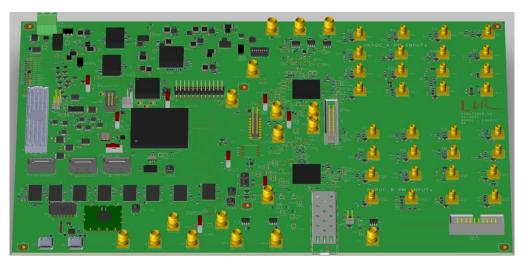

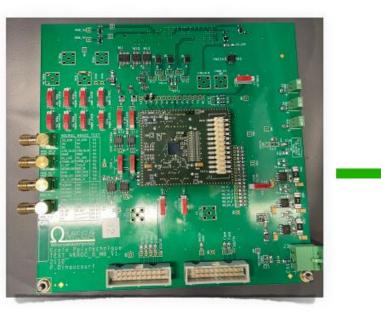

First board with mezzanine

6

#### **HKROC1B** general performances

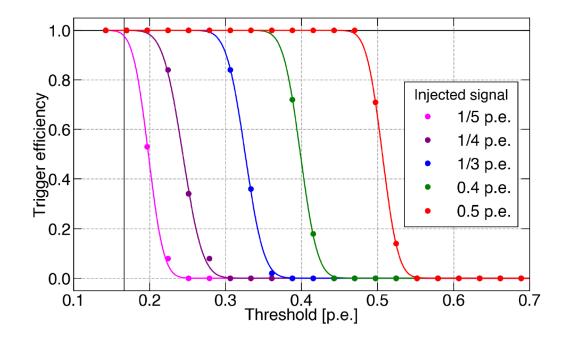

saturation because of generator jitter

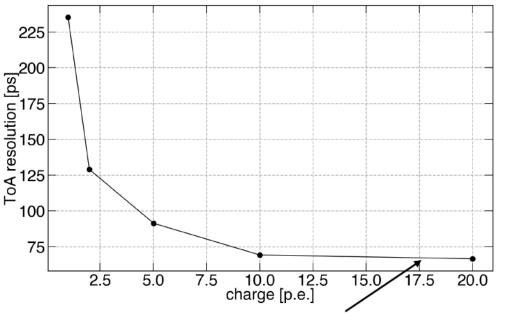

**Trigger threshold** = 1/6 p.e. > 90% efficiency for signal as low as 1/5 p.e. **Noise** amplitude < 1/22 p.e. **TDC characterization** with 1/6 p.e. threshold

**TDC resolution**:

225 ps std @ 1 p.e

60 ps std @ >10 p.e (intrinsic resolution 25 ps)

MEGA

#### **Charge reconstruction**

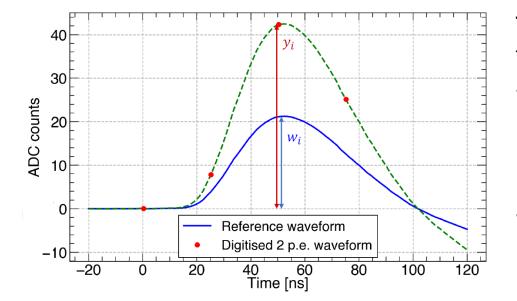

The digitized charge must be reconstructed offline in the FPGA.

The charge reconstruction method consists of two steps:

- Build a **reference waveform** to calibrate each channel:

- → High gain channel : 1. p.e.

- → Medium gain channel : 20 p.e.

- → Low gain channel : 200 p.e. 2.

- Given a digitized waveform, find the associated charge :

$\chi^{2}(\alpha) = \sum_{1}^{N} \left(\frac{\gamma i - \alpha w i}{\sigma i}\right)^{2} \qquad \frac{d\chi^{2}}{d\alpha} = 0 \iff \alpha = \frac{\sum_{1}^{N} \frac{\gamma i w i}{\sigma i^{2}}}{\sum_{1}^{N} \frac{w i^{2}}{\sigma i^{2}}} \Longrightarrow q = \alpha q_{ref}$

#### Pile-up et dead time

- The HKROC saturation naturally appears when the chip internal memory is full. The chip has one independent memory for each read-out link at 1.28 Gb/s

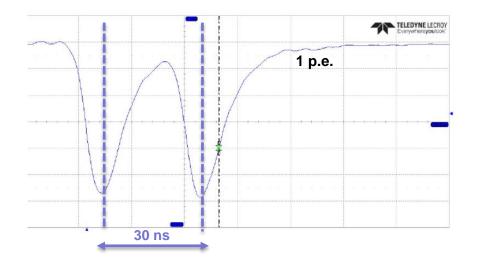

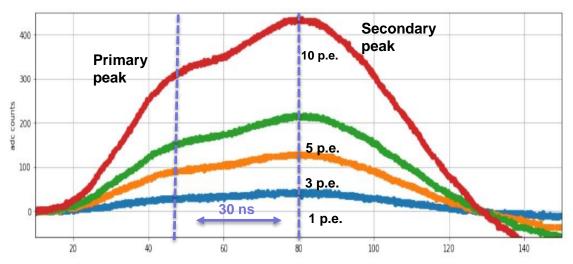

- ASIC hit rate: ~400 kHz/PMT, up to 1 MHz/channel, but we have tested the ASIC with pile-up events at a 30 ns delay time.

The HKROC feature to be a waveform digitizer and the charge reconstruction method allow the differentiation of events at extremely high frequencies

Events with separate timestamps >  $30 \text{ ns} \rightarrow 2$  trigger times Dead time **30 ns**

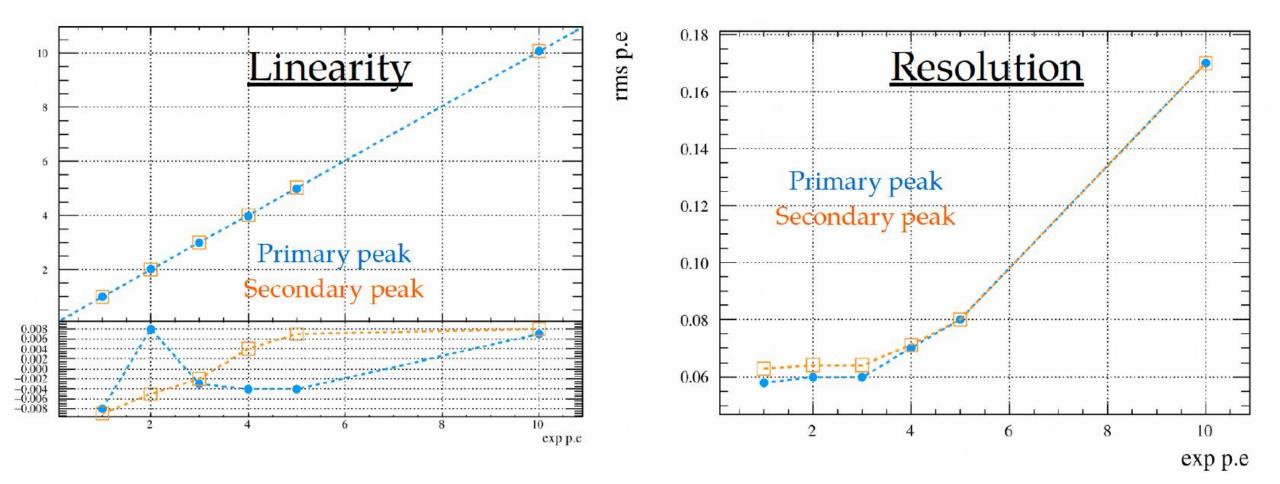

Accurate charge reconstruction of pile-up:

- → Charge linearity ~ 1%

- → Charge resolution:

- < 0.1 p.e. for charges < 5 p.e.

- < 0.17 p.e. @ 10 p.e.

#### **HKROC crosstalk – Diffuse crosstalk**

MEGA

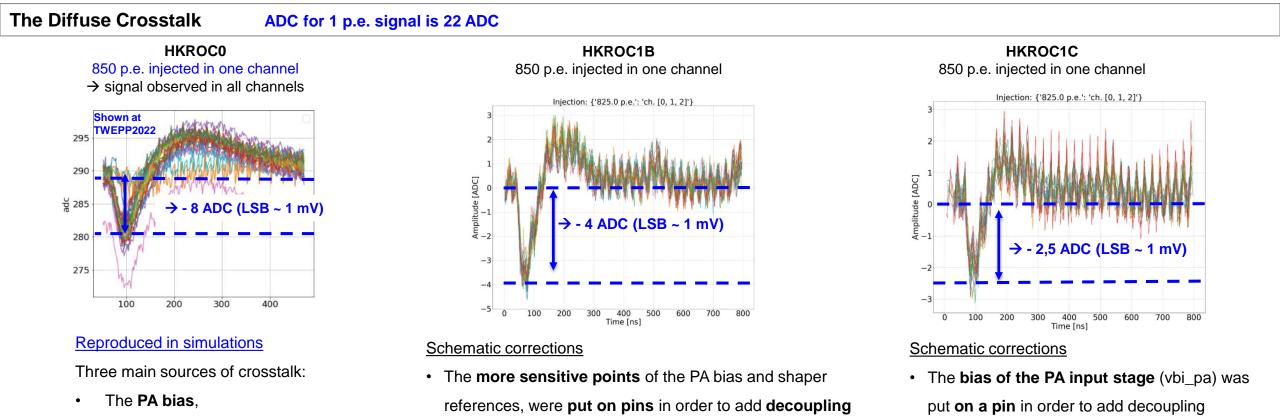

Two crosstalk observed already in the first prototype HKROC0:

- One defined "Diffuse crosstalk" → A negative crosstalk observed in all the channels

- The second one defined "Close crosstalk" → A positive signal was observed in the close channels

- The shaper references

- The input calibration block

A new input calibration block structure was implemented

capacitances on the board.

capacitances on the board.

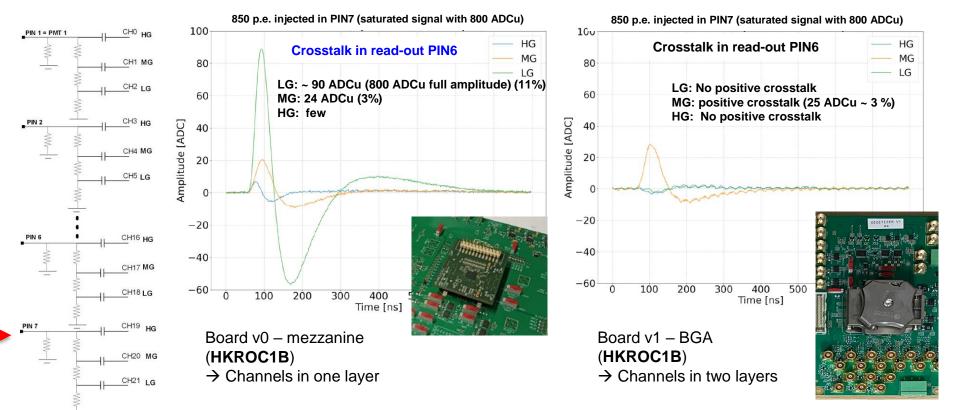

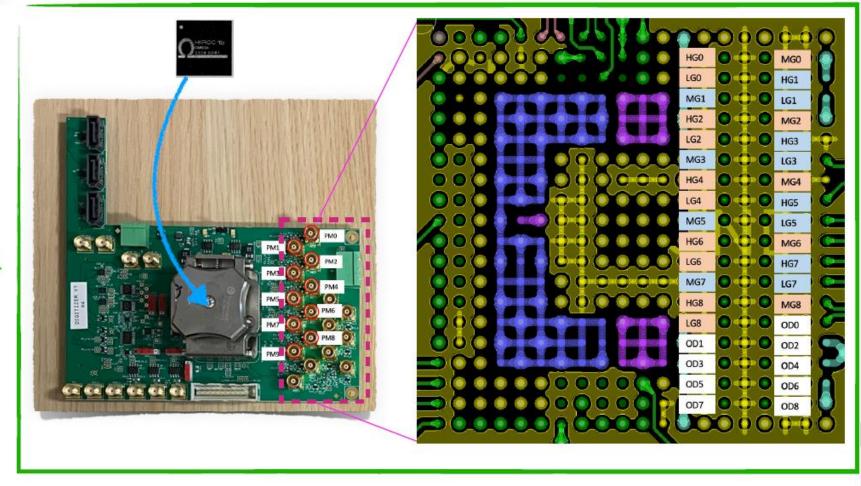

#### **Close crosstalk**

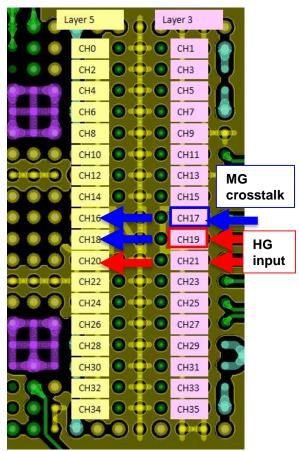

A large signal of 850 p.e. is injected into one pin (PIN7), affecting three ASIC channels, and an additional positive signal is observed only on the adjacent PIN6. This crosstalk was not reproduced in simulations, suggesting that it originates externally to the ASIC (in the BGA substrate and test board).

- A BGA substrate was designed with additional layers to separate the input into EVEN and ODD channels

- A new board for BGA packaging was also designed with two layers, dedicated to EVEN and ODD channels.

MEGA

#### **Conclusions and prospects**

- The HKROC1B, designed to reduce crosstalk, has demonstrated good overall performance, fitting the requirements of neutrino experiments. It has reduced 'diffuse crosstalk' by a factor of 2.

- The HKROC1C, further optimized to reduce 'diffuse crosstalk,' has shown a reduction by a factor of 1.6 compared to HKROC1B and 3.2 compared to HKROC0. Crosstalk is now at the noise level, with only 2 mV remaining.

- The new test board, designed to separate the channels into two layers, has completely eliminated 'close crosstalk' in the HG and LG channels and significantly reduced it in the MG channel.

- An **HKROC-based acquisition board** (21 x 29 cm) is currently in production. It includes two HKROCs and an FPGA for DAQ and charge reconstruction. This board is specifically designed **to further minimize 'close crosstalk**' and will be tested by the end of this year

Although it was designed for the Hyper-Kamiokande experiment, it will not be used for this detector. However, its **unique performance and flexibility** could make it useful for various experiments

• Backup

#### **Diffuse crosstalk**

#### For HKROC1C (2022 version):

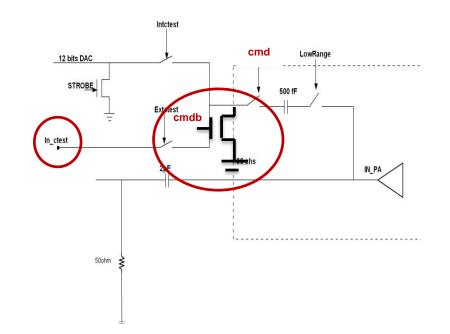

The "diffuse crosstalk" was observed in measurements, verified through simulations, and understood.

Three main sources of crosstalk were identified:

- PA bias  $\rightarrow$  Cdecoupling + pins

- Shaper references  $\rightarrow$  Cdecoupling + pins

- Ctest  $\rightarrow$  New input calibration block structure

For **HKROC1C** (2023 version):

An additional PA bias was better decoupled in the layout and on the external board.

#### **HKROC operating modes**

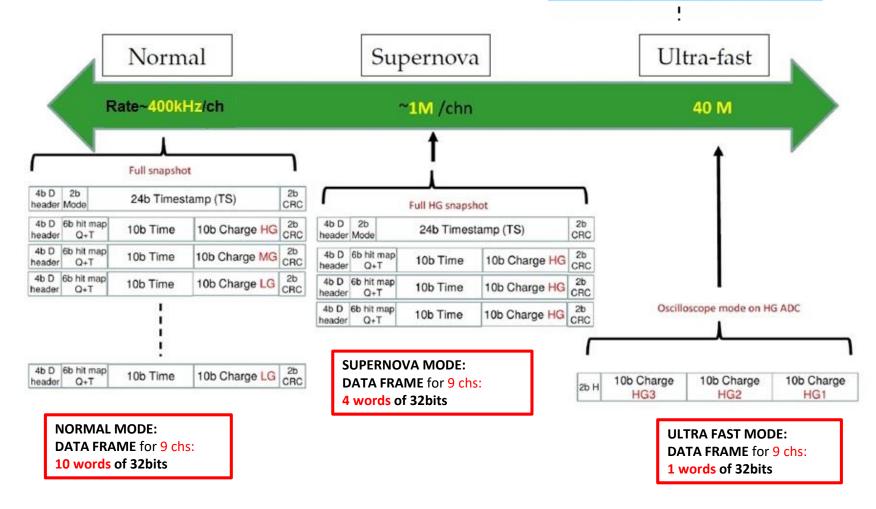

- → *Normal mode*: 10 words of 32 bits.

- → Supernova mode (focus on HG only, i.e. low energy): 4 words of 32 bits.

- → Ultra-fast mode (characterization mode): 1 word of 32 bits.

| 4b D<br>header | 2b<br>Mode 24b Timestamp (TS) |          |                            | 2b<br>CRC |

|----------------|-------------------------------|----------|----------------------------|-----------|

| 4b D<br>header | 6b hit map<br>Q+T             | 10b Time | 10b Charge HG              | 2b<br>CRC |

| 4b D<br>header | 6b hit map<br>Q+T             | 10b Time | 10b Charge <mark>MG</mark> | 2b<br>CRC |

| 4b D<br>header | 6b hit map<br>Q+T             | 10b Time | 10b Charge <mark>LG</mark> | 2b<br>CRC |

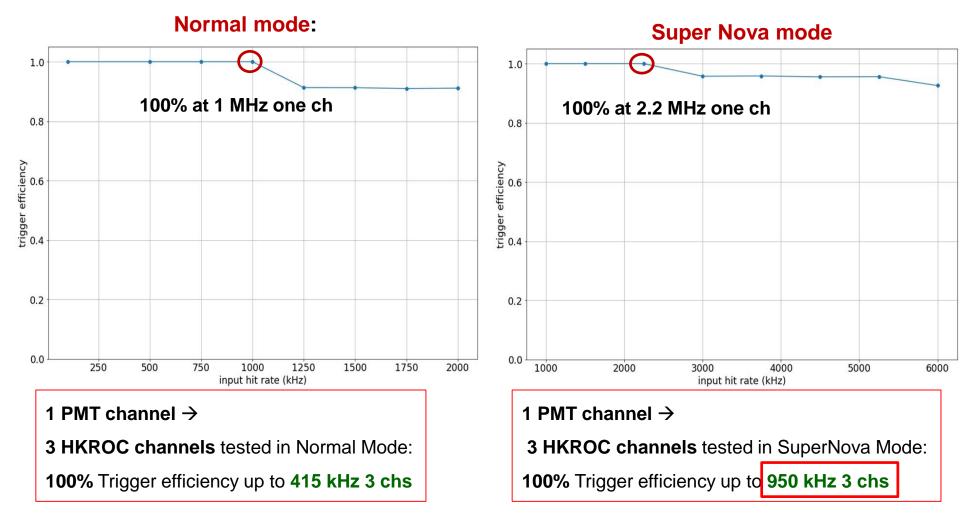

#### **HKROC Trigger rate measurements**

FAST hit rate (~ 1MHz) required for close Supernova signals (~ 1 p.e.)

The HKROC saturation naturally appears when the chip internal memory is full. The chip has one independent memory for each read-out link at 1.28 Gb/s, which gather 3 PMTs.

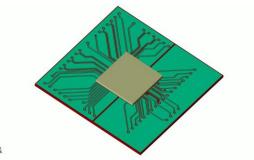

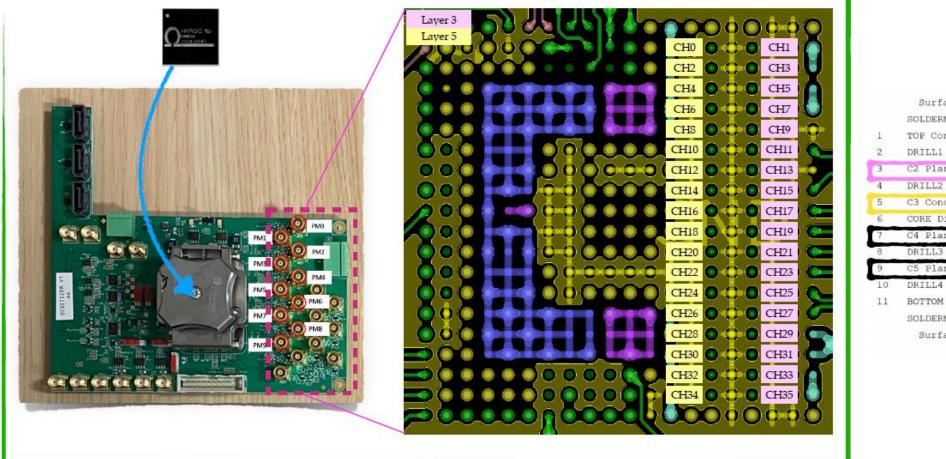

### From single-layer to multi-layer front-end board

Mezzanine daughter board on mother board

BGA on mother board

## From single-layer to multi-layer front-end board

| 1  | Surface<br>SOLDERMASK_TOP Mask 15 um<br>TOP Conductor 15 um       | A      |  |

|----|-------------------------------------------------------------------|--------|--|

| 2  | DRILL1 Dielectric 30 um                                           |        |  |

| 3  | C2 Plane 15 um                                                    |        |  |

| 4  | DRILL2 Dielectric 30 um                                           |        |  |

| 5  | C3 Conductor 12 um                                                | c      |  |

| 6  | CORE Dielectric 200 um                                            | →<br>→ |  |

| 7  | C4 Plane 12 um                                                    | 4      |  |

| 8  | DRILL3 Dielectric 30 um                                           |        |  |

| 9  | C5 Plane 15 um                                                    |        |  |

| 10 | DRILL4 Dielectric 30 um                                           |        |  |

| 11 | BOTTOM Conductor 15 um<br>SOLDERMASK_BOTTOM Mask 15 um<br>Surface | ↓<br>↓ |  |

BGA on mother board