# SOCRATES A Radiation-Tolerant SoC Generator Framework

Marco Andorno (marco.andorno@cern.ch)

On behalf of the CERN EP R&D WP5.3 team: Marco Andorno, Alessandro Caratelli, Davide Ceresa, Benoit Denkinger, Kostas Kloukinas, Anvesh Nookala 2024/10/01 – TWEPP 2024

| Ģ | Introduction          | Motivations<br>R&D context                                                             |

|---|-----------------------|----------------------------------------------------------------------------------------|

|   | The SOCRATES platform | SoCMake build system<br>Radiation-tolerance add-ons                                    |

|   | The TriglaV prototype | Architecture<br>Fault-tolerance and observability<br>Current status and future testing |

|   | Final remarks         | Possible applications<br>Future outlook                                                |

### The problem:

Future LHC and detector upgrades require more complex ASICs

They require advanced technology nodes, that come with high development costs

### The solution we propose:

#### Programmability

Retarget an ASIC for different applications

Change the algorithm at runtime

#### HW/SW codesign

Unified build system

System bring-up from a common description

#### **IP** blocks library

Pre-verified building

Promote collaborative work in the community

Compatible with a standard bus protocol

### **Towards System-on-Chips**

Turning our custom ASICs into programmable SoCs will provide:

- C Quick prototyping

- Smaller number of more capable ASICs

- Faster design and verification turnaround time

- Cost effective development

Where are SoCs applicable for the HEP community?

Standalone rad-hard microcontrollers

- LHC beam monitoring

- Power management

- On-detector monitoring

Embedded controllers in front-end ASICs

- Pixel chip calibration

- Control and monitoring

- Back-end tasks on chip

Advanced on-chip data processing

- On-chip pre-processing

- Custom HW accelerators

... but a single architecture can't fit all these applications, so... SoC RAdiation Tolerant Eco-System

Comprehensive **toolkit** to generate highly-customizable systems that can be integrated in custom radiation-tolerant ASICs. Its main goals:

Automatic SoC assembly and SW stack

Library of rad-tol verified IP blocks

Fault-tolerance support

It's going to be open-sourced for HEP and the wider open-source HW community

Development within the CERN EP R&D WP5:

Marco Andorno, Alessandro Caratelli, Davide Ceresa, Benoit Denkinger, Kostas Kloukinas, Risto Pejasinovic, Anvesh Nookala

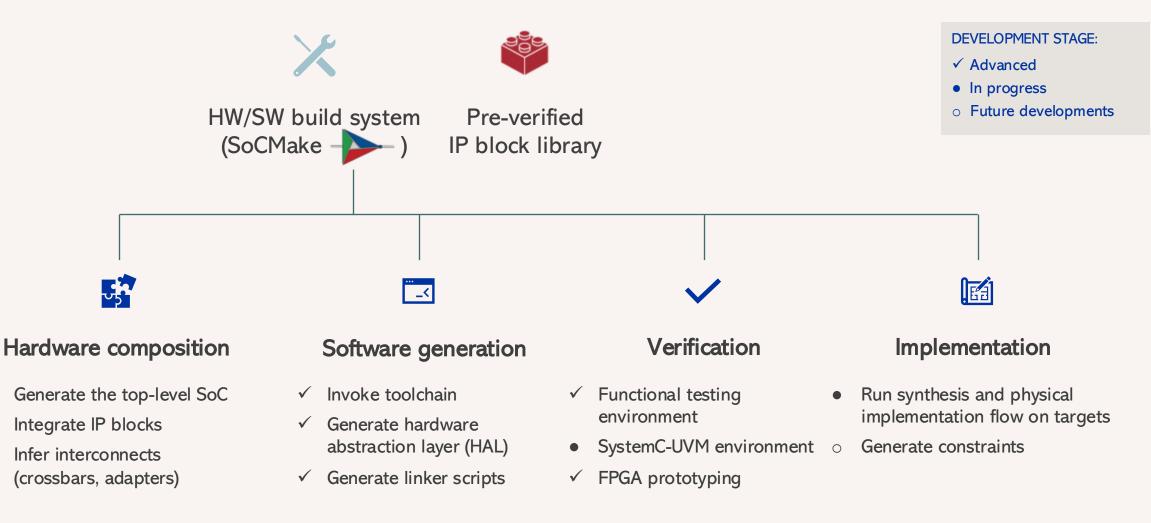

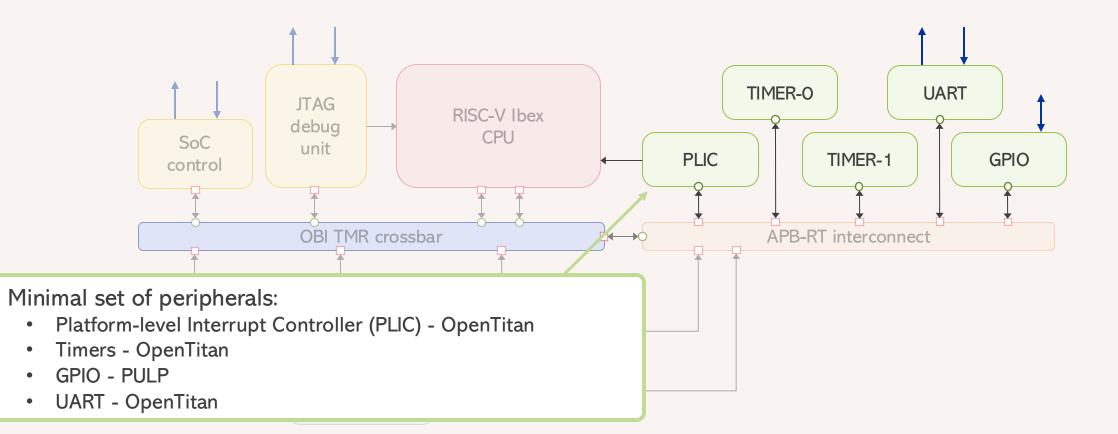

### The SOCRATES platform

$\checkmark$

$\checkmark$

$\checkmark$

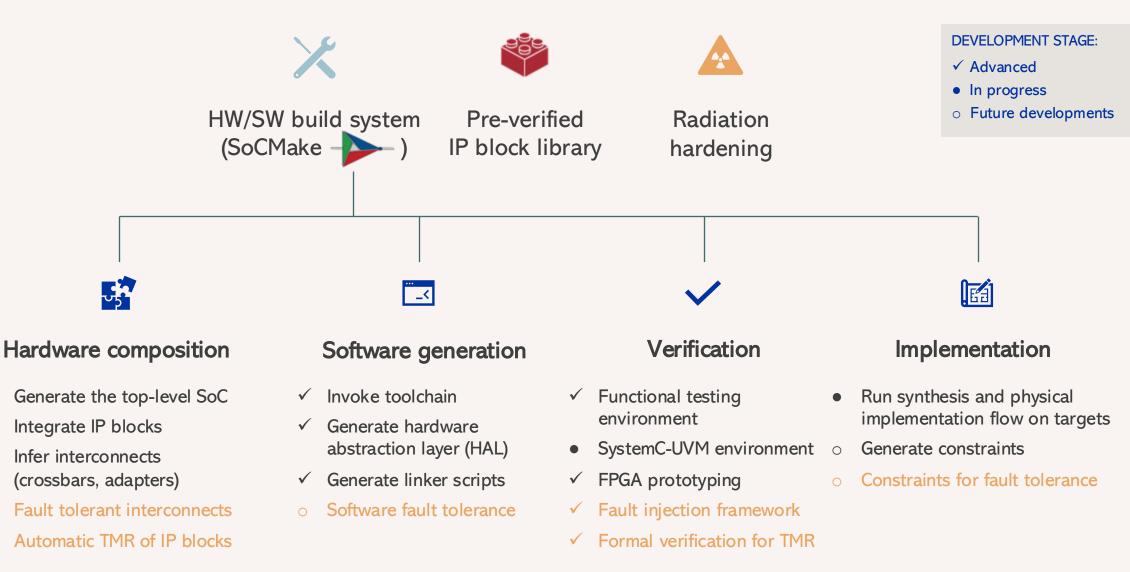

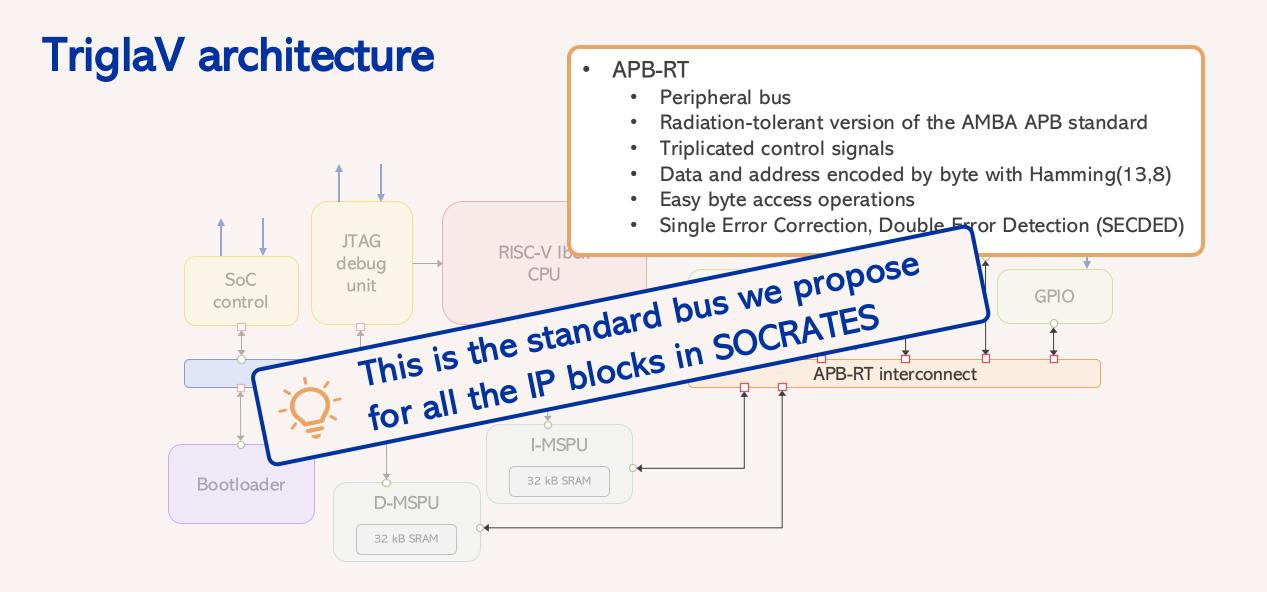

### ... and its rad-hardening add-ons

$\checkmark$

$\checkmark$

$\checkmark$

$\checkmark$

$\checkmark$

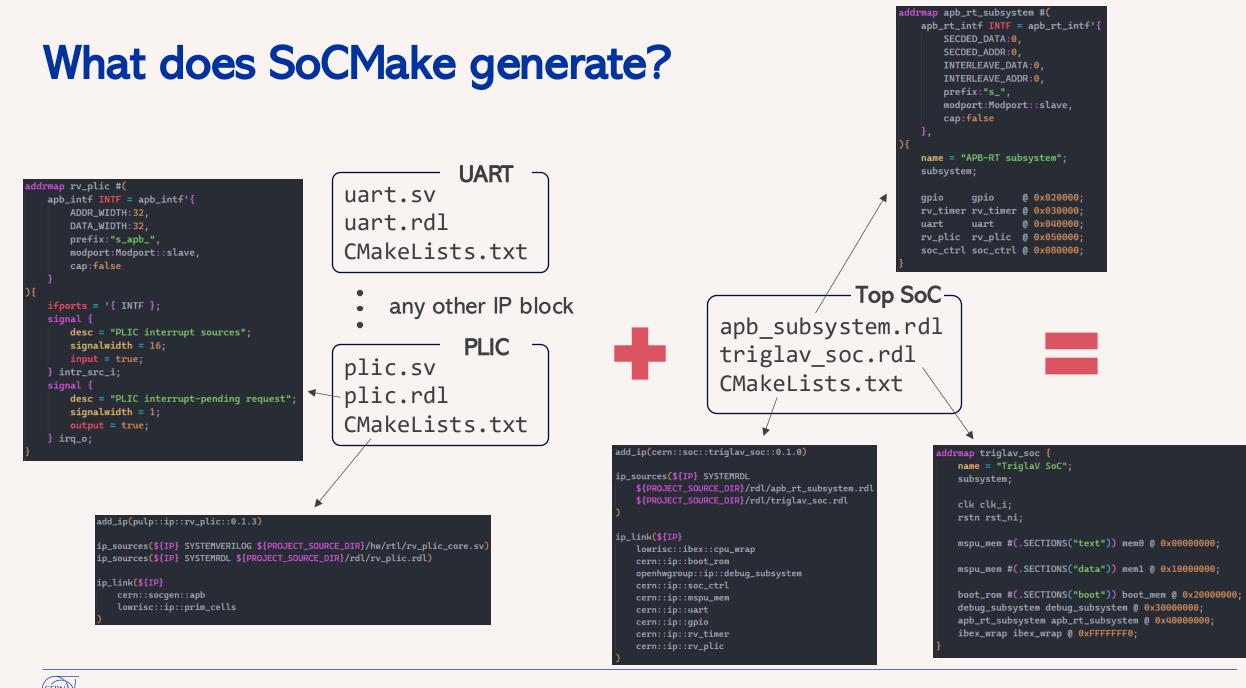

- CMake-based HW/SW build system generator for SoCs

- Supports SystemRDL as an input configuration

- Register Description Language

extended for supporting SoC description

- Used as top-level architecture description

- Rapid prototyping of SoCs:

- Quick composition of IP blocks into full systems

- Quickly build different architectures with different IP blocks, hardware accelerators or different CPUs

- Dependency management

- Open-source

- SoCMake: <u>github.com/HEP-SoC/SoCMake</u>

- Toolkit and implementation: gitlab.cern.ch/socrates

#### Goals:

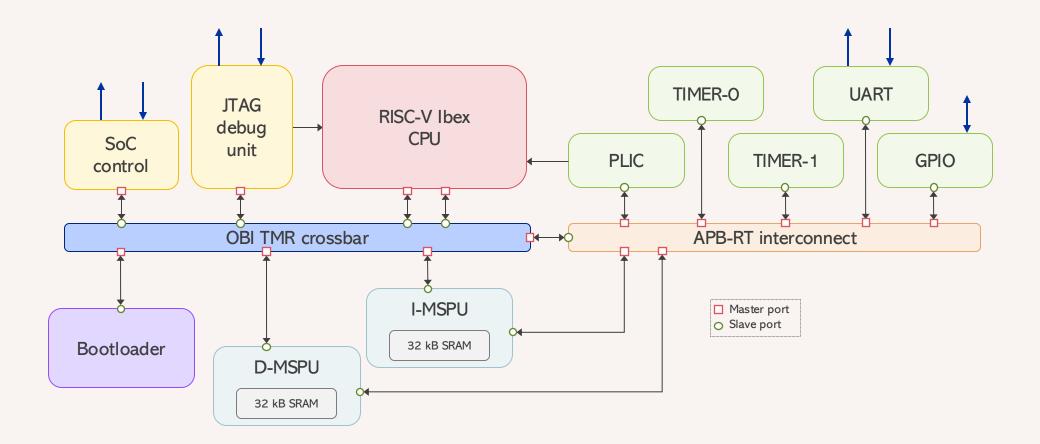

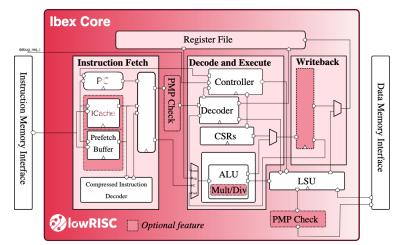

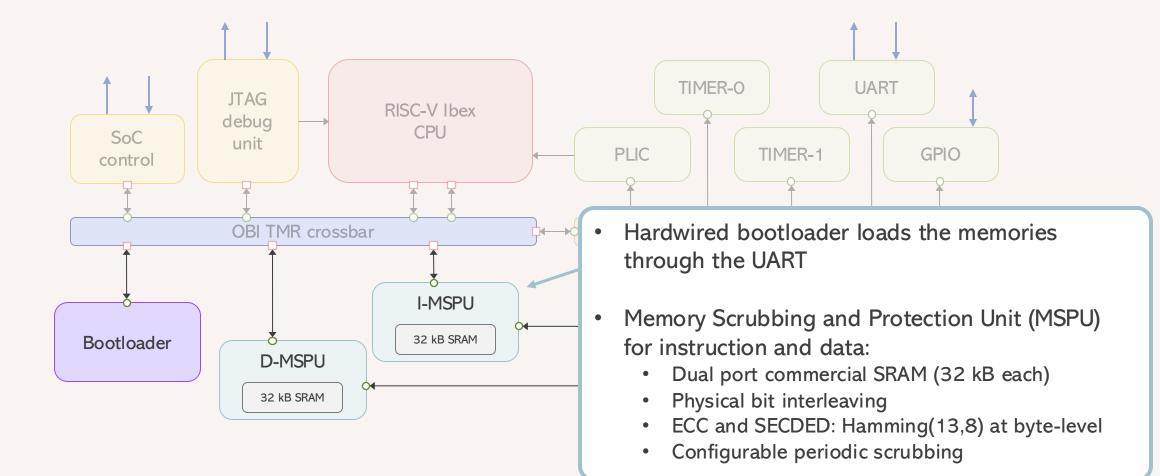

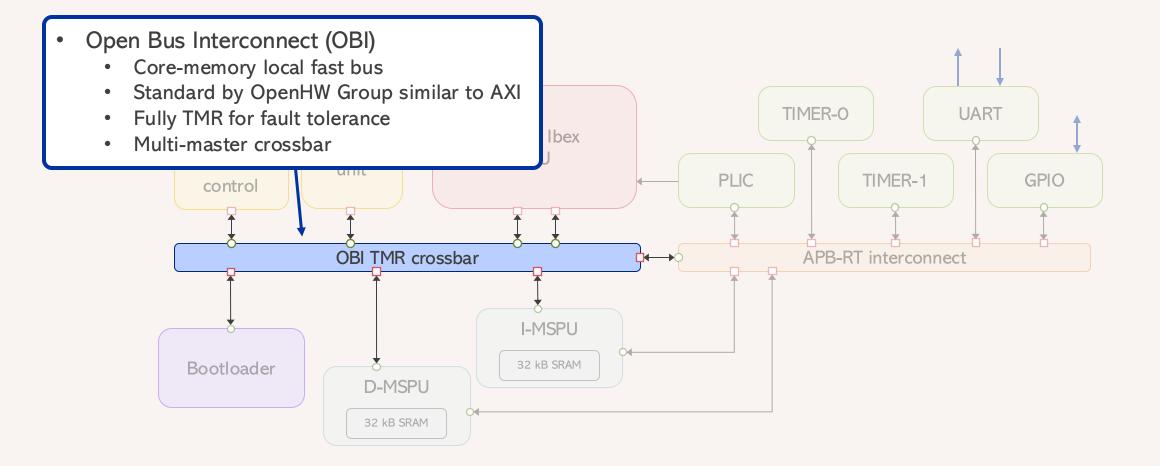

- Build a radiation-tolerant microcontroller-like SoC with the SOCRATES tools

- Validate the toolkit and demonstrate the feasibility of using programmable logic inside front-end ASICs

- Test-drive the HEP 28 nm Common Design Platform

- Test the radiation performance and gather experience on SoC design

#### Specifications:

- Fully generated out of the SOCRATES platform

- Suitable peripherals and architecture for a pixel readout ASIC embedded controller applications

- Radiation-tolerant design up to ~CMS IT levels, with testability features to trace faults under irradiation

- Implemented on 28 nm bulk CMOS technology

Prototype tapeout on MPW scheduled for November 27<sup>th</sup>

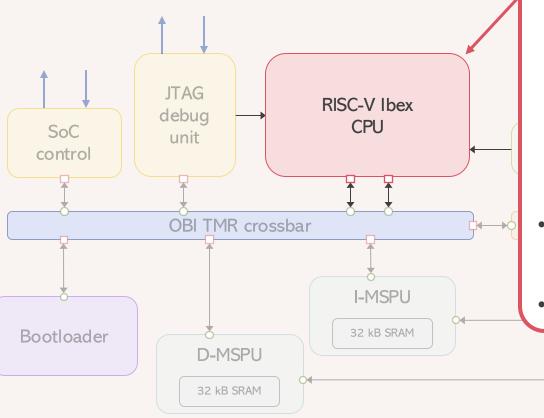

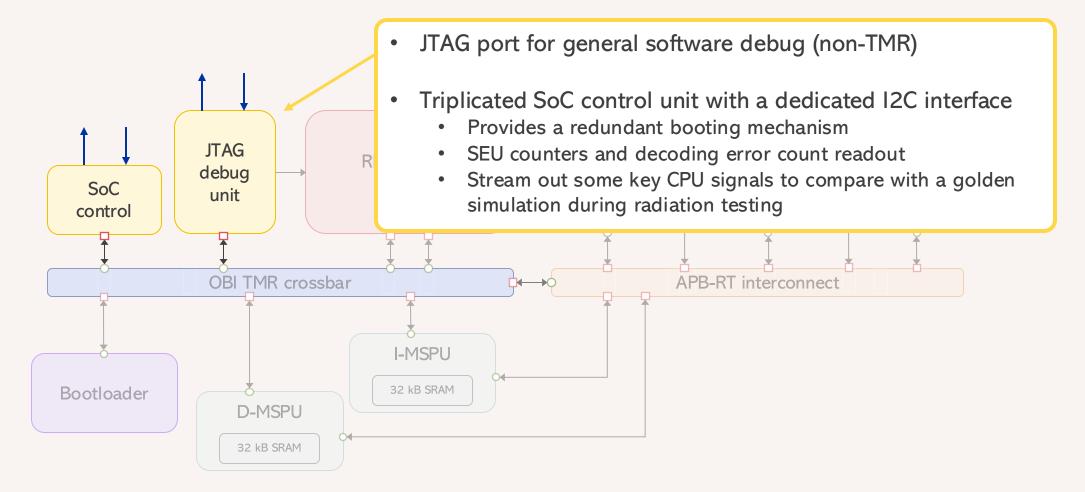

- Open-source high-TRL RISC-V core by IowRISC<sup>[1]</sup>

- RV32IMC ISA

- 2-stage pipeline

- Full TMR at FF level

- 4x area overhead for TMR, ~6x final area with SEU observability

- TMR formal verification<sup>[2]</sup> and fault injection<sup>[3]</sup>

[1] P. Davide Schiavone et al., Slow and steady wins the race? A comparison of ultra-low-power RISC-V69cores for Internet-of-Things applications, PATMOS (2017) pp. 1-8.70

- [2] A. Pulli, M. Lupi, A simulation methodology for verification of transient fault tolerance of ASICs designed for high-energy physics experiments, 2023 JINST 18 C01038

- [3] A. Nookala et al., Soft-error Reliability Analysis and Error Rate Estimation for RISC-V Processors in High Energy Physics Environments, NSREC (2024), draft for IEEE TNS 2025

CÉRN

CERN

CERN

٠

(CERN)

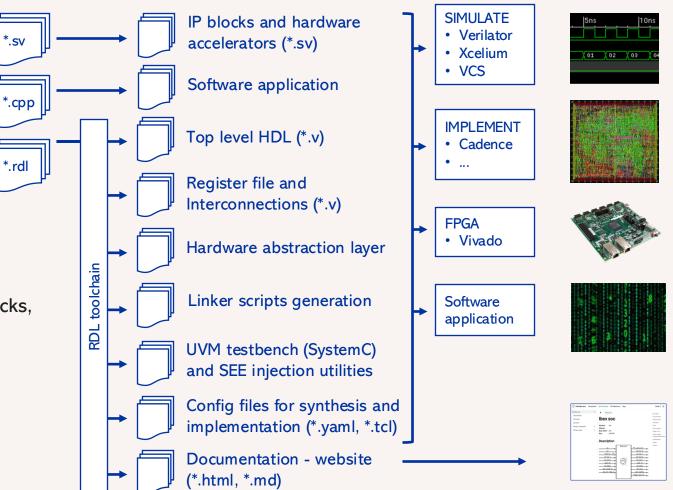

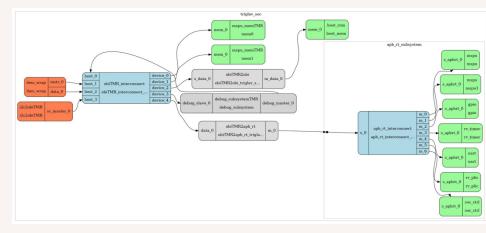

### What you get in output from the tools

odule triglav\_soc (

input wire [0:0] clk\_iA,

input wire [0:0] clk\_iB,

input wire [0:0] clk\_iC,

input wire [0:0] rst\_niA,

input wire [0:0] rst\_niC,

output wire [0:0] uart\_tx\_oA

output wire [0:0] uart\_tx\_oC

#### Top SoC Verilog

| module <b>rv_plic</b> | C   |    |           |

|-----------------------|-----|----|-----------|

| input wire            | [15 | 0] | intr_src_ |

| input wire            | [15 | 0] | intr_src_ |

| input wire            | [15 | 0] | intr_src_ |

| output wire           | [0] | 0] | irq_oA,   |

| output wire           | [0] | 0] | irq_oB,   |

| output wire           | [0] | 0] | irq_oC,   |

| output wire           | [3  | 0] | irq_id_oA |

| output wire           | [3  | 0] | irq_id_oB |

| output wire           | [3  | 0] | irq_id_oC |

| output wire           | [0] | 0] | msip_oA,  |

| output wire           | [0] | 0] | msip_oB,  |

| output wire           | [0] | 0] | msip_oC,  |

| input wire            | 0]  | 0] | clk_iA,   |

| input wire            | [0  | 0] | clk_iB,   |

| input wire            | [0  | 0] | clk_iC,   |

| input wire            | [0  | 0] | rst_niA,  |

| input wire            | [0  | 0] | rst_niB,  |

| input wire            | [0  | 0] | rst_niC,  |

|                       |     |    |           |

#### TMR peripherals

#### SECTIONS

/\* we want a fixed boot point \*/

PROVIDE(\_\_boot\_address = ORIGIN( boot\_mem ))

bootloader : {

\*bootloader.S.o\*(\*);

\*bootloader.cpp.o\*(\*)

. = ALIGN(4);

} > boot\_mem

/\* we want a fixed entry point \*/

PROVIDE(\_\_entry\_address = ORIGIN( mem0 ) + 0x180);

/\* stack and heap related settings \*/

\_\_stack\_size = DEFINED(\_\_stack\_size) ? \_\_stack\_size : 0x800;

PROVIDE(\_\_stack\_size = \_\_stack\_size);

\_\_heap\_size = DEFINED(\_\_heap\_size) ? \_\_heap\_size : 0x800;

#### Linker script

#include <stdint.h>

#include \_\_include/halcpp\_base.h"

#if defined(\_\_clang\_\_)

#pragma clang diagnostic ignored "-Wundefined-var-template"

#endif

namespace rv\_plic\_nm

#### /\* \* Interrupt Source 0 Priority

template <uint32\_t BASE, uint32\_t WIDTH, typename PARENT\_TYPE>

class PRI00 : public halcpp::RegRW<BASE, WIDTH, PARENT\_TYPE>

#### . oublic:

using TYPE = PRIO0<BASE, WIDTH, PARENT\_TYPE>;

static halcpp::FieldRW<0, 1, TYPE> val0;

using halcpp::RegRW<BASE, WIDTH, PARENT\_TYPE>::operator=;

#### Peripheral HAL

#### A nice block diagram

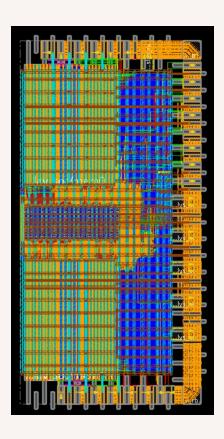

## TriglaV design status

- Physical implementation in progress

- Area: 1 mm x 2 mm

- ~300k instances

- Target operating frequency: 320 MHz

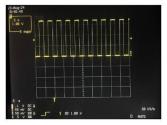

- FPGA emulation setup (credits to Georgios Nikolaidis)

- $\sim 10^3$  faster than simulation

- Increased confidence in the RTL to real HW

- Functional verification

- Random verification of peripherals

- Simulation of the top level

#### Hello world from Triglav in C++!

Messages from TriglaV printed in UART console

**GPIO** test Results

#### **Future outlook**

- 1. Tape out the TriglaV prototype and test its radiation performance to get a baseline

- 2. Evaluate alternative fault-tolerance solutions (e.g. selective triplication, core lockstepping) for better/multiple PPA/radiation resistance tradeoff

- 3. Polish the toolkit to make it more user friendly and open source it

- 4. Demonstrate the use of a similar SoC embedded in a pixel readout chip (e.g Picopix)

# Thank you!

home.cern