# **Development of ASIC for CoRDIA, a future camera for** pioneering x-ray sources.

H. Graafsma<sup>a,b,d</sup>, <u>A. Klujev<sup>a,b</sup></u>, H. Krueger<sup>c</sup>, S. Lange<sup>a,b</sup>, T. Laurus<sup>a,b</sup>, A. Marras<sup>a,b</sup>, D. Pennicard<sup>a,b</sup>, S. Spannagel<sup>a</sup>, U. Trunk<sup>a,b</sup>, T. Vanat<sup>a</sup>, C.B. Wunderer<sup>a,b</sup>

a) Deutsches Elektronen-Synchrotron (DESY), Hamburg, Germany b) Center for Free Electron Laser Science (CFEL), Hamburg, Germany

c) University of Bonn, Bonn, Germany d) Mid Sweden University, Sundsvall, Sweden

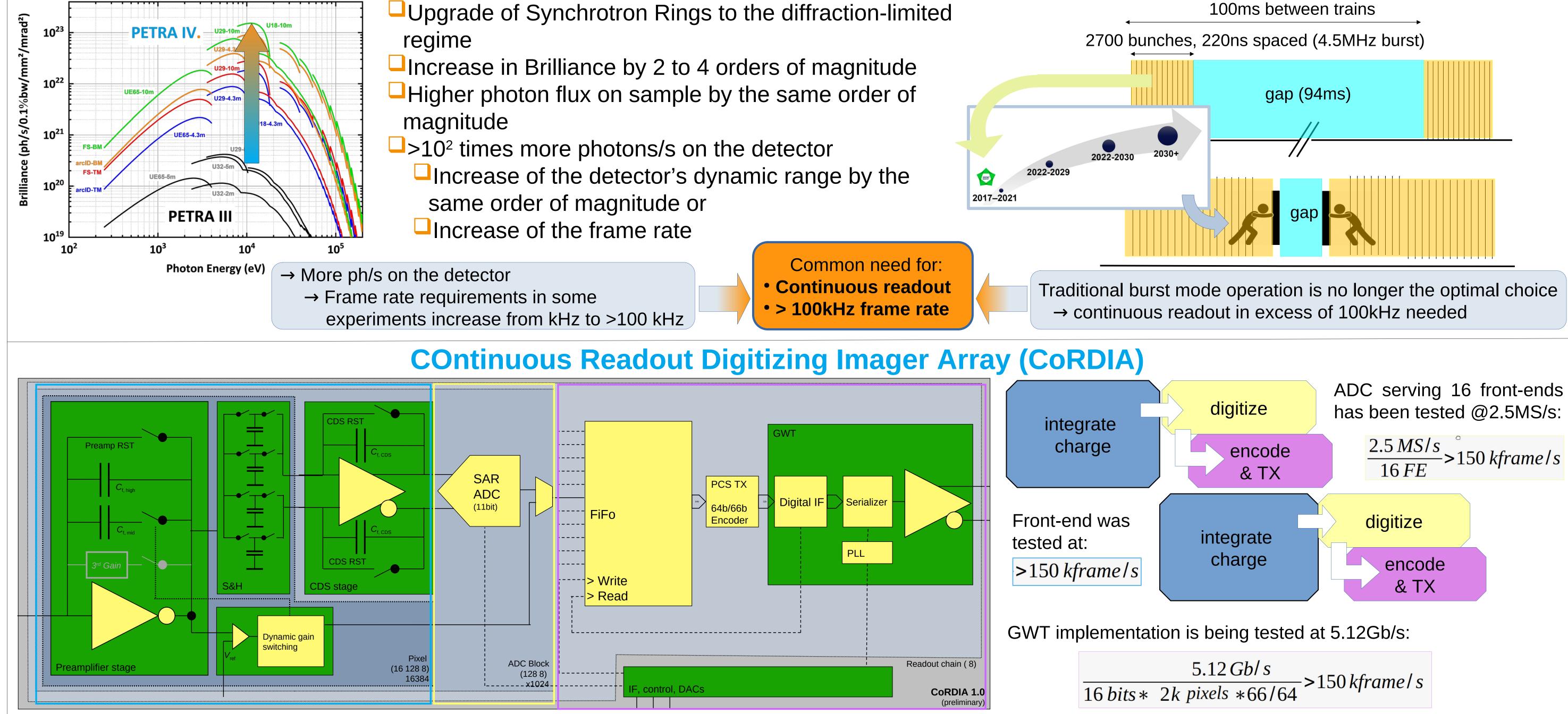

# **Detector Challenges from Next Generation Synchrotron Sources**

## **Example: PETRA III** $\rightarrow$ **PETRA IV upgrade at DESY**

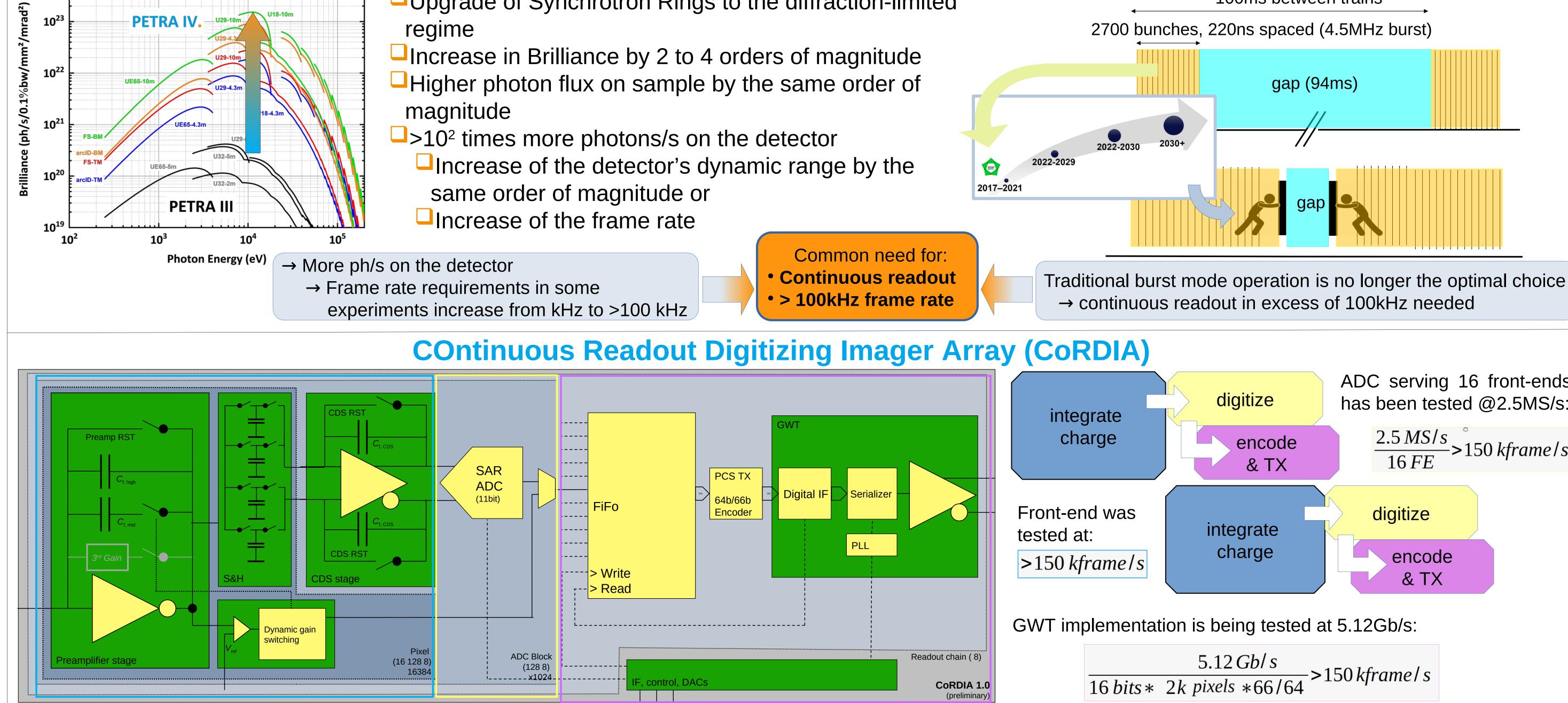

$\Box$ On-chip digitization @  $\geq$  10 ENOB

Dead-time free pipelined operation

Compatibility with high-Z sensors

Dynamic gain switching (à la AGIPD)

**Design Goals**

$\square$  Pixel size 110µm × 110µm  $\supseteq \ge 10k$  photon Dynamic Range  $\Box$  = 1.5 ×10<sup>9</sup> photons/pixel/s

### □Continuous Frame Rate $f_{FR} \approx 150$ kHz (≥100kHz) TSVs for gapless tile assembly □Single-photon sensitive (@ $\leq 12$ keV) **TSMC 65 nm (CERN design kit) technology**

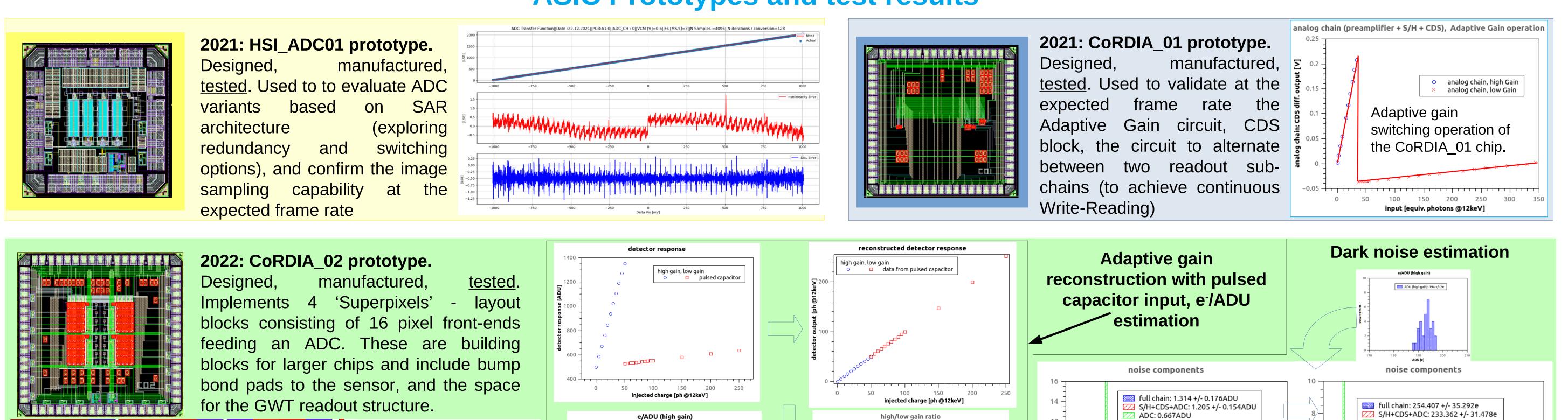

**ASIC Prototypes and test results**

Outlook

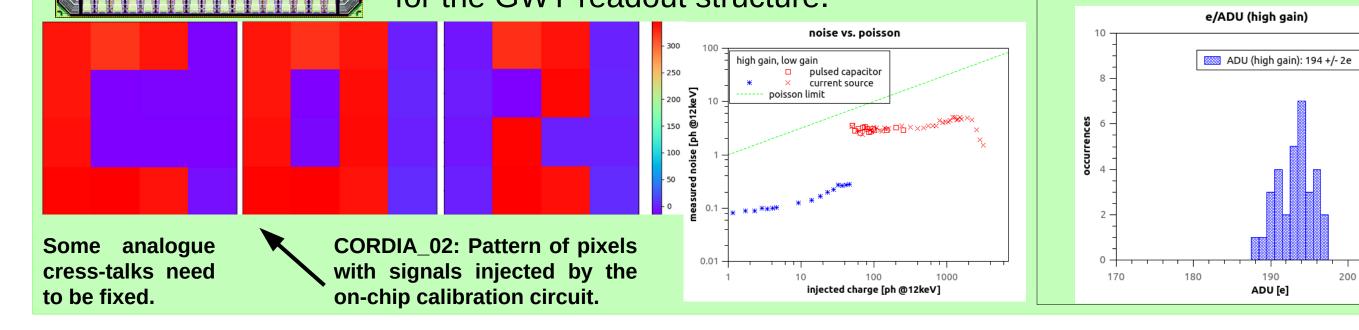

2023: CoRDIA\_03 prototype. Designed. Manufacturing IN

28

26

2.5

100

ADC: 0.667ADU

1.5

noise [ADU]

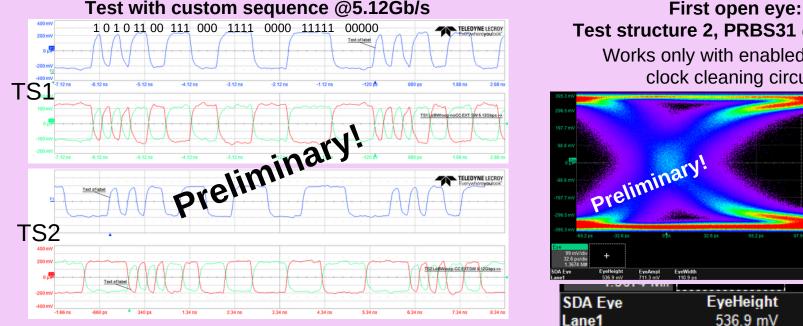

First open eye: Test structure 2, PRBS31 @5.12Gb/s Works only with enabled PLL & clock cleaning circuit

250

noise [e]

300

350

ADC: 129.121e

200

150

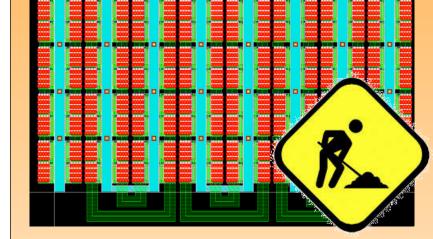

CoRDIA 0x prototype-to-come: smallsized ~2k pixel array. Design in progress. Floorplan as a meandering structure to emulate full-size chip size "column" (to estimate eventual drops before full-size chip engineering run).

CoRDIA 0y prototype-to-come: similar

possibly additional experimental circuits

to CoRDIA\_02 design with improved

like digital periphery and alternative

analogue "superpixel" layout and

200

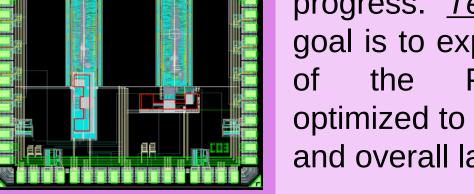

progress. <u>Test in progress!</u> The goal is to explore/validate variants the PCS+GWT circuits, optimized to the CoRDIA data flow TS2 and overall layout constraints.

high/low gain ratio

high/low gain ratio: 30.87 +/- 0.39

30

gain ratio

32

34

### Acknowledgments

The authors would like to acknowledge:

- The Caribou team for providing us with a versatile system for prototype testing

- NIKHEF (particularly V. Gromov and A. Vitkovskiy), for allowing us to include a version of the PCS-GWT circuit in our design for fast data streamout

12 -

0.5

- CERN and the RD53 collaboration, for allowing us the reuse of CMOS IO pads and SOFIC ESD structures in our design

- Europractice, IMEC and CERN for their MPW and design tool support

building blocks.