# 3D Integration of Pixel Readout Chips using Through-Silicon-Vias

#### **TWEPP-2024**

<u>F. Piernas</u><sup>1</sup>, J. Alozy<sup>1</sup>, S. Al-Tawil<sup>1</sup>, J. Buytaert<sup>1</sup>, M. Campbell<sup>1</sup>, T. Fritzsch<sup>2</sup>, K. Kloukinas<sup>1</sup>, M. Kovacs<sup>1</sup>, X. Llopart<sup>1</sup>, M. Barreto<sup>3</sup> and K. Wyllie<sup>1</sup>

<sup>1</sup>CERN <sup>2</sup>Fraunhofer IZM <sup>3</sup>UniGe

Supported by CERN EP R&D WP5 and the Medipix4 Collaboration

#### Outline

- 1. Through-Silicon-Via (TSV) Overview

- 2. Why TSV in Particle Detectors

- 3. TSV Processing of Timepix4

- 4. Module Design to Test TSV

- 5. First Results and Future Work

2. Why TSV in Particle Detectors

- 3. TSV Processing of Timepix4

- 4. Module Design to Test TSV

- 5. First Results and Future Work

4th October 2024

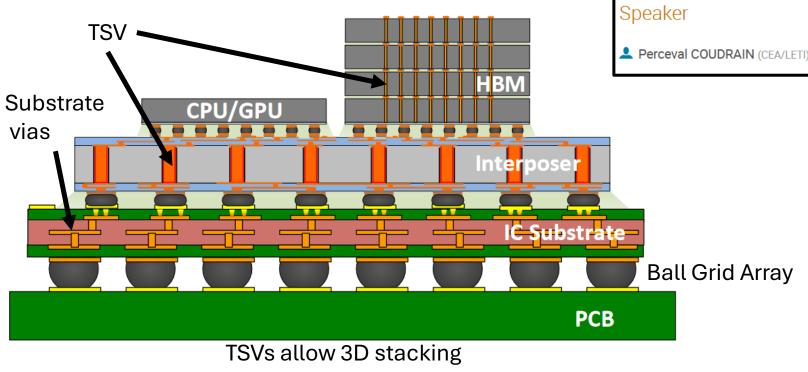

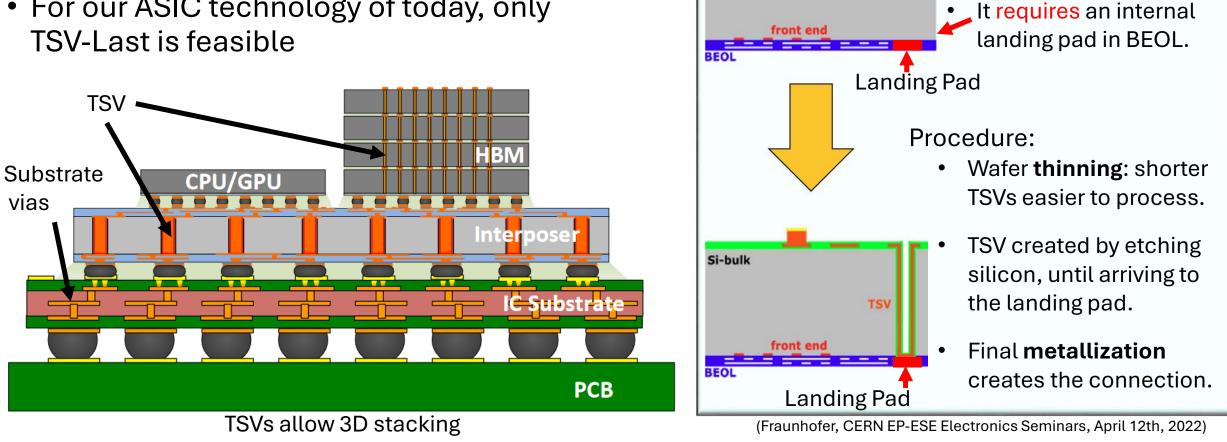

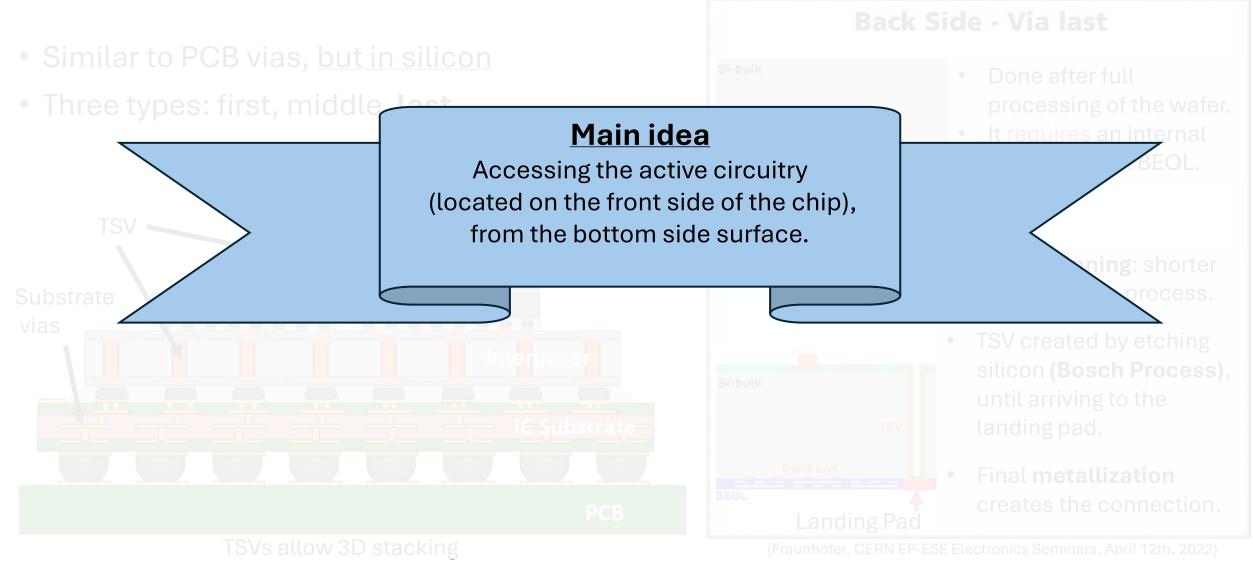

- Similar to PCB vias, but in silicon

- Three types: first, middle, last

- For our ASIC technology of today, only TSV-Last is feasible

- Similar to PCB vias, but in silicon

- Three types: first, middle, <u>last</u>

- For our ASIC technology of today, only TSV-Last is feasible

Si-bulk

**Back Side - Via last**

Done after full

processing of the wafer.

4th October 2024

francisco.piernas.diaz@cern.ch | TWEPP 2024

# 2. Why TSV in Particle Detectors

- 4. Module Design to Test TSV

- 5. First Results and Future Work

### 2. Why TSV in Particle Detectors

- Access to all the back-side area

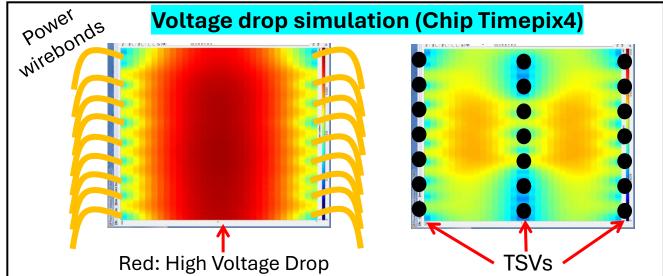

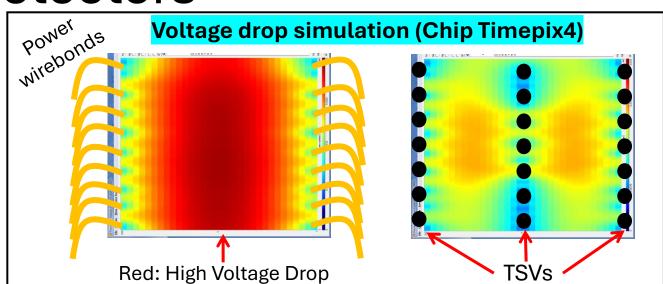

- Better power distribution

- Better signal integrity(\*)

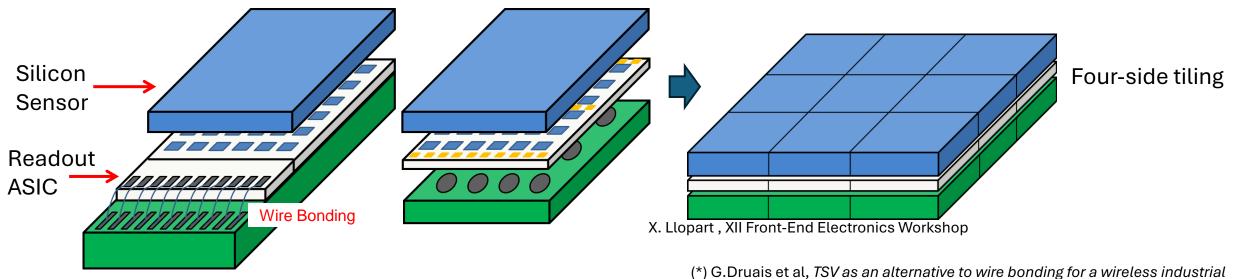

- 4-Side buttability: minimal dead space

(\*) G.Druais et al, TSV as an alternative to wire bonding for a wireless industrial product: another step towards 3D integration

### 2. Why TSV in Particle Detectors

- Access to all the back-side area

- Better power distribution

- Better signal integrity(\*)

- 4-Side buttability: minimal dead space

product: another step towards 3D integration

francisco.piernas.diaz@cern.ch | TWEPP 2024

2. Why TSV in Particle Detectors

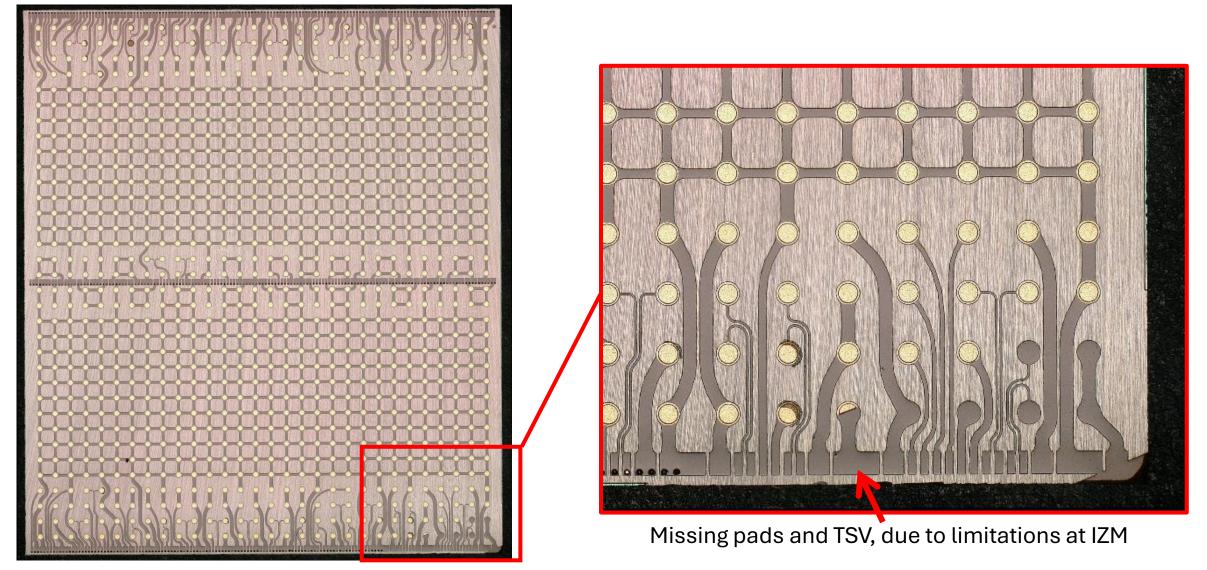

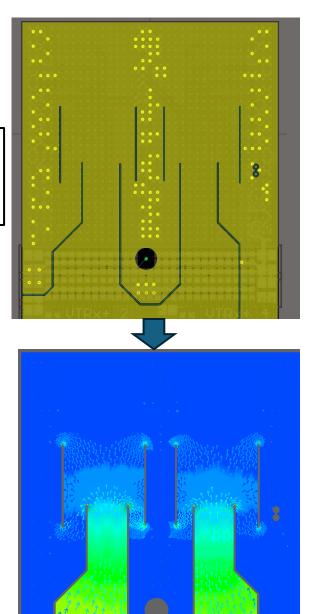

# 3. TSV Processing of Timepix4

4. Module Design to Test TSV

5. First Results and Future Work

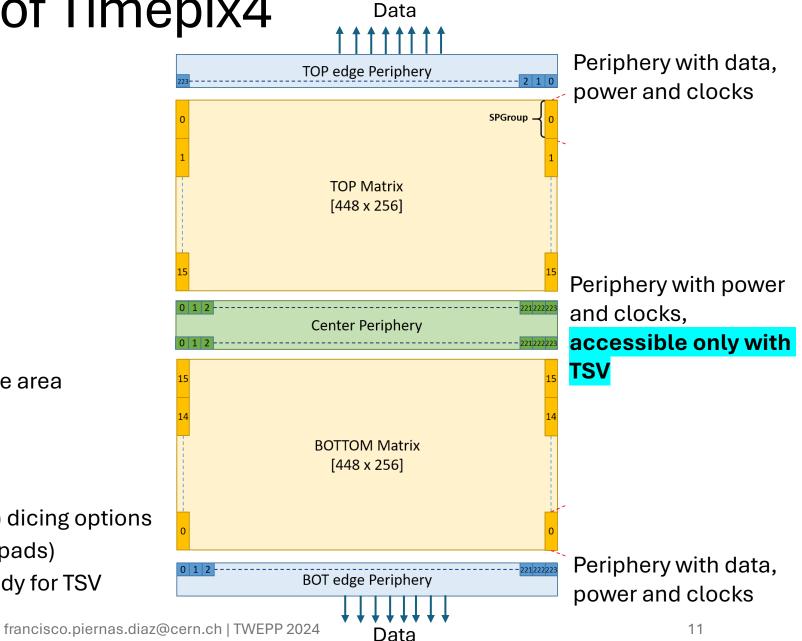

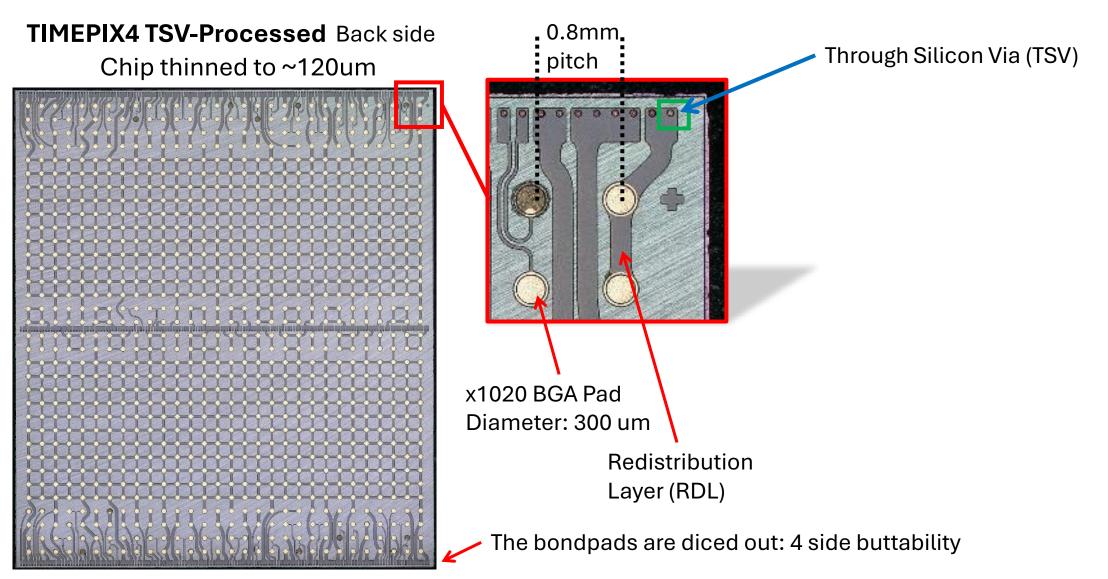

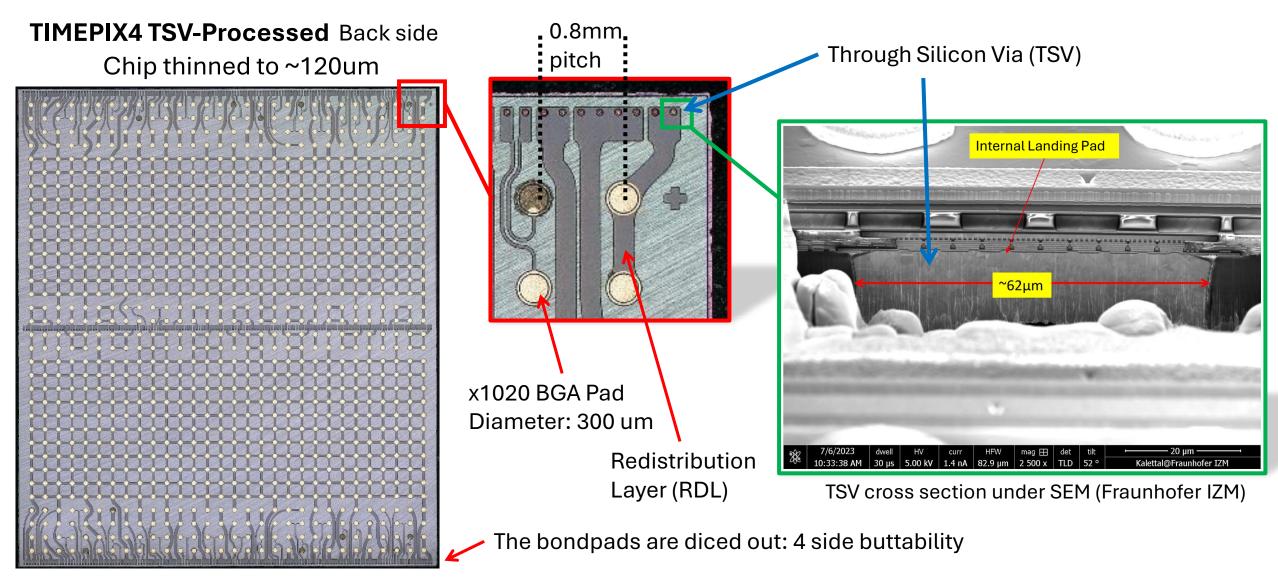

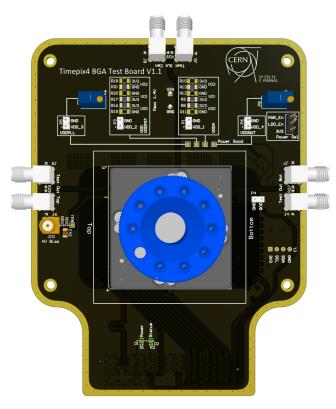

#### Timepix4: Our test-vehicle for TSV

#### Timepix4: Hybrid pixel detector

- 29x24mm = almost 7cm^2 sensitive area

- 512x448 pixels

- 16 links up to 5Gbps

#### Why Timepix4 as test vehicle?

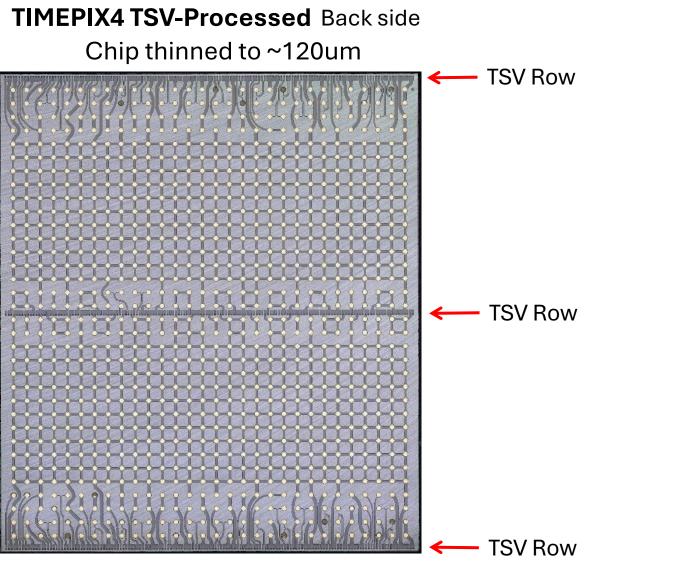

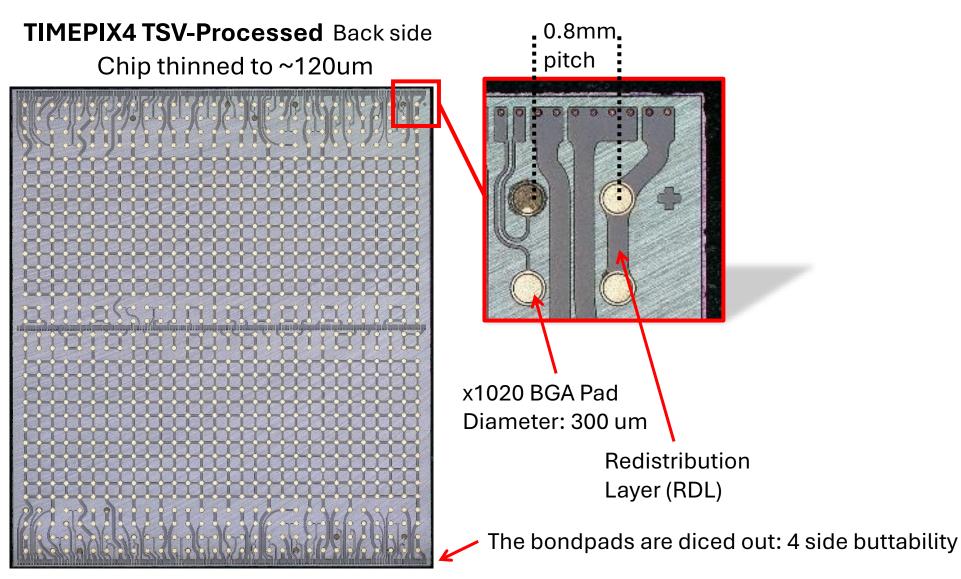

- Wirebond and Ball Grid Array (BGA) dicing options

- Four-side buttability (without bondpads)

- Internal landing pads in Metal 1 ready for TSV

| Timepix4 Version                | V0                                                                                                   | V1                                                                         | V2 / V3                                                                               |

|---------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Considerations                  | Excessive jitter in data<br>links, due to PLL not<br>locking properly.<br>Chip for electrical tests. | Same problems on data<br>links as V0.<br><b>Chip for electrical tests.</b> | Versions with<br>PLL problem solved.<br>Links working at 5Gbps at<br>nominal voltage. |

| ZM Fraunhofer<br>SV Processing: | Two wafers 200mm<br>done                                                                             | Two wafers 200mm<br>done                                                   | Three V3 wafers 200mm<br>Ongoing TSV processing                                       |

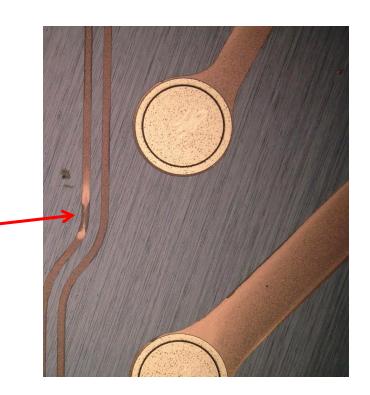

Some difficulties:

- Setup by trial and error: some wafers are consumed for setup

- Wafer level processing

- Post processing for balling

- Defects in RDL or pixel matrix (not common)

- Visual inspection and good handling is important

Damaged track

Metal deposition over defects

- 1. Through-Silicon-Via (TSV) Overview

- 2. Why TSV in Particle Detectors

- 3. TSV Processing of Timepix4

5. First Results and Future Work

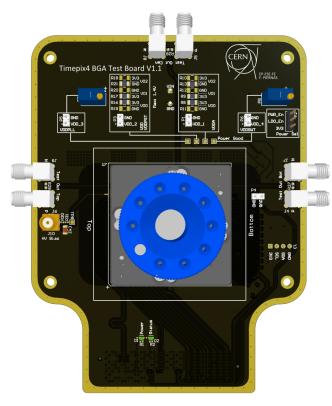

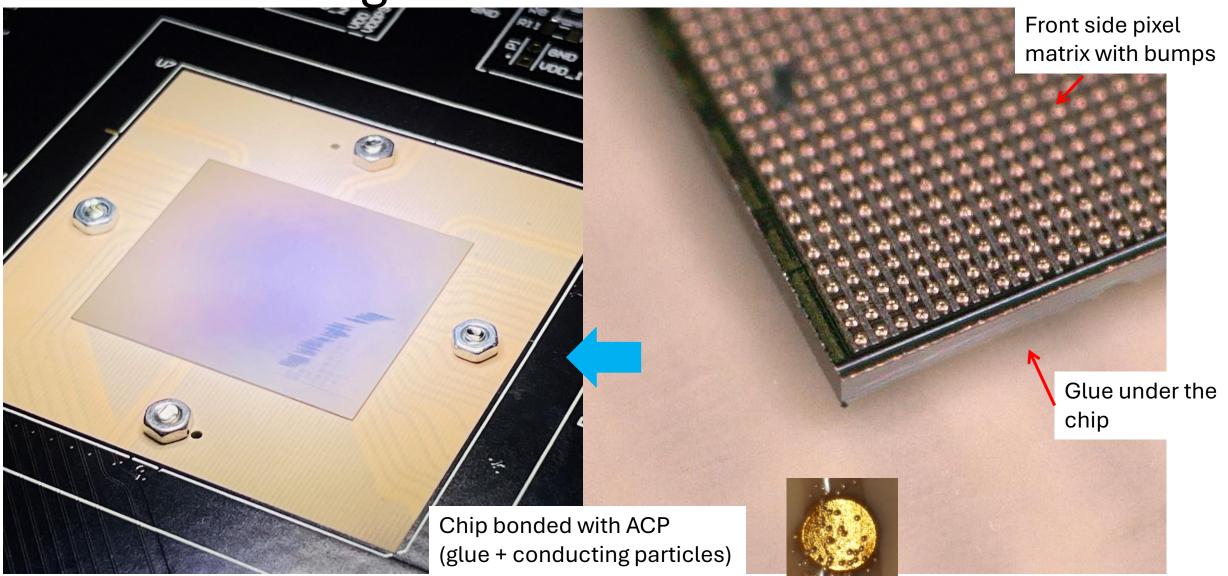

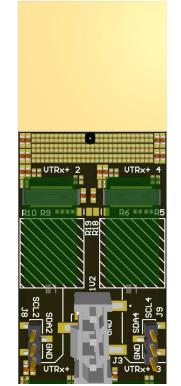

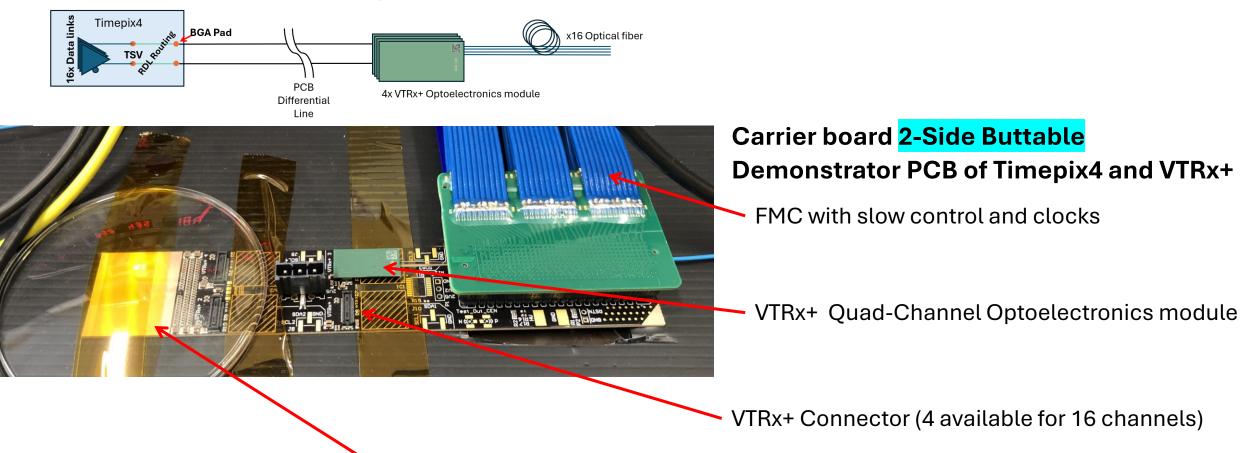

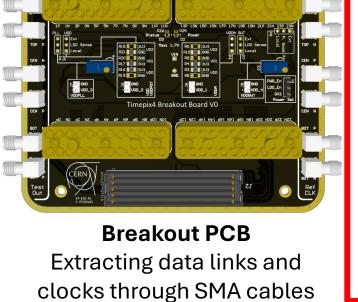

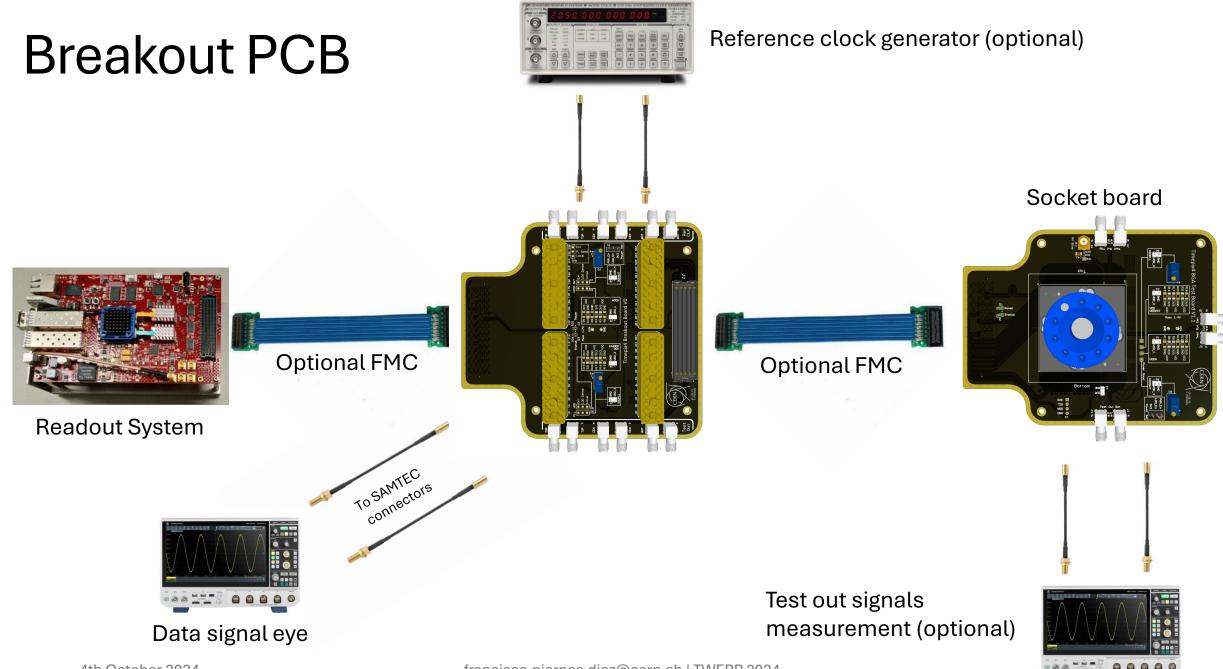

Family of PCBs for testing TSV-processed Timepix4

Socket PCB Electrical Tests

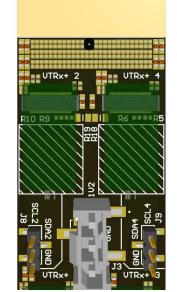

**Timepix4 & VTRx+** Optoelectronics Demonstrator

**Breakout PCB** Extracting data links and clocks through SMA cables

imepix4 Breakout Board VC

Timepix4 & SystemPIC Silicon Photonics

More in progress...

Family of PCBs for testing TSV-processed Timepix4

Socket PCB Electrical Tests

**Timepix4 & VTRx+** Optoelectronics Demonstrator

imepix4 Breakout Board VC

**Timepix4 & SystemPIC** Silicon Photonics

More in progress...

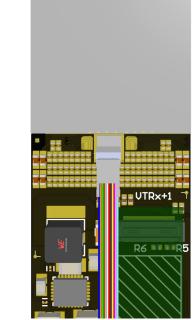

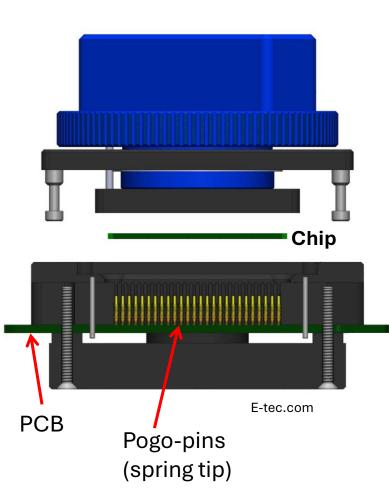

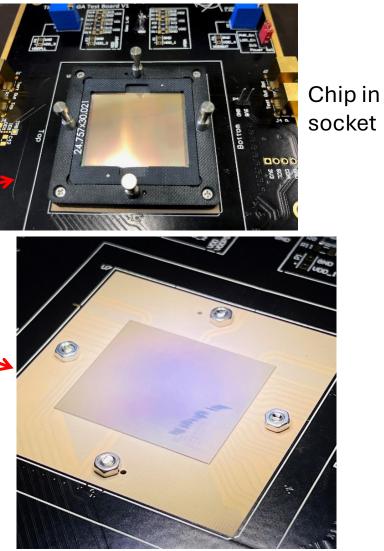

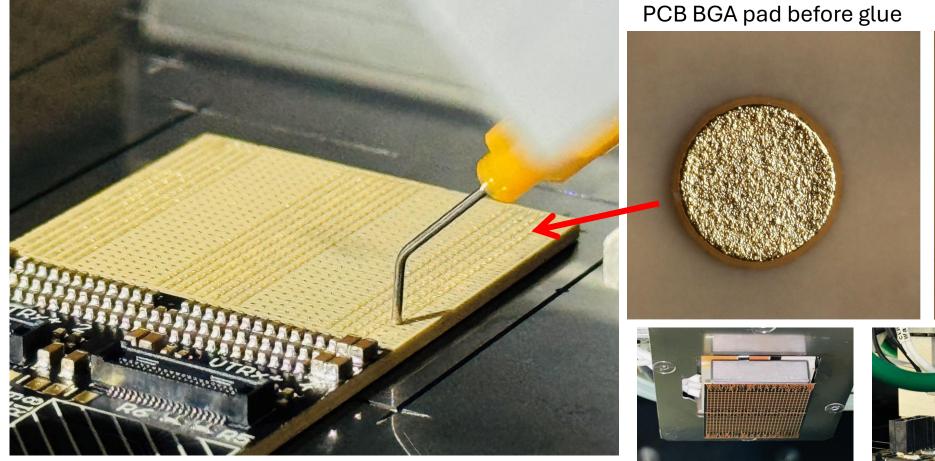

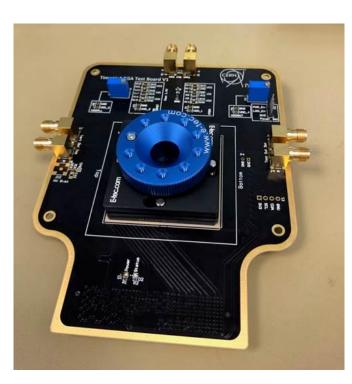

#### Pogo-pin based socket PCB that allows testing TSV-processed chips

Direct bonding compatible, with Anisotropic Conductive Paste (ACP) or BGA

PCB pad

Family of PCBs for testing TSV-processed Timepix4

Socket PCB Electrical Tests

**Timepix4 & VTRx+** Optoelectronics Demonstrator

**Timepix4 & SystemPIC** Silicon Photonics

More in progress...

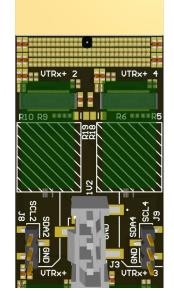

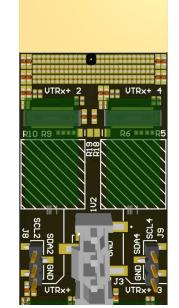

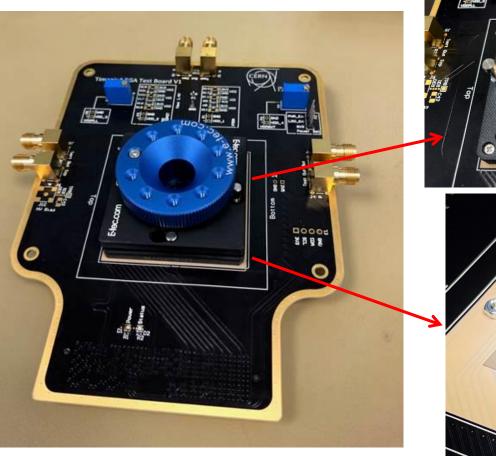

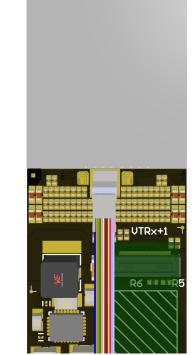

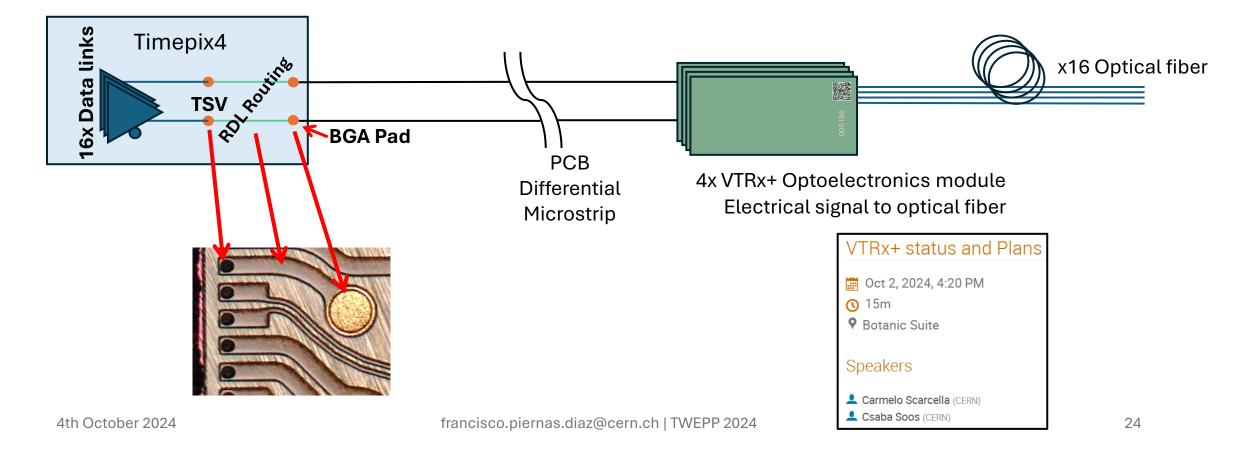

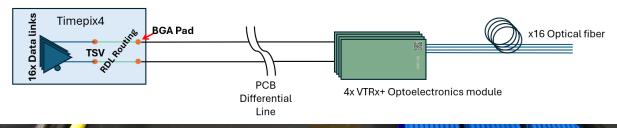

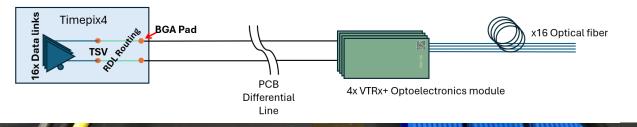

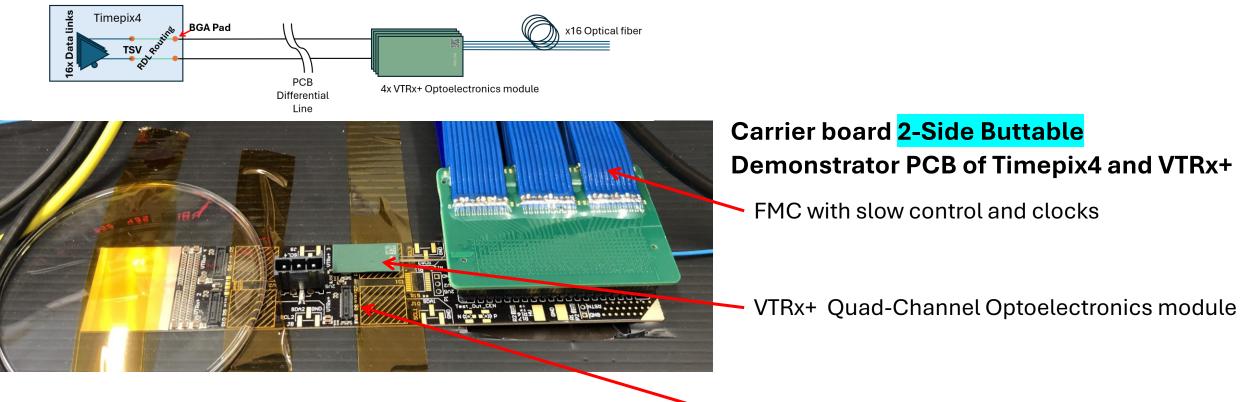

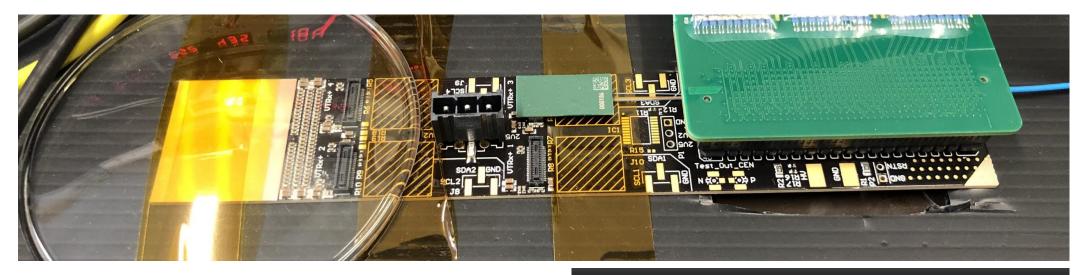

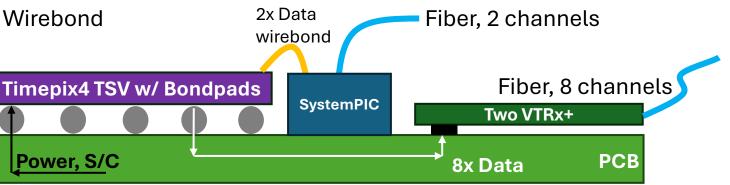

#### The Idea: Proof of principle for particle detector modules

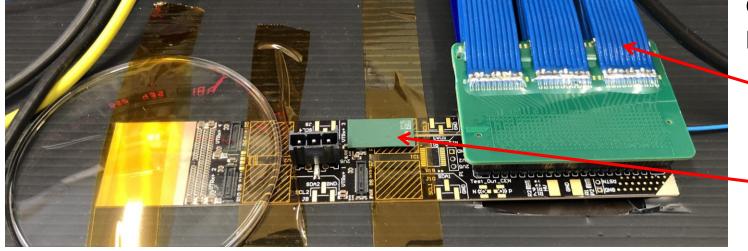

#### Carrier board <mark>2-Side Buttable</mark> Demonstrator PCB of Timepix4 and VTRx+

#### Carrier board <mark>2-Side Buttable</mark> Demonstrator PCB of Timepix4 and VTRx+

• FMC with slow control and clocks

#### Carrier board <mark>2-Side Buttable</mark> Demonstrator PCB of Timepix4 and VTRx+

FMC with slow control and clocks

VTRx+ Quad-Channel Optoelectronics module

VTRx+ Connector (4 available for 16 channels)

Timepix4 V1 TSV, bonded with ACP glue

|           | Pixel detector hybridization with anisotropic conductive adhesives |                                |  |  |

|-----------|--------------------------------------------------------------------|--------------------------------|--|--|

|           | 📑 Oct 1, 2024<br>🔇 1h 20m                                          | 1, 4:40 PM Seckaging and Inter |  |  |

|           | Speaker                                                            |                                |  |  |

|           | L Dr Ahmet Lale                                                    |                                |  |  |

| fore glue |                                                                    | After glue (30um particles)    |  |  |

|           |                                                                    |                                |  |  |

Assembly done at UniGe (University of Geneva)

Thermocompression

4th October 2024

francisco.piernas.diaz@cern.ch | TWEPP 2024

- 1. Through-Silicon-Via (TSV) Overview

- 2. Why TSV in Particle Detectors

- 3. TSV Processing of Timepix4

- 4. Module Design to Test TSV

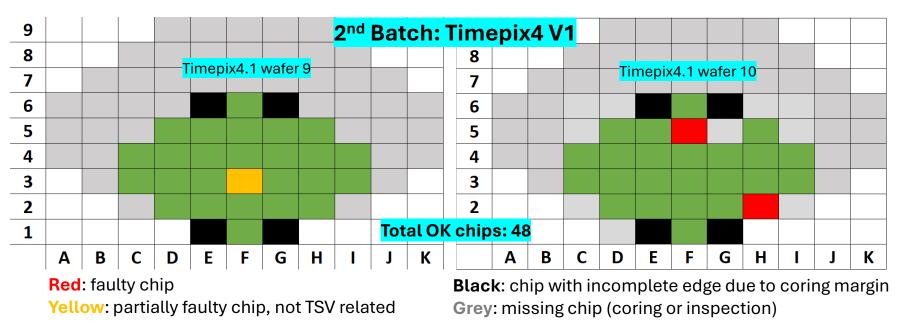

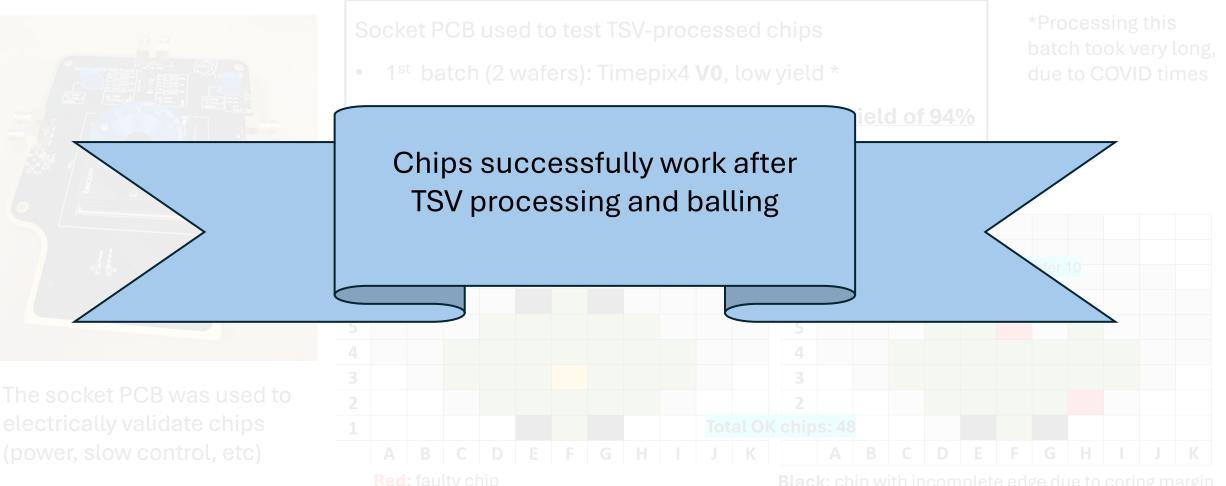

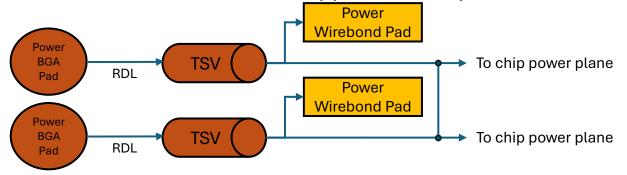

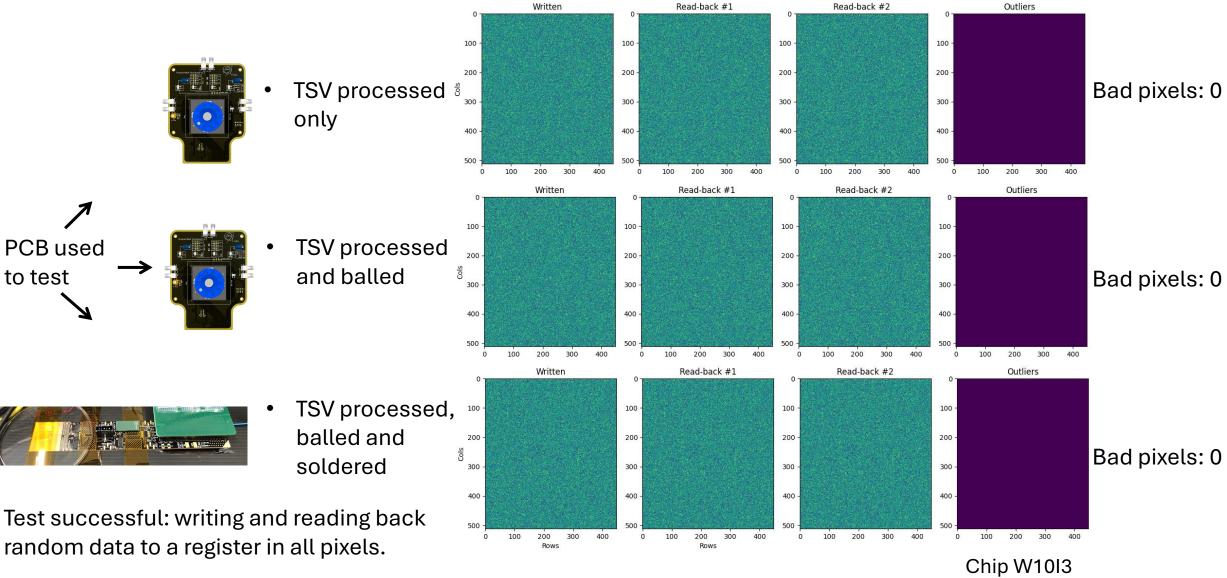

The socket PCB was used to electrically validate chips (power, slow control, etc) **Results:**

- 1<sup>st</sup> batch (2 wafers): Timepix4 V0, low yield \*

- 2<sup>nd</sup> batch (2 wafers): Timepix4 **V1**, <u>excellent yield of 94%</u>

- 3<sup>rd</sup> batch (3 wafers): Timepix4 V3, expected soon

\*Processing this batch took very long, due to COVID times

Yellow: partially faulty chip, not TSV related

**Black**: chip with incomplete edge due to coring margin **Grey:** missing chip (coring or inspection)

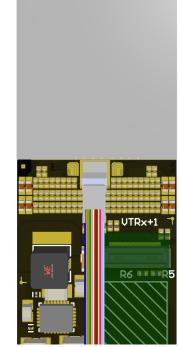

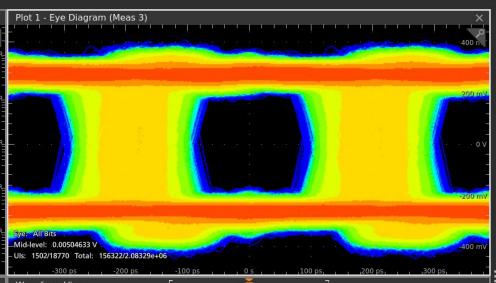

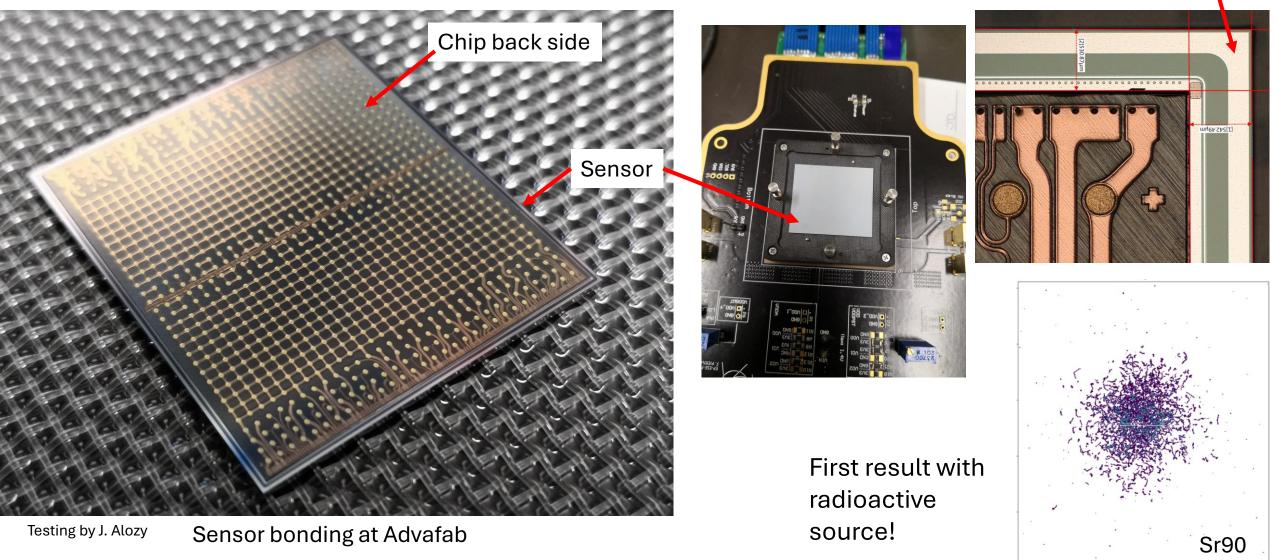

#### **Opto-demonstrator module**

#### Timepix4.1 TSV, bonded with ACP glue

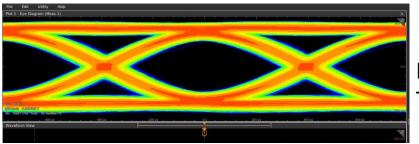

- Eye diagram through **optical fiber** at 2.56Gbps.

- This version of the chip has **problems with jitter**.

- Waiting for TSV processing of Timepix4 V3

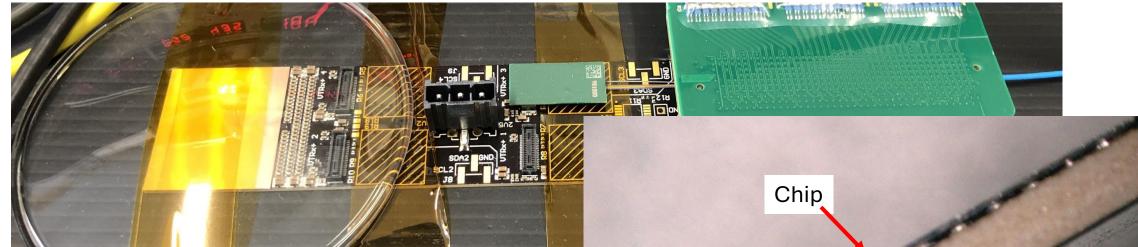

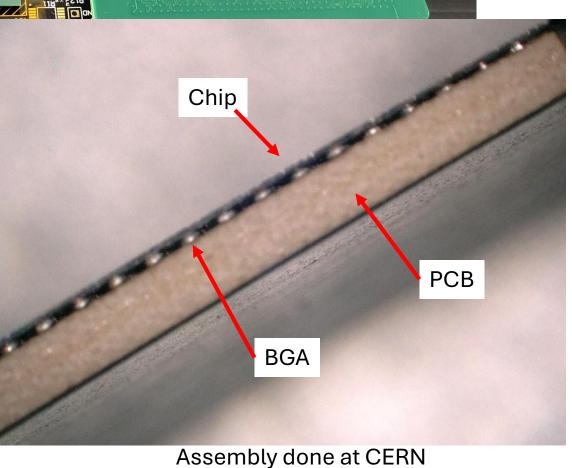

Same PCB but Timepix4.1 TSV soldered with BGA balls (for the first time) instead of ACP glue SAC305 alloy, 300um solder balls

Eye @1.25Gbps Through optical fiber

francisco.piernas.diaz@cern.ch | TWEPP 2024

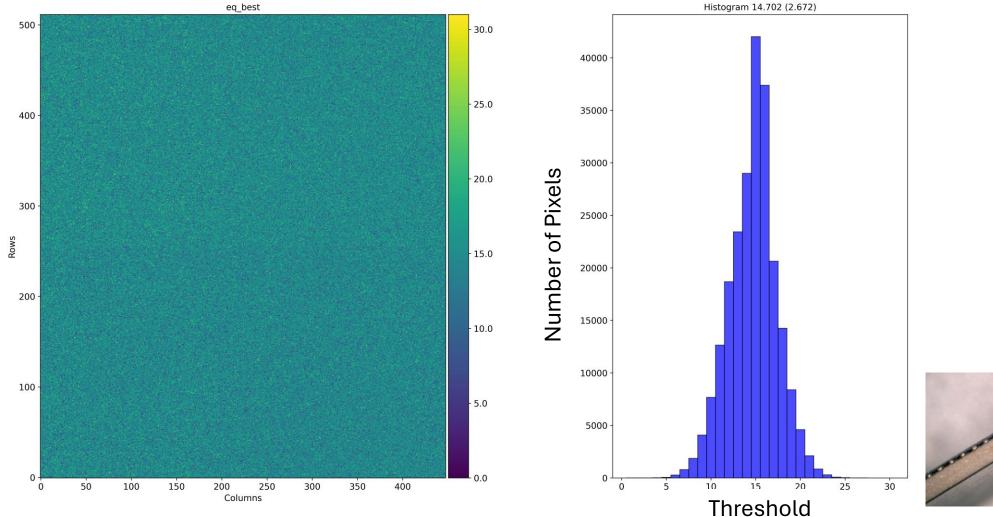

Threshold equalization with the previous PCB (Timepix4 V1 TSV soldered with BGA)

Slow control, global biasing DACs and pixel matrix working, after TSV processing, balling and soldering

4th October 2024

# 5. First Results and Future Work

Family of PCBs for testing TSV-processed Timepix4

Socket PCB Electrical Tests

**Timepix4 & VTRx+** Optoelectronics Demonstrator

**Timepix4 & SystemPIC** Silicon Photonics

More in progress...

# 5. First Results and Future Work

# Demonstrator PCB of Timepix4 and SystemPIC 2-Side Buttable Chip w/ bond pads and BGA SystemPIC Photonics Wirebond required Two VTRx+ Carrelo Scacella (CBM) C

#### One PCB to test, at the same time:

- Power and S/C through TSV

- Silicon Photonics with data through short Wirebond

- Optoelectronics with data through TSV

- In production

#### How will this assembly perform?

Silicon Photonics Circuits for the optical readout of CERN

### Last-minute Surprise!

## First Timepix4.1 TSV with Silicon Sensor

Sensor

## Conclusions and outlook

- TSV are a **suitable alternative** to wirebond.

- TSV successfully fabricated on Timepix4 chips.

- Tests show that chips work when connected to test modules.

- TSV processing is **tricky**, done at wafer level and some wafers are **used** for tuning of the process.

- Demonstrator **modules** for extracting data through optical fiber.

- Waiting for Timepix4 V3 with TSV for 5Gbps readout.

- Exploring other vendors for TSV processing (Europe and worldwide).

# Thank you for your attention

# Extra Slides

## **PCB** Design considerations

Copper cutouts to distribute current and voltage drop

Extension of data lines up to 15cm to test signal integrity (how far the VTRx+ can be placed).

- <u>Too close</u> to the readout ASIC: high radiation

- <u>Too far</u>: signal degradation

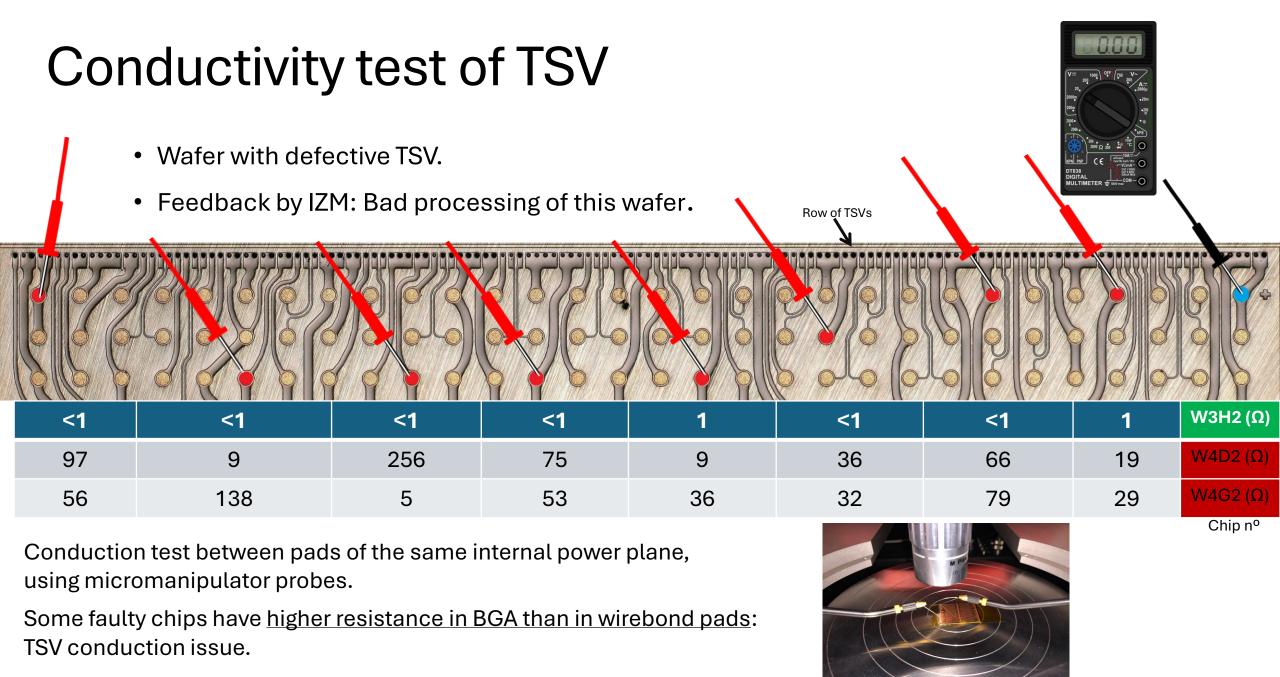

### **Bondpad Resistance vs BGA Resistance**

|              | Wafer 4 (faulty TSV) Resistance on VDDA |              |     |              |     |              |     |              |     |              |     |  |

|--------------|-----------------------------------------|--------------|-----|--------------|-----|--------------|-----|--------------|-----|--------------|-----|--|

| F1           |                                         | D2           |     | E2           |     | F2           |     | G2           |     | H2           |     |  |

| Bond<br>Pads | BGA                                     | Bond<br>Pads | BGA | Bond<br>Pads | BGA | Bond<br>Pads | BGA | Bond<br>Pads | BGA | Bond<br>Pads | BGA |  |

| 2            | 2                                       | 2            | 19  | 1.8          | 19  | 1.3          | 51  | 1.9          | 29  | 1.5          | 52  |  |

| 2            | 7                                       | 1.9          | 66  | 2.9          | 70  | 1.3          | 47  | 1.4          | 79  | 1.4          | 2   |  |

| 1.7          | 24                                      | 2            | 36  | 2.9          | 66  | 1.4          | 1   | 1.8          | 32  | 1.6          | 35  |  |

| 2            | 19                                      | 1.3          | 9   | 1.3          | 20  | 1.4          | 60  | 1.5          | 49  | 1.6          | 95  |  |

| 2            | 29                                      | 1.9          | 75  | 1.4          | 83  | 1.4          | 3   | 1.5          | 53  | 1.3          | 20  |  |

| 2            | 9                                       | 2.2          | 256 | 1.3          | 54  | 1.7          | 1   | 1.5          | 5   | 1.5          | 19  |  |

| 2            | 16                                      | 2            | 9   | 1.4          | 16  | 2.2          | 15  | 1.5          | 136 | 1.4          | 30  |  |

| 2            | 48                                      | 2            | 97  | 1.4          | 239 | 1.7          | 53  | 1.3          | 55  | 1.5          | 2   |  |

Measurements done by S. Al-Tawil

Observations: resistance on bond pads is overall lower than BGA on this wafer. Measurement sensitive to force applied on the pads.

# Soldering and Testing a Timepix4 V1

4th October 2024

francisco.piernas.diaz@cern.ch | TWEPP 2024

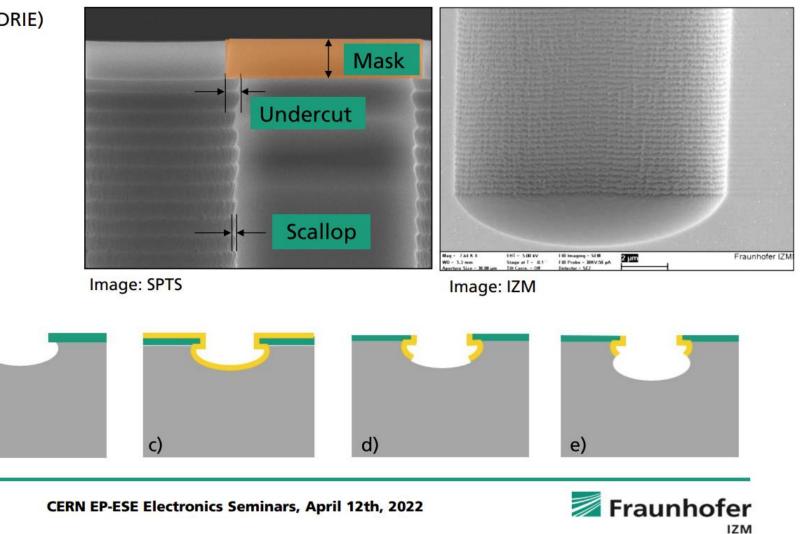

### Deep Reactive Ion Etching (DRIE) in Silicon

Deep Reactive Ion Etching (DRIE)

b)

- Bosch Process

- Switched Process

a) Resist or Hardmask

b) Isotropic Etch (SF6)

c) Deposition (C4F8)

d) Anisotropic Etch (SF6)

e) Isotropic Etch (SF6)

Silicon

Seminar by T. Fritzsch et al.

© Fraunhofer IZM

**IZM Fraunhofer**

a)

francisco.piernas.diaz@cern.ch | TWEPP 2024

# Chip with incomplete edge