#### UNIVERSITÉ DE GENÈVE

Performance tests and hardware qualification of the FEBs for the Super-FGD of T2K Phase II

> Topical Workshop on Electronics for Particle Physics Glasgow, October 4<sup>th</sup>, 2024

Lorenzo Giannessi, F. Cadoux, S. Cap, J. Chakrani, O. Drapier, Y. Favre, F. Gastaldi, M. Jakkapu, J. Nanni, K. Sakashita, F. Sanchez

- **1.** Introduction: what is the Super-FGD ?

- **2.** Electronics overview

- **3.** Requirements and FEB performance tests

- 4. FEB mass production serial testing

- **5.** Conclusions

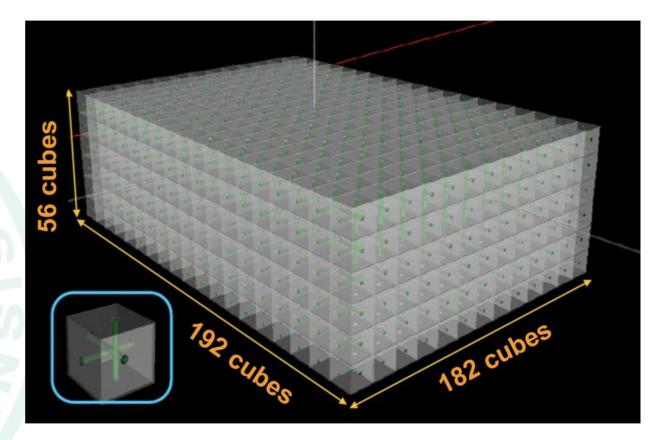

# 1. What is the Super-FGD?

## **The Super Fine-Grained Detector**

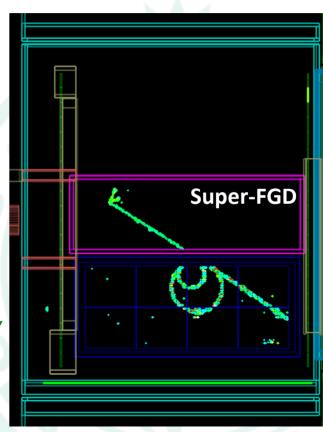

# New neutrino active target for T2K Near Detector

- 2-million 1-cm<sup>3</sup> polystyrene cubes

- 2 tons fiducial mass

high granularity

3D tracking

- ≻~60k optic fibers + SiPM

⇔ 60k readout channels

MPPC

# 2. Electronics overview and requirements

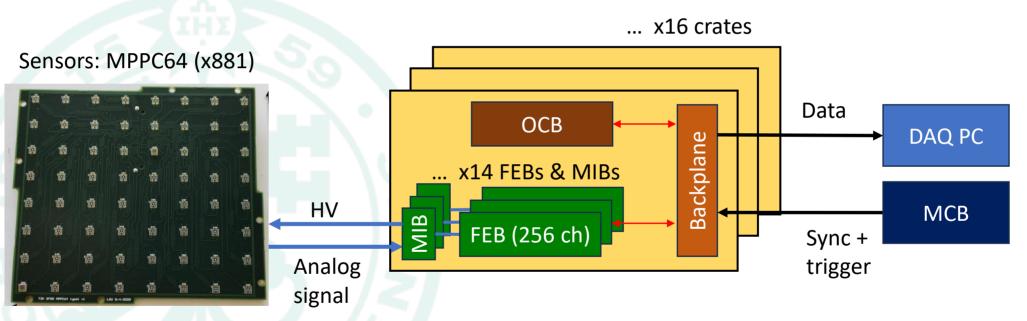

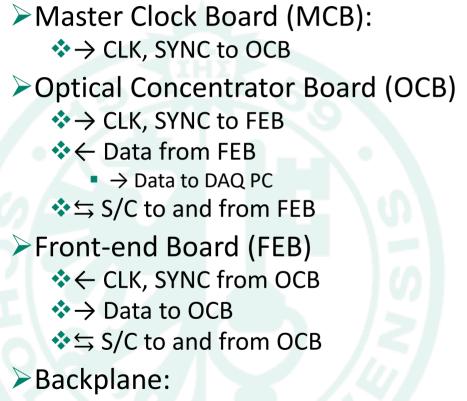

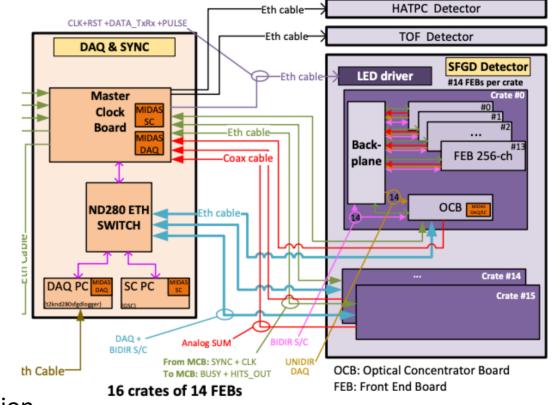

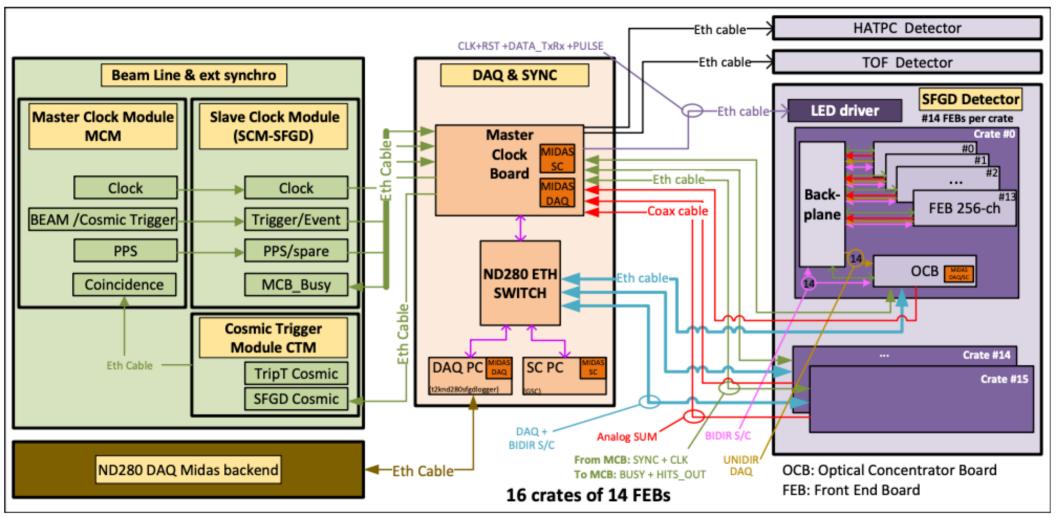

## **SFGD electronics overview**

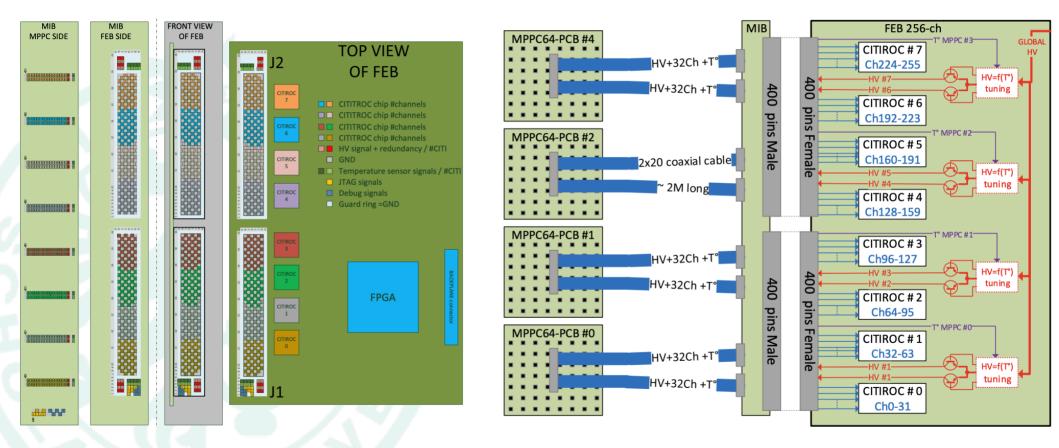

### 55'888 SiPM channels $\Rightarrow$ 16 Crates, 14 FEBs each

OCB (1 per crate) and MCB: S/C, data concentration, sync, trigger

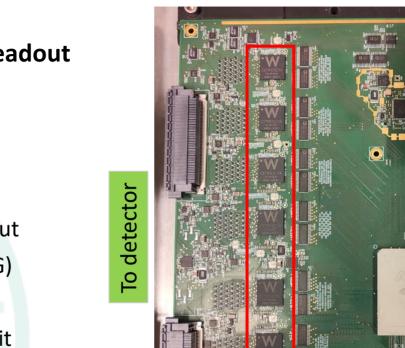

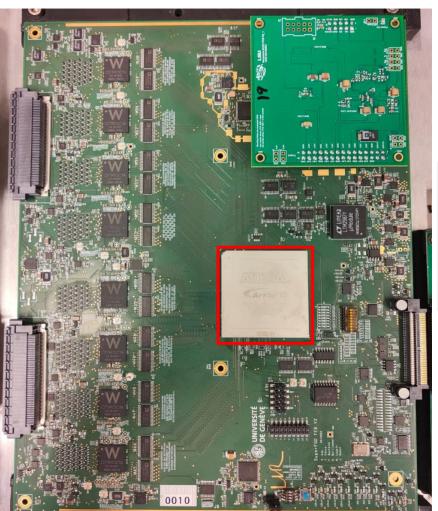

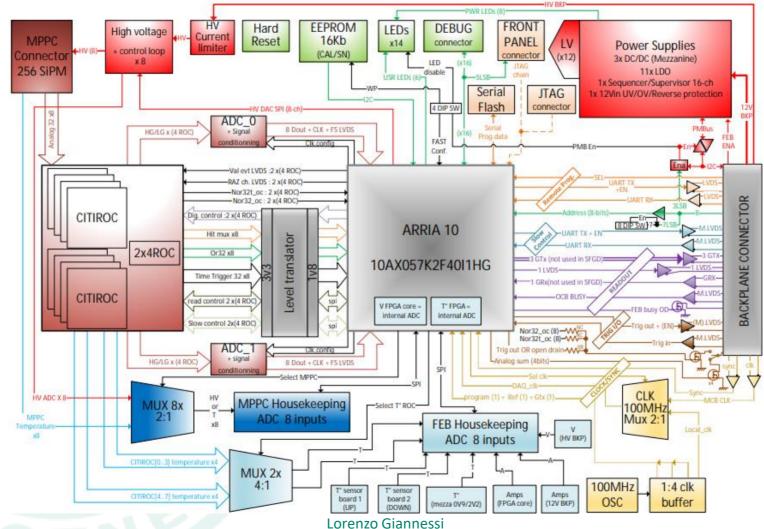

#### Focus of this talk: FEB:

Amplification, shaping and digitization of 256 channels

03/10/24

256 channel charge + timing readout

- ➢8 CITIROC by Omega [1]:

- 32-ch read out chips

- Types of read-out:

- Timing: constant threshold trigger output

Charge: dual gain peak detector (HG, LG)

Programmable devices:

- Timing and analog thresholds: 10(+4)-bit

- ✤Gain for charge readout: 6-bit

- Shaping time: 3-bit

#### [1] CITIROC by Omega

Lorenzo Gianness

#### 03/10/24

б

backplane

**Configuration and slow control**

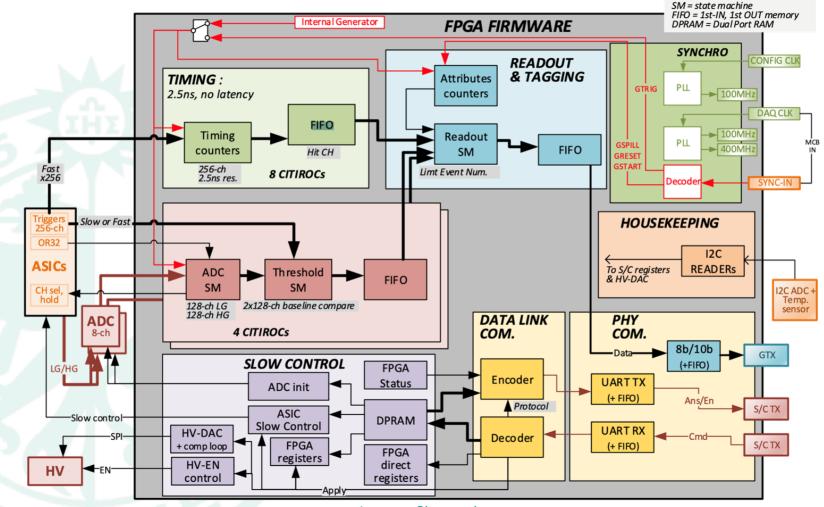

#### FPGA ARRIA 10

- Data concentration and S/C

- 400 MHz sampling rate for timing measurement

- ROC configuration

- Housekeeping

- Remote programming

# To detector

0

backplane

#### Digitization, power, housekeeping

- ➤Two 8-ch 12-bit ADCs for charge digitization

- Sensors for temperature, voltage and currents

- Supervisor chip

- DC-DC mezzanine board

- >16 3v3-1v8 level translators

- EEPROM for calibration data

# To detector

To backplane

# 3. Requirements and performance tests

Validation of the FEB design against detector requirements

## Requirements

- ➢ Dynamic range: 1 − 1000 p.e (or 100 fC − 100 pC)

- Energy resolution < 1 p.e. in HG mode</p>

- Electronics cross talk below 1%

- ≻1 ns timing resolution

## **Challenges:**

- $\sim$ 1 year for production + hardware testing + installation

- Limited space inside UA1 magnet

- $\sim$ 10 years expected lifetime

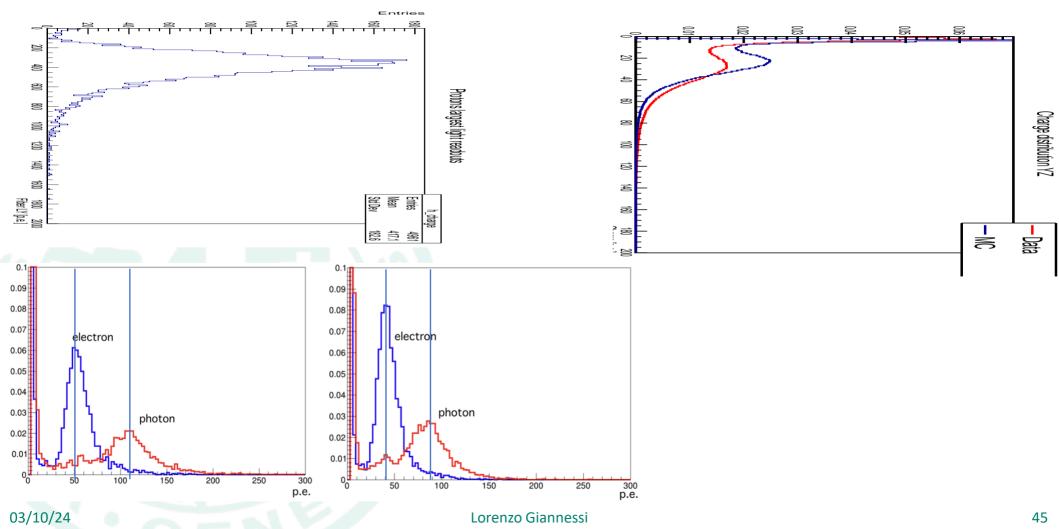

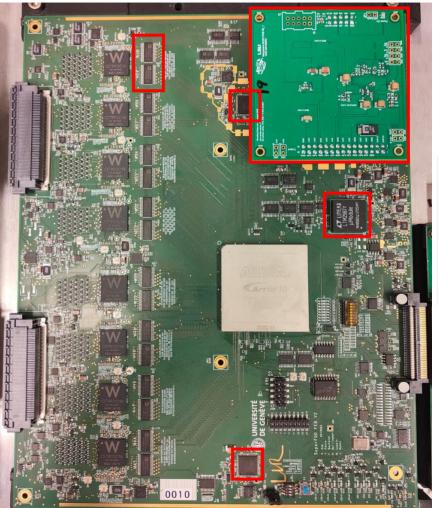

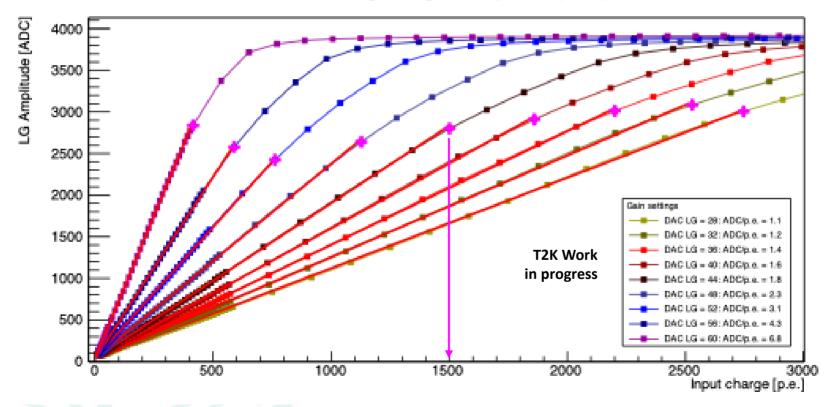

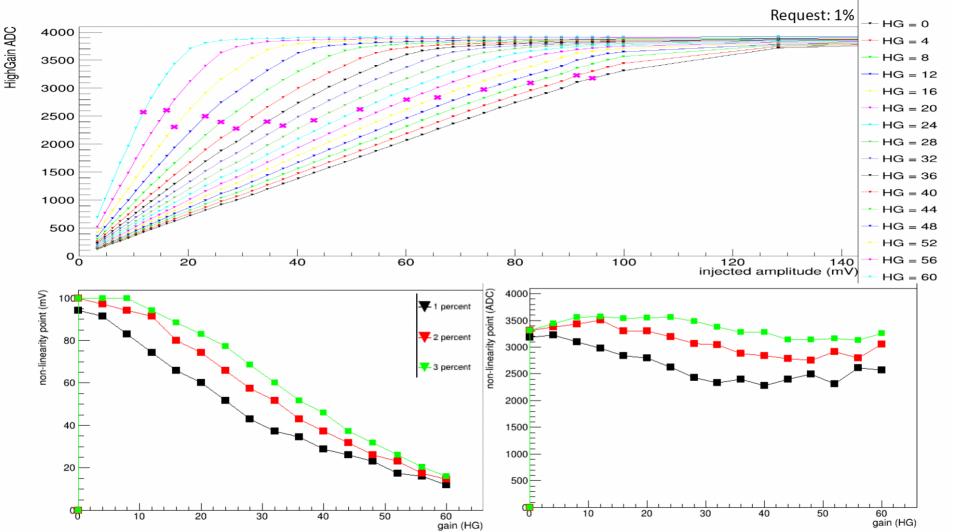

## **Dynamic range & energy resolution**

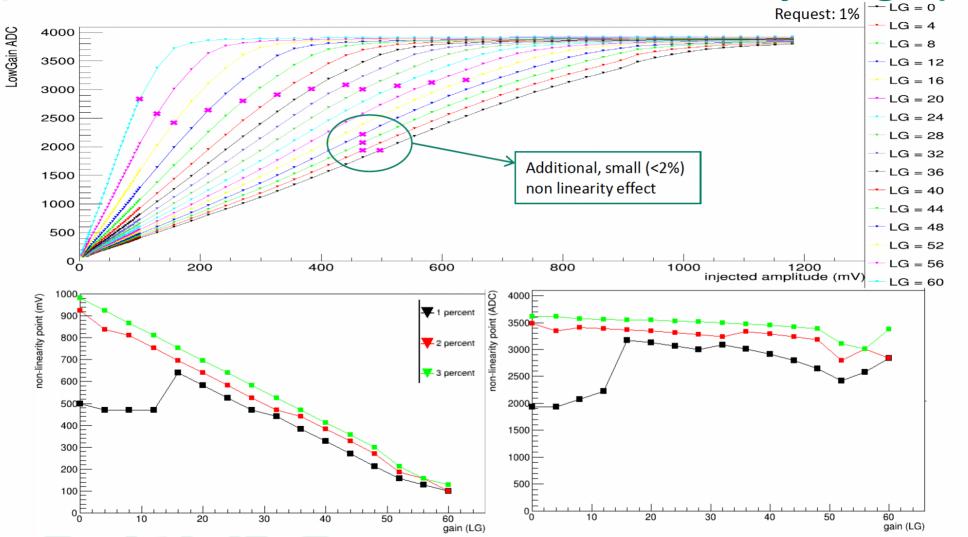

#### Dynamic range

- Limited by **non-linearity** of the CITIROC response.

- Upper limit: LG linear limit

#### LG linear limit > 1000 p.e

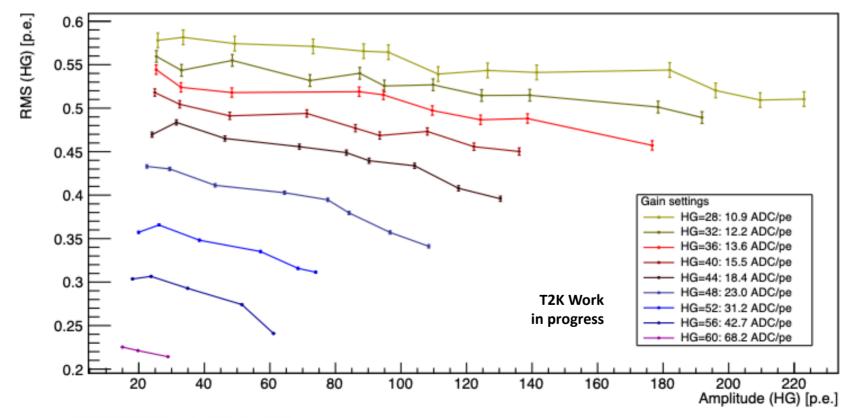

#### Energy resolution (HG output)

Electronic noise degrades energy resolution.

Study RMS of the signal in HG mode.

RMS < 1 p.e.

RMS vs Amplitude (FEB ch 0) in the linearity regime

FEB low-gain signal response (ch 0)

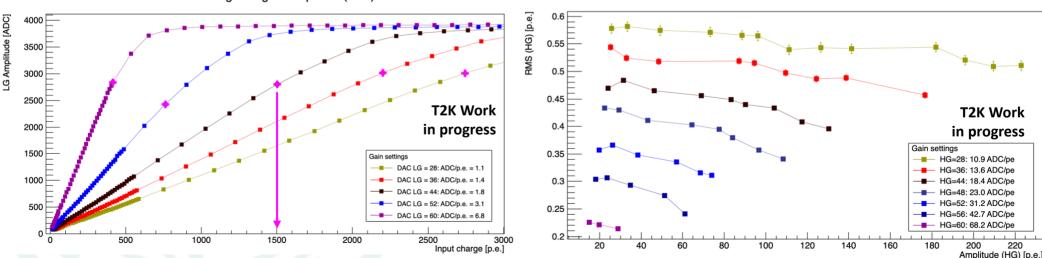

Electronics cross talk:

< 0.5 %

Only intra-ROC

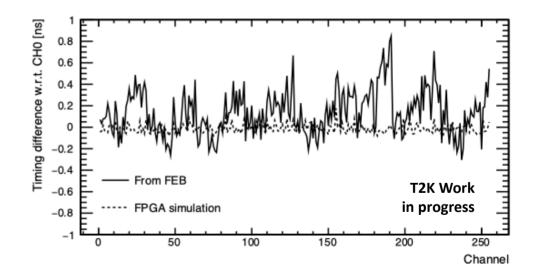

## **Cross talk & timing**

Channel-by-channel timing delays:

~ 1 ns

$\rightarrow$  Need time calibration or FPGA programmable delay

Work by J.Chakrani

12

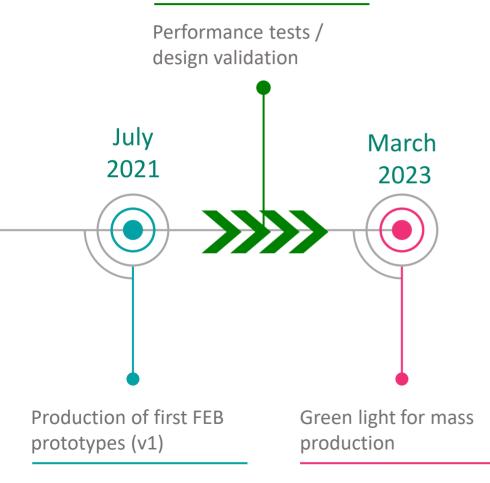

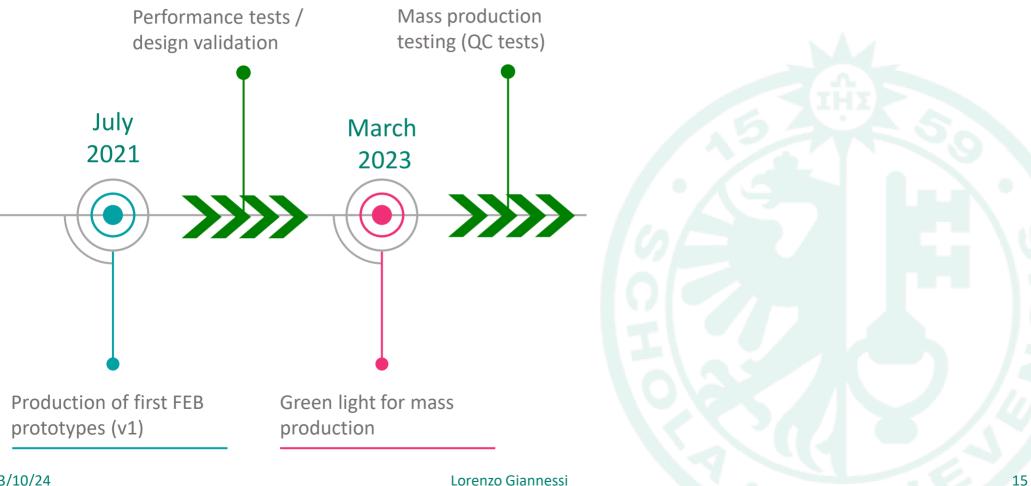

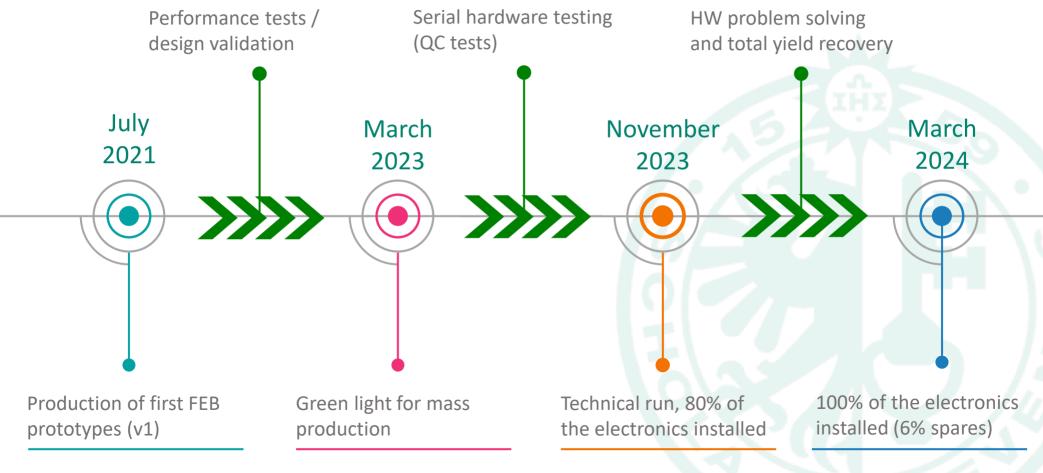

## **History of the Super-FGD FEBs**

prototypes (v1)

03/10/24

## **History of the Super-FGD FEBs**

## **History of the Super-FGD FEBs**

03/10/24

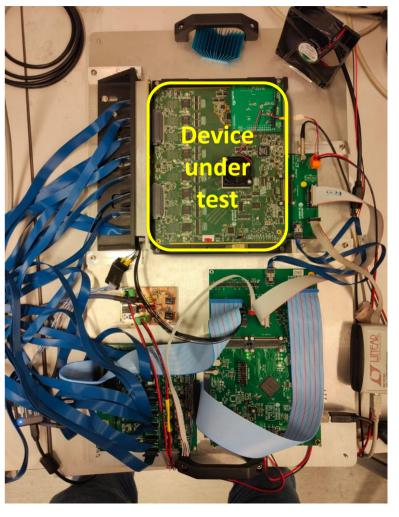

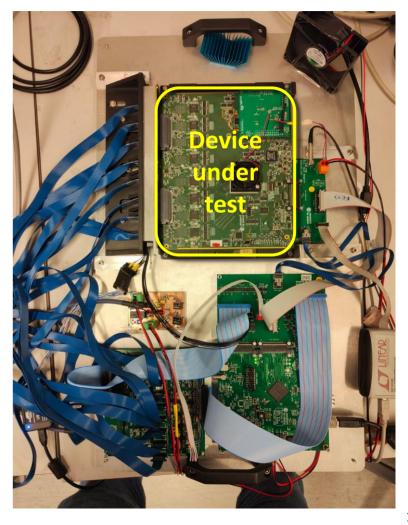

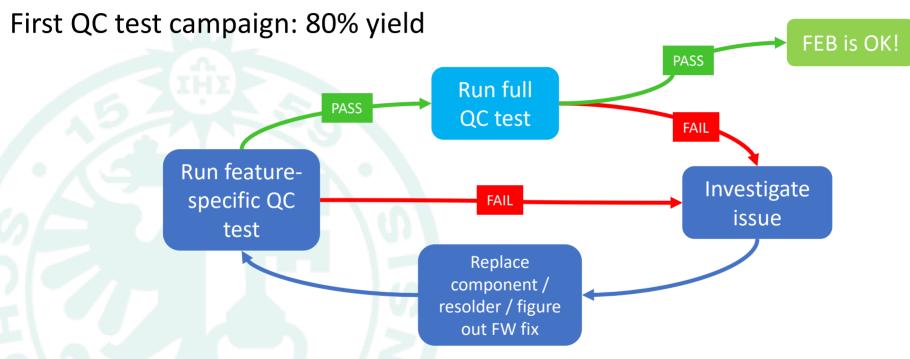

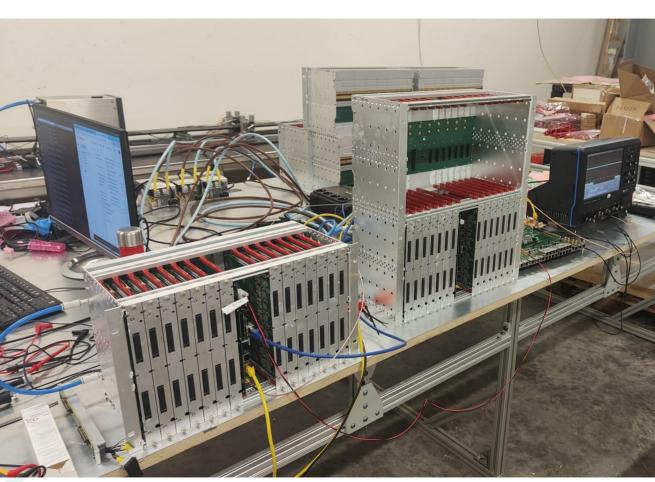

# 4. Mass production testing

Hardware quality check for the FEB mass production

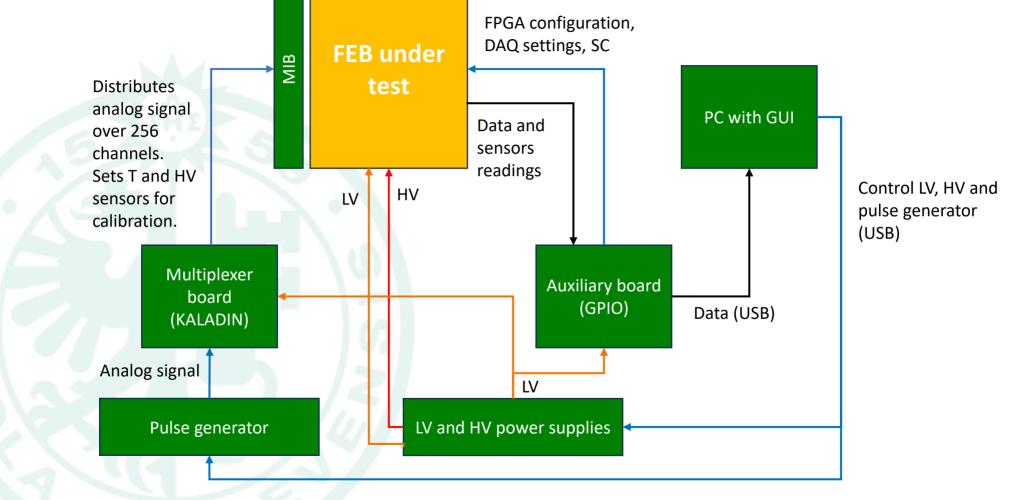

Mass production: 240 FEBs -> serial hardware testing

**Challenge:** need to speed up the testing (and repairing!) process.

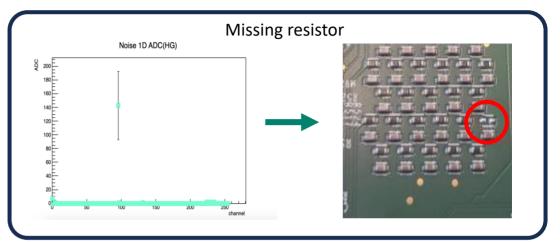

**Solution**: custom QC test bench with "symptom  $\rightarrow$  HW issue" diagnostic.

> Table-top setup, 6 minutes >99% hardware coverage: Analog traces Sync, clk, trigger, busy CITIROC configuration, S/C HV/T sensors + calibration Custom auxiliary board **Flexible**: edit software to test specific hardware problems **Locate** HW problems

03/10/24

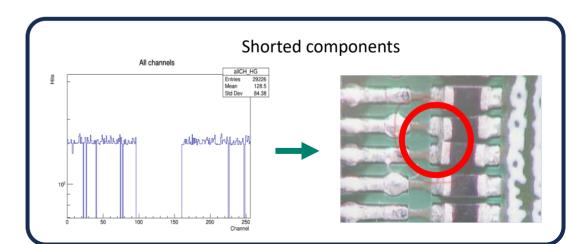

- Bad/cold soldering

Missing/wrong passive component

- Shorts on surface components

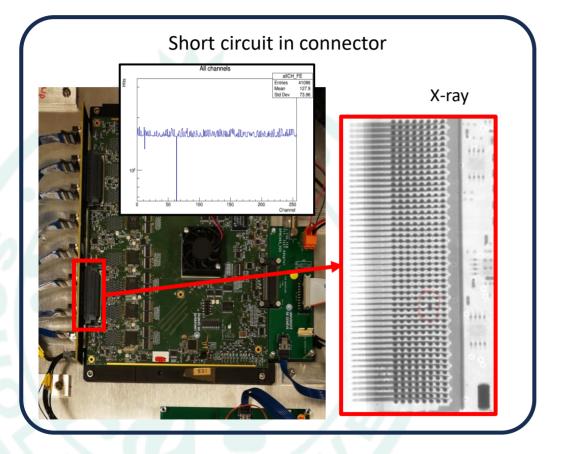

### Others can be nasty...

Shorts under connectors

Cold-soldered BGA

CITIROC to be replaced

Bad PCB routing

Ship back to manufacturer: major delay

**Yield recovery**

#### Initial plan: 222 FEBs installed + 10% spares

Take-home message: A custom, versatile QC setup is more work, but ends up saving time and resources.

## T2K

## **History of the Super-FGD FEBs**

03/10/24

## **5.** Conclusions

FEBs for the Super-FGD performances validated and 240 FEBs successfully tested (repaired) and installed

Custom, table-top QC test bench proven to be essential

First neutrino beam run of T2K phase II (June 2024)

# **Back up**

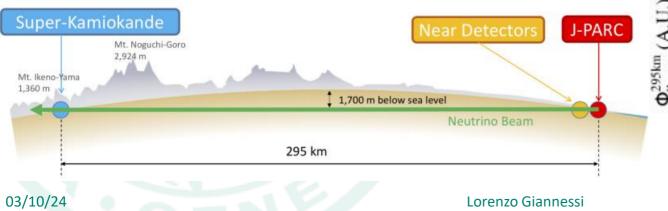

## **The T2K Experiment**

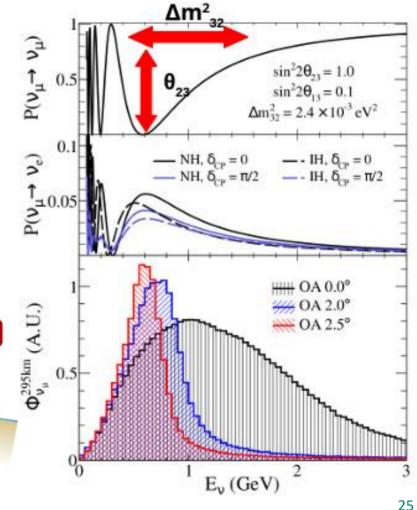

- T2K is a long baseline neutrino oscillation experiment

- Sensitive to  $\delta_{\text{CP}}$  through **electron (anti-) neutrino disappearance**

- Sensitive to  $\Delta m_{32}^2$  and  $\theta_{23}^2$  through muon (anti-) neutrino appearance

- Near detector is being upgraded with 3 new subdetectors (Super-FGD, High-angle TPCs, TOF)

Super-FGD: new neutrino active target

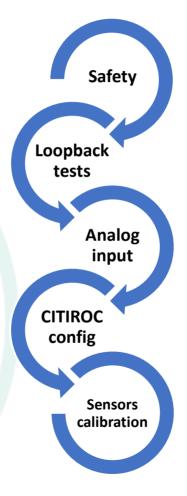

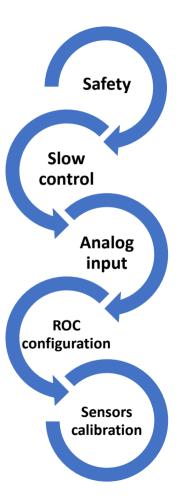

## Hardware serial testing - scheme

03/10/24

#### Safety:

Test HV current limiter circuit

### Slow control

Test slow control lines (FPGA to backplane, FPGA to CITIROC, ) with loopback circuits (FPGA driven)

### Analog input

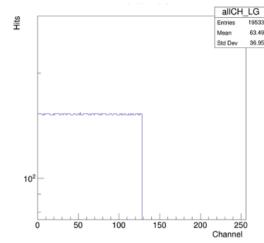

Test all channels against open/short circuits. Check ADC output validity range. Evaluate noise and baseline – extensive use of Kaladin board

## ROC configuration

Check that the FPGA is able to configure the CITIROCs with different trigger configurations (ability to control the CITIROC programmable devices)

### Sensors calibration

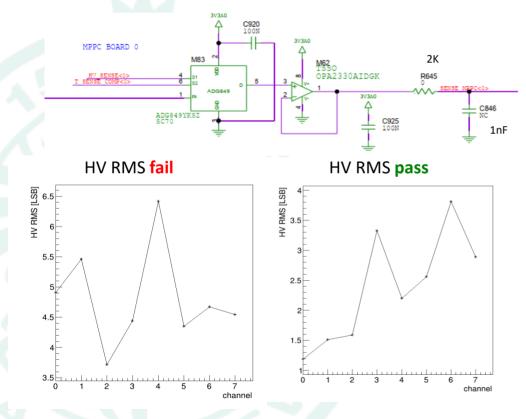

Calibrate the HV and T sensors and check that the calibration constants are stored in the EEPROM. Measure RMS (RC filter test)

## **Global testing**

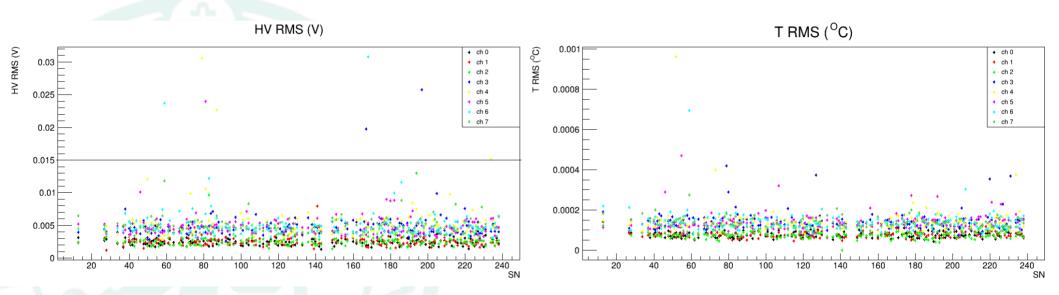

Global results on T/HV sensors precision [gain equalization]

>RMS values of the T and HV sensors to evaluate overall performances

Gain equalization: 55mV/°C HV gain change in MPPC sets requirement on RMS(V)

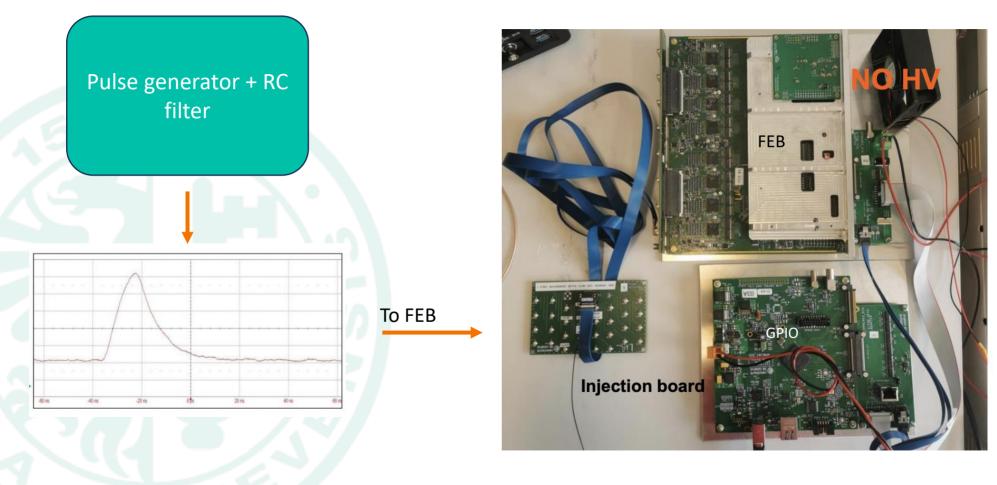

## **Linearity range & resolution - setup**

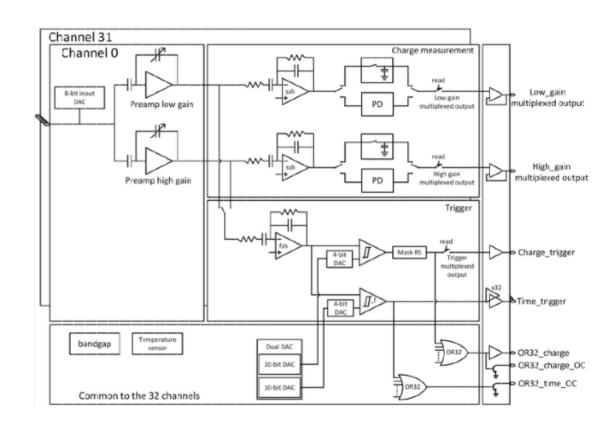

## **FEB architecture - CITIROC**

## ➤32 channels

## **Types of read-out:**

- Timing: constant threshold trigger output

- Charge: dual gain with peak detector (HG, LG)

- **Programmable devices:**

- Timing and analog thresholds: 10(+4)-bit

- Input DAC for MPPC voltage tuning: 8-bit

- ➢Gain for charge readout: 6-bit

- Shaping time: 3-bit

[1] add CITIROC reference here

#### 03/10/24

- Full crate "burning test"

- BER tests (OCB-FEB)

- > OCB-FEB communication

- MCB-OCB communication

- DAQ stability tests

## **Other tests**

03/10/24

## Connectivity

## **Linearity & energy resolution**

FEB low-gain signal response (ch 0)

## **Linearity & energy resolution**

#### Energy resolution (HG output)

#### RMS vs Amplitude (FEB ch 0) in the linearity regime

## Hardware test: RC filter

# Calibration of HV and NTC sensors Check passive components

## Hardware test: HV current limiter

HV BKF

ST2325DS-SOT23

R586

0.125W

R248

125MW

0805

Ζ

150 K

HV MATN

HV SET<0>

CURRENT LIMITER

R247

2.2K

**R249** 47K 0.125W

Q2

MMBT2907

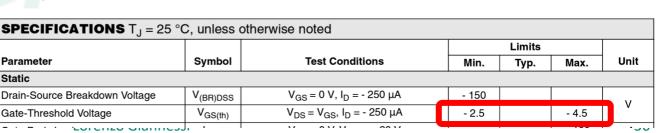

- We want to make sure that the resistor in the current limiter circuit is 150KΩ.

\* |V<sub>gs</sub>| < 20 V to not damage transistor</li>

The GS threshold voltage is between -2.5 and -4.5 V

- > V<sub>GS</sub> is computed as (given R=R586):

$$V_{GS} = V_{PS} \cdot \left(\frac{R}{(47+R+0.022)}\right) - \left(V_{PS} \cdot \frac{(47+R)}{(47+R+0.022)}\right)$$

- For the same V<sub>PS</sub>, if the resistance changes, the voltage applied on the GS terminals of the transistor change.

- With higher R, the V<sub>PS</sub> necessary to enable the transistor is higher

SPECIFICATIONS T<sub>J</sub> = 25 °C, unless otherwise noted

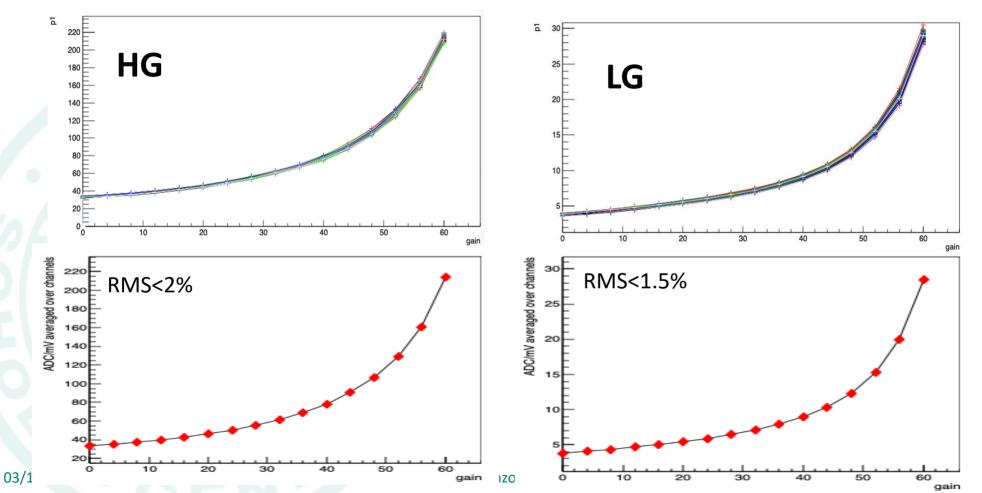

## **Gain uniformity**

### Measured gain (ADC/mV) for all 256 FEB channels

37

## Linearity range (LG)

## Linearity range (HG)

39

## **Electronics overview**

## 16 crates – 14 FEBs per crate – 256 read out channels per FEB

OCB-FEB interface and power distribution

#### OVERVIEW: 16 crates – 14 FEBs per crate – 256 read out channels per FEB

## **Firmware**

03/10/24

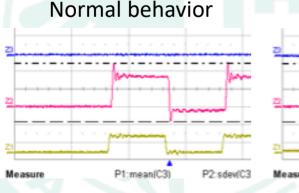

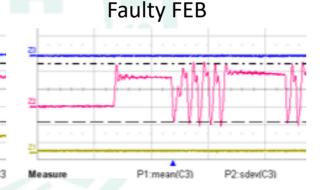

## **Example of "FW fix"**

- Problem: CITIROC (group 1) configuration fails

- Cause: reflections on the ROC-FPGA bidirectional level translator

- Due to change in design between FEB v1 and v2

- Solution: increase current on FPGA pin out

Design improvement in v3 (adding capacitor, change level translator)

#### Test S/C signal:

#### QC test symptom:

#### 4 mA on FPGA pin-out:

#### 03/10/24

44

## **Typical light yields in SFGD**