# Circuits and Layouts

- Introduction, definitions

- Layout and interconnects in IC technology

- Transistor MOS layouts

- Passive components layouts

#### Introduction

- IC (integrated circuits) single silicon chip that includes active and passive interconnected devices to implement complex operations (analogue, digital)

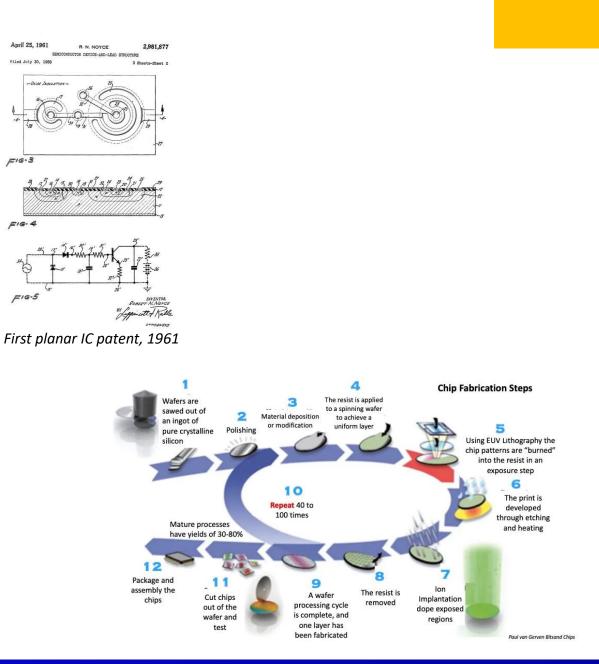

- Planar technology: the processing steps are implemented in a thin layer of the surface of the chip

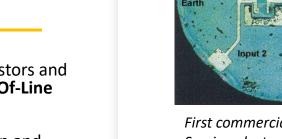

- Fabrication of chip is an extremely complex process, requiring several steps of atomic precision

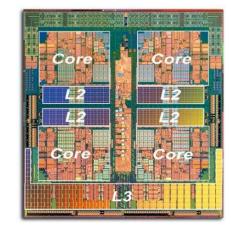

- **Device scaling** leads to cost reduction and increased speed per transistor

- However, due to the high number of transistors on chip, layout optimization at chip level has become as important as transistors fabrication

- Interconnecting the devices has become the bottleneck for IC performances

#### in Data Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years This advancement is important for other aspects of technological progress in computing – such as processing speed or the p Transistor count 50,000,000,000 10,000,000,000 5.000.000.000 1.000.000.000 500,000,000 100.000.000 50,000,000 10.000.000 5.000.000 1.000,000 500,000 100,000 ARM 50,000 ARM

Moore's Law: The number of transistors on microchips doubles every two years Our World

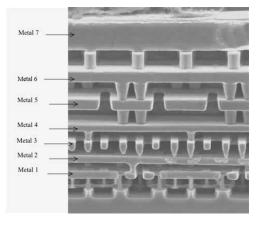

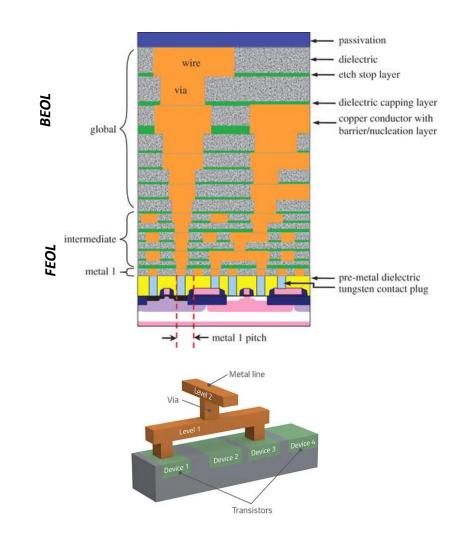

- The processing steps involved in fabricating transistors and their immediate interconnect is called Front-End-Of-Line (FEOL)

- That includes implantation, oxide growth, diffusion and ٠ first metal layer deposition

- Interconnecting all the devices together with higher metals is the Back-End-Of-Line (BEOL)

- As the number of transistors on chips grew, it became impossible to make all connections in a single layer ٠

- Added additional vertical levels of interconnects ٠

- Simpler IC might have a few metal layers, complex ICs exceed 10 layers ٠

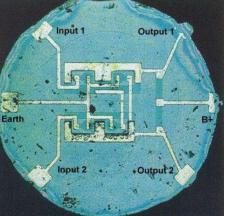

First commercial IC, Fairchild Semiconductor, 1961. Flip-Flop

- 1. N-Si substrate polishing  $(80 \ \mu m \pm 5 \ \mu m)$

- Oxidation (wet oxide 8000 Å) 2.

- MASK 1 (Isolation Wet etch oxide

- Boron Deposition and Drive-in MASK 2 (Base and P-Resistor)

- 7. Boron diffusion (~ 6000 Å oxide, ~ 150  $\Omega/sq$

- 8. MASK 3 (Emitter and Collector Contacts)

- 9. Phosphorus Deposition and Drive-in (~ 2  $\Omega/sq$  and  $X_i \sim 1.4-1.6 \mu m$ ) 10. Resist (front side)

- 11. Wet etch oxide (back side only)

- 12. Vacuum Evaporation of Gold on the back side ( $\sim 400$  Å)

- 13. Gold Diffusion (~  $1050^{\circ}C/\sim 15$  min with fast cool)

- 14. MASK 4 (Contacts)

- 15. Evaporate Aluminum (front side, 0.01  $\Omega/sq$ )

- 16. MASK 5 (Metal)

- 17. Wet etch metal (25% solution of sodium hydroxide)

- 18. Metal alloying ( $\sim 600^{\circ}$ C/ Argon)

Original Planar process flow (from Fairchild Semiconductor)

- Various levels of interconnects are present in modern ICs:

- **Metal 1**, for short local interconnects

- Intermediate, to connect devices within blocks

- **Global interconnects**, for long, low resistivity connections, including power, grounds

- Various levels are connected by vias and separated by dielectrics

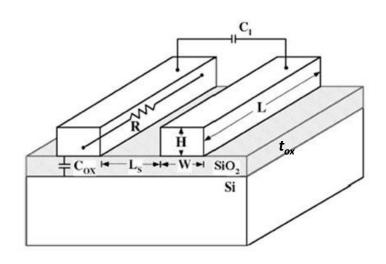

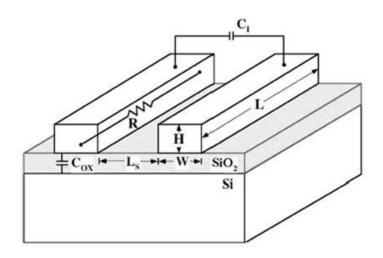

- Interconnects and their layouts are of increasing importance as the feature size of circuit elements become smaller

- **Delay times** of interconnect transmission line

$$R = \rho \frac{L}{WH}$$

$$C_{ox} = \varepsilon_{ox} \varepsilon_o \frac{WL}{t_{ox}}$$

$$c_I = \varepsilon_{ox} \varepsilon_o \frac{HL}{L_s}$$

$$\tau_I \cong \varepsilon_{ox} \varepsilon_o \rho \frac{L^2}{WH} (\frac{W}{t_{ox}} + \frac{H}{L_s})$$

$$C_{tot} \cong C_I + C_{ox}$$

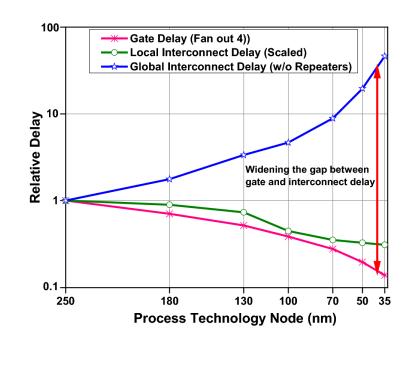

- As the technology size decreases:

- W, L<sub>s</sub> and H decrease

- $t_{ox}$  decrease at ~ the same rate as W and H i.e. by a scaling factor  $\lambda$

- The distance L for local interconnect decreases as the sized of devices gets smaller (~  $\lambda$ )

- Time delay  $\tau_{iloc}$  for local interconnect remains ~ constant or slightly decreases

$$\tau_i \cong \varepsilon_{ox} \varepsilon_o \rho \frac{L^2}{WH} \left( \frac{W}{t_{ox}} + \frac{H}{L_s} \right)$$

$$\tau_{iloc} \propto \varepsilon_{ox} \varepsilon_o \rho \frac{\lambda^2}{\lambda^2}$$

- As the technology size decreases:

- Area S of the die tends to increase

- Length of global interconnect increases √S

- Time delay  $\tau_{igIo}$  for **global interconnect** tends to increase

$\tau_{igIo} \cong \varepsilon_{ox} \varepsilon_o \rho \frac{S}{\lambda^2}$

- Time delay  $\tau_{igIo}$  for **global interconnect** tends to increase as the technology size decreases

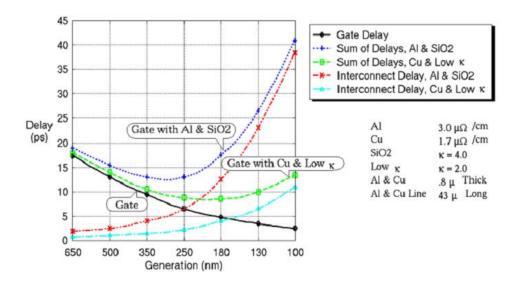

- Different materials can be used for the interconnect to reduce  $\rho$  and  $\epsilon$

The global interconnect delay vs. technology node for standard and advanced materials

$$\tau_{igIo} \cong \varepsilon_{ox} \varepsilon_o \rho \frac{S}{\lambda^2}$$

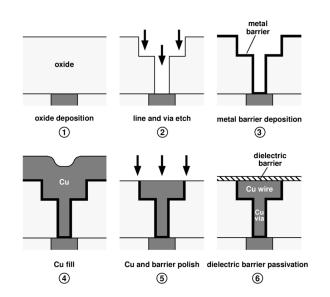

- Reducing ρ has been achieved by using Cu instead of Al (Damascene\* process)

- Reduce ε is more challenging: low-K dielectrics can be obtained using F and other dopants but resulting dielectric show poorer quality

- Air gaps are also used (ε =1) in some locations in <10 nm nodes</li>

Dual Damascene process. An additional metal barrier (W) is deposited first to avoid Cu contamination of Si. Cu deposited by electroplating. CMP is needed as Cu does not plasma etch<sup>[1]</sup>.

| Properties                  | SiO <sub>2</sub> | FSG     | Dense low-k<br>(OSG) | Porous low- |

|-----------------------------|------------------|---------|----------------------|-------------|

| Density (g/cm³)             | 2.2              | 2.2     | 1.8~1.2              | 1.2~1.0     |

| Dielectric constant (k)     | 4                | 3.5~3.8 | 2.8~3.2              | 1.9~2.7     |

| Modulus (Gpa)               | 55~70            | ~50     | 10~20                | 3~10        |

| Hardness (GPa)              | 3.5              | 3.36    | 2.5~1.2              | 0.3~1.0     |

| CTE (ppm/K)                 | 0.6              | ~0.6    | 1~5                  | 10~18       |

| Thermal Conductivity (W/mK) | 1.0              | 1.0     | ~0.8                 | 0.26        |

| Porosity (%)                | NA               | NA      | <10                  | 25~50       |

| Average Pore Size (nm)      | NA               | NA      | <1.0                 | 2.0~10      |

| Breakdown Filed (MV/cm)     | >10              | >10     | 8~10                 | <8          |

*Low- dielectrics have been used for < 100 nm nodes. Reliability issues with very low k-dielectrics*

<sup>[1]</sup>C. K. Hu and J. M. E. Harper, Copper Interconnections and Reliability, Mater. Chem. Phys., vol. 52, p. 5-16, 1998.

\*from ancient sword making technique in Damascus, Syria

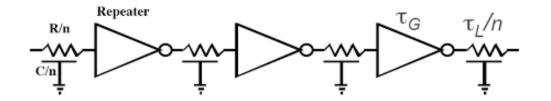

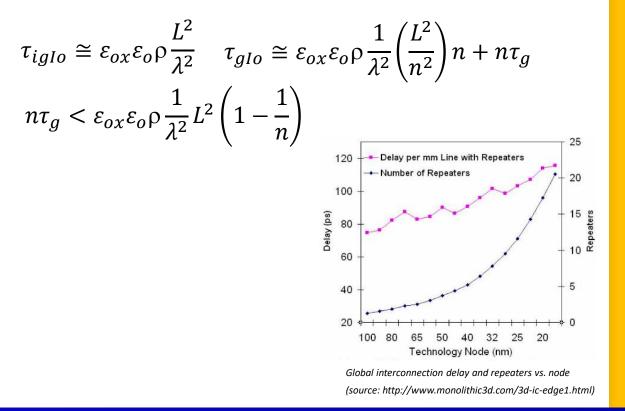

- Another way to reduce the interconnect delay is to use pass transistors (or repeaters)

- A long interconnect L is broken into n shorter lines, with the delay of each section reduced quadratically

- A small repeaters' delay  $\tau_g$  reduces the global delay  $\tau_{igIo}$

- The repeater solution increases the occupied area and the power consumption

A long interconnect line **L** is broken into **n** segments, each of length **L/n**

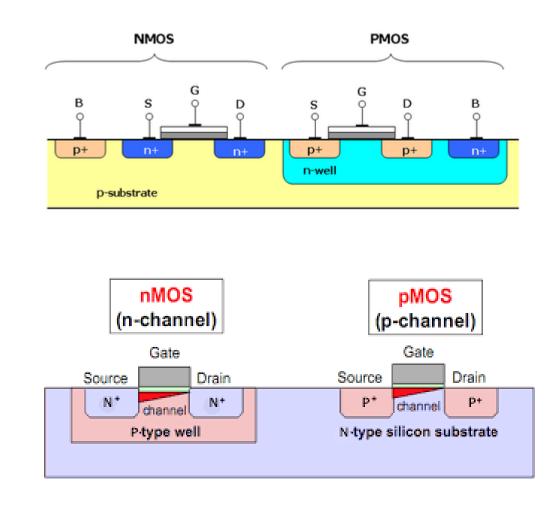

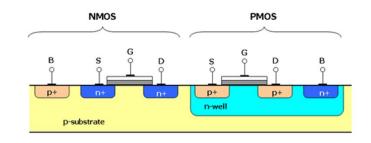

- Very often standard silicon wafers are P type and devices, including MOS transistors, are implemented in them

- This stems from the fact that NMOS are intrinsically faster than PMOS (e<sup>-</sup> mobility higher than h<sup>+</sup>)

- Fastest NMOS is obtained from high resistivity (low doping) P substrate rather than lower resistivity (higher doping) P well

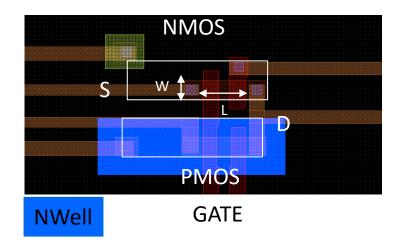

• In **digital circuits**, the transistors are normally designed with minimum size, to increase density of functions/storage /area

• In **analog circuits** a large **form factor**  $\beta$  = W/L is required, to increase the transcoductance  $g_m$

$$I_{D,sat} = \frac{\mu_p \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_T)^2$$

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} = \mu C_o \frac{W}{L} (V_{GS} - V_T)$$

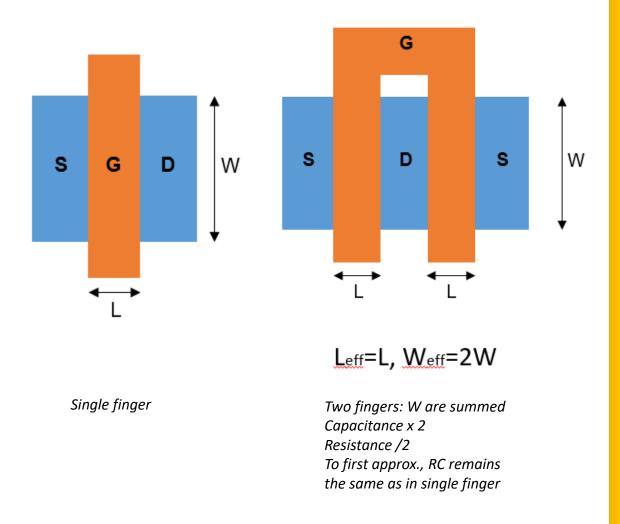

• In the layout of **analog transistors** the form factor is crucial as it determines  $g_m$  (straight structures preferable)

- However, a big value of W might increase Gate resistance/capacitance

- Special layout issues in analog design:

- multi-finger structure

• Multi finger structures decrease the Gate resistance but increase the parasitic effects (drain-gate coupling, gate to substrate)

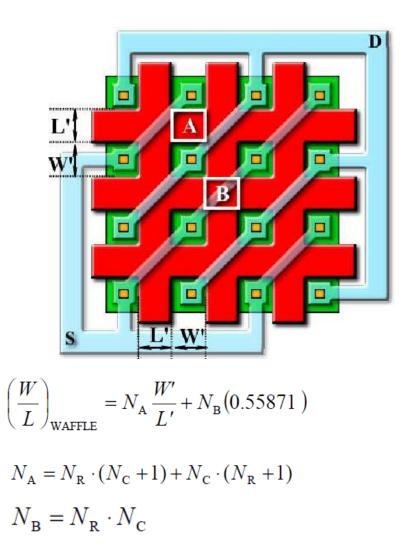

• Special structure (Waffle structure) used for RF CMOS applications

P. Vacula 1,2, M. Husák, M. 2013 Waffle MOS channel aspect ratio calculation with Schwarz-Christoffel Transformation

- Typical figures of CMOS process vs. size

- Scaling down does not imply better device characteristics per se

| CMOS Tech. min. size L                    | 180   | 130  | 90 nm | 65 nm | n 45 nm |

|-------------------------------------------|-------|------|-------|-------|---------|

|                                           | nm    | nm   |       |       |         |

| V <sub>DD</sub> (V)                       | 1.8   | 1.2  | 1.0   | 0.9   | 0.8     |

| $g_m (mS/\mu m)$                          | 0.55  | 0.85 | 1.01  | 1.45  | 1.65    |

| $A_{v} = g_{m}/g_{ds} \left( V/V \right)$ | 19.5  | 13.1 | 8.5   | 7.8   | 7.1     |

| $C_{GS}$ (fF/ $\mu$ m)                    | 1.37  | 1.06 | 0.82  | 0.55  | 0.45    |

| $C_{GD}$ (fF/ $\mu$ m)                    | 0.45  | 0.42 | 0.39  | 0.34  | 0.31    |

| f <sub>T</sub> (GHz)                      | 50    | 90   | 128   | 160   | 226     |

| NF <sub>min</sub> (dB)*                   | > 0.5 | 0.5  | 0.33  | 0.2   | < 0.2   |

\*Estimated at 2 GHz for the NMOS devices in [2].

| PARAMETER                   | 0.8µm |      | 05µm |      | 025µm |      | 0.18µm |      |

|-----------------------------|-------|------|------|------|-------|------|--------|------|

|                             | NMOS  | PMOS | NMOS | PMOS | NMOS  | PMOS | NMOS   | PMOS |

| t <sub>ox</sub> (nm)        | 15    | 15   | 9    | 9    | 6     | 6    | 4      | 4    |

| $C_{OX}(fF/\mu m^2)$        | 2.3   | 2.3  | 3.8  | 3.8  | 5.8   | 5.8  | 8.6    | 8.6  |

| $\mu(cm^2/V.S)$             | 550   | 250  | 500  | 180  | 460   | 160  | 450    | 100  |

| $\mu C_{\rm OX}(\mu A/V^2)$ | 127   | 58   | 190  | 68   | 267   | 93   | 387    | 86   |

| $V_t(V)$                    | .7    | 7    | .7   | 8    | .43   | 62   | .48    | 45   |

| $V_{DD}(V)$                 | 5     | 5    | 3.3  | 3.3  | 2.5   | 2.5  | 1.8    | 1.8  |

| $V'_{A}(V \mid \mu m)$      | 25    | 20   | 20   | 10   | 5     | 6    | 5      | 6    |

| $C_{ov}(fF \mid \mu m)$     | .2    | .2   | .4   | .4   | .3    | .3   | .37    | .33  |

- Integrated **Capacitors** are normally obtained by structures close to the silicon substrate

- Three type of capacitors:

- MOS (Metal Oxide Semiconductor)

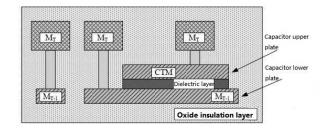

- MiM (Metal Insulator Metal)

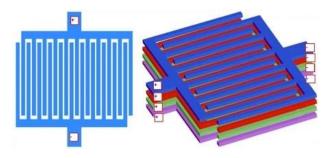

- **MoM** (<u>Metal Oxide Metal</u>) use interdigitated capacitors formed by metal layers

MOS capacitor: capacitance values changes with voltage, small area

**MIM** use different layers of metal and interposed dielectric to form a capacitor. Similar to plate capacitor, good stability but require additional masks

*MOM* use interdigitated capacitors formed by metal connections, placed in close proximity – preferred choice for advanced CMOS, also no additional mask required

- Typical values of capacitance

- Typical dielectric layers are SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>

- Use of high k materials is common in more advanced CMOS technologies

| PARAMETER                 | 0.8µm |      | 05µm |      | 025 <i>µm</i> |      | 0.18µm |      |

|---------------------------|-------|------|------|------|---------------|------|--------|------|

|                           | NMOS  | PMOS | NMOS | PMOS | NMOS          | PMOS | NMOS   | PMOS |

| t <sub>ox</sub> (nm)      | 15    | 15   | 9    | 9    | 6             | 6    | 4      | 4    |

| $C_{OX}(fF \mid \mu m^2)$ | 2.3   | 2.3  | 3.8  | 3.8  | 5.8           | 5.8  | 8.6    | 8.6  |

$$t_{ox} = 4 nm$$

$$= \frac{\varepsilon_0 \varepsilon_r}{t_{ox}} WL$$

$$C = 8.6 \, fF/\mu m^2$$

С

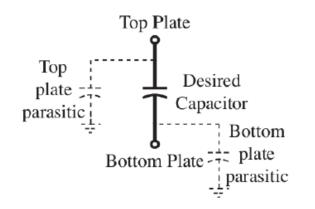

MIM/MOMs parasitic

$$C_{t,p} = 0.1 \% C$$

$C_{b,p} = 1 \% C$

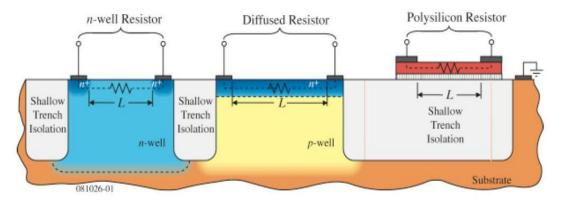

- Integrated **Resistors** are normally obtained by thin strips of resistive layers

- Insulation from surrounding achieved by oxide layers or reversed biased junctions

# Resistors

- · Diffused and/or implanted resistors.

- Well resistors.

- Polysilicon resistors.

- Metal resistors.

- Thin film resistors

Nwell:  $\rho_{\bullet} \sim 1 \ k\Omega / \bullet$ Poly:  $\rho_{\bullet} \sim 10 \ \Omega / \bullet$ Metallic:  $\rho_{\bullet} \sim 0.1 \ \Omega / \bullet$   $R = \rho_{\bullet} \frac{L}{W}$

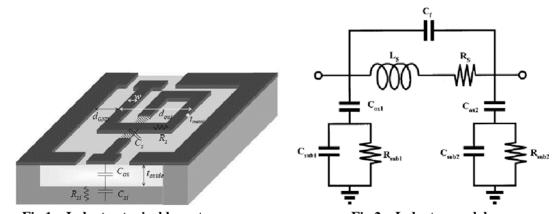

- Integrated **Inductors** are obtained by using different layouts of metal layers

- Used in some RF CMOS applications

Fig 1 – Inductor typical layout

Fig 2 – Inductor model

Yishay, Roee Ben et al. "High performance MEMS 0.18µm RF- CMOS inductors." 2008 IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems (2008): 1-7.

E.G. Villani, et al., A monolithic 180 nm CMOS dosimeter for In Vivo Dosimetry medical application, Radiation Measurements, Volume 71, 2014, Pages 389-391, ISSN 1350-4487,https://doi.org/10.1016/j.radmeas.2014.07.007.

#### Circuits and layout I

# Thank you

giulio.villani@stfc.ac.uk

- Layouts and interconnects in IC

- FEOL and BEOL different characteristics

- Interconnect delays and ways to mitigate them

- Transistors layouts in IC

- Passive components layouts in IC