# All-Silicon Module: Belle II and Beyond

$\triangleright$  The PXD Module at Belle II

$\triangleright$  Outlook – the way forward

Ladislav Andricek

for the team at the Semiconductor Laboratory of the Max Planck Society

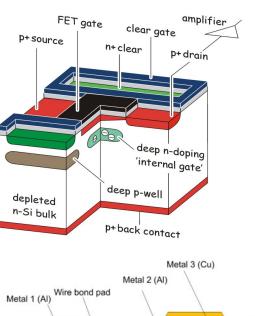

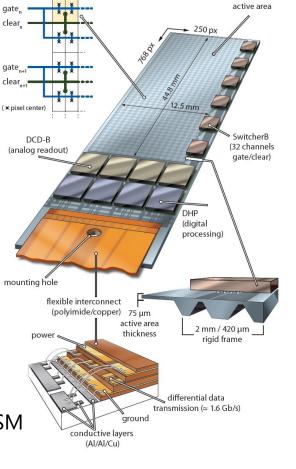

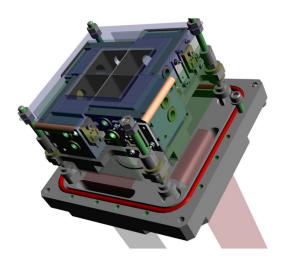

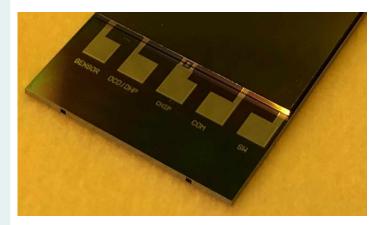

# the DEPFET all-silicon module for Belle II PXD

clear

( × pixel center)

DCD-B

(analog readout)

mounting hole

flexible interconnect (polyimide/copper) 75 um

active area

thickness

around

conductive lavers

(Al/Al/Cu)

Solder

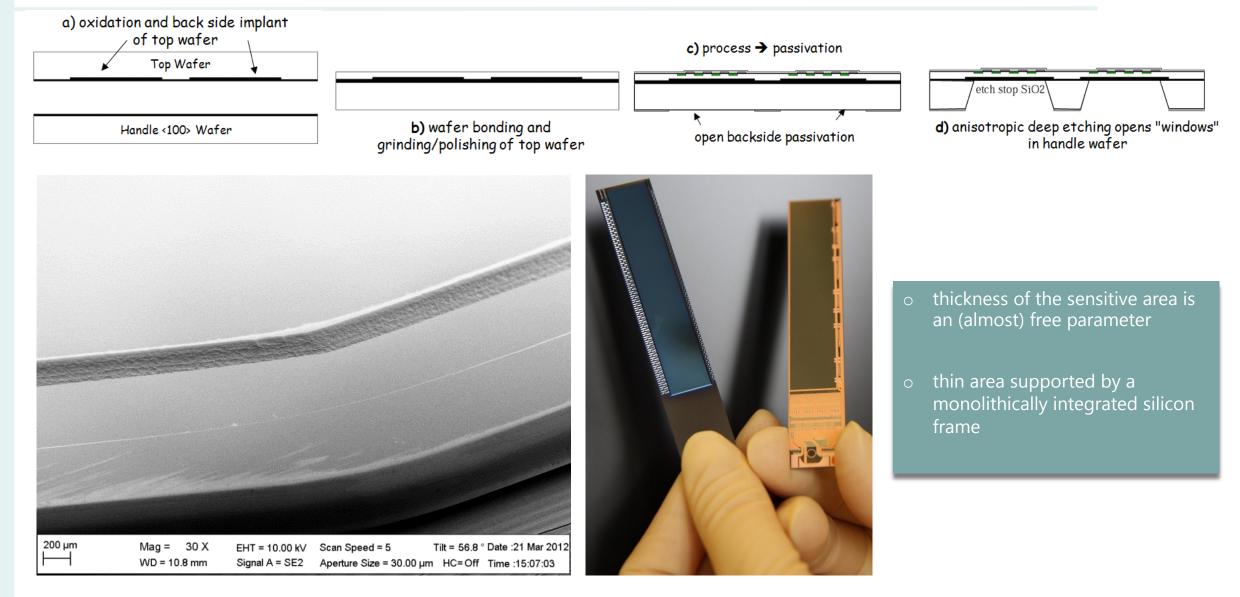

$\triangleright$  module design starts on wafer level

- $\triangleright$  module is one piece of silicon

- Sensitive area (APS) ╘

- High density interconnect (HDI) ╘

- $\triangleright$  HDI as board for non-sensor parts

- UMC 180, TSMC 65, IBM/AMS/TSI 180

- Passive components ╘

- On-module solder interconnect  $\rightarrow$

- Off-module interconnect with flex  $\triangleright$

- Solder and wire bonds L.

▷ "MCM-D", "2.5 D", "SoC" ... We call it ASM

#### All-Silicon Module

Thin pixel array operated in "rolling shutter" mode, 20µs/f  $\triangleright$

differential data transmission (≈ 1.6 Gb/s)

(digital

processing)

2 mm / 420 µm

rigid frame

Only 4/768 rows active a time  $\rightarrow$  low power in active area ╘

active area

witcherB

(32 channels

gate/clear)

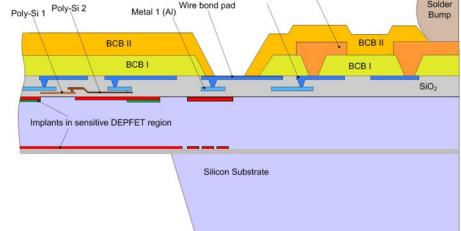

# the DEPFET all-silicon module for Belle II PXD

$\triangleright$  module design starts on wafer level

- $\triangleright$  module is one piece of silicon

- $\rightarrow$  Sensitive area (APS)

- $\mapsto$  High density interconnect (HDI)

- $\triangleright$  HDI as board for non-sensor parts

- → UMC 180, TSMC 65, IBM/AMS/TSI 180

- └→ Passive components

- $\mapsto$  On-module solder interconnect

- $\triangleright$  Off-module interconnect with flex

- $\rightarrow$  Solder and wire bonds

▷ "MCM-D", "2.5 D", "SoC" ... We call it ASM

#### All-Silicon Module

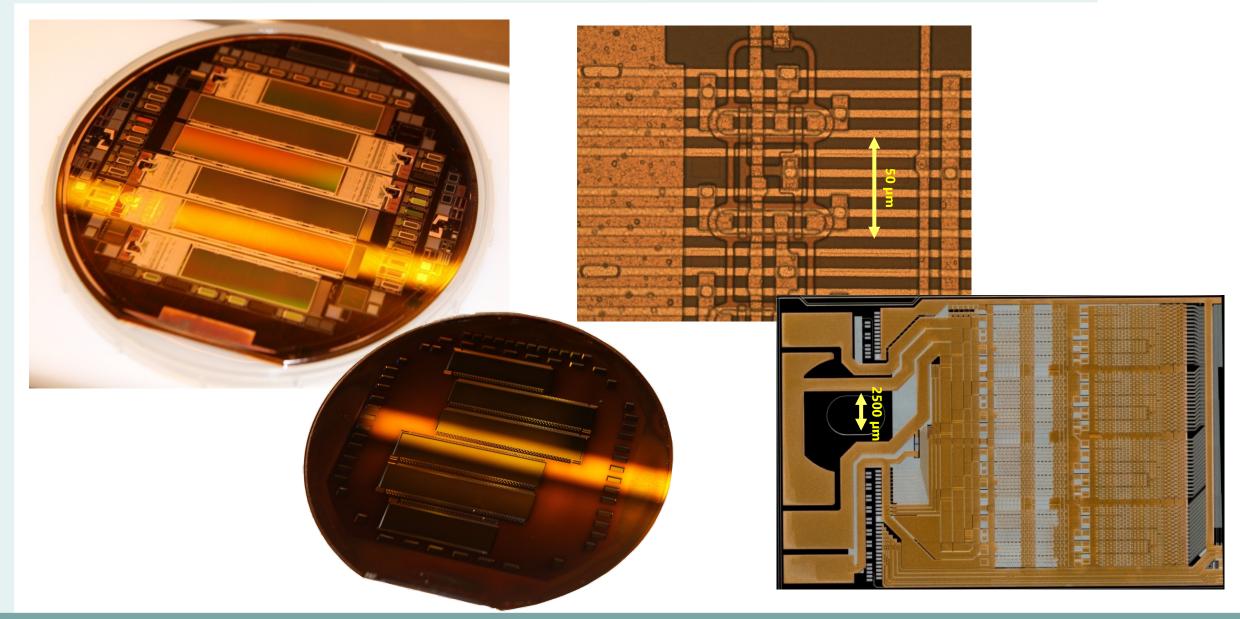

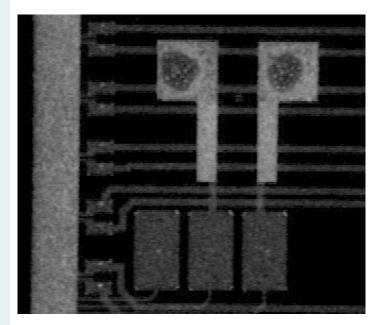

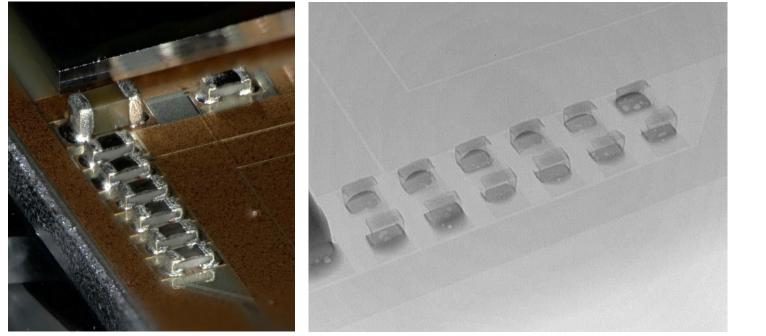

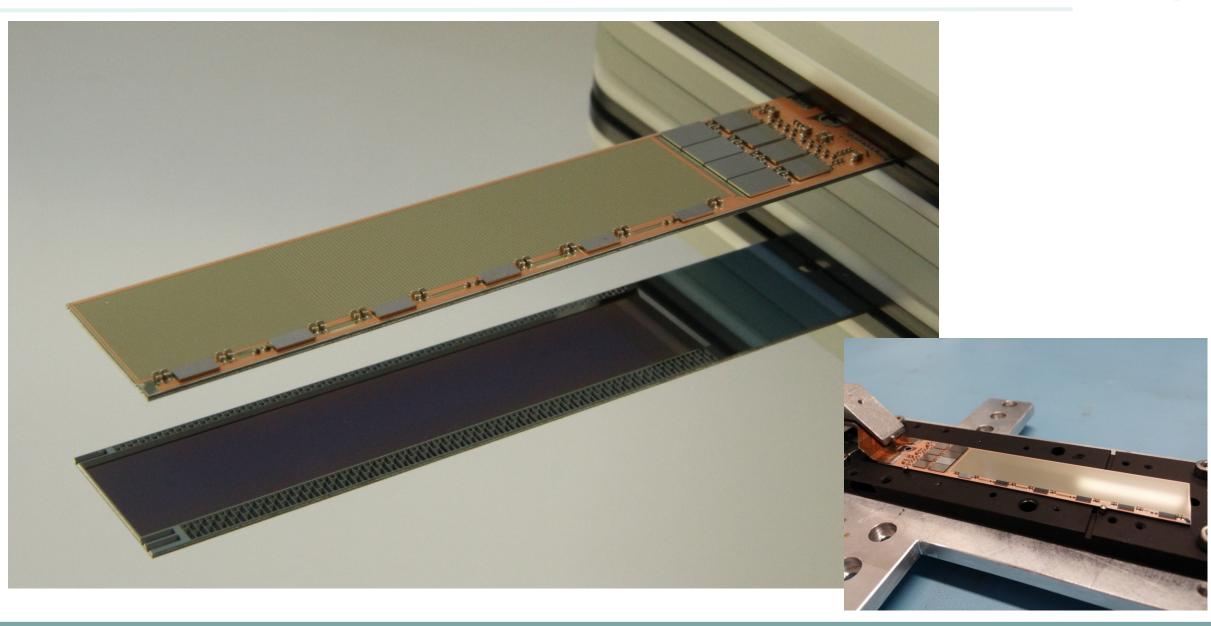

x-ray picture of fully assembled module 0.21% of X<sub>0</sub>

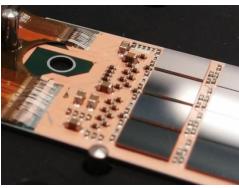

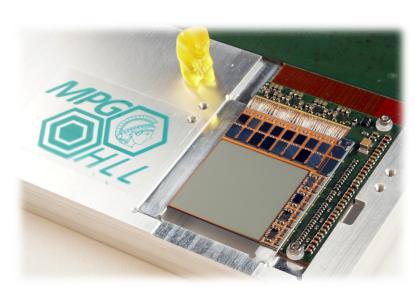

## module assembly overview

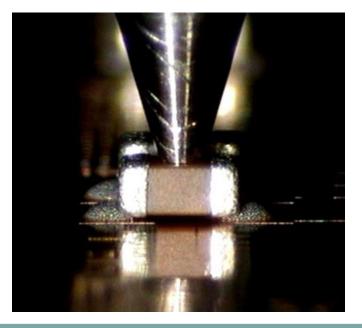

Flip Chip of ASICs (~240°C):

- Bumped ASICs have (almost) the same solder balls (SnAg)

- → DHP bumping at TSMC, DCD bumping via Europractice

- Fraunhofer SWB bumping on chip and wafer level as post-process

- Bump bonding on customized support plates

- Initially at IZM, then at HLL  $\triangleright$

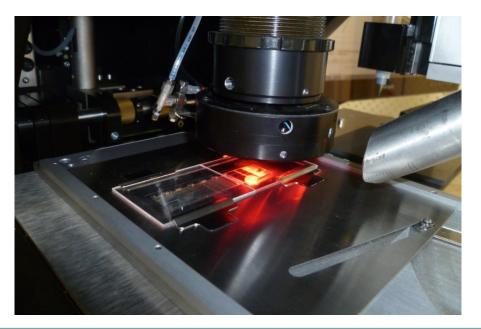

- Passive components (termination resistors, decoupling caps)  $\triangleright$

- Dispense solder paste, pick, place and reflow  $\triangleright$

- Solder paste printing on kapton, vapor phase soldering

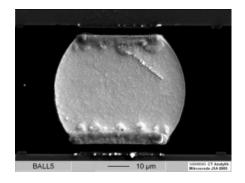

- Wire-bond, wedge-wedge, 32 µm Al bond wires  $\triangleright$

- Each module has about 100 capacitors and resistors of various formats (0402, 0201, 01005)

- → Very small footprint, no screen printing of solder possible, delicate handling of module ...

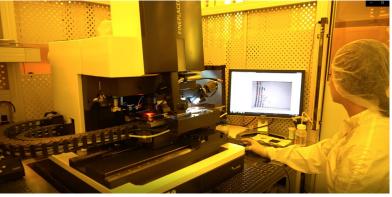

- → Adapted SMD technology installed at HLL

- ▷ Automated micro assembly tool, the same as for flip-chip

- → Additional dispense system

#### $\triangleright$ Process flow

└→ Condition module, dispense solder, place SMD parts, reflow in process chamber

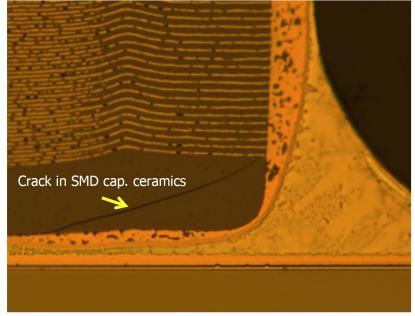

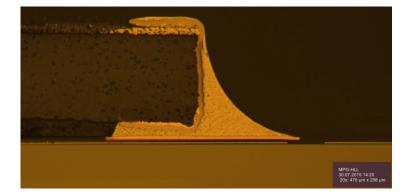

### Process qualification

Extensive tests and QC/QA: shear tests, cross section, metallurgy, thermal stress tests ...

Optimization, fine tuning, reliability ...  $\rightarrow$  need higher quality SMDs

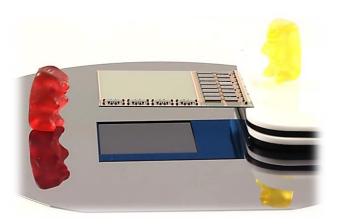

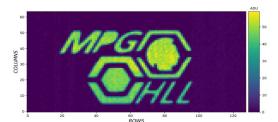

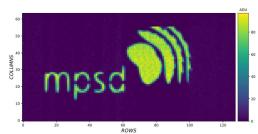

- ▷ Application of the ASM concept for a different application direct electron detection in TEMs

- $\mapsto$  Sensitive DEPFET area thinned to 30  $\mu$ m and 50  $\mu$ m

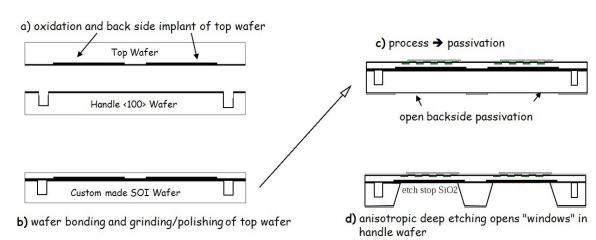

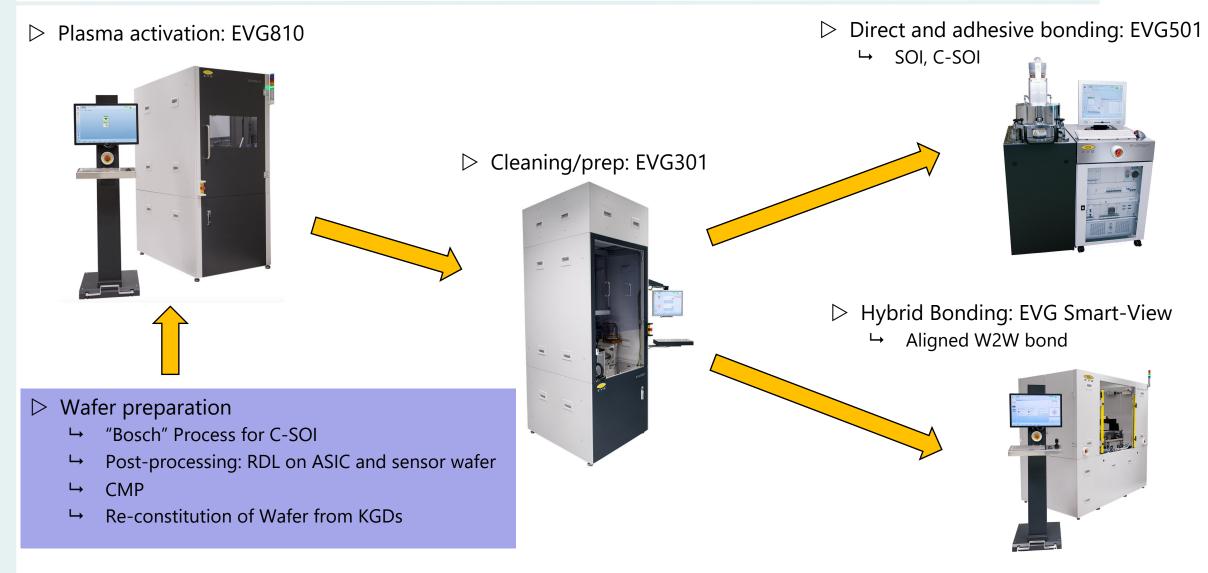

▷ Designed for DEPFET sensors for HEP applications

- $\triangleright$  Back side implant first, etch channels in handle wafer

- ▷ Wafer bonding/SOI fabrication, processing of wafers with cavities (C-SOI)

- ▷ C-SOI wafer design and fabrication specific for each project

- ▷ More flexibility, if cavities and bonding are introduced in post-processing steps

UUU

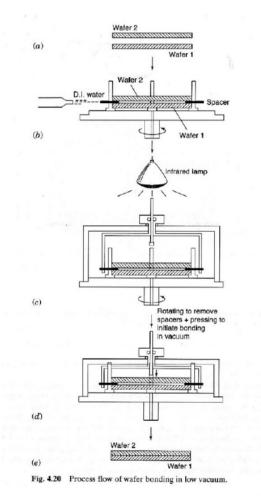

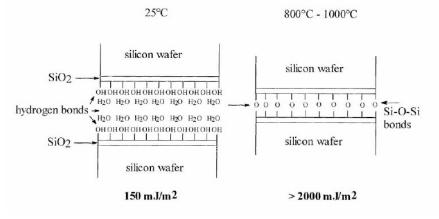

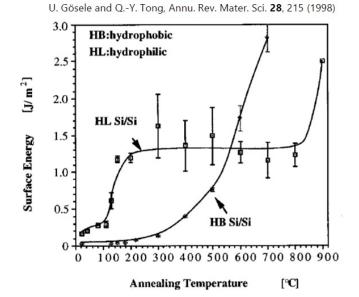

#### Direct Wafer Bonding - reminder

- $\triangleright$  Relatively simple process

- → Needs just clean, (very) smooth surfaces

- ▷ High Temp. for good bonding (>2 J/m<sup>2</sup>)  $\rightarrow$  not BEOL compatible

- bonding in UHV or with prior plasma treatment reduces annealing temp. well below 400°C

"Plasma Activation – An Enabling Technology for Wafer Bonding",

Eric F. Pabo, EV Group, Semicon West 2010

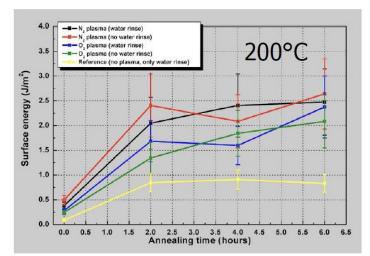

# Low temperature bonding tests at EVG, Austria

- ▷ 1<sup>st</sup> DWB tests at equipment manufacturer EVG very successful

- → Focused on bonding of implanted oxide, tests still yielded surface energies of about 1 J/cm<sup>2</sup>

- ▷ 2<sup>nd</sup> round to optimize surface energy at low annealing temperature

- → Twelve 6" DSP FZ wafer pairs prepared at HLL (oxidation, cleaning)

- → six pairs as path finder for best parameter set (plasma/atmosphere/temperature)

- → six pairs to confirm and increase statistics

Plasma Activation

• Activation of both wafer surfaces in the LTM of the Gemini system

Single Wafer Cleaning

• DIW cleaning with JetNozzle in the CLM of the Gemini system

Pre-Bonding

• Bonding with center pin in the Pre-bond module of the Gemini system (ambient conditions or vacuum) or in an EVG301 system (ambient conditions)

Thermal

• Annealing of the bonded wafers in an EVG5xx bond module

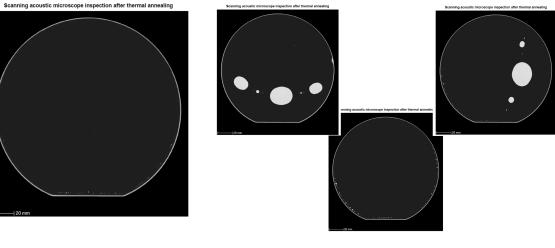

$\triangleright$  9/12 bonds look like this

3/12 bonds with edge voids and larger area voids due to particles or surface quality variations

▷ Result: reliable, reproducible, and wide process window with T<300 °C and surface energy > 2 J/cm<sup>2</sup>

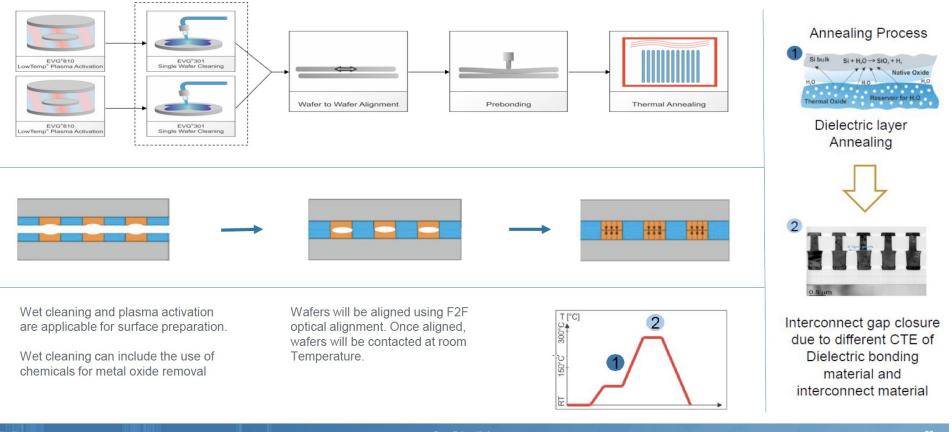

### Wafer bonding – more general

- ▷ Very versatile basic process step for (heterogenous) integration

- → Wafer-to-wafer or collective chip-to-wafer bonding

- → Si to Si, Si to other materials like compound semiconductors, e.g.

- → "Hybrid bonding": embedded Cu-Cu bonds for electrical interconnections

Confidential

www.EVGroup.com

▷ Contract with tool manufacturer for equipment supply and process support in preparation

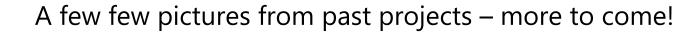

- Based on the experience with the all-silicon module for Belle II PXD, the HLL is extending this technology to other applications

- → detectors for HEP, photon science in general, low-energy particle detection

- $\mapsto$  photonic applications, quantum computing

In Summary

- > The vision is heterogeneous integration of very different technologies on support silicon (active or passive)

- $\mapsto$  Sensor + CMOS + Photonics 2.5D and 3D integrated

- > Additional post-processing tools and technologies for 6" and 8" wafers are being installed in the new clean room

- $\mapsto$  ICP-DRIE, CMP (not presented here)

- ▷ Key technology is wafer bonding at BEOL compatible temperatures

- → Direct bonding, adhesive bonding

- → Hybrid bonding allowing for advanced fine-pitch vertical interconnection

Backup

# The way forward: **overview**

- ▷ Extend sputtering capability on existing sputter system

- → targets are easy to exchange

- $\rightarrow$   $\rightarrow$  new metals possible

- → replace 2/4 DC sputter guns with RF biased ones

- $\rightarrow$  sputtering of isolators (SiO2, Al2O3 .. )

- $\mapsto$  software upgrade for co-sputtering and reactive sputtering

- ▷ Improve lithography capability

- → Use of e-beam lithography system installed at MQV partners

- → HLL contribution: installation and qualification of required photo resist systems suitable for e-beam

- $\triangleright$  Extend structuring capability

- → Installation of ICP-DRIE for silicon

- $\mapsto$  TSV, Si wave guides

- $\triangleright$  Extend interconnect capabilities and post-processing of ASICs and/or PICs

- $\mapsto$  Install CMP of SiO2 and metals as preparation for wafer bonding

- → Install and W2W and C2W direct and hybrid bonding

- → Low temperature bonding <350 °C mandatory

# The way forward: ICP-DRIE "dry etching"

- > Oxford Instruments Estrelas System, single wafer etcher for up to 8" wafers

- $\mapsto$  Hook-up, process installation, and commissioning ongoing  $\rightarrow$  end of 2025

#### $\triangleright$ Main process modules

- → Deep Si etch ("Bosch Process")

- → TSV, fluidic channels, large area partial thinning of wafers, also as post-process option

- → "mixed gas" process

- → Shallow Si etching with very smooth side walls for Si wave guides

#### 3. Bosch: TSV etching

#### Advanced packaging applications

- + ~5% Si exposed on a 500  $\mu m$  thickness wafer

- Use SiO<sub>2</sub> as a stop layer

| Parameter                            | a                                              | b                                              |

|--------------------------------------|------------------------------------------------|------------------------------------------------|

| Process Chemistry                    | SF <sub>6</sub> -C <sub>4</sub> F <sub>8</sub> | SF <sub>6</sub> -C <sub>4</sub> F <sub>8</sub> |

| Wafer size (mm)                      | 150                                            | 200                                            |

| Exposed area (%)                     | 5                                              | 5                                              |

| Clamping method                      | ESC                                            | ESC                                            |

| Via size (µm)                        | 100                                            | 100                                            |

| Depth (µm)                           | 500                                            | 500                                            |

| Etch rate (µm/min)                   | > 7                                            | > 6                                            |

| Selectivity to PR mask               | > 70                                           | > 70                                           |

| Selectivity to SiO <sub>2</sub> mask | > 120                                          | > 120                                          |

| Profile control (°)                  | 90±1                                           | 90±1                                           |

| Bosch scallop (nm) (peak to peak)    | < 200                                          | < 200                                          |

| Uniformity within wafer (±/%)        | < 3                                            | < 3                                            |

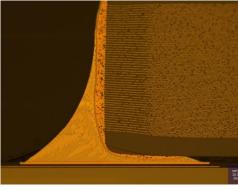

#### 4. Mixed gas Si etching

#### Si waveguide applications

- SOI wafers

- Etch a top Si layer of 220nm thickness

- Smooth sidewalls and accurate control

| Parameter                            | a                                              | b                                              |

|--------------------------------------|------------------------------------------------|------------------------------------------------|

| Process Chemistry                    | SF <sub>6</sub> -C <sub>4</sub> F <sub>8</sub> | SF <sub>6</sub> -C <sub>4</sub> F <sub>8</sub> |

| Wafer size (mm)                      | 150                                            | 200                                            |

| Exposed area (%)                     | 25                                             | 25                                             |

| Clamping method                      | ESC                                            | ESC                                            |

| Trench size (µm)                     | 5                                              | 5                                              |

| Depth (nm)                           | 220                                            | 220                                            |

| Etch rate (nm/min)                   | > 50                                           | > 40                                           |

| Selectivity to PR mask               | > 1.5                                          | > 1.5                                          |

| Selectivity to SiO <sub>2</sub> mask | > 2.5                                          | > 2.5                                          |

| Profile control (°)                  | 90±2                                           | 90±2                                           |

| Added sidewall roughness (nm)        | < 2 (rms)                                      | < 2 (rms)                                      |

| Uniformity within wafer (±/%)        | < 5                                            | < 5                                            |

© Oxford Instruments 2023

Confidential Z.R. provides to MPG HLL, Feb 2023

© Oxford Instruments 2023

Confidential Z.R. provides to MPG HLL, Feb 2023

5