# Introduction to FPGA, FINN and Brevitas

Dr. Mario Ruiz AMD University Program

#### **AUP** Vision

Empower academics with AMD technology to enhance teaching and learning experiences and advance state-of-the-art research.

#### **Our Team**

Dedicated world-wide technical team

Supporting High Performance and Adaptive Compute

25+ years experience working with academia

#### What We Offer

Research Programs

Donation Program

#### Teaching Resources

#### Training

Academic Solutions

Support

#### **HACCs: Heterogeneous Accelerated Compute Clusters**

together we advance\_

5

### **HACC Adaptive Computing Hardware**

HACC hardware consists of:

- Compute and Alveo<sup>™</sup> nodes (initially U250 and U280 with HBM)

- Latest heterogeneous nodes (SMC 4124GS) include:

- 2 EPYC<sup>™</sup> 3rd generation CPUs

- 4 AMD Instinct<sup>™</sup> MI210 GPUs

- 2 Alveo U55C FPGA with HBM

- 2 VCK5000 Versal Adaptive SoC with AIEs

- Run-time via AMD ROCm™, XRT

- SW development via HIP, Vitis, frameworks

- 100G network

- Community hub for researchers

- Support from in-house AMD research groups

- Reproducible results & experiments

#### **Contact Us**

**Email us:**

aup@amd.com

#### Visit our website to:

- Discover our research programs

- Access educational resources

- Submit a donation request

- Find training & other events

AMD | together we advance\_ × + S www.amd.com/universit Q Products Downloads & Suppor Shop **AMD University Program** Educator, researcher and student hub for AMD resources, program and news Educators FAQ Contact Us Researchers Students Events

www.amd.com/AUP

## What is Adaptive Computing?

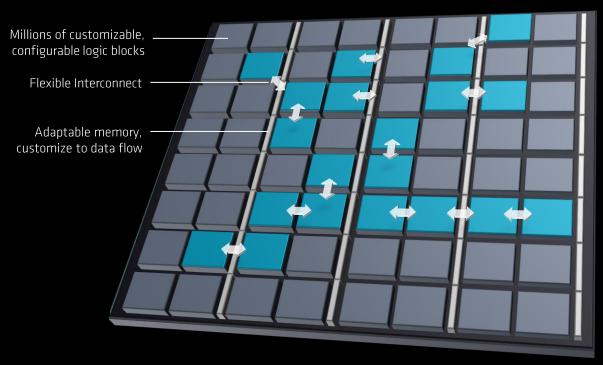

Adaptive Hardware ("FPGA") Conceptual Representation

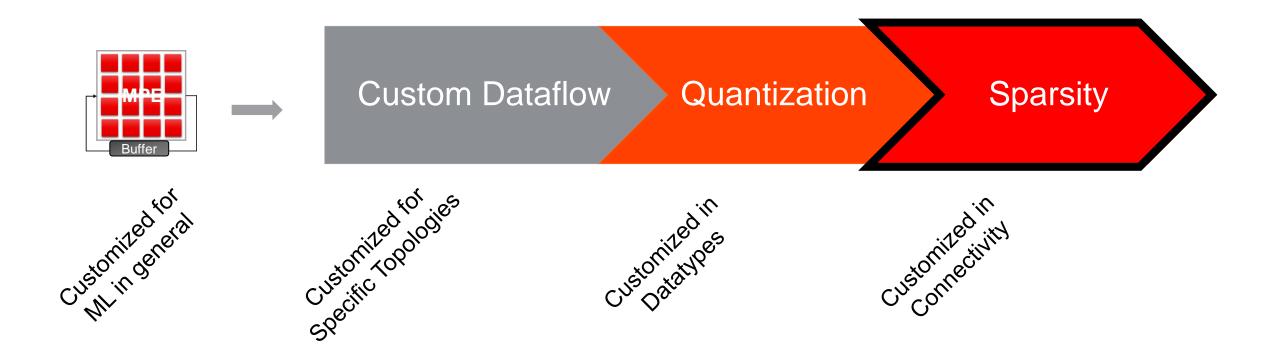

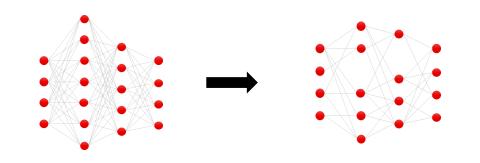

#### **Optimize for the Workload**

Domain-Specific Architecture for your exact requirements, accelerating the whole application

#### Adapt as Algorithms Change

Re-implement the silicon after deployment, adapting to evolving use cases

#### **Accelerate Pace of Innovation**

Keep pace with fast moving markets and rapid innovation cycles, e.g., AI algorithms

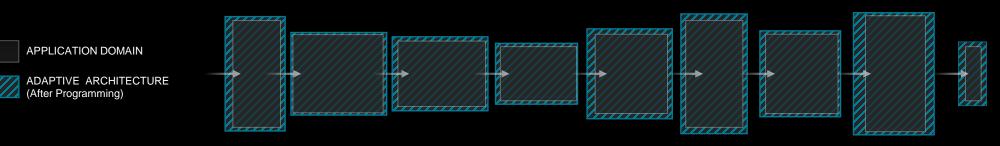

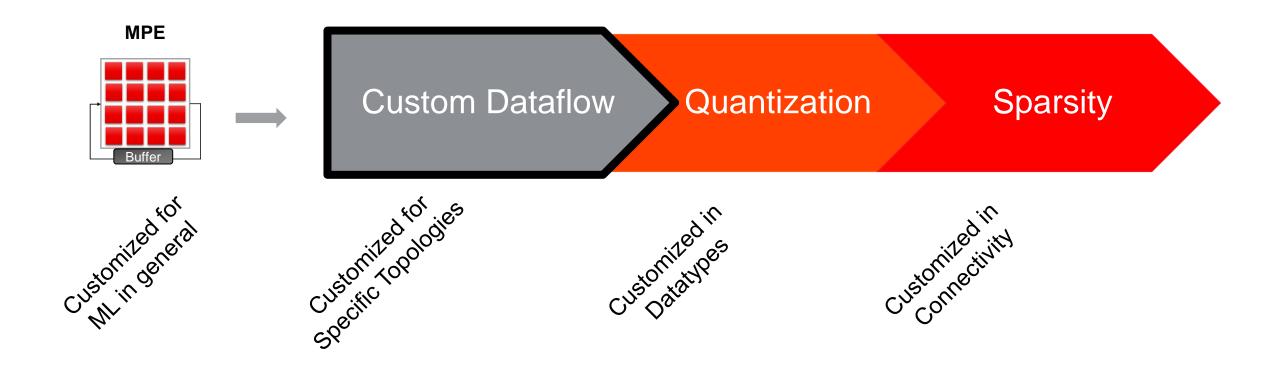

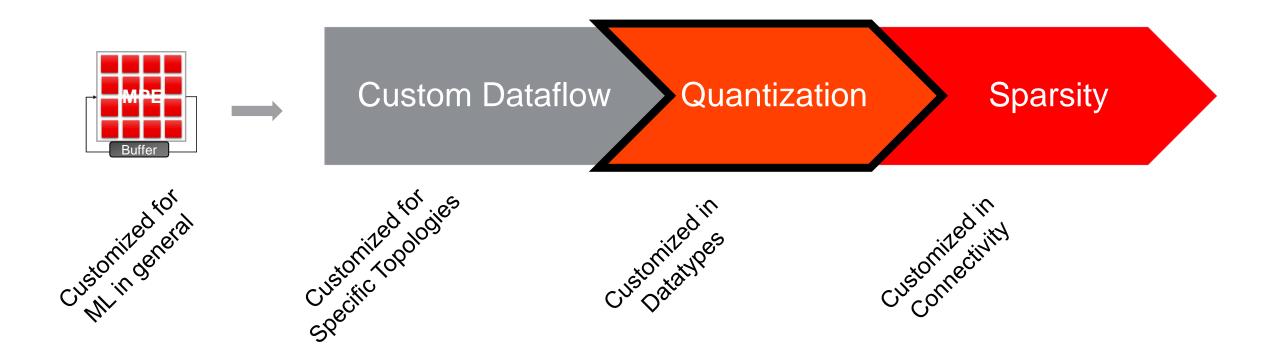

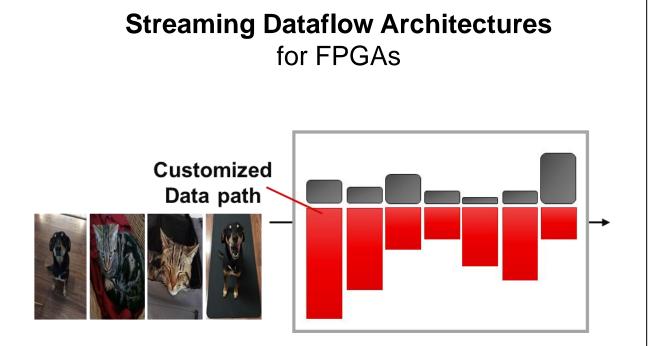

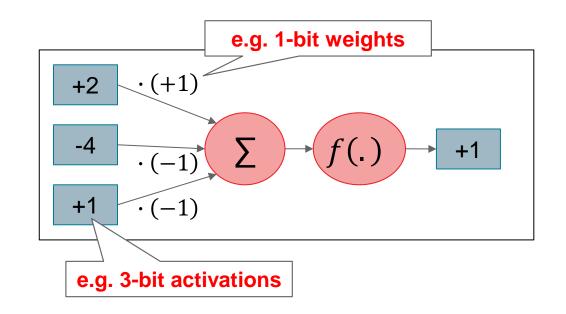

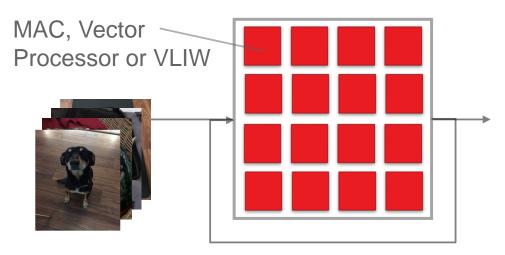

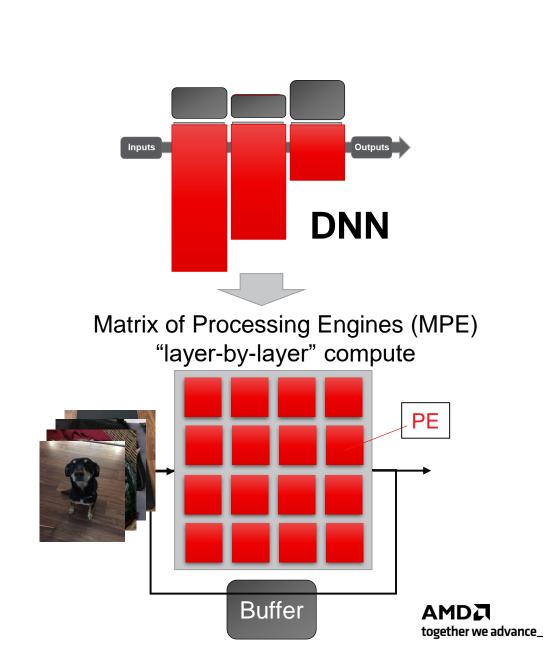

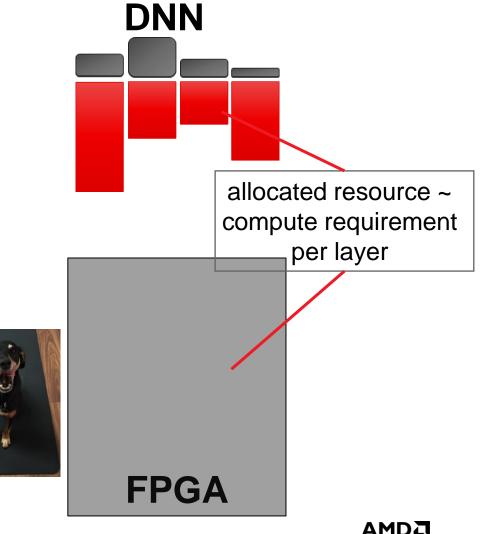

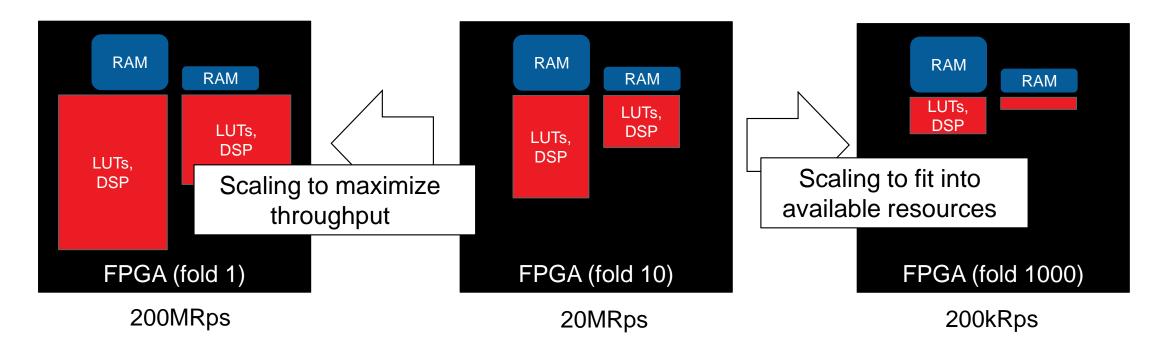

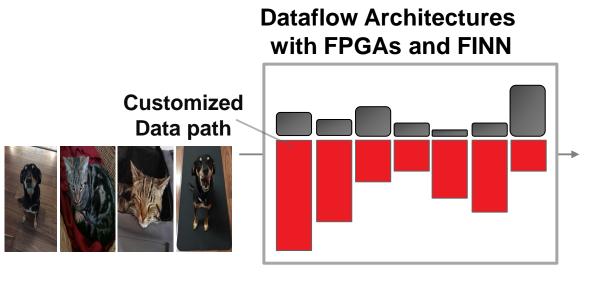

Matching the Architecture to the Application

Custom Data Flow, Custom Memory Hierarchy, Custom Precision

AMD together we advance\_

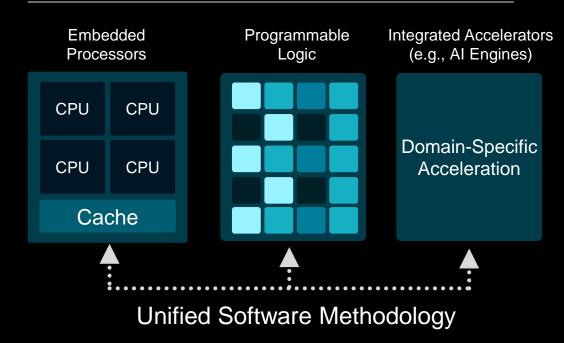

#### **Evolution to Heterogeneous Platforms**

- From FPGAs to adaptive SoCs → matching the engine to the workload

- Balancing diverse technologies for domain-specific requirements

#### **Domain Specific Optimization**

[Public]

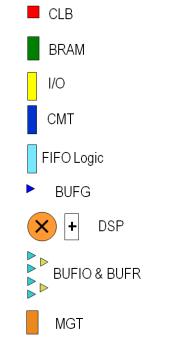

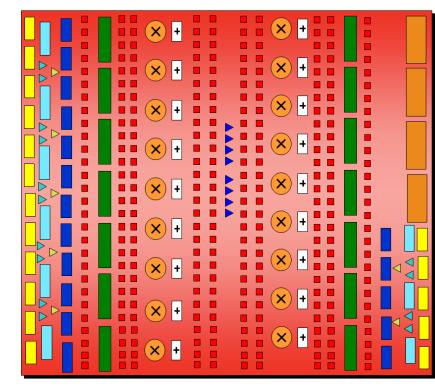

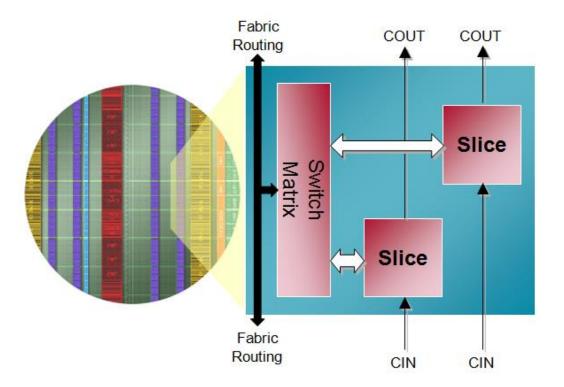

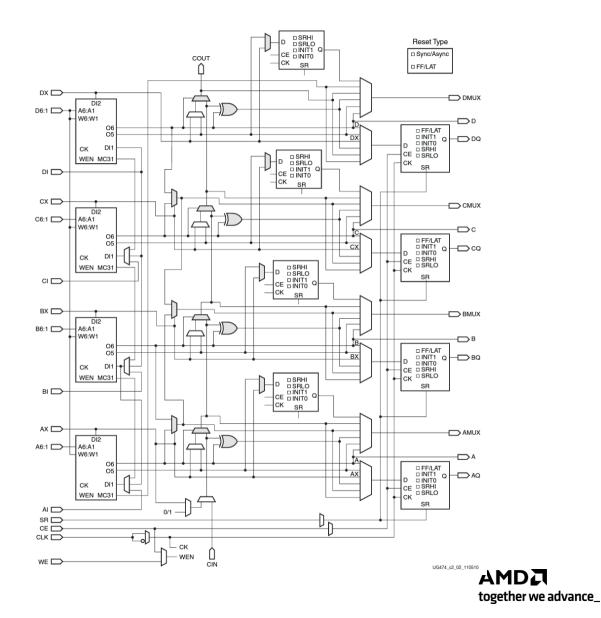

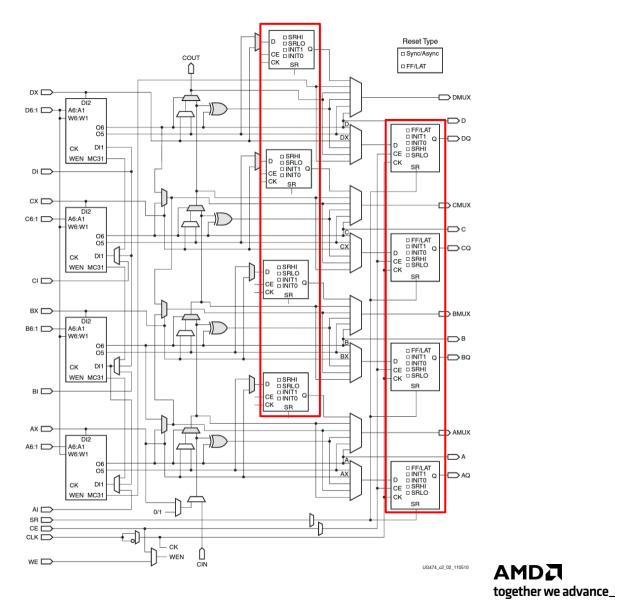

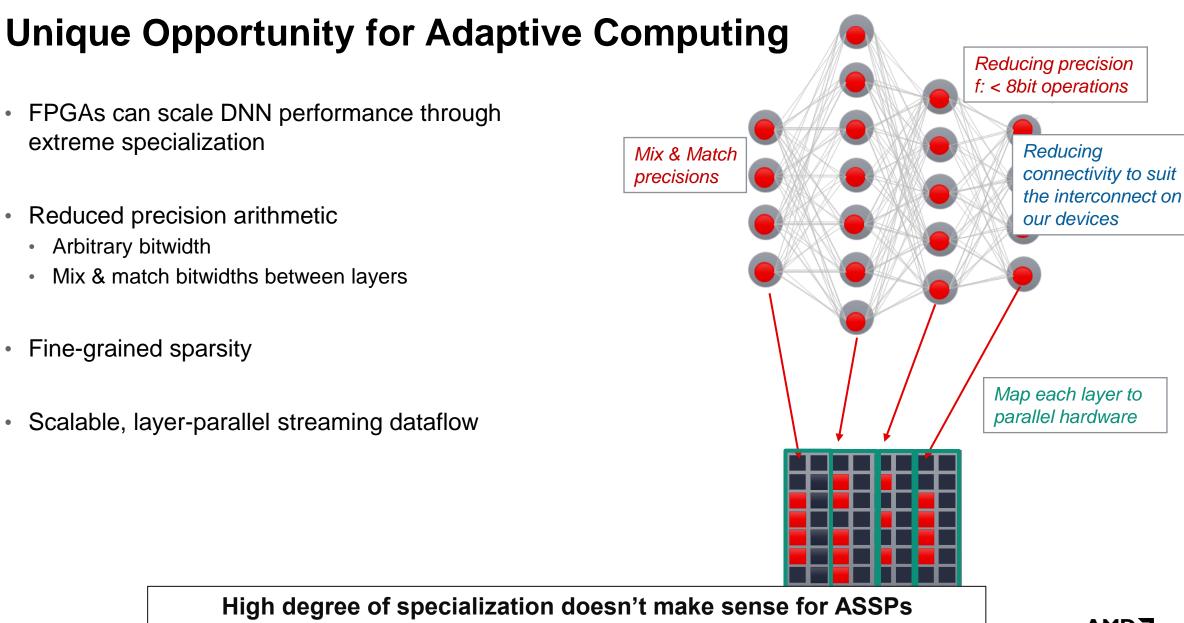

#### Field Programmable Gate Array (FPGA)

- Semiconductor devices

- Programmed and reprogrammed by a user

- Configuration attributes manipulated after manufacturing

- Matrix of configurable logic blocks (CLBs)

- Dedicated specialized logic

- Flexible programmable interconnects

- Ideal fit for many different workloads

- Massive parallelism

- Hardware adaptability is a unique differentiator from CPUs and GPUs

- Invented in 1985

#### Applications

- Automotive

- Broadcast & Pro AV

- Consumer Electronics

- Data Center

- High Performance Computing and Data Storage

- Industrial

- Medical

- Video & Image Processing

- Wired Communications

- Wireless Communications

[Public]

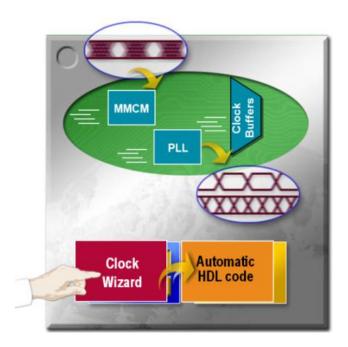

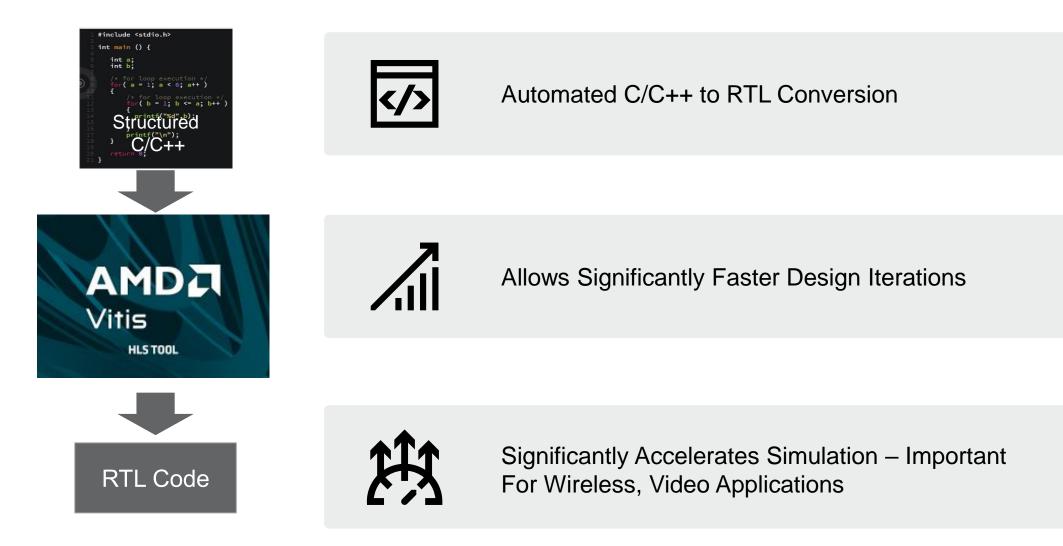

# **Core Adaptable Hardware Technologies**

|                                                                   | Provide and a second se | BCIE 8     DDU     HBM     Allwards     6004     700       BCIE 9     DDU     HBM     Allwards     700     700 |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGAs                                                             | SoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Adaptive SoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| From high-bandwidth<br>connectivity to massive<br>compute engines | Multi-processing subsystem<br>with Arm <sup>®</sup> cores and integrated<br>FPGA logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Adaptive Compute Acceleration<br>Platforms for any application,<br>any developer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AMDA AMDA AMDA AMDA<br>Spartan Artix Kintex Virtex                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AMDA<br>VERSAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **Three Ages of FPGAs**

- A Retrospective on the First Thirty Years of FPGA Technology

- S. M. Trimberger, "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology," in Proceedings of the IEEE, vol. 103, no. 3, pp. 318-331, March 2015, DOI: 10.1109/JPROC.2015.2392104

| INVITED FAFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                         | Trimberger: Three Ages of FPGAs                                                                                                | Trimberger: Three Ages of FPGAs                                                                                         |                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         | The disadvantage of the FPGA per-unit cost premium<br>over ASIC diminished over time as NRE costs became a                     | <br>3 macrocells                                                                                                        | the AND array grows with the square of the number of<br>inputs (more precisely, inputs times product terms). Pro-   |

| Three Ages of FPGAs: A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ă t                                                                                                                                     | larger fraction of the total cost of ownership of ASIC. The                                                                    |                                                                                                                         | cess scaling delivers more transistors with the square of the                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ASIC Crossover                                                                                                                          | dashed lines in Fig. 2 indicate the total cost at some process                                                                 |                                                                                                                         | shrink factor. However, the quadratic increase in the AND                                                           |

| Potrognoctive on the First Thirty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | point,<br>generation n+1                                                                                                                | node. The solid lines depict the situation at the next process<br>node, with increased NRE cost, but lower cost per chip, Both | Product terms                                                                                                           | array limits PALs to grow logic only linearly with the<br>shrink factor. PAL input and product-term lines are also  |

| Retrospective on the First Thirty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Crossover                                                                                                                               | FPGA and ASIC took advantage of lower cost manufacturing.                                                                      |                                                                                                                         | heavily loaded, so delay grows rapidly as size increases. A                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FPGA generation n                                                                                                                       | while ASIC NRE charges continued to climb, pushing the                                                                         |                                                                                                                         | PAL, like any memory of this type, has word lines and bit                                                           |

| Years of FPGA Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                         | crossover point higher. Eventually, the crossover point grew                                                                   |                                                                                                                         | lines that span the entire die. With every generation, the                                                          |

| 5/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Number of Units                                                                                                                         | so high that for the majority of customers, the number of<br>units no longer justified an ASIC. Custom silicon was war-        |                                                                                                                         | ratio of the drive of the programmed transistor to the<br>loading decreased. More inputs or product terms increased |

| This paper reflects on how Moore's Law has driven the design of FPGAs through                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fig. 2. FPGA versus ASIC Crossover Point. Graph shows total cost                                                                        | ranted only for very high performance or very high volume;                                                                     |                                                                                                                         | loading on those lines. Increasing transistor size to lower                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | versus number of units. FPGA lines are darker and start at the lower<br>left corner. With the adoption of the next process node (arrows | all others could use a programmable solution.                                                                                  | 2 Inputs                                                                                                                | resistance also raised total capacitance. To maintain speed,                                                        |

| hree epochs: the age of invention, the age of expansion, and the age of accumulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | from the earlier node in dashed lines to later node in solid lines).                                                                    | This insight, that Moore's Law [33] would eventually<br>propel FPGA capability to cover ASIC requirements, was a               | 2 inputs                                                                                                                | power consumption rose dramatically. Large PALs were<br>impractical in both area and performance. In response, in   |

| By Stephen M. (Steve) Trimberger, Fellow IEEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | the crossover point, indicated by the vertical dotted line, grew larger.                                                                | fundamental early insight in the programmable logic busi-                                                                      | Fig. 3. Generic PAL architecture.                                                                                       | the 1980s, Altera pioneered the Complex Programmable                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         | ness. Today, device cost is less of a driver in the FPGA                                                                       |                                                                                                                         | Logic Device (CPLD), composed of several PAL-type blocks                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol> <li>Age of Expansion 1992–1999;</li> </ol>                                                                                         | versus ASIC decision than performance, time-to-market,<br>power consumption, I/O capacity and other capabilities.              | B. FPGA Versus PAL                                                                                                      | with smaller crossbar connections among them. But FPGAs<br>had a more scalable solution,                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol><li>Age of Accumulation 2000–2007.</li></ol>                                                                                        | Many ASIC customers use older process technology,                                                                              | Programmable logic was well established before the                                                                      | The FPGA innovation was the elimination of the AND                                                                  |

| BSTRACT Since their introduction, field programmable gate 10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         | lowering their NRE cost, but reducing the per-chip cost                                                                        | FPGA. EPROM-programmed Programmable Array Logic                                                                         | array that provided the programmability. Instead, config-                                                           |

| rrays (FPGAs) have grown in capacity by more than a factor of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | II. PREAMBLE: WHAT WAS THE<br>BIG DEAL ABOUT FPGAs?                                                                                     | advantage.                                                                                                                     |                                                                                                                         | uration memory cells were distributed around the array to                                                           |

| 0 000 and in performance by a factor of 100. Cost and energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                         | Not only did FPGAs eliminate the up-front masking<br>charges and reduce inventory costs, but they also reduced                 | However, FPGAs had an architectural advantage. To un-<br>derstand the FPGA advantage, we first look at the simple       |                                                                                                                     |

| er operation have both decreased by more than a factor of 1000 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A. FPGA Versus ASIC                                                                                                                     | design costs by eliminating whole classes of design prob-                                                                      | programmable logic structures of these early 1980s de-                                                                  |                                                                                                                     |

| caling, but the FPGA story is much more complex than simple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                         | lems. These design problems included transistor-level de-                                                                      | vices. A PAL device, as depicted in Fig. 3, consists of a two-                                                          |                                                                                                                     |

| echnology scaling. Quantitative effects of Moore's Law have Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (ASIC) companies brought an amazing product to the<br>electronics market; the built-to-order custom integrated                          |                                                                                                                                | level logic structure [6], [38]. Inputs are shown entering at<br>the bottom. On the left side, a programmable AND array |                                                                                                                     |

| driven qualitative changes in FPGA architecture, applications 100 —Price Power 100 Price 100 Price 100 Price 100 Power 100 Pow | circuit. By the mid-1980s, dozens of companies were sell-                                                                               |                                                                                                                                | generates product terms, ANDS of any combination of the                                                                 |                                                                                                                     |

| ral distinct phases of development. These phases, termed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ing ASICs, and in the fierce competition, the winning at-                                                                               |                                                                                                                                | inputs and their inverses. A fixed on gate in the block at                                                              | AND array. Not every function was an output of the chip, so                                                         |