## EPF

## An Open-Source RISC-V-based GPGPU Accelerator for Machine Learning-based Edge Computing Applications

Simone Machetti, Pasquale Davide Schiavone, Giovanni Ansaloni, David Atienza

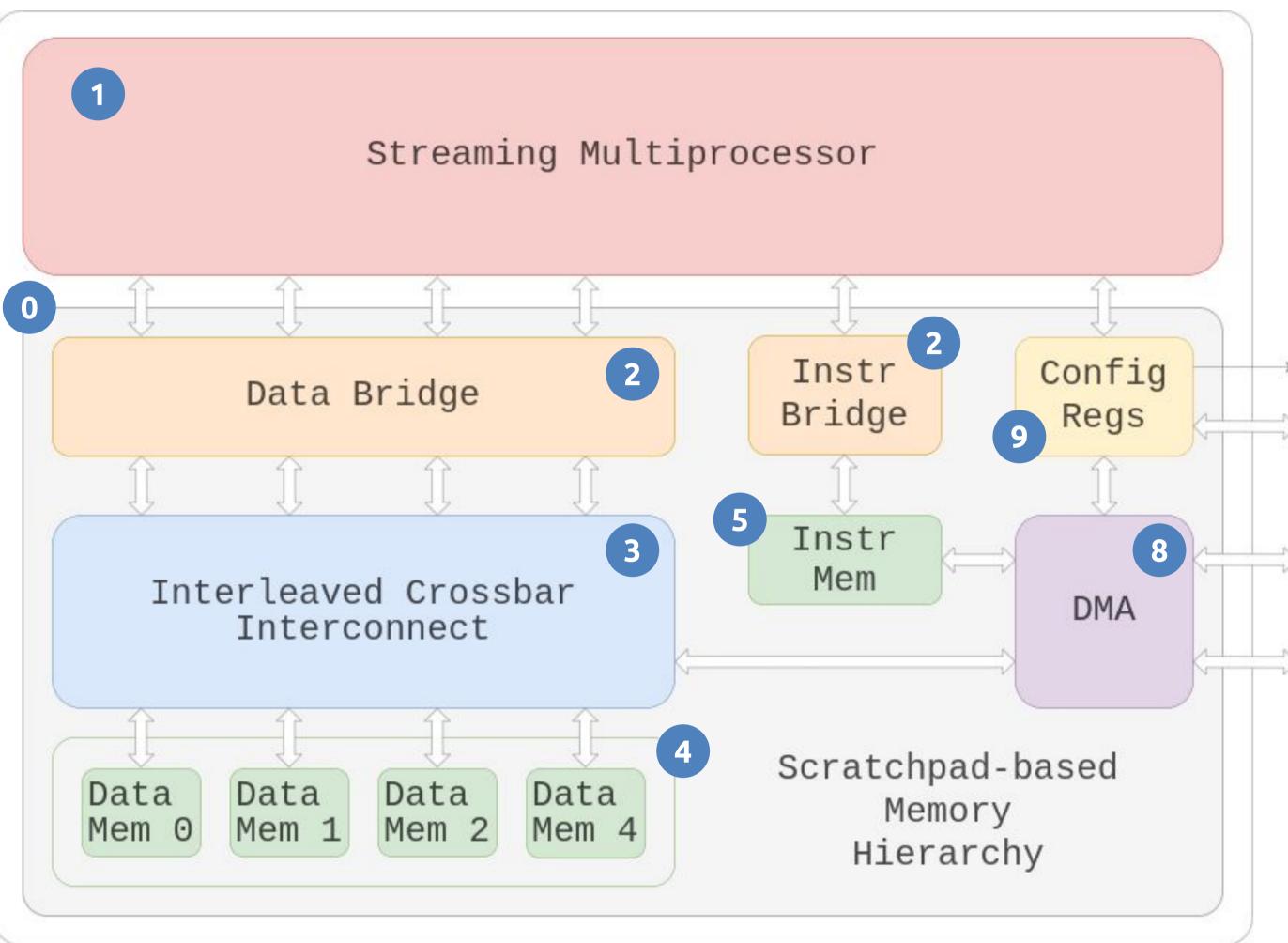

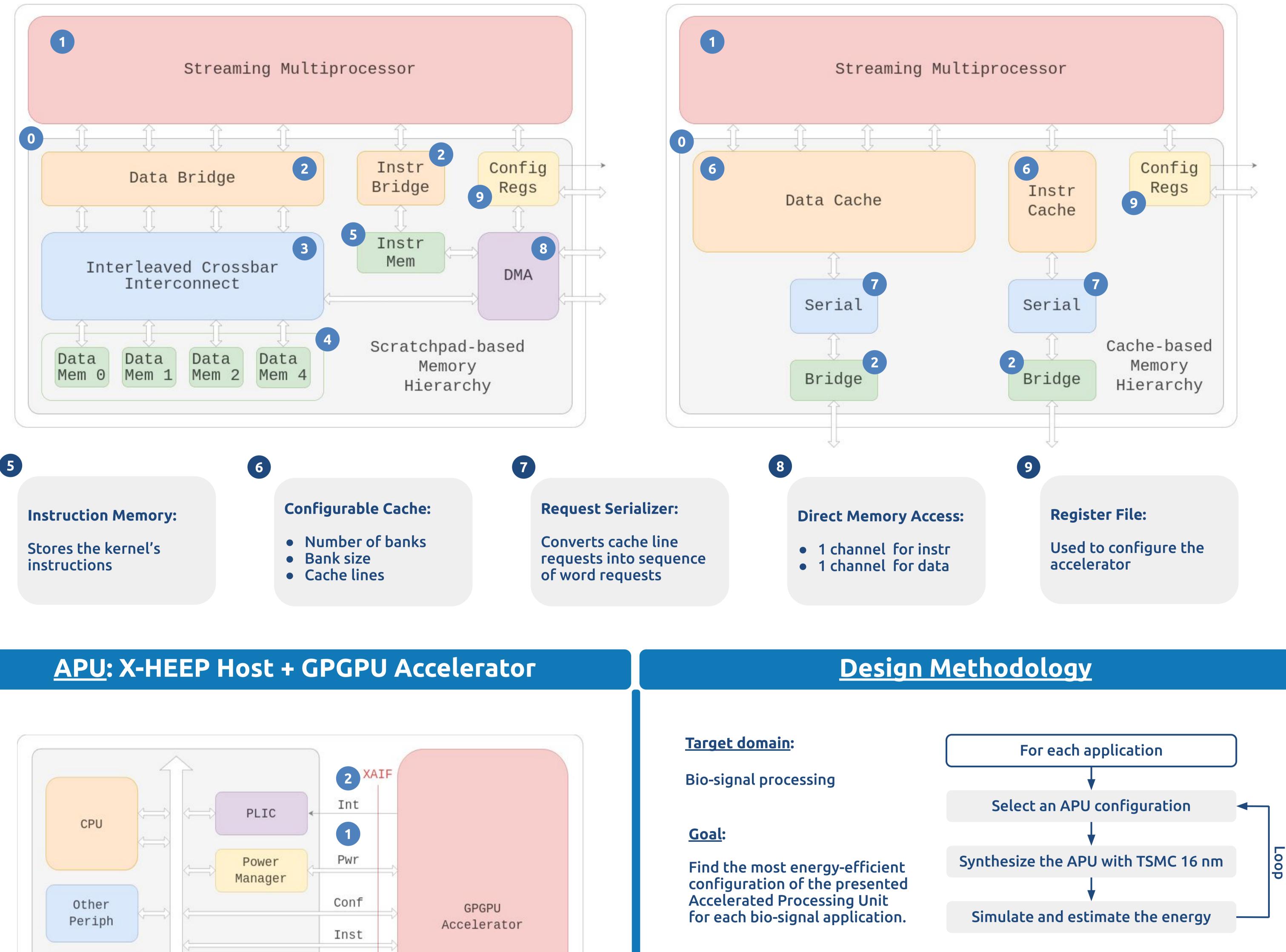

## **<u>GPGPU Accelerator</u>: Scratchpad-based and Cache-based Architectures**

| 0 |                               | 1                                                              | 2                                            | 3                                                  | 4                        |

|---|-------------------------------|----------------------------------------------------------------|----------------------------------------------|----------------------------------------------------|--------------------------|

|   | figurable Memory<br>archy:    | Configurable RISC-V<br>GPGPU Core:                             | <b>Protocol Bridge:</b><br>Converts from the | Bus Interconnect:<br>Interleaved fully             | Data Memory:             |

|   | cratchpad-based<br>ache-based | <ul> <li>Number of threads</li> <li>Number of warps</li> </ul> | MEM to the OBI<br>protocol used by           | connected crossbar to<br>enable parallel access to | Stores the kernel's data |

• Floating-point unit

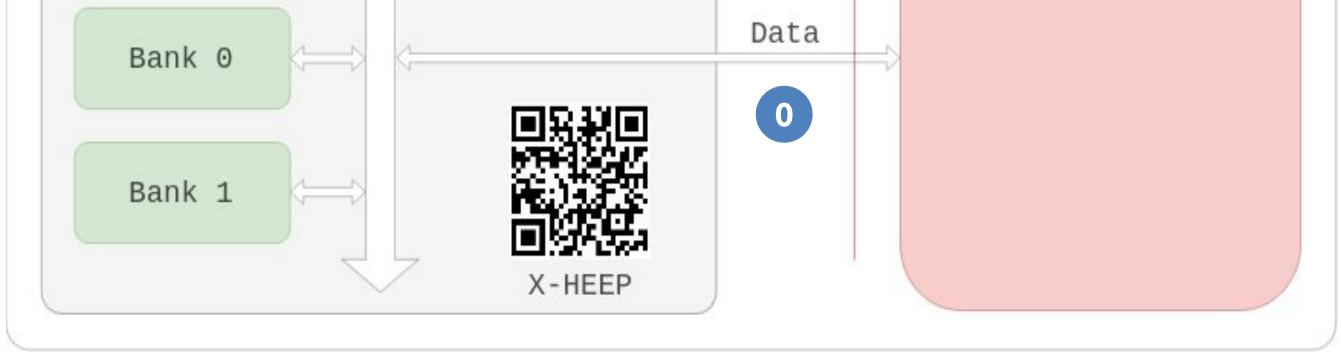

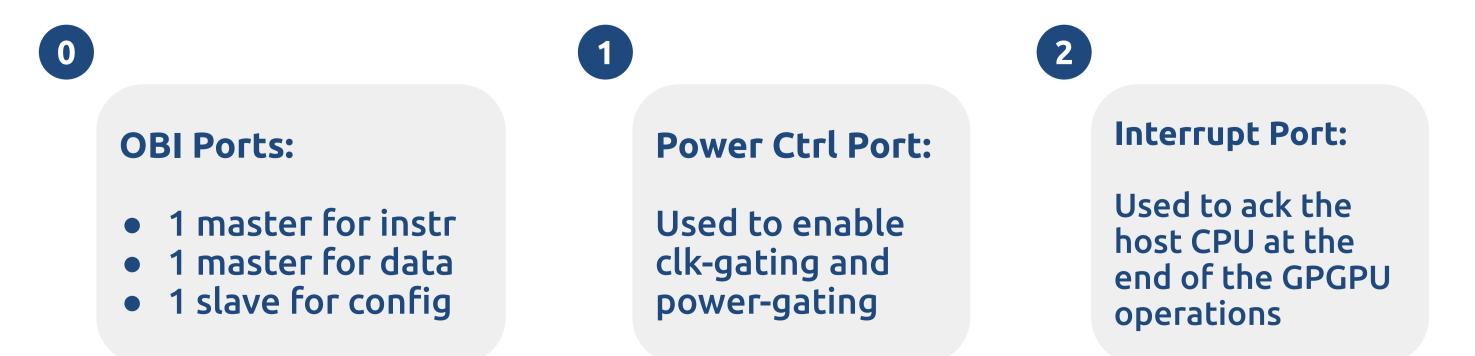

X-HEEP host

- We present the first open-source and configurable GPGPU accelerator specifically designed for ultra-low-power wearable devices.

- We integrate the presented GPGPU accelerator with our in-house-designed X-HEEP host microcontroller to realize an APU for exploring CPU/GPGPU interactions.

- We propose a design methodology to select the most energy-efficient configuration of the presented APU for each bio-signal application.