G. Calderini (LPNHE Paris), D. Dannheim (CERN), F. Huegging (Bonn)

G.Calderini, D.Dannheim, F.Huegging, DRD3/WG7 Workshop 1

DRD3

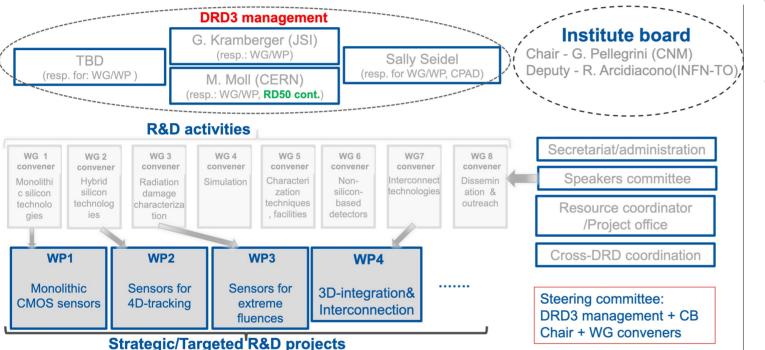

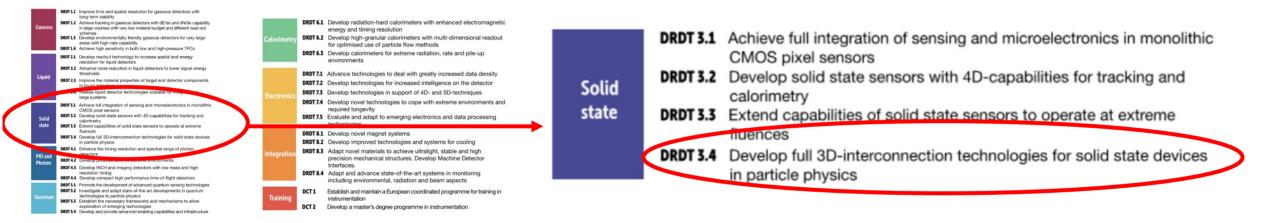

## **Evolution of the DRD3 Collaboration**

#### **List of Participating Institutes**

132 institutes registered537 people on the mailing list

ECFA

Furopean Committee

https://drd3.web.cern.ch/institutes

The DRD3 Collaboration has evolved a lot in the last year A number of new Institutes joined Structure of WGs is now more clear An Institute Board and Management Structure is in place Progressing towards a DRDC approval

DRD3

**European** Committee for

## **Evolution of the Collaboration**

WG7 has a strong association with the Interconnection WP

DRD3

The idea is to organize the activities as formal tasks inside the WP

Everybody interested in interconnections is welcome to deposit a EoI to allow us with the organisation

We will try to build aggregation of groups on a number of projects

European Committee for

## WP4/WG7: Interconnections

# DRD3

# Interconnections are a strong point of future detector and electronics development

They have a critical role in the development of detectors and electronics Sensor-FE, Tier to tier, multiple stacks Interconnections for modules, interconnection for characterization

Furopean Committee for

Activity of the WP4/WG7 will be organized around axes (Research Goals)

- RG 7.1: Yield consolidation for fast interconnection technologies

- RG 7.2: Demonstration of in-house process for single dies and pixel interconnections for a range of pitch (down to < 30  $\mu$ m)

- RG 7.3: Development of maskless post-processing for classical bumping interconnection technologies

- RG 7.4: Development of wafer-to-wafer approach in presently advanced interconnection technologies

- RG 7.5: Development of VIAS in multi-tier sensor/front-end assemblies

**European** Committee for

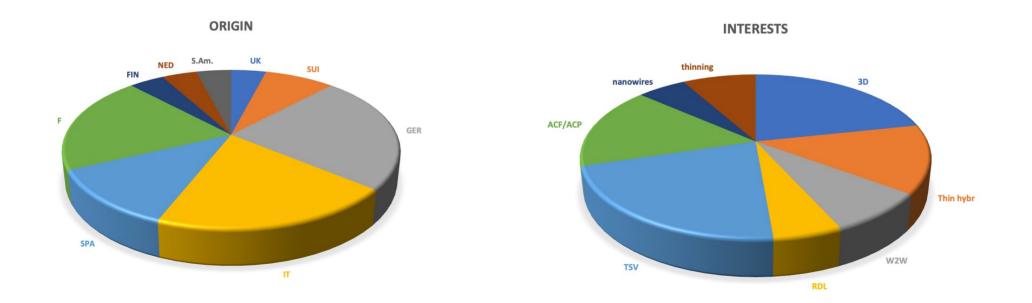

- New version of the EoI slides from institutes are still flowing in (on 16/5 we have 10)

- For reference: at the time of last year workshop:

- 35 groups / 85 questionnaires already interested and planning to have resources

- Among them 25 gave some specific information

- 15-20 FTE already declared

European Committee for

TSV, RDL 3D, direct wafer bonding ACF/ACP

- -> 3 institutes

- -> 2 institutes

Statistics from interconnection interests inside the "Emerging technologies, DRD7.5"

#### Today:

ECFA

Furopean Committee for

- Introduction and analysis of interests

- Quick overview of the main WP4 axes

- Fast Interconnections for R&D

- In-house interconnection technologies

- Interconnection technologies via specialized vendors

- Discussion with present groups

- Collaboration meeting: June 17-20th

- Thematic presentations centered on WP4 projects

DRD3

### Different stages and technology levels

### I – Maskless connections

# DRD3

# Testing and fast connections: not only to have a cheap way to test objects but also for fast prototyping

Application possible even for temporary connection

#### Permanent maskless connections (for example ACF/ACP)

Maskless, in house technology for plating/interconnect

Allows for cheap interconnection Quick turnaround time

- Wafer and device level connection

- Module to flex interconnections

#### Research goals:

ECFA

Committee f

- RG 7.1 Yield consolidation for fast interconnections

- RG 7.2 Demonstration of in-house process for single dies and pixel interconnections for a range of pitches (down to < 30µm)

- RG 7.3 Development of maskless post-processing for classical bump-like interconnection technologies

(Temporary connections already widely used in testing / characterization)

#### ATLAS AM chips test setup

Conductive micro-particles

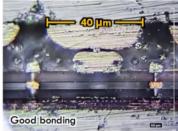

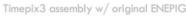

Timepix3 assembly w/ re-worked pad

## I – Maskless connections: status and plans

Recent progress by CERN EP R&D WP 1.3, Geneva Univ., Medipix, LPNHE Paris, FBK, ESRF, Univ. Pisa:

- Plating

- Systematic optimisation of ENIG processing parameters  $\rightarrow$  Uniform plating with ~10 µm ± 0.5 µm height down to 50 µm pitch

- Hybridisation

- Proof-of-concept ACF hybrids with Timepix3, SPHIRD, ALTIROC3, TimeSpot

- Confirmed low resistance of ACF/ACP micro-particle connections using FBK/LPNHE chain devices

- Module integration

- Adhesion tests and module bonding with ACF, gold studs, nano wires for MALTA2 and test structures

- Multi-module flex PCB produced; functional demonstrator with chip-to-chip data transfer for 4 MALTA

- Plans for EP R&D phase II (2024-2028) / DRD3

- Further **exploration** of innovative interconnect + module-integration technologies

- Reliability testing (thermal cycling, irradiations)

- Scalability towards large-area applications, integration of optical links

Chain device for resistance meas.

18 μm ACF – resistance measurement

#### Nano wires on MALTA2 pads

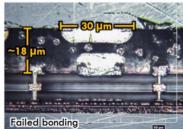

ACF-bonded 4-chip module

# II - More advanced bumping / bonding interconnections DRD3

#### Different technological level

This needs today RTO or industry

#### Vendors busy with upgrade productions

Move part of process to laboratories

#### Different features from different technologies can address specific complex issues

- small pitch

ECFA

European Committee fo

- process-temperature constraint

- electrical properties (current, C)

- connection flow

(wafer-wafer, device-wafer)

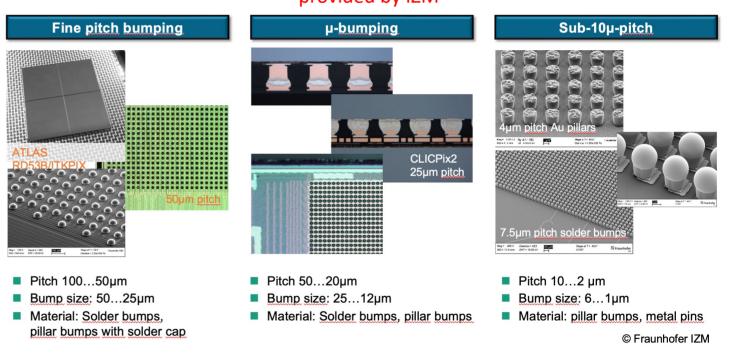

## Examples of interconnection technologies provided by IZM

### **II - W2W BONDING PROCESS DEVELOPMENT**

# DRD3

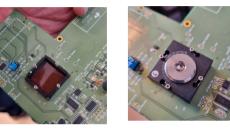

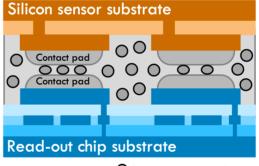

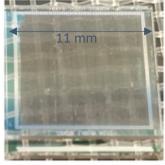

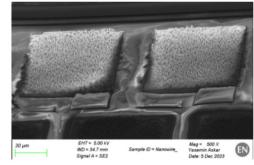

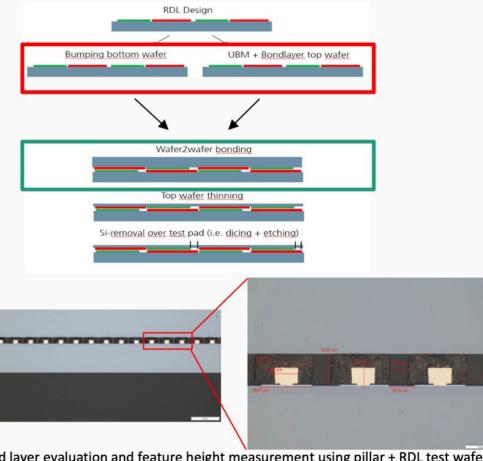

Recent work at Bonn University in collaboration with IZM

- WP1: Design development and manufacturing of process qualification wafer, design preparation of functional TIMEPIX3 and DMAPS sensor wafer

- 1.1 Definition of technological approach for ultra-thin low-mass hybrid pixel detectors

- 1.2 Process qualification design including test structures

- 1.3 Fabrication of process development wafer

- 1.4 Design and mask preparation for TIMEPIX3 readout electronics and DMAPS active sensor wafer

- WP2: Wafer bonding and thinning process

- Bonding material evaluation and process

- WP3: Wafer bonding with capacitive coupled IOs and conductive IOs

- WP4: Backside wafer process with TSV-etching and backside metallisation process

- Next steps:

ECFA

European Committee for

- Processing of daisy chain test layout setup wafer

- Evaluation of full process chain (bonding, thinning, silicon etching)

- Electrical conductivity test of daisy chain test structures

Bond layer evaluation and feature height measurement using pillar + RDL test wafe Recalculation of the required pillar + UBM height based on bond layer thickness results

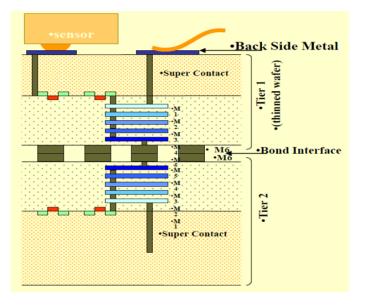

### III - 3D and vertical integration

Via industry it will profit of commercial drive

Stack to match digital/analog many reasons to do so

Could allow complex communication between different connected devices

Allow to contact/power/read a lower layer through an upper one

Multi-tier, mixed-technology

#### This is at the interface with DRD7: institutes/groups interested?

#### Interconnections are essential point of all hybrid sensor-FE technologies

Different levels:

- Cheap temporary (for test) or permanent connections

- Fast connections for prototyping: short turn-around

- More advanced partially in-house process to address specific constraints (small pitch, temperature)

- Complex interconnection process via RTOs/industries

For monolithic technologies, interconnections are necessary for multi-tier extensions. Here, important applications also for module-to-flex interconnections

Strong link with electronics (DRD7): importance of interface definition

Groups interested in the above activities should work proactively to help us to build up the WP4 collaborative projects in view of the June DRD3 Collaboration Meeting

European Committee for Eu

**DRDT** 7.5

**Emerging Technologies**

13

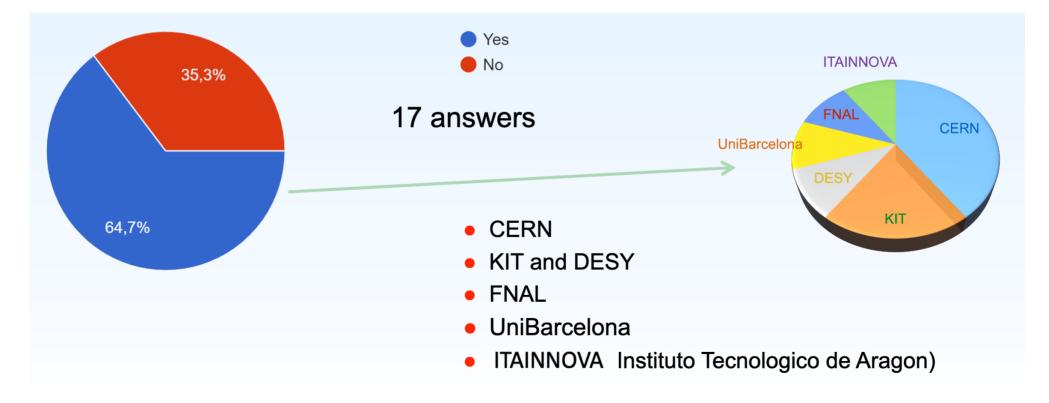

### 3D integration & high density interc. (5)

Please describe the topics you (and/or your group) would like to participate in?

- Integration of single photon sensor and readout chip (UniBarcelona)

- Characterisation of 3D stacks, with focus on irradiation studies (CERN)

- Power consumption, heat, combine analogue, digital and photonic functions (CERN,

Test and characterization

Developments of TSV, TGV, RDL and 3D ICs

- Edgeless IC design (FNAL, KIT)

- High-density integration sensor, electronic & photonic ICs (KIT, DESY)

- 3D integration of silicon photonics and Electronic IC using TGV and TSV (CERN, KIT)

- Development of detector modules concepts for 3D stacked MAPS with redistribution layers (CERN)

- Design and prototyping of chip/sensor/interconnect assemblies focusing on low mass, powering, heat dissipation, signal integrity, and electromagnetic compatibility (EMC) (*ITTAINOVA*)

- 3D Tools for LVS and DRC; partitioning of functions across layer stack (FNAL)

ECFA DRDT 7.5 Kick-off

ECFA

European Committee