# **Spacely + Caribou on the ZCU102**

Adam Quinn

May 14, 2024

# **Agenda**

- Brief Overview of Spacely

- Spacely-Caribou

- Work done to make Caribou Compatible w/ ZCU102

# **Spacely**

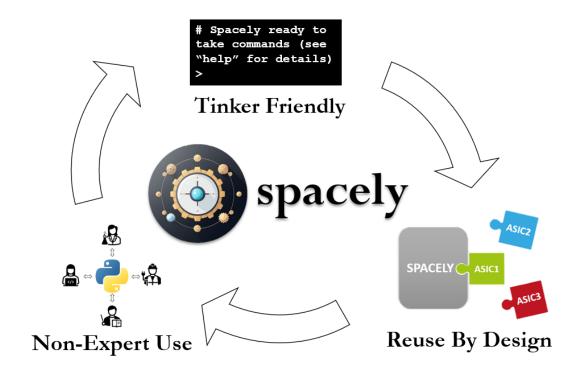

- Spacely is an open-source,

Python based test automation framework

- Spacely consists of a core

Python repository,

supplemented by instrument

libraries, firmware, and

recommended design flows.

- Spacely is targeted toward small ASIC design teams in research/academia, and nonexpert (scientific) users.

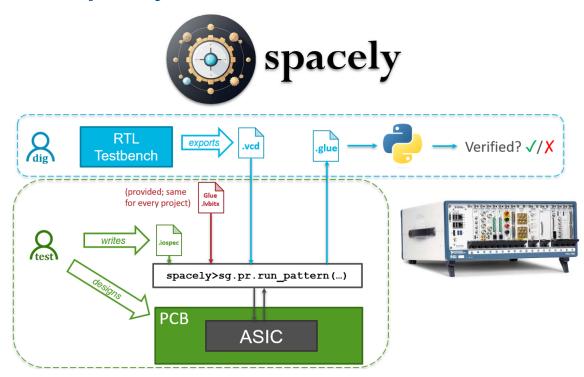

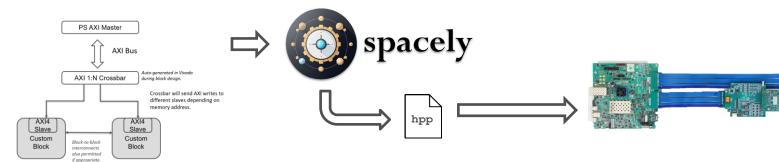

## Go from Verilog to the Lab with Spacely

- Export VCD waveforms from your verification testbench and use them directly as test stimulus for your ASIC.

- Expert digital ASIC and test engineers can both participate directly in test, reducing miscommunication.

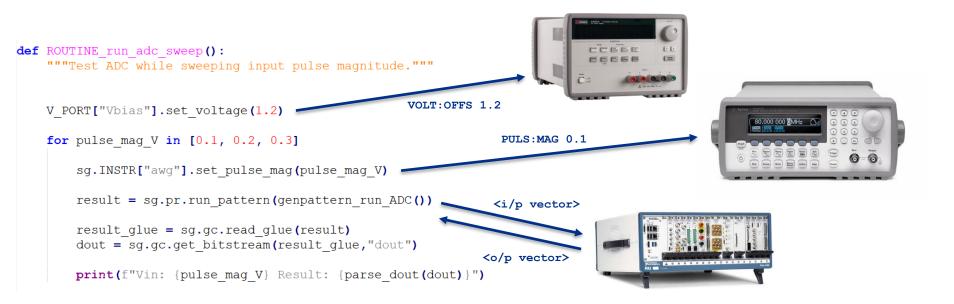

### **Control Test Instruments with Spacely**

- Spacely abstracts interfaces to test equipment

- Python test routines read like natural language; easy for scientific stakeholders to participate.

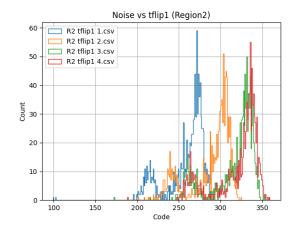

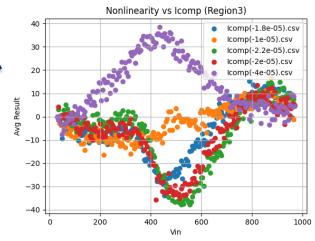

### **Analyze Data with Spacely**

- Experiments and

DataFiles, each with tagged

Metadata corresponding to

the Python variables used in

the Spacely routine, which is

automatically written to file.

- Calculate statistics and generate scatter plots / histograms natively in Spacely.

- Ibdig(0.2).csv

- Ibdig(0.3).csv

- lbdig(0.4).csv

- lbdig(0.5).csv

- Ibdig(0.6).csv

- 🛂 Ibdig(0.7).csv

- meta.txt

- Nonlinearity\_vs\_lbdig.png

- Transfer\_Function\_vs\_Ibdig.png

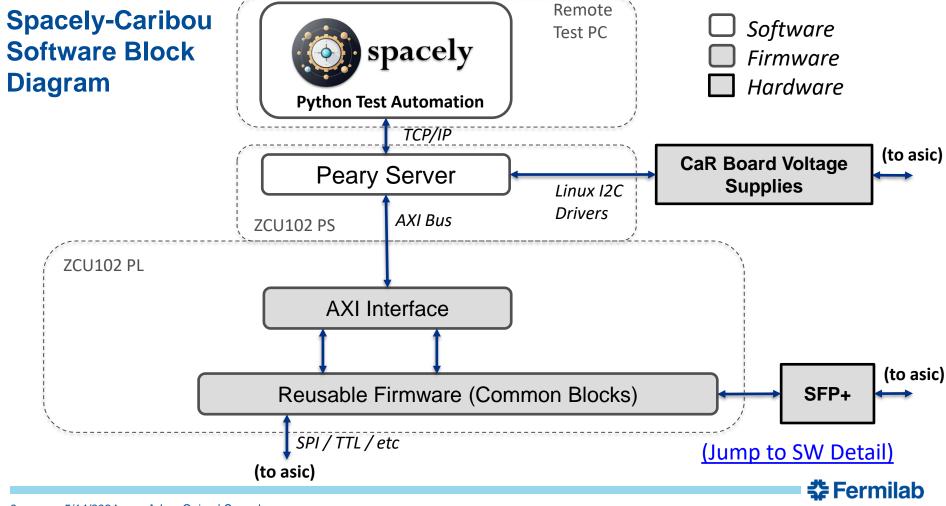

### What is Spacely-Caribou?

- Spacely-Caribou is a test strategy which uses the Spacely test automation framework to write Python tests which are carried out using Caribou test hardware and firmware.

- The primary aim is to leverage Caribou infrastructure, while shifting as much of the ASIC-specific development into the high-productivity Python environment.

## Caribou Usage Model w/ Spacely

(1) Build a firmware design in Vivado by connecting pre-made AXI blocks (no RTL experience required unless you need custom blocks)

(2) Spacely generates a C++ style AXI memory map, which you include in the SpacelyCaribouBasic peary device. (All other parts of the device are generic.)

(3) Flash your ZCU102 with the provided BOOT.BIN, and build Peary with the SpacelyCaribouBasic device.

```

def ROUTINE_run_adc_sweep():

"""Test ADC while sweeping input pulse magnitude."""

V_PORT["Vbias"].set_voltage(1.2)

for pulse_mag_V in [0.1, 0.2, 0.3]

sg.INSTR["awg"].set_pulse_mag(pulse_mag_V)

result = sg.pr.run_pattern(genpattern_run_ADC())

result_glue = sg.gc.read_glue(result)

dout = sg.gc.get_bitstream(result_glue, "dout")

print(f"Vin: (pulse_mag_V) Result: (parse_dout(dout))")

```

(4) Write your test routines in Python with commands like caribou.get\_memory() and V\_PORT["VDD"].set\_voltage()

(5) Do Science!

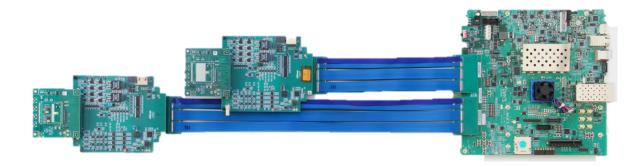

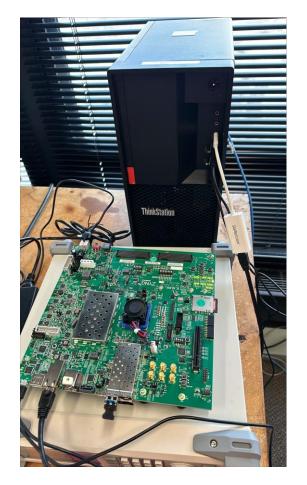

#### **How we Ported Caribou to ZCU102**

1. Software: Minor updates to Peary

2. OS: Petalinux

3. Hardware: ZCU102 Mezzanine Board

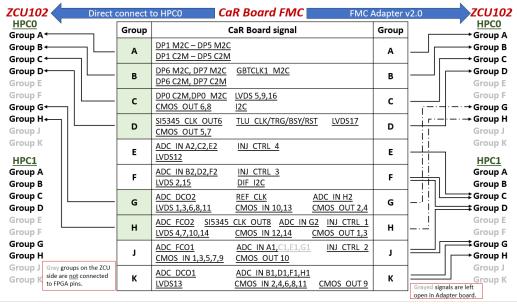

#### Hardware: ZCU102 Mezzanine Board

- Modification of the BNL ZC706

Mezzanine Board

- Minor component updates and signal re-routing.

- Note: A small number of connections (ADC\_IN C1, E1, and G1) were sacrificed due to insufficient pinout.

- Status: Manufacturing

#### **OS: Petalinux**

- Built a basic image for the ZCU102 using Petalinux tools.

- Included a very basic FW image which maps 4 GB of AXI address space (0x400000000 to 0x4FFFFFFF) so that it is addressable from Peary.

- Edited the Device Tree to include CaR board I2C multiplexers

- Booted the ZCU102 from SD card.

### **Software: Minor Updates to Peary**

- Updated CaR board I2C addresses to match the ZCU102 Device Tree

- Added car\_i2c\_read/write functions that can be accessed from pearyd for flexibility.

- Created "SpacelyCaribouBasic" Device

- Keeping with Spacely-Caribou philosophy, this "device" should be sufficient for most ASICs.

- Only the memory map must change, and this can be autogenerated from Spacely.

- Small update to Memory interface to make AXI reads 32b wide independent of platform.

```

9efc27f7 (HEAD -> aq_dev) 32b memory write function

c6858df1 Updated memory reads to 32b

c7e0d13c Implemented 16b car_i2c_read

54303bac Created SpacelyCaribouBasic Device

1c3c5824 Updated I2C buses for Si570 USR MGT CLK

a05e8d5d (origin/master, origin/HEAD, master) Merge branch 'p-fix-cmake-install-prefix' into 'master'

b4cefd60 cmake: add back INSTALL_PREFIX option

13ed3026 cmake: only override install prefix if default initialized

e049b5ed Merge branch 'p-include-dir-export' into 'master'

017bd89e cmake: also add include/peary to interface include dirs

```

Caveat: I am not a C++ developer. Pull from my branch at your risk & expect to see some warnings about integer casting... ©

### Let's work together!

Spacely is open-source: <a href="https://github.com/SpacelyProject/spacely-docs">https://github.com/SpacelyProject/spacely-docs</a>

-- Includes common firmware blocks for ZCU102 PL

Happy to push my aq\_dev branch to the Peary Gitlab (need permission)

#### Other things we'd be happy to share (need to figure out the best way):

- Boot Image for Petalinux on the ZCU102

- Design for the ZCU102 Mezzanine Board

#### **Possible Targets for Collaboration:**

Documentation / Guide on setting up Caribou + Peary