## Readout of Straw Tube Tracker for Neutrino Physics

R. Petti

University of South Carolina, Columbia SC, USA

for the WP3 Project D

DRD1 collaboration meeting Topical workshop on electronics for gaseous detectors June 19th 2024, CERN

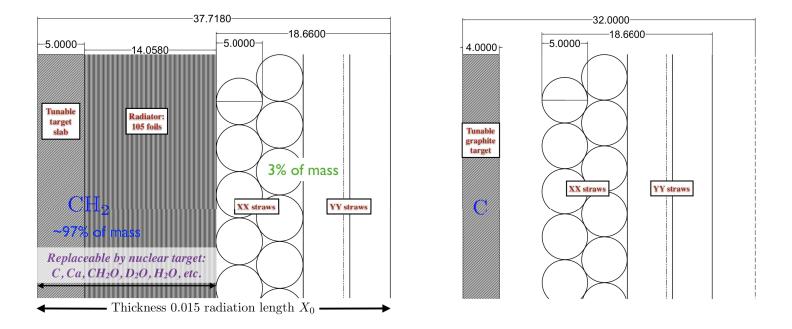

- Many ( $\sim$ 80-100) thin ( $\sim$ 1.5%  $X_0$ ) passive targets separated from active detector (straw layers);

- ← Targets of high chemical purity (~ 97% of mass) keeping average density  $\rho \leq 0.17$  g/cm<sup>3</sup>

- + High track sampling: 0.15 (0.36)% $X_0 \perp (\parallel)$  with total detector dimensions  $\sim 1X_0$ ;

- ◆ "Solid" hydrogen target from a subtraction of CH<sub>2</sub> & C | targets;

- Common tracking modules with 4 XXYY straw layers across entire detector.

⇒ Individual targets can be replaced with planar targets of desired material of varying thickness

#### **REQUIRED PERFORMANCE**

- ◆ STT designed to offer a control of *ν*-target(s) similar to e<sup>±</sup> fixed-target experiments

⇒ Detector fully tunable/configurable during data taking

- + Low-density design & target mass allow accurate in-situ calibrations:

- $\Delta p < 0.2\%$  momentum scale uncertainty from  $K_0 \rightarrow \pi^+\pi^-$  in STT volume (~ 300k);

- p reconstruction and identification, vertex, etc. from  $\Lambda \rightarrow p\pi^-$  in STT volume (~ 500k);

- $e^{\pm}$  reconstruction and identification from  $\gamma \rightarrow e^+e^-$  in STT volume (~  $10^7$ ).

- Combined particle ID & tracking over the entire STT volume:

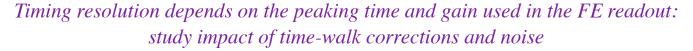

- Electron ID with Transition Radiation (TR) and  $dE/dx \Longrightarrow \left| \pi/e \sim 10^{-3} \right|$ ;

- $4\pi$  detection of  $\pi^0$  from  $\gamma$  conversions (~ 49%) within the STT volume;

- $p/\pi/K$  ID with dE/dx, range, and time-of-flight with surrounding calorimeter.

- $\implies$  Readout of both drift time and charge with  $10^3$  dynamic range for  $\mathcal{O}(100k)$  straws

- + Accurate reconstruction of transverse plane kinematics from particle 4-momenta:

- "Transparent" target/tracker system with dimensions  $\sim 1X_0$  and  $4\pi$  acceptance;

- Momentum resolution  $\delta p/p \sim 3\%$ , angular resolution  $\sim 1-2$  mrad.

#### **INTEGRATED STT READOUT BOARDS**

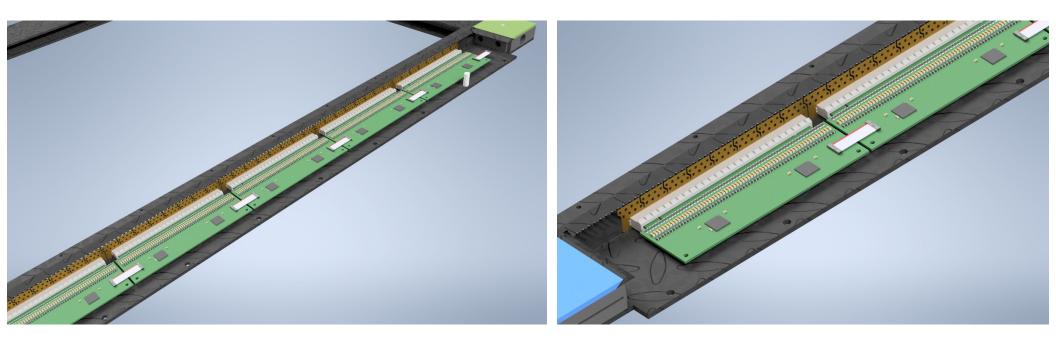

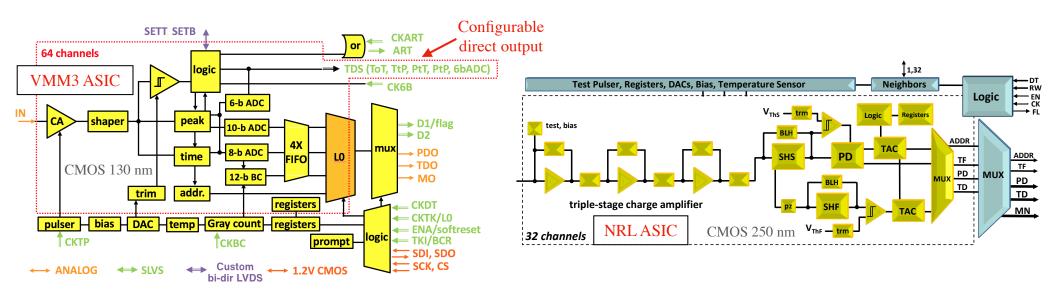

- ◆ Integrated boards reading up to 64 straws each with ASIC + micro-controller (MCU):

- Connection with straw pins via flexible kapton PCBs with PCIe connector for easy upgradability/replacement;

- Design variants with different ASICs: NRL analog (G. De Geronimo), VMM3a, custom ASIC;

- Surge protections, LV fuses, and Solid State Relay (SSR) for HV connect/disconnect.

- + Low-power boards (~0.65 W for 64 channels with NRL ASIC) minimizing signal path

- $\implies$  First version (v1) successfully tested, prototypes of revised version (v2) in preparation

Revised design (v2) of the readout board and of the connecting flexible kapton board

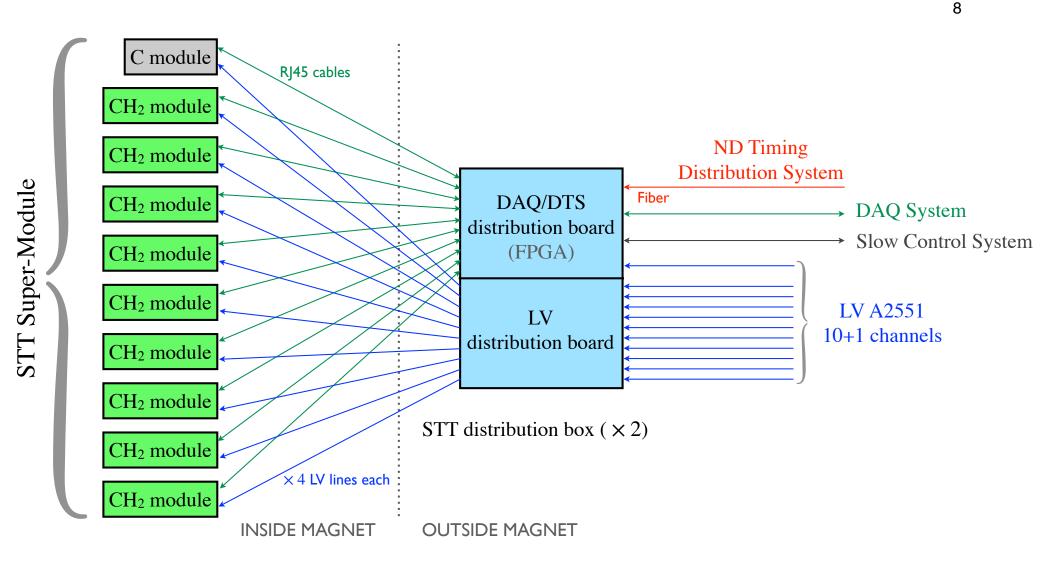

Schematic diagram of the DAQ/DTS and LV connections for one STT Super-Module

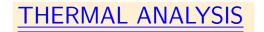

- ✦ Thermal analysis of full scale STT module with 24 integrated readout boards;

- + Self-cooling design with expected total power dissipation about 0.65 W per board (mostly ASIC)

- $\implies$  Maximal temperatures obtained below 40° C allow extended board lifetime

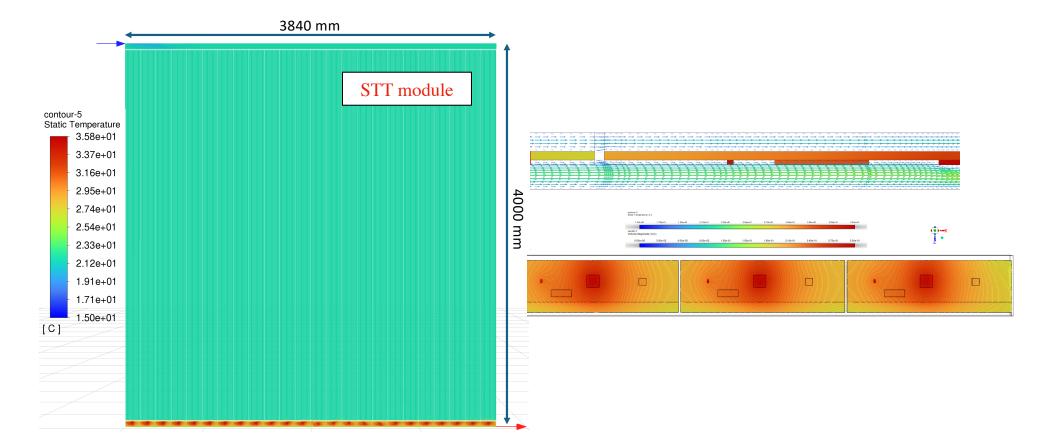

#### VMM3A ASIC AND NRL ASIC

◆ Design variant of STT readout board with existing VMM3a as backup solution:

- Use VMM3a direct output in "external" ADC mode with the MCU (bypassing internal ADCs);

- Readout variant readily available which could be used during construction and initial data taking;

- Default STT readout minimizing project risks while developing custom ASIC.

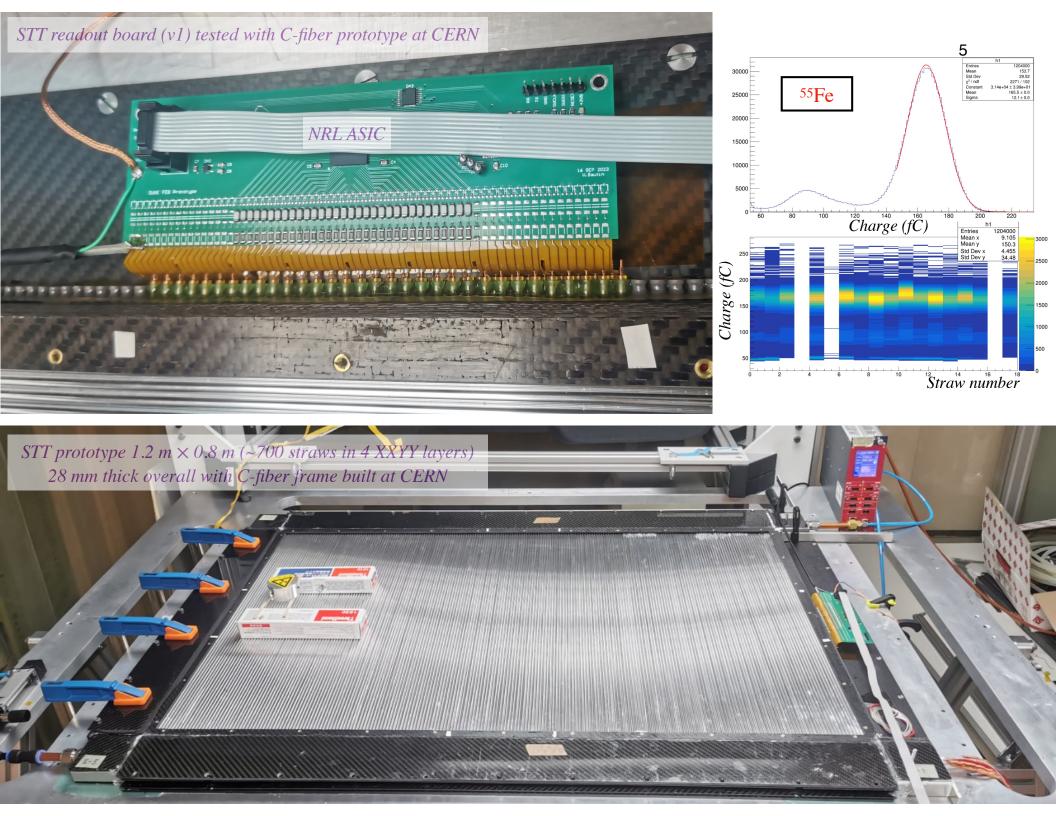

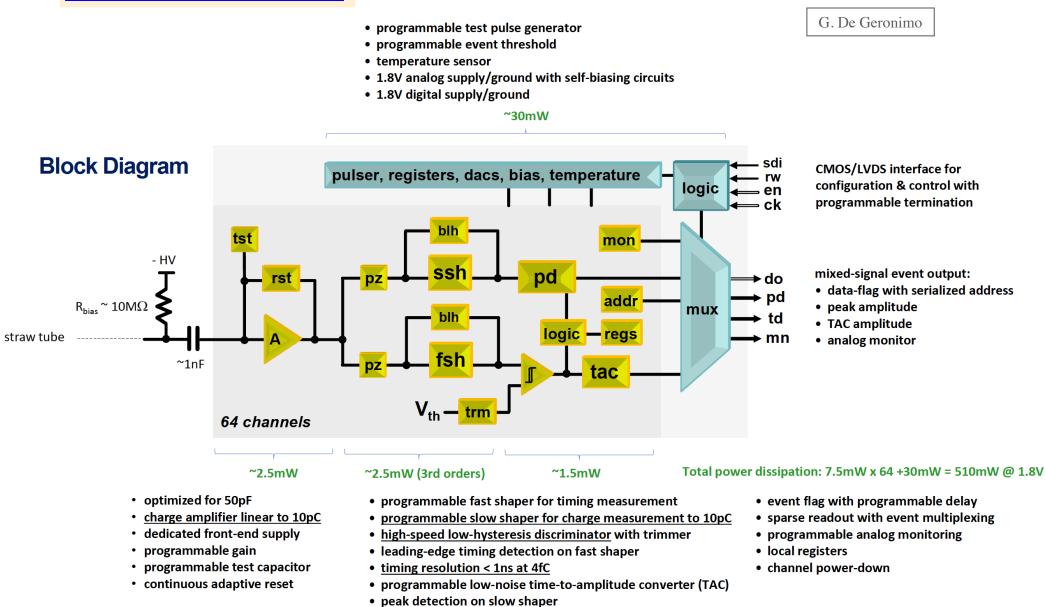

◆ Design variant with existing NRL ASIC to test base architecture for custom ASIC

$\implies$  Flexible design allows easy exchange/upgrade of individual STT readout boards

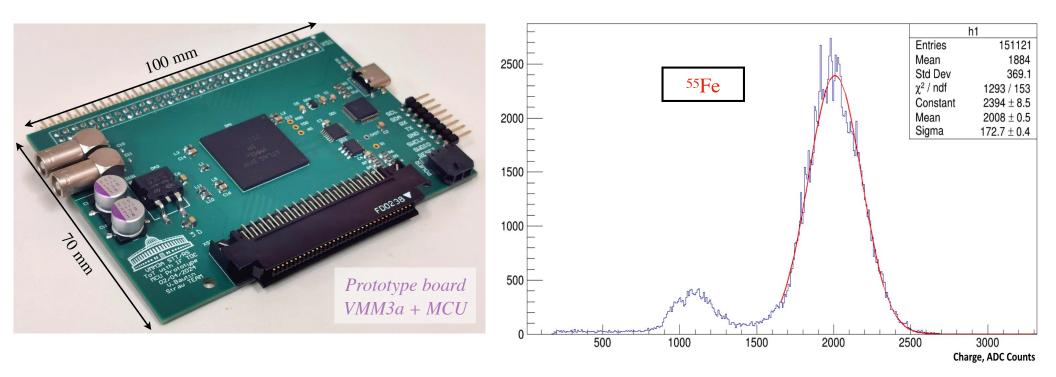

- ◆ Prototype board with VMM3a in "external" ADC mode and 12-bit 4MSPS ADC in MCU;

- ◆ Successful test of charge readout from a straw tracker prototype with <sup>55</sup>Fe source;

- + External ADC mode fixes known bad ADC/TDC performance in VMM3a continuous mode.

- $\implies$  Prototype with the form factor and connections of STT readout boards in preparation

#### PRELIMINARY ASIC REQUIREMENTS

- Modularity: 64 channels

- Input capacitance: 10-40 pF (optimize for 40 pF)

- + <u>Flat cable</u>:  $\sim I$  cm traces + PCIe connector (capacitance < I pF)

- Architecture: dual sub-channel with independent gain and shaper

(i) fast shaper & high gain for time measurement

(ii) slow shaper & low gain for energy measurement

- Minimum charge: 4 fC (time measurement), 20 fC (energy measurement)

- <u>Maximal charge</u>: 10 pC (energy measurement)

- Dynamic range: 1,000 (energy measurement)

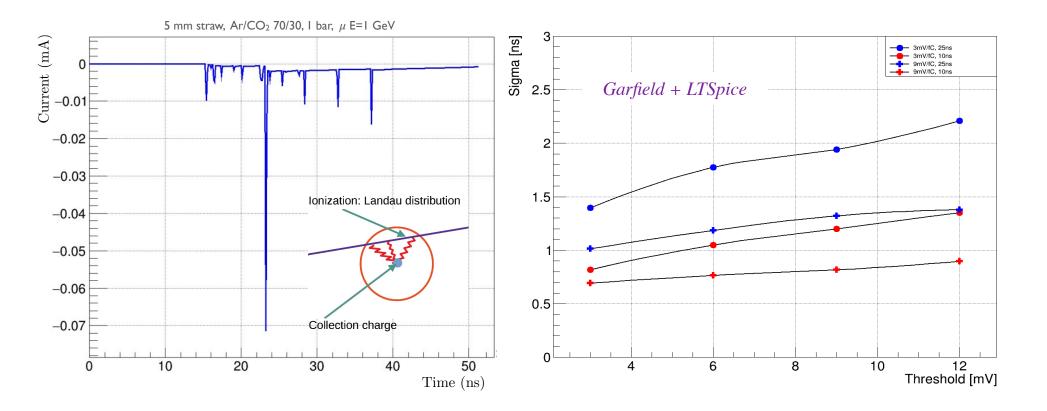

- ✦ <u>Timing resolution</u>: < Ins</p>

- ◆ <u>Gain settings</u>: (i) 6, 9, 12 mV/fC for time measurement

(ii) ≤0.5 mV/fC for energy measurement

- Peaking times: (i) 10, 25 ns fast shaper

(ii) 50, 100 ns slow shaper

- Power consumption: <10 mW/channel</p>

- ♦ Expected rates: ≪I kHz

13

$\implies$  Peaking time ~10 ns with high gain can give resolutions around 1 ns

$\implies$  Dynamic range ~1,000 with charge <10 pC and peaking times ~50 ns

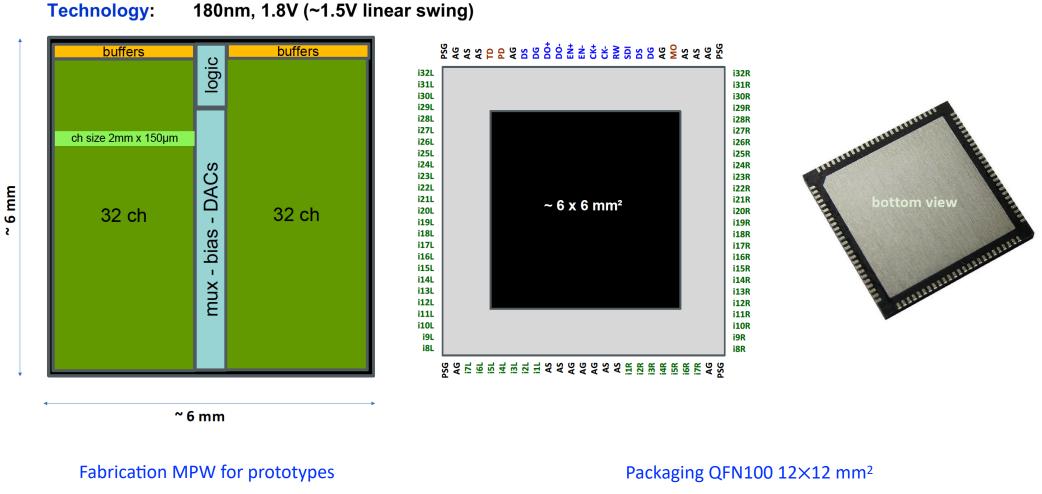

#### CUSTOM ASIC FOR STT

#### sub-circuits and functions largely inherited from well established NRL and VMM

USC

#### Floorplan, Pinout, Packaging

### **SUMMARY**

- Straw Tube Tracker for neutrino physics applications characterized by compact tracking modules with 4 XXYY straw layers and high level of detector integration

- ◆ Developed integrated boards reading 64 straws with ASIC + micro-controller:

- Design variants with different ASICs: NRL analog, VMM3a, custom ASIC;

- Low-power boards (0.65 W for 64 channels with NRL ASIC) minimizing signal path.

- ⇒ Flexible design allows easy upgrade/exchange of individual readout boards

- Prototypes of STT readout boards equipped with NRL and VMM3a ASICs tested with straw tracker prototypes

- Preliminary studies for the development of custom ASIC for STT

- $\implies$  ASIC requirements and overall architecture based on VMM3a and NRL

# **Backup slides**