## **CMS RPC Link System**

(2nd DRD1 Collaboration Meeting & Topical Workshop on Electronics for Gaseous Detectors)

Behzad Boghrati, Mojtaba Mohammadi Najaf abadi Institute for Research in Fundamental Sciences (IPM),

Mohammad Ebrahimi, Fatemeh Esfandi, Elham Zareiyan

Tehran, IRAN

### on behalf of CMS Muon Group

19 June 2024

2/29

### **Back-up:** 96-Channel TDC , HL-LHC Background Rate, Project Schedule, Radiation level at the CMS Tower Racks, CHARM location G0, CHARM TID and Fluences distribution, CHARM Irradiation Results

CMS RPC Phase-2 Upgrade Projects

Review on new RPC Link System Project

Irradiation Test Results and Validation at P5

□ Present CMS RPC Link System – Upgrade

**G** Summary

**Motivation**

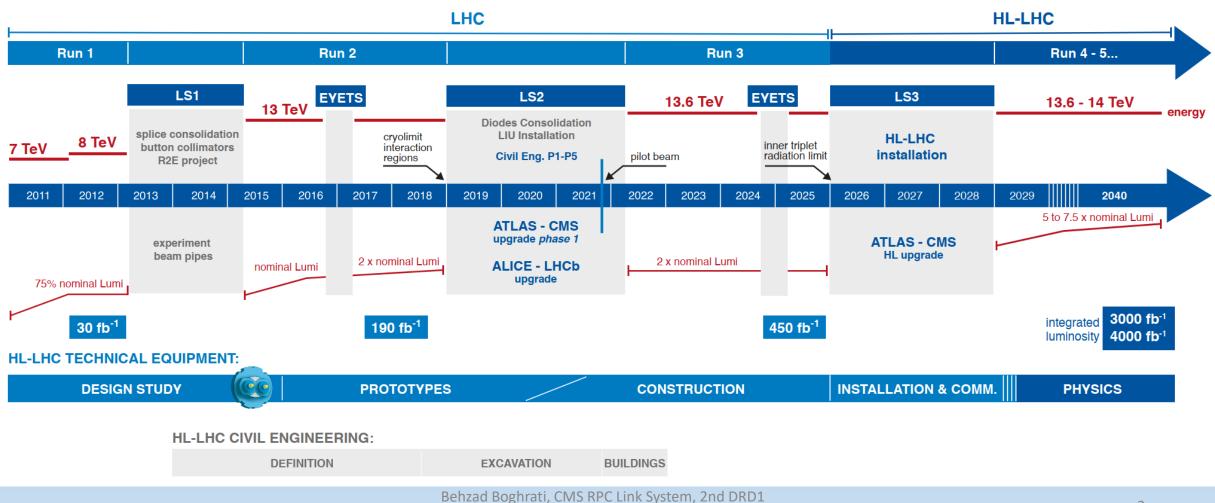

### LHC / HL-LHC Plan

Collaboration Meeting, 19 June 2024

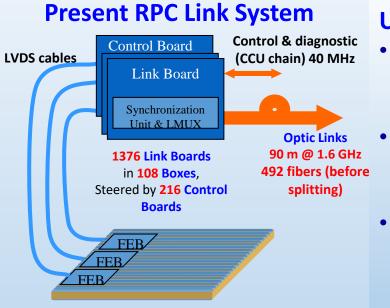

## **Present RPC Link System - Upgrade Motivation**

### **Upgrade Motivation**

- RPC signals synchronization, timing <sup>b</sup>/<sub>a</sub>

resolution is 25ns

- Data transmission speed is about

1.6 Gbps

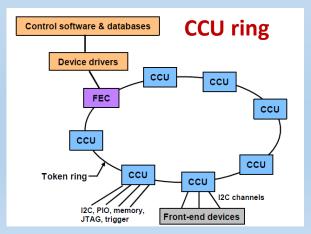

- Control, diagnostic and monitoring of the Link system has been designed based on CCU ring (combination of copper cable and fiber optic), very susceptible to electromagnetic interference

- CCU ring is not very fast, the bandwidth (40 MHz) share between 12 control boards

- Most radiation hard electronic components are obsoleted

- Electronic aging, presently the Link system at the end of LS3 is already 17 years old

## **Present RPC System Ingredients**

**RPC Endcap Chamber**

**Front-end Board**

**Present Link Board**

**On-detector Electronics**

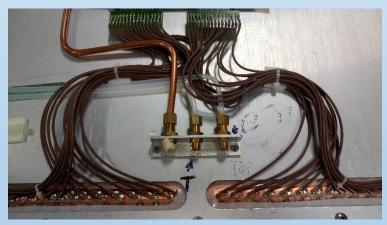

#### RPC Strips, Coaxial cables, Cooling and Gas Pipe

Link System (LBB)

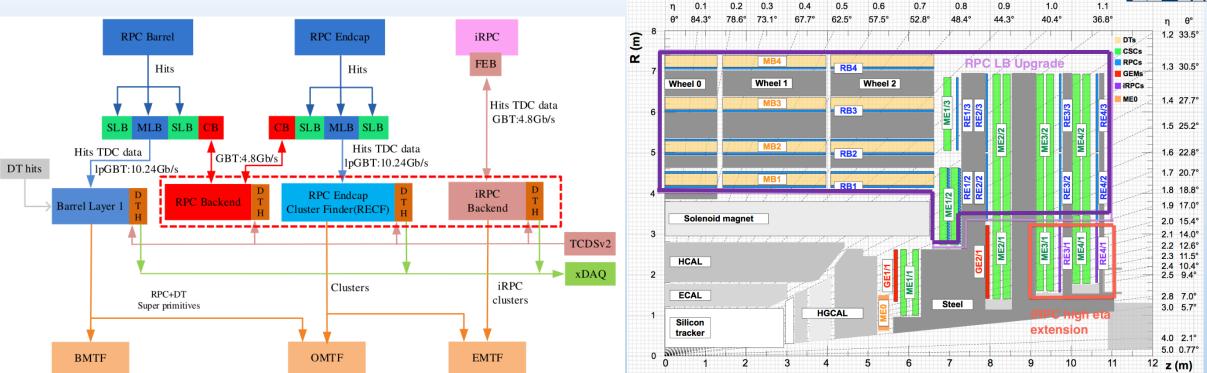

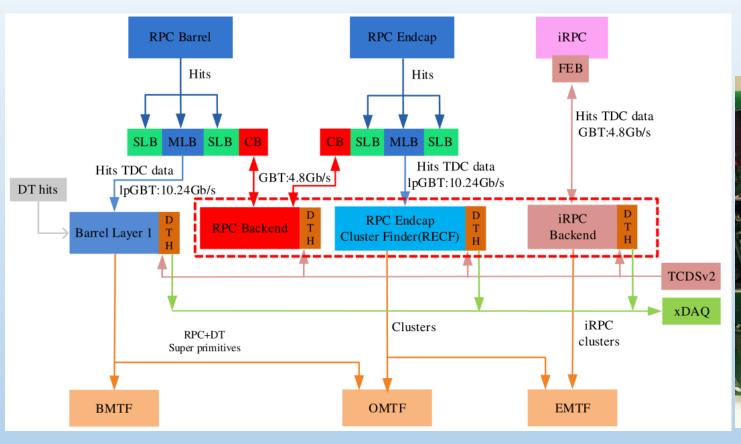

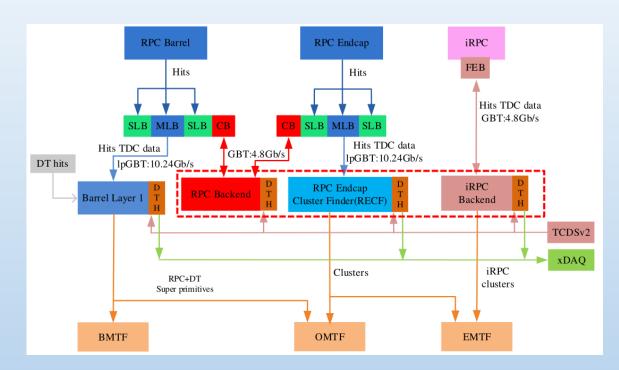

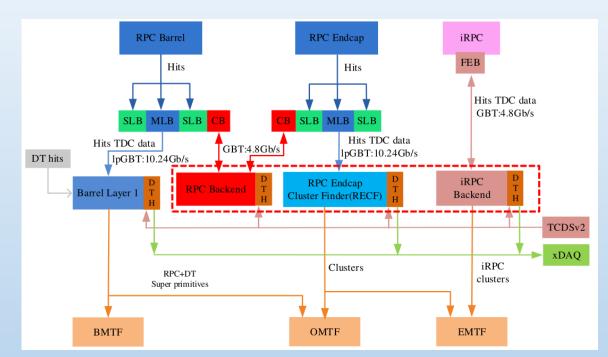

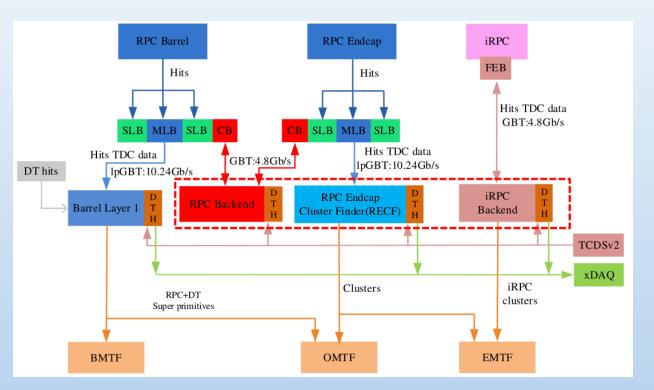

## **RPC Phase-2 Upgrade Architecture and Layer1**

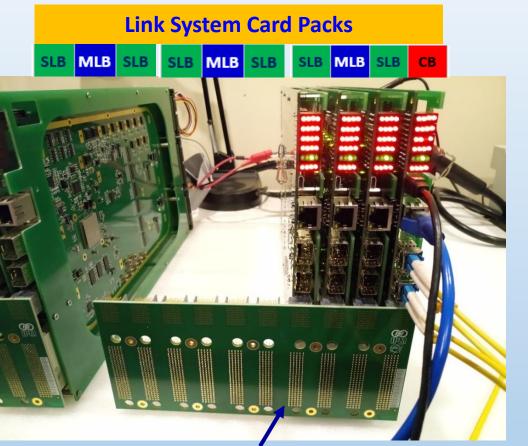

SLB: Slave Link Board MLB: Master Link Board CB: Control Board B/O/E MTF: Barrel/ Overlap/ Endcap Muon Track Finder

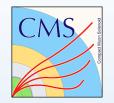

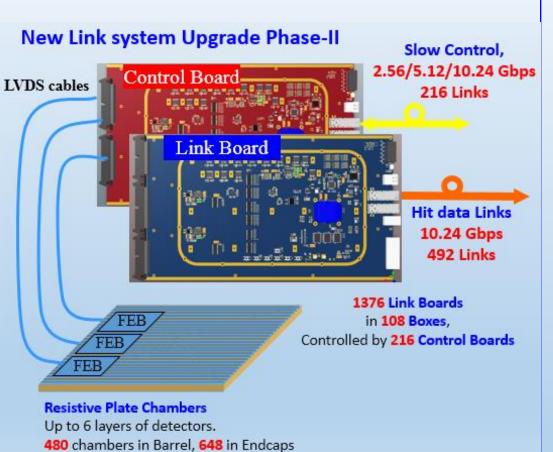

## New RPC System for Phase-2 Upgrade

## **Overview of the Electronics**

### **New Link system Features :**

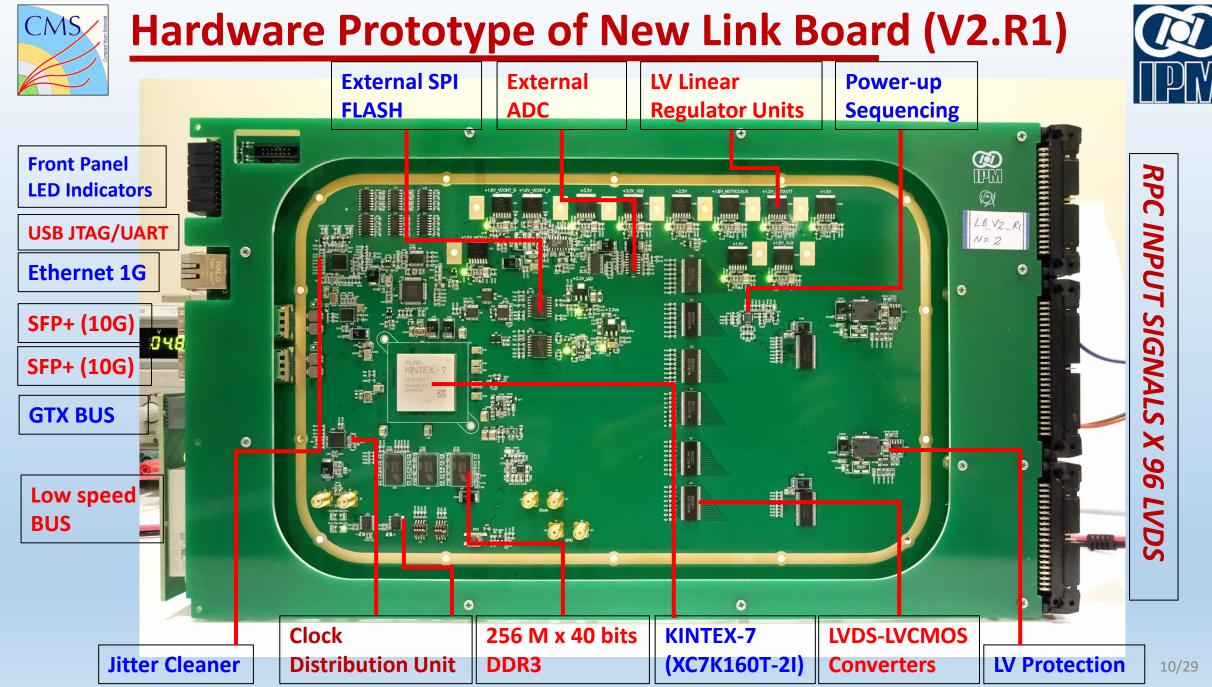

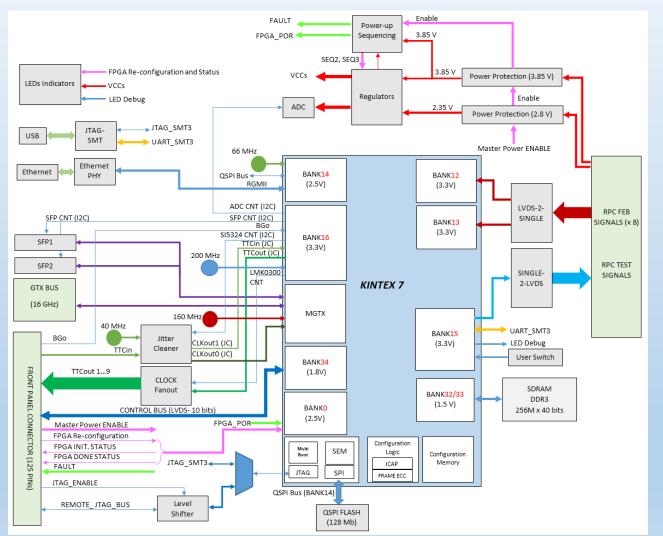

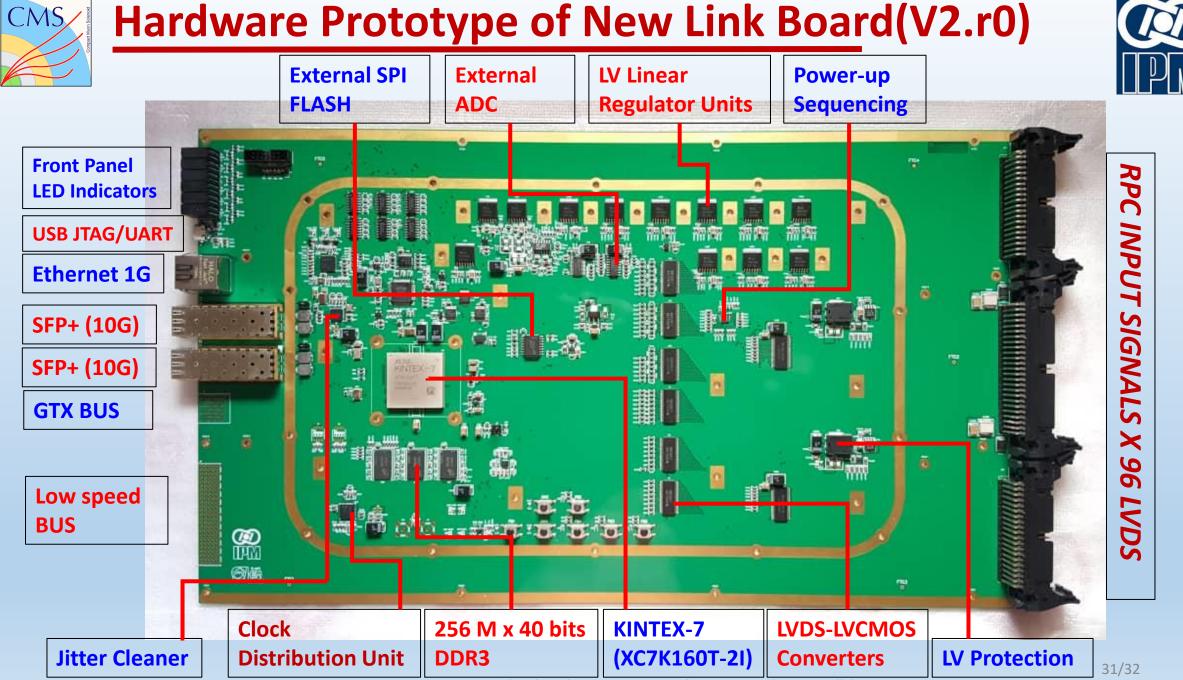

- 1. 14 Layer PCB ,  $40\times28\ cm^2$

- 2. FPGAs are KINTEX-7, XC7K160T Industrial Version

- 3. Muon hit time, TDC timing Resolution : 1.56 ns

- 4. Master Link board output data rate : 10.24 Gbps

- 5. Control Board communication with RPC Backend electronics: 4.8 Gbps

- 6. Input Voltage: 4.0 V (3.8V 5.1 V)

- 7. Current: 3 A -> 2 A

- 8. Power Consumption: 12 W -> 8 W

- 5. Embedded internal buffer (DDR3) : 4 Gbyte

- 6. Optical Transceiver: SFP-10G-SR

- 7. Radiation Mitigation: TMR + Internal Scrubbing

- Scrub Rate of entire FPGA (Real time SEU detection and Correction) : 13ms (31,770 times faster than the rate of SEU at the tower racks)

- SEU at the tower racks : Every 413000 ms

- 8. Safety Systems:

- Over & Under Voltage Protection, FPGA Over temperature Protection, Transient Voltage Suppressor

- ESD Protection (15 kV)

## **System Requirements**

- 1. Signal Conditioning: Single LVDS signal (pair of wires/pins) for each RPC channel (strip). RPC hit is a pulse of 100ns.

- Each LB receives 96 RPC channels i.e. full Endcap RPC (3 eta rolls),

- or one roll of barrel RPC.

- **2.** Impedance Matching: According to the LVDS standard, the line should be terminated on the receiver side by ~100 Ω resistance inside the LVDS line receiver chips.

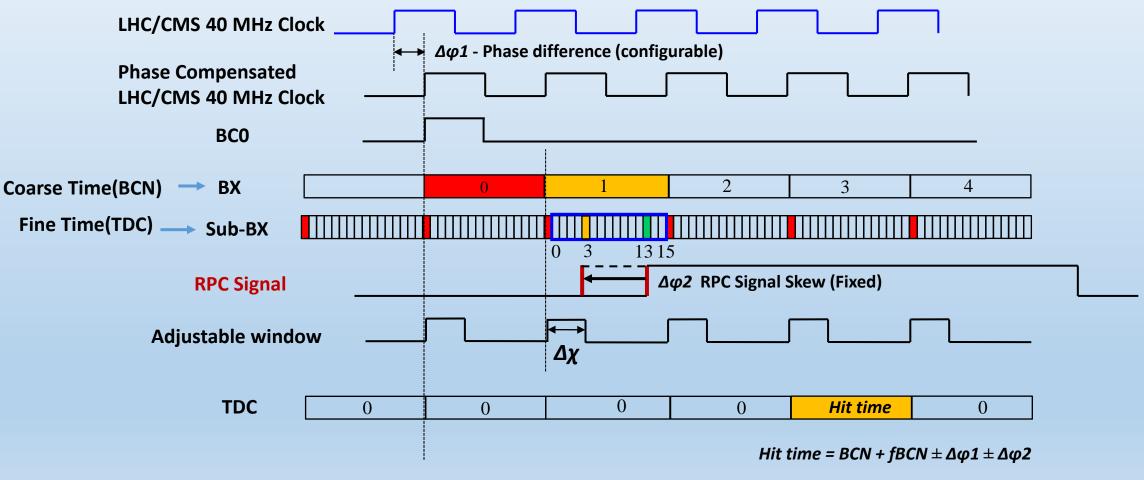

- 3. Time-Stamping: The signals are asynchronous, and the rising pulse edge brings information about the RPC hits timing (the signals are not synchronous to any clock). Time-Stamping unit, implemented in the FPGA, measures the arrival time of the rising edge of the pulses to the corresponding bunch crossing.

- 4. Latency Compensation: The RPC signal and received TTC clock has been delayed concerning the main bunch crossing and should be fixed first. RPC signal delay and TTC clock phase shift compensator.

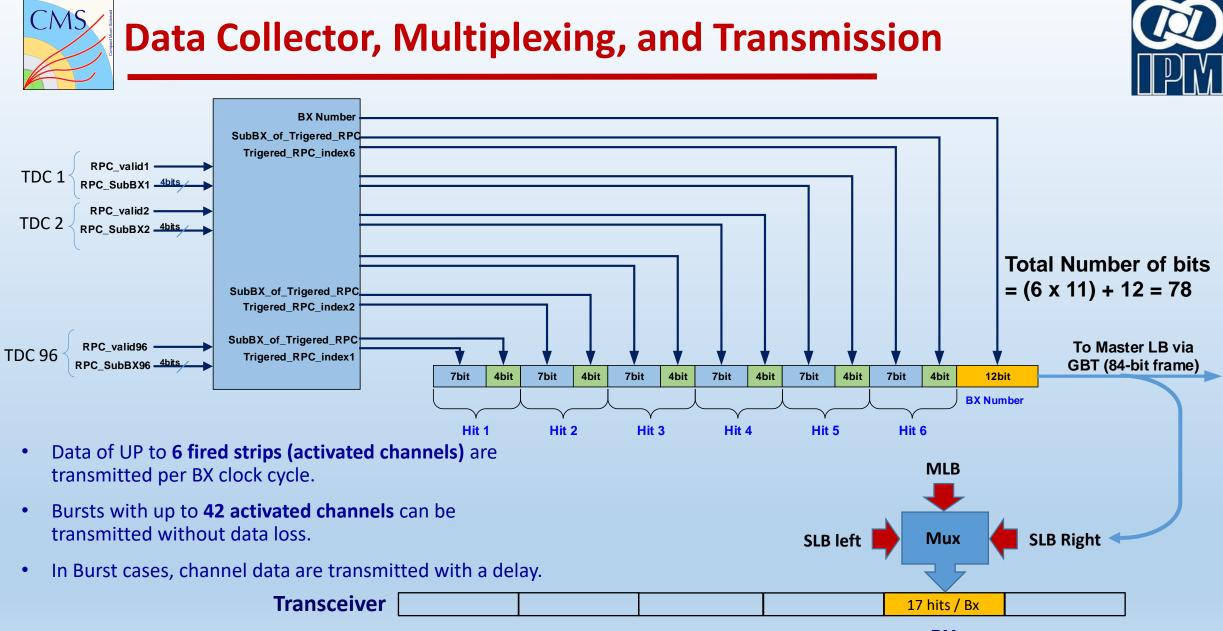

- 5. Data collection and transmitter: Data of 42 fired strips at each bunch crossing are selected and buffered by the data collector inside the Link Board FPGA. Crossing data of 6 hits from one Link Board will be sent to the Master Link Board. In the Master Link board, its data and the data of two adjacent Link boards are collected and merged. At Final, data of 18 hits of current bunch crossing will send to the next layer of the trigger.

- Master/ Slave Link Board: The system is built with Slave Link Boards and Master Link Boards, the PCB is the same, but the firmware is different.

- Link System Front Panel

- 16 Layer PCB

- Board will be cover by an insulator layer

Behzad Boghrati, CMS RPC Link System, 2nd DRD1 Collaboration Meeting, 19 June 2024

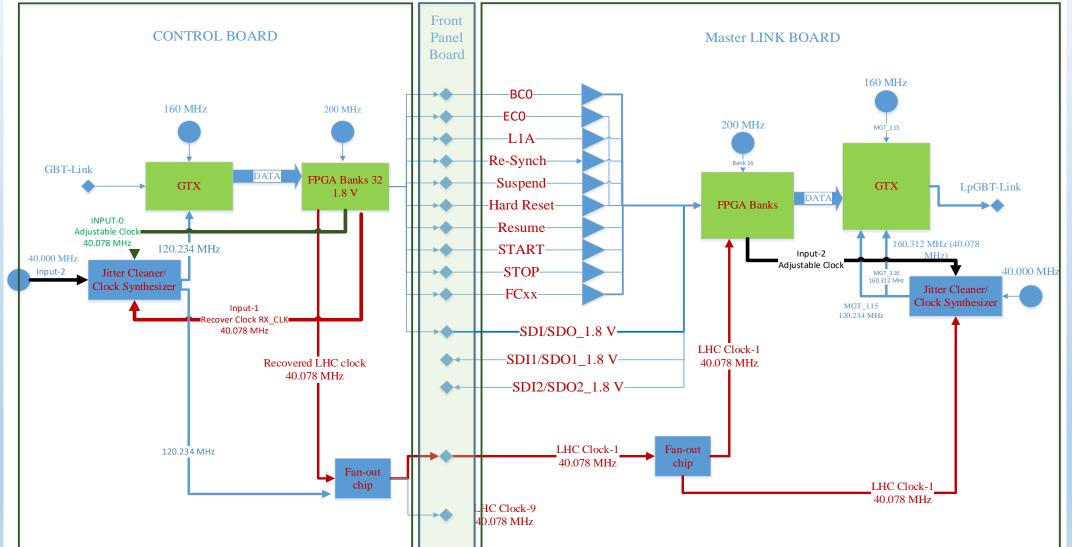

## **Control Board**

- 1. 14 Layers PCB FR4

- 2. The only bridge between RPC backend electronics and Link Boards

- 3. Optical Links to receive TTC, Fast, and Slow commands. GBT-FPGA link driver.

- 4. TTC clock and Fast BGo commands, BC0

- 5. TTC Clock Phase shift adjustment

- 6. FEB Parameter Configuration and Verification.

- 7. Control and monitor the Link Boards Histograms, Data Logs, and Diagnostics through the front panel bus.

## Hardware Prototype of New Link Board (V2.R2)

### Link system final Version:

- Based on the <u>ESR/PRR recommendations (Nov. 2022)</u> and our experience especially from irradiation test at CHARM, a few modifications applied to the electronics:

- 1. PCB Material changed to Halogen-free.

- 2. To optimise power consumption from 12 W to 8 W, some unnecessary components were removed

- 1. Ethernet interface

- 2. DDR3 Memories

- 3. Optimized Voltage regulators

- 4. Two of six front-panel diagnostic LEDs

- 3. The Link system clock chain was modified for more flexibility in measuring the TTC and BCO latency.

- 4. An Analogue Watchdog Supervisor (AWS) is added to recover electronics from the link loss failure.

- 5. A large front panel connector (125-pin) was replaced with a smaller one (55-pin). It helps to shrink the size of the front panel board and prevent any damage during the system assembly by the technicians at P5.

## Link System Clock distribution Scheme (modified)

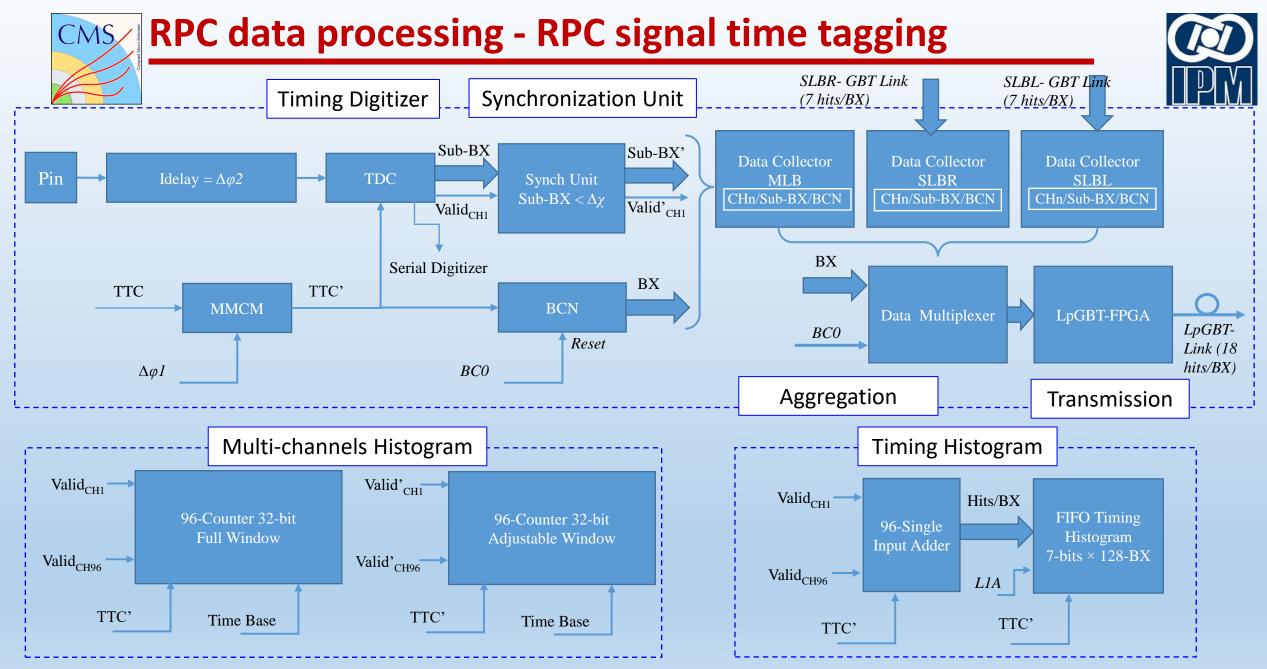

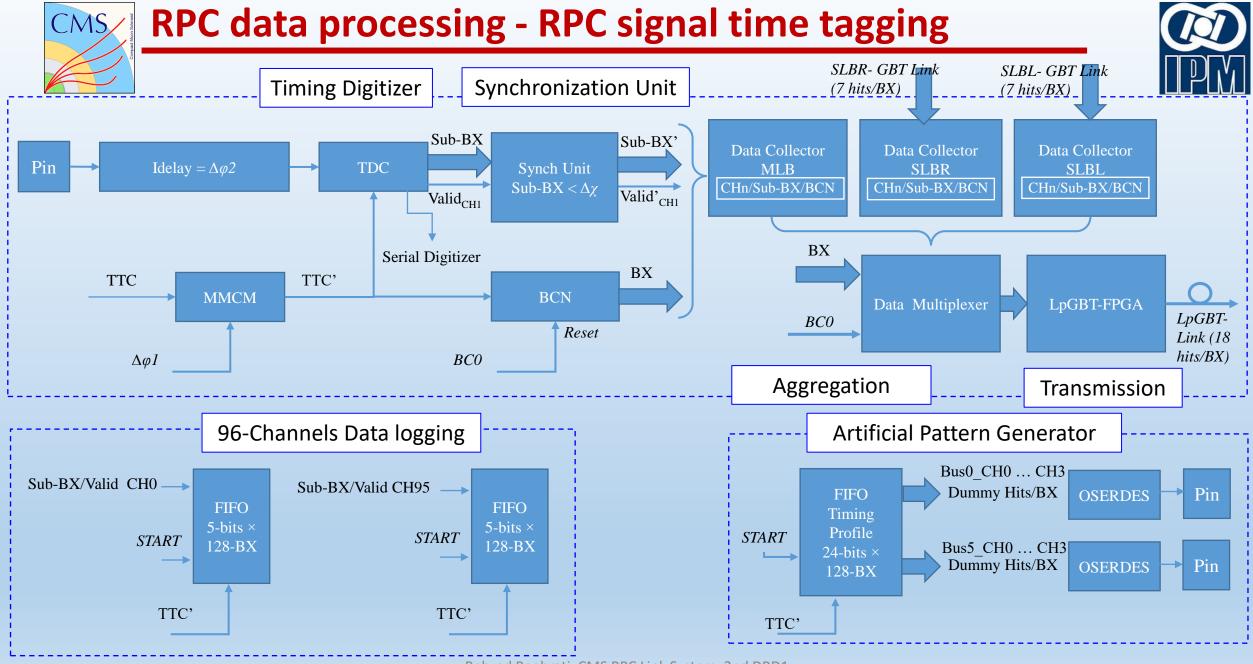

## **Time-Stamping**

RPC signals time Stamp

The first step of the RPC signal processing is the measurement of RPC signal arrival time and assignment of this data to the phase compensated LHC/CMS clock (40 MHz).

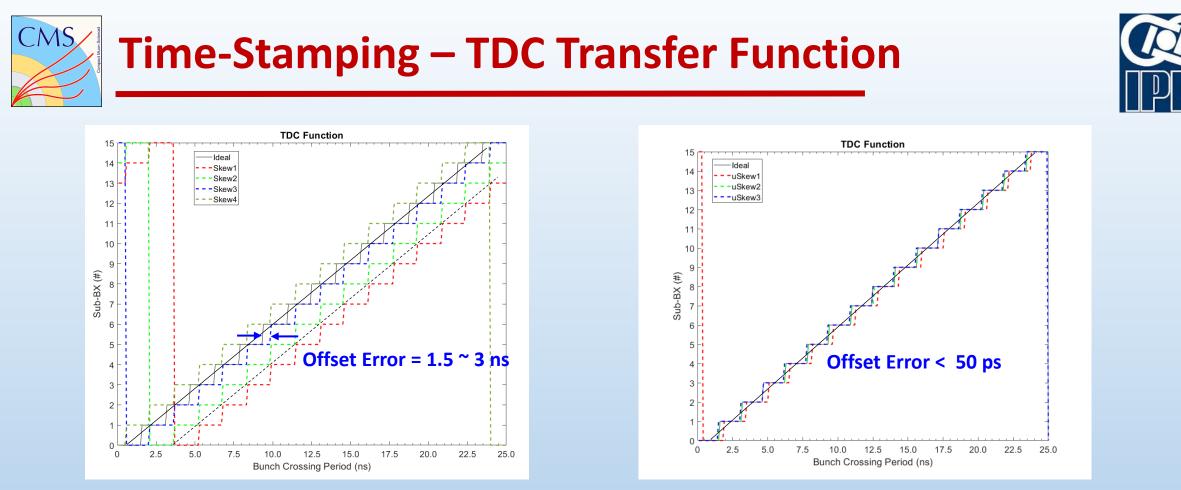

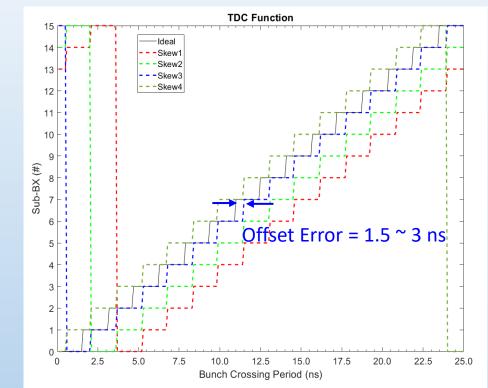

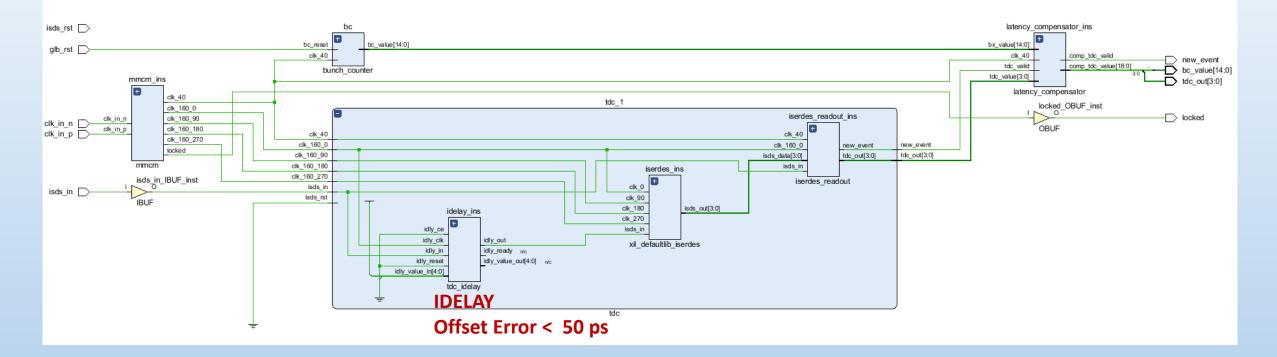

- $\checkmark$  TDC resolution is 1.56 ns. The gain error is <u>zero</u> but the offset error <u>is not</u>.

- ✓ TTC clocks and RPC hit signals have delays w.r.t the origin of the LHC clock. This cause a fixed offset error on the TDC transfer function.

- ✓ In Link Board, the TDC data is compensated with two parameters; 1) Macro steps: 1.56 ns, and 2) Micro steps: 48 ps. Figure left, Macro step offset error compensation, and Figure right, Macro + Micro steps offset error compensation.

BX

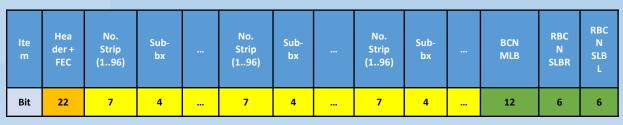

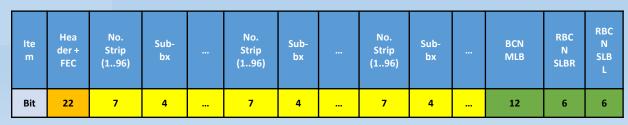

## **RPC Signal and Data processing – Data Transmission**

Frame structure Hit-1 ...

#### Hit-6

| Item | Header<br>+ FEC     | No. Strip<br>(196) | Sub-bx |               | No. Strip<br>(196) | Sub-bx |         | No. Strip<br>(196) | Sub-bx |  | BCN<br>MLB | BCO<br>SLBR | BCO<br>SLBL |

|------|---------------------|--------------------|--------|---------------|--------------------|--------|---------|--------------------|--------|--|------------|-------------|-------------|

| Bit  | 22                  | 7                  | 4      |               | 7                  | 4      |         | 7                  | 4      |  | 12         | 6           | 6           |

|      |                     |                    |        |               |                    |        |         |                    |        |  |            |             |             |

|      | SLB Right (66 bits) |                    |        | MLB (66 bits) |                    |        | SLB Lef | ft (66 bi          | ts)    |  |            |             |             |

### Frame Fields

- **Overhead electronics: Header** (2 bits) + **FEC** (20 bits) ٠

- Hit information: •

- The number of fired strips could be between strip no. 1 to strip no. 96. Size of this field is 7 bits.

- **The Sub-BX** or fractional part of the hit time of a fired strip. The size of this field is 4 bits.

- Master LB Bunch Crossing: Sets as a reference and keeps in the BCN MLB.

- **Bunch Crossing Offsets:** The Bunch crossing in **the Slave LB Right and Left** has an offset w.r.t the Master Link ٠ Board bunch crossing. These offsets keep in the **BCO SLBR/SLBL** fields.

- Frame size: 256 bits ٠

- Total Number of data bits: (3 x 66) + 12 + 6 + 6 = 222 bits

## **Preparation for Irradiation test in Cern 904 Lab**

### □ June/July 2022: Preparation for Irradiation Test

- ✓ Link System Test Setup was tested at 904 Lab.

- ✓ System fully stable, responsive during 8 hours continuous run.

- ✓ Cold Test was passed. Error injection to the FPGA was done and every errors (virtual SEU) were detected and corrected by FPGA SEM IP core.

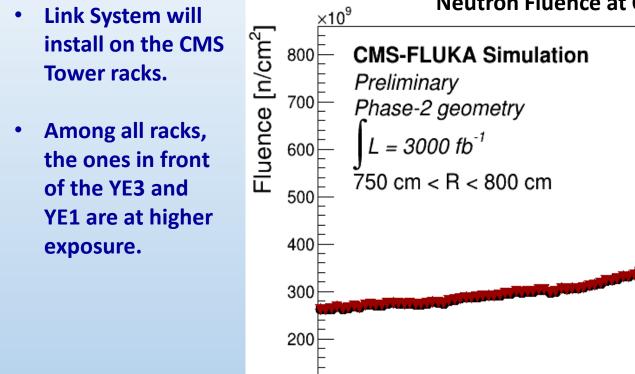

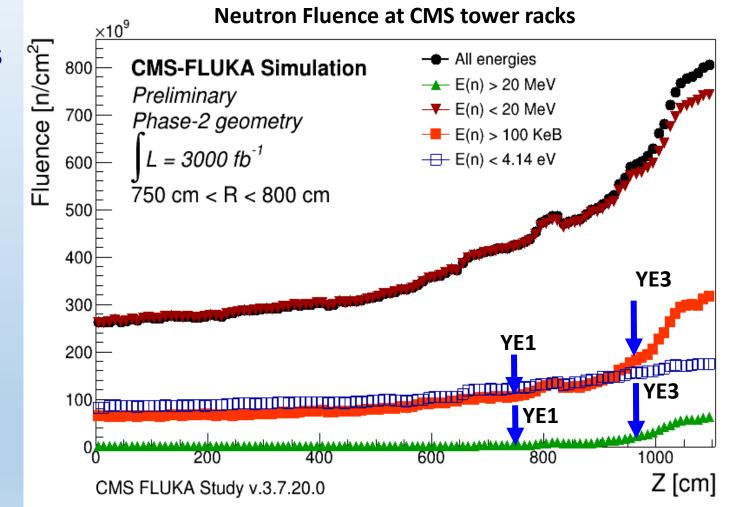

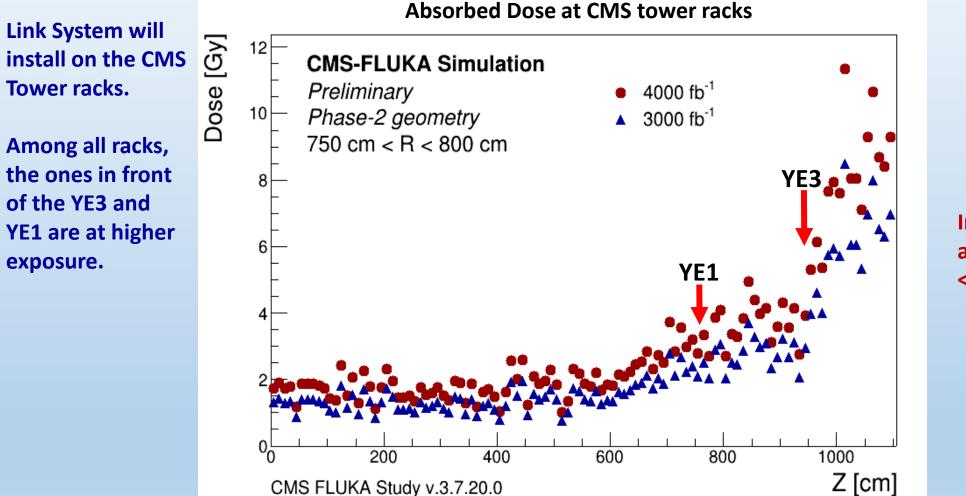

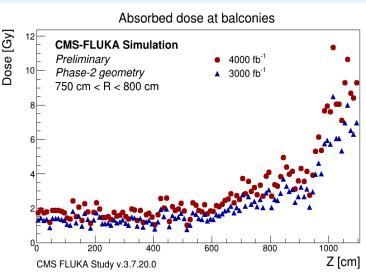

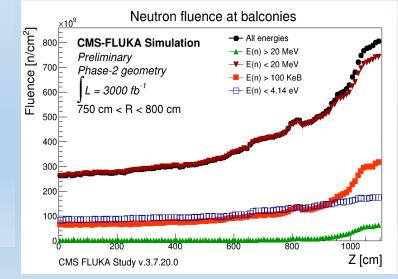

## **Radiation Consideration in HL-LHC**

**Epithermal Neutrons** Fluence at YE3 tower racks < 1.6 x 10<sup>11</sup> n/cm<sup>2</sup>

**20 MeV neutron Fluence** at YE3 tower racks < 2 x 10<sup>10</sup> n/cm<sup>2</sup>

•

## **Radiation Consideration in HL-LHC**

Integrated Dose at YE3 tower racks < <u>6 Gy</u>

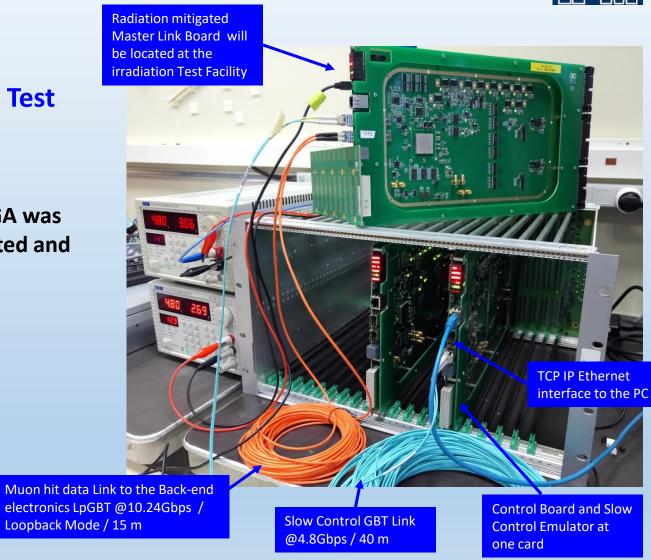

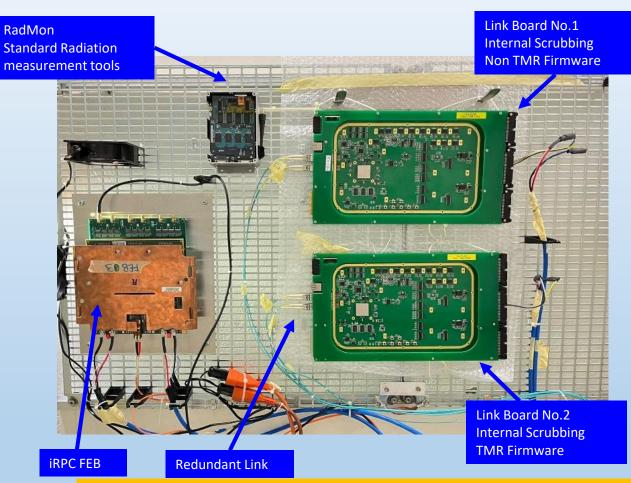

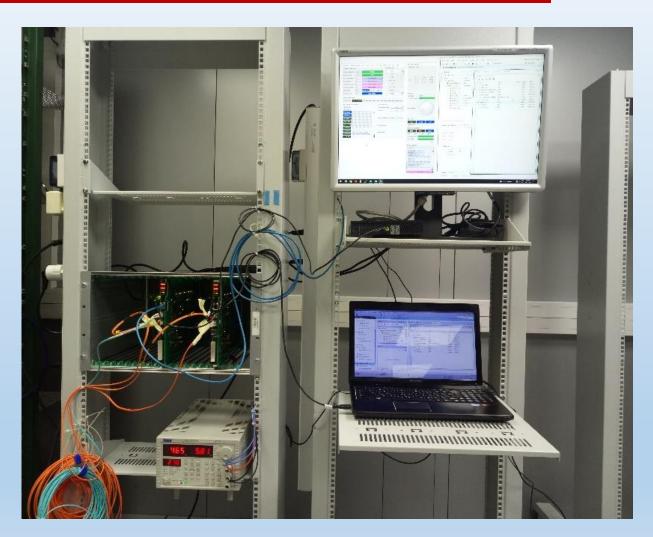

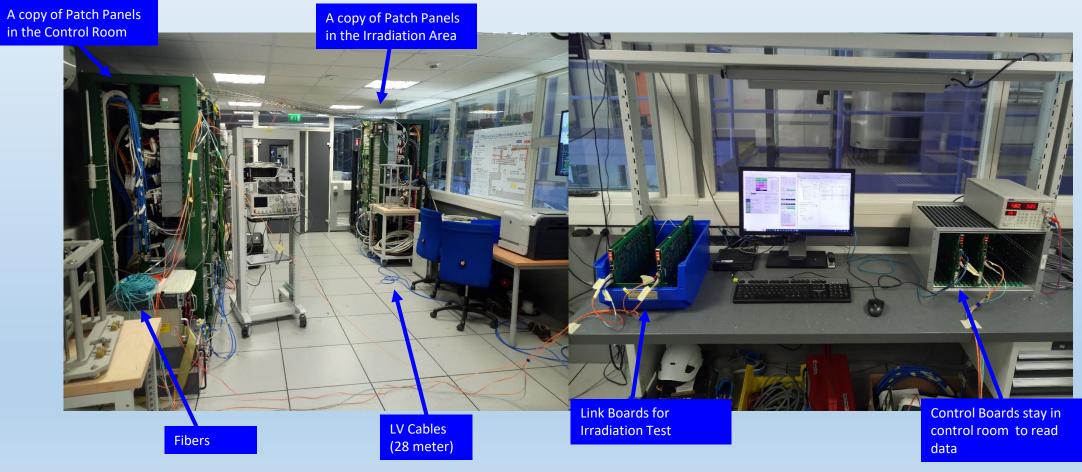

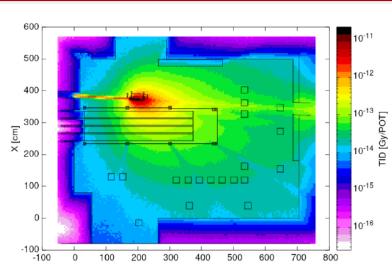

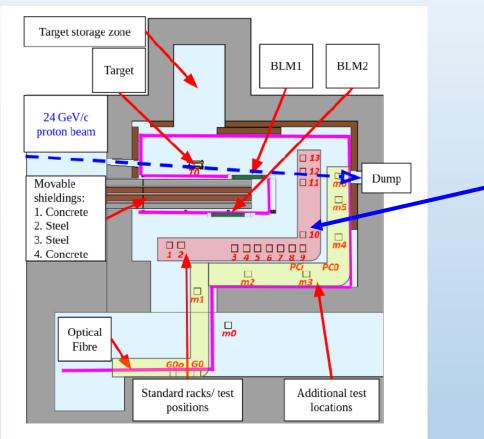

## **Irradiation Test Setup in CHARM**

### **Oct. 12-Nov. 1st: Irradiation Test for**

### 3 weeks

- ✓ CHARM location G0

- ✓ TID: 3.45 Gy/Day

- ✓ Thermal neutron flux:  $2.7 \times 10^5$  (cm<sup>-2</sup> s<sup>-1</sup>)

- ✓ High energy hadron flux:  $1.4 \times 10^5$  (cm<sup>-2</sup> s<sup>-1</sup>)

- ✓ Target for 10 years HL-LHC

- ✓ 4000 fb<sup>-1</sup>

- ✓ Location of Installation on CMS tower racks

- ✓ TID < 6 Gy

- ✓ Total High and Low energy neutron flux

< 1 .8 × 10<sup>3</sup> (cm<sup>-2</sup> s<sup>-1</sup>)

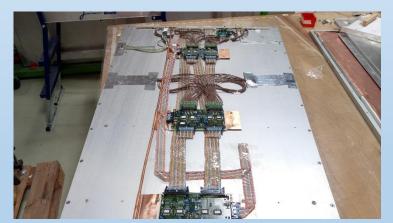

- ✓ Hardware Test Setup on the Charm

- $\checkmark~$  Two Link Boards is chosen for this test.

- ✓ Link Board and Control Board is designed based on the same electronics devices and their circuits are very similar above 90%. For this reason, we decided to test only Link Boards.

- ✓ Each board has a redundant optical Links and an Ethernet interface (added in week 3<sup>rd</sup> of the test)

- ✓ In the Link System, Loss of connection is consider as a failure

Behzad I

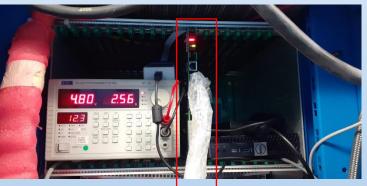

### CAEN power module, set a limit on the current to see the over-current and record the latch-up

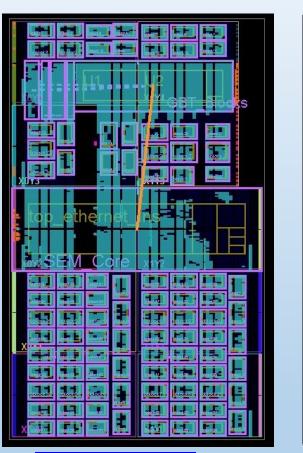

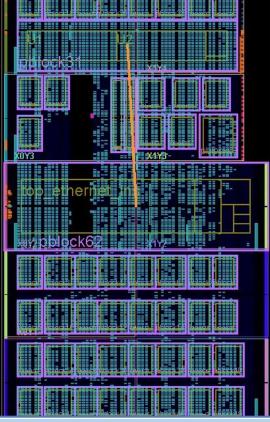

## **Irradiation Test – FPGA Firmware**

- Link Board firmware covers almost all logics and primitives expected to be used for HL-LHC.

- We have evaluated two mitigation techniques on the Link Board FPGAs (Kintex-7 XC7K160T):

- Non-TMR + Internal Scrubbing (SEM)

- TMR + Internal Scrubbing (SEM)

- In both firmware, a test logic block has been replicated over the entire FPGA to increase the chance of the SEUs and precisely evaluate the mitigation methods.

- Ninety-eight test blocks are implemented on the non-TMR firmware, and 37 TMRed test logic blocks are replicated on the TMR firmware.

- Additionally, both firmware comprises two modified GBT-FPGA lanes, automatic link loss detection, and swapping, an Ethernet interface, Clock recovery and Jitter cleaner, and an SEM controller.

Kintex-7, TMR +

**Internal Scrubbing**

Kintex-7, non-TMR + Internal Scrubbing

### **Irradiation Test – Results**

- **Oct. 12-Nov. 1<sup>st</sup> 2022: Irradiation Test Results**

- $\checkmark~$  Electronics running for over three weeks

- ✓ <u>The CHARM dosimetry document Link</u>

- ✓ Total integrated dose (TID): 56.9 Gy

- ✓ Total HEH fluence (cm-2): 1.62 e11

- ✓ Total ThN fluence (cm-2): 3.34 e11

- $\checkmark~$  No latch-up has been seen on the entire electronics

- ✓ Expected #SEU in FPGA CRAM per minutes: 22.1

- ✓ Expected #SEU in FPGA BRAM per minutes: 2.88

- ✓ Rate of SEU detection and correction by SEM at configuration memory: 0.2 s<sup>-1</sup> (12 SEU per minute)

- ✓ For the Link Boards, failure is defined as link loss.

- $\checkmark~$  The power cycling is used to failure recovery

- ✓ MTBF of the Non-TMR firmware + SEM per Link: 250 minutes

- ✓ MTBF of TMR firmware + SEM per link: 250 minutes

- ✓ MTBF extended for HL-LHC condition:

✓ MTBF<sub>HL-LHC</sub> = 250 min ×  $\frac{4.23 \times 10^5 (\text{cm}^{-2} \text{ s}^{-1})}{1.8 \times 10^3 (\text{cm}^{-2} \text{ s}^{-1})}$  = 40.79 days

- ✓ Redundant links make MTBF<sub>HL-LHC</sub> ×2

- ✓ Power Recycling time: 5 sec

- No over-current appeared during the test.

- No permanent damage nor performance degradation detected on the electronics.

- Electronics test results are fulfilled the HL-LHC requirement with following safety factors:

| Item                                                     | CHARM                         | HL-LHC                   | Safety<br>Factor |

|----------------------------------------------------------|-------------------------------|--------------------------|------------------|

| TID (Gy)                                                 | 56.9                          | < 6                      | > 9.33           |

| Total HEH fluence (cm <sup>-2</sup> )                    | 1.62 × 10 <sup>11</sup>       | < 2 × 10 <sup>10</sup>   | > 8.1            |

| Total ThN fluence (cm <sup>-2</sup> )                    | 3.35 × 10 <sup>11</sup>       | < 1.6 × 10 <sup>11</sup> | > 2              |

| Irradiation Flux (cm <sup>-2</sup> s <sup>-1</sup> )     | <b>4.23</b> × 10 <sup>5</sup> | 1.8 × 10 <sup>3</sup>    | 235              |

| #SEU detection and<br>Correction (minute <sup>-1</sup> ) | 12                            | 0.14                     | 85               |

| #days between failure                                    | 0.17                          | 40.79                    |                  |

| # failure per one<br>HL-LHC year                         |                               | 2.45                     |                  |

| # failure in all HL-LHC years                            |                               | 24.5                     |                  |

| Dead time over HL-LHC<br>(sec)                           |                               | 122.5                    |                  |

Collaboration Meeting, 19 June 2024

Behzad Boghrati, CMS RPC Linl

## **Verification in CMS**

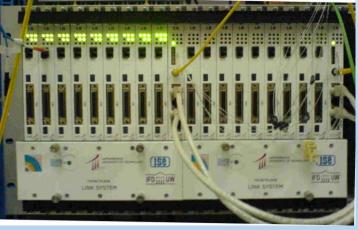

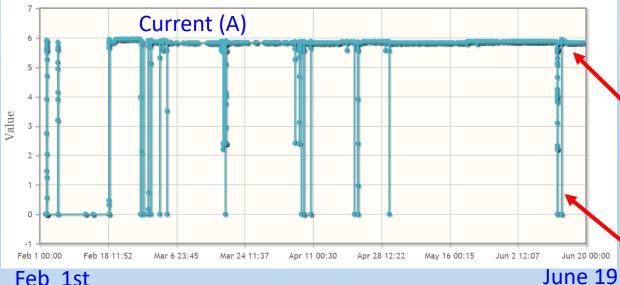

### **RPC Link System status at P5**

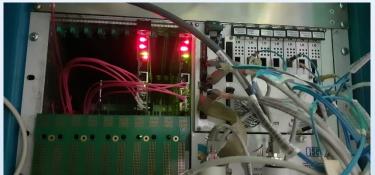

- ✓ The Link board and Control Board installed on the P5 at the beginning of February 2024 are monitored to see their behavior regarding irradiation, magnetic field, and electrical noises. So far, the Link Board and Control Board are pretty stable in real environmental conditions.

- ✓ The firmware Fine-tuning of the Link Board and Control Board is also in progress using remote programming from Tehran.

New Link System (Left) -**Present Link System(Right) Installed at UXC**

**New Slow Control Emulator located at USC**

Stable Current consumption shows stable behavior under real environmental conditions

Link System remote programming from Tehran/Cern

## RPC Firmware Repository - GitLab

### • New Link system Firmware

- 1. Unified Link Board

- 2. Unified Control Board

- 3. Control Board GTX IBERT test

- 4. Link System Irradiation

- 5. User Graphic Interface

- 6. TDC (1.56ns)

- 7. Diagnostic & Histogramming (LB)

- 8. GTX and LpGBT transceiver (Xilinx)

- 9. GTX Fixed Latency data transmission

- **10. FEB Controller**

- **11. Multi Boot Remote Programming**

- **12. Ethernet LAN**

- 13. DDR3 interface Controller

- 14. Soft Error Mitigation Engine (SEM)

- **15. Front Panel Controller**

- 16. TTC Clock Recovery & Phase Shift

- **17. Jitter Cleaner (State Machine Controller)**

- 18. Control & Diagnostic (CB)

- **19. Slow Controller Emulator (SCE)**

- 20. GBT-FPGA for the Control Board

- 21. Triple Modular Redundancy (TMR)

### https://gitlab.cern.ch/cms\_rpc\_muons\_firmware

| Subgroups and projects Shared projects Archived projects                                                  | Search by na Updated date v |

|-----------------------------------------------------------------------------------------------------------|-----------------------------|

| ✓ Se L Link System ⊕                                                                                      | 8•17 Q 0 881 €              |

| v S• U Unified Link Board Firmware  Owner                                                                 | °°1 ()0 861 :               |

| ✓ S● M Master Link Board  Owner Owner                                                                     | °•0 ↓ 1 861                 |

| □ MLBv1 ⊕<br>Unified Master Link Board firmware. The development tool is vivado 2017 ★ 0                  | 2 months ago                |

| <ul> <li>Se C Control Board GTX IBERT Test          Owner</li> </ul>                                      | °•0 Ø3 Å61 ₿                |

| CB-IBERT only-bits ⊕<br>CB IBRET test 5.2G / 8G /10.24G. ★ 0                                              | 2 months ago                |

| CB-IBERT 10.24 G ⊕<br>To test the noise figure and the quality of the GTX line, this code is developed    | 2 months ago                |

| C CB-IBERT 4.8G C<br>To test the noise figure and the quality of the GTX line, this code is developed * 0 | 2 months ago                |

| <ul> <li>v So U Unified Control Board Firmware A Owner</li> </ul>                                         | °°0 () 1 88 1 €             |

| C CBv1 ⊕<br>Unified Control Board firmware supports all types of commands (A/B/C). The                    | 2 months ago                |

### **Summary**

- Progress of the Link System Project is well advanced, and Prototypes are finalized.

- Each Board consumes 12 W. Still, there is room for power consumption reduction.

- The latest version of firmware is available on the RPC repository.

- The irradiation test of the Link System is completed, and the results are satisfactory.

- The electronics meet the HL-LHC radiation condition with high safety factors.

- No permanent damage nor performance degradation appeared on the electronics.

- Number of failures per board for 10 HL-LHC years is 24.5, which means 122.5-sec dead time over 10 HL-LHC years. The overall dead time for full system is 168560-sec.

- This number even would be better by using redundant links.

- The project schedule is protected with well enough floating time.

# •Thank you!

### παιικ γου:

## **Backup Slides**

## **Link Board**

- 1. 14 Layers PCB FR4

- 2. 96 Input Channels. 15 kV ESD protected.

- 3. Twenty-four output channels to inject a signal in the FEB(s) for calibration, a test of the flat cables and connectors.

- 4. Detector Diagnostic and monitoring:

- a. Full/Adjustable window Histograms

- b. RPC Data logging

- c. Timing Histogram

- 5. Muon Hit time information with a time resolution of 1.5 ns.

- 6. Collects 42 hits per Bunch Crossing without any buffer overflow and data loss.

- 7. Transmit 18 hits per Bunch, Crossing to the L1T through a 10 G optical Link.

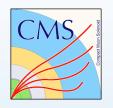

## **New Link Board Hardware Architecture**

- The design specifications and components:

- 1. FPGAs are KINTEX7, XC7K160T-2FFG676I.

- 2. Fully support 10.3 Gbps data transmission. FPGA Chip is equipped with a heat sink.

- 3. High-resolution TDCs (at the steps of 1.56 ns) implemented into the Kintex7 FPGA

- 4. <u>Two Redundant optical data transmission lines at the data rate</u> of 10.24 Gbps

- 5. Ethernet link for the debugging and onboard JTAG programmer

- 6. <u>256 M x 40 bits</u> of SDRAM-DDR3 for data buffering and debugging

- 7. Data transmission with adjacent slave link boards through the SAMTEC back-plane type connector with a bandwidth of <u>16 GHz</u> and front panel PCB board.

- 8. Radiation Mitigation is based on Triple Modular Redundancy (TMR) techniques and Soft Error Mitigation (SEM) IP core from Xilinx.

- 9. Voltage Regulators selected from low dropout linear regulator families <u>have already been tested under radiation</u>.

Behzad Boghrati, CMS RPC Link System, 2nd DRD1 Collaboration Meeting, 19 June 2024

Behzad Boghrati, CMS RPC Link System, 2nd DRD1

Collaboration Meeting, 19 June 2024

## **RPC Phase-2 Upgrade Architecture and Layer-1**

SLB: Slave Link Board MLB: Master Link Board CB: Control Board B/O/E MTF: Barrel/ Overlap/ Endcap Muon Track Finder

## **RPC LB Link structure**

- Latency

- RPC + Cable = 9 BX,

- LB = 11-20 BX,

- Fiber 110m = 22 BX.

- Optics

- Standard Short Range 10G-SR-SFP+.

- Fiber type = OM4.

- Protocols (low-level data)

- Optical encoding (bits) = FEC 5.

- General Frame specs

- Size = 256 bits

- Header = 2 bit.

- FEC5 = 20 bit.

- User data = 234 bit.

## **RPC Link structure in the Barrel**

#### • The link between RPC to BMT-L1

- one-way direction.

- Total number of Links = 300.

- Number of links per sector = 5.

- The link bandwidth = 10.24 Gbps.

- Data transmission Protocol = LpGBT.

- Firmware = Customized version of LpGBT-FPGA.

- Type of data synchronization = Asynchronous.

- Type of FEC = FEC 5.

- Object

- Object name = hit.

- Object size = 11 bits.

- Object fields name = Fired Strip number (7 bits), Sub-BX (4 bits)

## **RPC Link structure in the Endcap**

#### The link between MLB to RECF

- one-way direction.

- Total number of Links = 192.

- The link bandwidth = 10.24 Gbps.

- Data transmission Protocol = LpGBT.

- Firmware = Customized version of LpGBT-FPGA.

- Type of data synchronization = Asynchronous.

- Type of FEC = FEC 5.

- Object

- Object name = hit.

- Object size = 11 bits.

- Object fields name = Fired Strip number (7 bits), Sub-BX (4 bits)

## The RPC Data Payload to Layer-1

#### Payload on the Barrel

- Maximum payload per Link = 0.811 Gbps

- Maximum Payload per Sector = 4.055 Gbps

- Maximum Payload in Barrel = 243.3 Gbps

- Payload on the Endcap

- Maximum payload per Link = 0.546 Gbps

- Maximum Payload in Endcap = 104.8 Gbps

- Fiber Mapping

- The same as present Link System

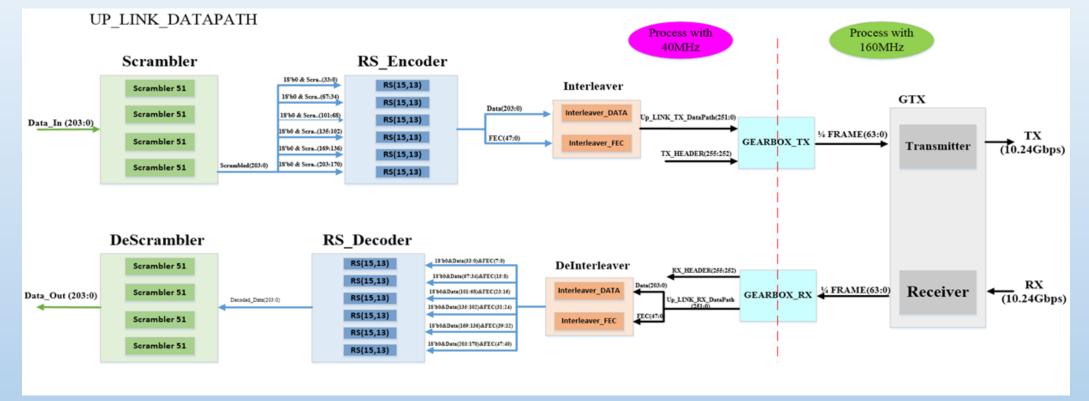

# **RPC Link System for Phase-2**

#### • Transceiver Architecture

- ✓ In the scrambler avoiding long sequences of bits of the same level helps GTX distinguish each bit's boundary.

- ✓ Using Reed-Solomon, by adding redundancy to each packet, will have the possibility to correct defects.

- ✓ Using Interleaver by distributing defects in a frame makes FEC more robust.

#### Total Number of CBs, MLBs, SLBs in <u>Barrel</u> Required Optical Links for Link System Phase-2 Upgrade

| 2  |       |          |         |    |    | Nun | nber of | f Maste  | er Link  | Board   | s in Ea | ch Seo | tors |     |     |                     |                       |                    |

|----|-------|----------|---------|----|----|-----|---------|----------|----------|---------|---------|--------|------|-----|-----|---------------------|-----------------------|--------------------|

| 3  | WHEEL | Chambers | SECTORS | S1 | S2 | S3  | S4      | S5       | S6       | S7      | S8      | S9     | S10  | S11 | S12 | Total Number of MLB | Optical Links<br>(SX) | SX = Single Fiber  |

| 4  | RB+2  | 96       | 12      | 5  | 5  | 5   | 5       | 5        | 5        | 5       | 5       | 5      | 5    | 5   | 5   | 60                  | 60                    |                    |

| 5  | RB+1  | 96       | 12      | 5  | 5  | 5   | 5       | 5        | 5        | 5       | 5       | 5      | 5    | 5   | 5   | 60                  | 60                    |                    |

| 6  | RB0   | 96       | 12      | 5  | 5  | 5   | 5       | 5        | 5        | 5       | 5       | 5      | 5    | 5   | 5   | 60                  | 60                    |                    |

| 7  | RB-1  | 96       | 12      | 5  | 5  | 5   | 5       | 5        | 5        | 5       | 5       | 5      | 5    | 5   | 5   | 60                  | 60                    |                    |

| 8  | RB-2  | 96       | 12      | 5  | 5  | 5   | 5       | 5        | 5        | 5       | 5       | 5      | 5    | 5   | 5   | 60                  | 60                    |                    |

| 9  |       | 480      |         |    |    |     |         |          |          |         |         |        |      |     |     | 300                 | 300                   | MLB OUTPUTS        |

| 10 |       |          |         |    |    | Nu  | mber o  | of Salve | e Link E | Boards  | in Eac  | h Sect | tors |     |     |                     |                       |                    |

| 11 | WHEEL | Chambers | SECTORS | S1 | S2 | S3  | S4      | S5       | S6       | S7      | S8      | S9     | S10  | S11 | S12 | Total Number of SLB |                       |                    |

| 12 | RB+2  | 96       | 12      | 8  | 8  | 8   | 10      | 8        | 8        | 8       | 8       | 8      | 10   | 8   | 8   | 100                 |                       |                    |

| 13 | RB+1  | 96       | 12      | 8  | 8  | 8   | 10      | 8        | 8        | 8       | 8       | 8      | 10   | 8   | 8   | 100                 |                       |                    |

| 14 | RB0   | 96       | 12      | 8  | 8  | 8   | 10      | 8        | 8        | 8       | 8       | 8      | 10   | 8   | 8   | 100                 |                       |                    |

| 15 | RB-1  | 96       | 12      | 8  | 8  | 8   | 10      | 8        | 8        | 8       | 8       | 8      | 10   | 8   | 8   | 100                 |                       |                    |

| 16 | RB-2  | 96       | 12      | 8  | 8  | 8   | 10      | 8        | 8        | 8       | 8       | 8      | 10   | 8   | 8   | 100                 |                       |                    |

| 17 |       |          |         |    |    |     |         |          |          |         |         |        |      |     |     | <br>500             |                       |                    |

| 18 |       |          |         |    |    | N   | umber   | of Con   | trol B   | oards i | n Each  | Secto  | ors  |     |     |                     |                       |                    |

| 19 | WHEEL | Chambers | SECTORS | S1 | S2 | S3  | S4      | S5       | S6       | S7      | S8      | S9     | S10  | S11 | S12 | Total Number of CB  | Optical Link<br>(DX)  | DX = Double Fibers |

| 20 | RB+2  | 96       | 12      | 2  | 2  | 2   | 2       | 2        | 2        | 2       | 2       | 2      | 2    | 2   | 2   | 24                  | 24                    |                    |

| 21 | RB+1  | 96       | 12      | 2  | 2  | 2   | 2       | 2        | 2        | 2       | 2       | 2      | 2    | 2   | 2   | 24                  | 24                    |                    |

| 22 | RB0   | 96       | 12      | 2  | 2  | 2   | 2       | 2        | 2        | 2       | 2       | 2      | 2    | 2   | 2   | 24                  | 24                    |                    |

| 23 | RB-1  | 96       | 12      | 2  | 2  | 2   | 2       | 2        | 2        | 2       | 2       | 2      | 2    | 2   | 2   | 24                  | 24                    |                    |

| 24 | RB-2  | 96       | 12      | 2  | 2  | 2   | 2       | 2        | 2        | 2       | 2       | 2      | 2    | 2   | 2   | 24                  | 24                    |                    |

| 25 |       |          |         |    |    |     |         |          |          |         |         |        |      |     |     | 120                 | 120                   | CB Control Link    |

#### Total Number of CBs, MLBs, SLBs in <u>Endcap</u> Required Optical Links for Link System Phase-2 Upgrade

| 30 |      |          |         |    |    | Nur | mber o | f Maste  | er Link  | Board | ds in Ea | ach Se     | ctors |      |      |                  |                     |                    |

|----|------|----------|---------|----|----|-----|--------|----------|----------|-------|----------|------------|-------|------|------|------------------|---------------------|--------------------|

| 31 | DISK | chambers | SECTORS | S1 | S2 | S3  | S4     | S5       | S6       | S7    | S8       | S9         | S10   | S11  | S12  |                  | Total Number of MLB | SX = Single Fiber  |

| 32 | RE+4 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 33 | RE+3 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 34 | RE+2 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 35 | RE+1 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 36 | RE-1 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 37 | RE-2 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 38 | RE-3 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 39 | RE-4 | 72       | 12      | 2  | 2  | 2   | 2      | 2        | 2        | 2     | 2        | 2          | 2     | 2    | 2    |                  | 24                  |                    |

| 40 |      | 576      |         |    |    |     |        |          |          |       |          |            |       |      |      |                  | 192                 | MLB OUTPUTS        |

| 41 |      |          |         |    |    |     |        |          |          |       |          |            |       |      |      |                  |                     |                    |

| 42 |      |          |         |    |    | Nu  | mber ( | of Slave | e Link I | Board | s in Ea  | ch Sec     | tors  |      |      |                  |                     |                    |

| 43 | DISK | chambers | SECTORS | S1 | S2 | S3  | S4     | S5       | S6       | S7    | S8       | S9         | S10   | S11  | S12  |                  | Total Number of SLB |                    |

| 44 | RE+4 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 45 | RE+3 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 46 | RE+2 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 47 | RE+1 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 48 | RE-1 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 49 | RE-2 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 50 | RE-3 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 51 | RE-4 | 72       | 12      | 4  | 4  | 4   | 4      | 4        | 4        | 4     | 4        | 4          | 4     | 4    | 4    |                  | 48                  |                    |

| 52 |      | 576      |         |    |    |     |        |          |          |       |          |            |       |      |      |                  | 384                 |                    |

| 53 |      |          |         |    |    | N   | lumber | r of Cor | ntrol B  | oards | in Eac   | h Sect     | ors   |      | 1    |                  |                     |                    |

| 54 | DISK | chambers | SECTORS | S1 | S2 | S3  | S4     | S5       | S6       | S7    | S8       | S9         | S10   | S11  | S12  |                  | Total Number of CB  | DX = Double Fibers |

| 55 | RE+4 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 56 | RE+3 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 57 | RE+2 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 58 | RE+1 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 59 | RE-1 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 60 | RE-2 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 61 | RE-3 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | 1        | 1          | 1     | 1    | 1    |                  | 12                  |                    |

| 62 | RE-4 | 72       | 12      | 1  | 1  | 1   | 1      | 1        | 1        | 1     | . 1 h    | 1 <b>1</b> | 1     | 1    | 1    | <del>, 2nd</del> | 12                  |                    |

| 63 |      | 576      |         |    | l  |     | B      |          |          |       |          |            |       |      |      |                  | 96 DKD1             | CB Control Link    |

|    |      |          | -       |    | -  |     |        |          | Colla    | abor  | ation    | Me         | eting | , 19 | June | 2024             |                     |                    |

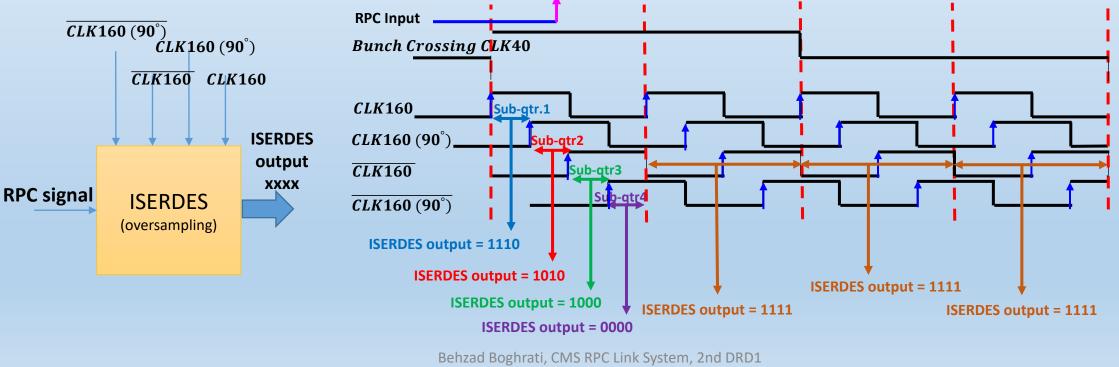

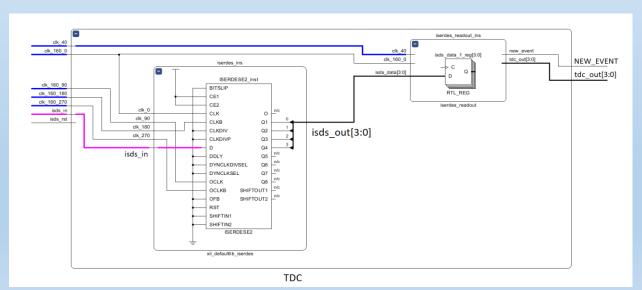

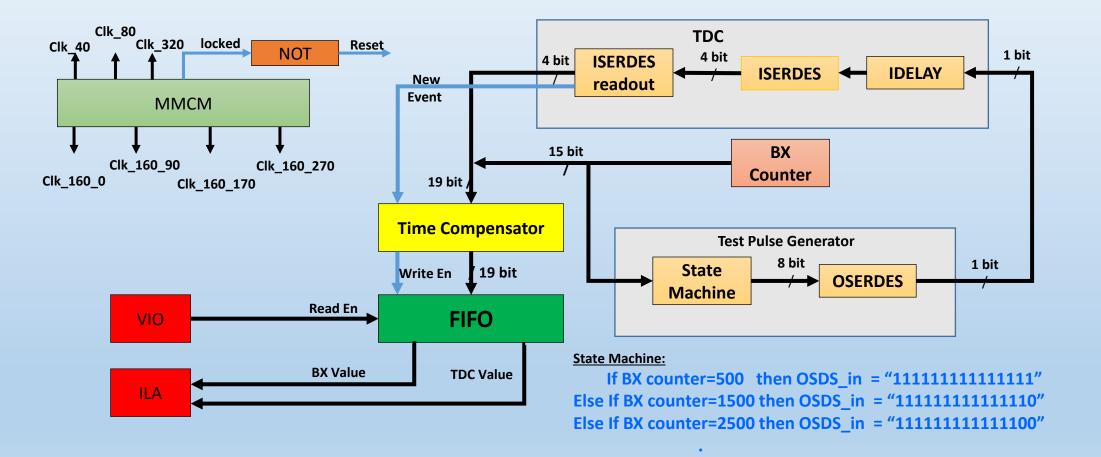

## **RPC data processing – Time-Stamping**

- RPC signals time-Stamping on RPC hits

- Time-to-Digital Converter (TDC)

- In TDC the first stage is the Input Serial/De-serial (ISERDES) DIGITIZAER unit.

- It needs four Clocks, four times higher than the reference clock (Bunch Crossing). Take four samples on every quarter of the reference Clock

- ISERDES is a hardware built-in component inside the FPGA

- The main function of ISERDES is to serialize the RPC input signal at the specific sampling rate

- The output of the ISERDES is four bits code

Collaboration Meeting, 19 June 2024

# **RPC data processing – Time-Stamping**

CMS

Collaboration Meeting, 19 June 2024

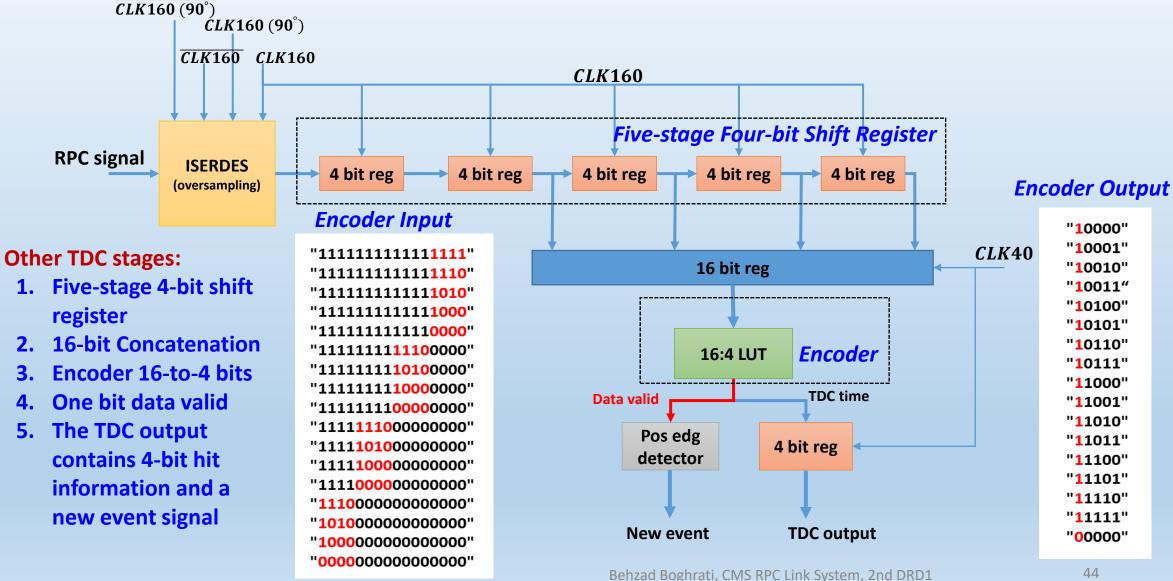

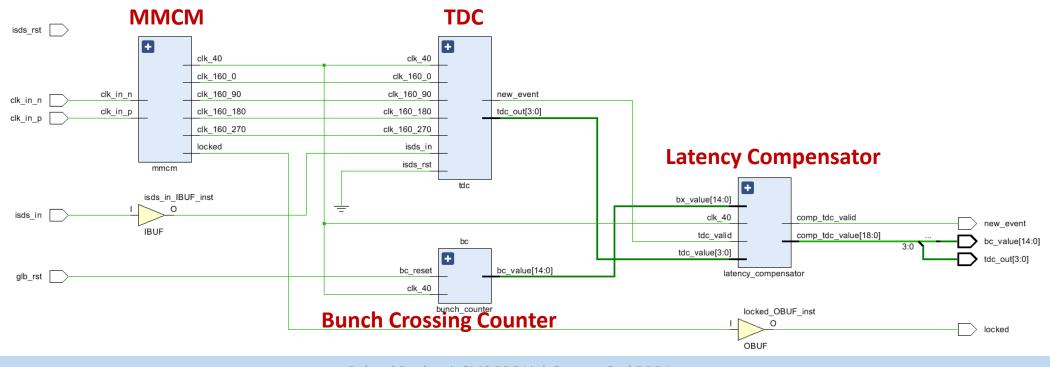

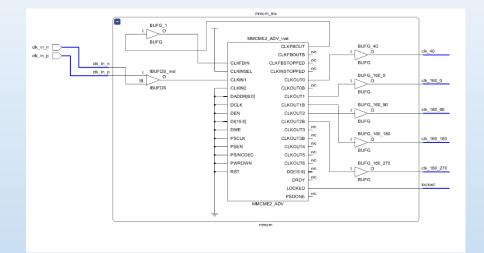

## **Time-Stamping – FPGA Implementation**

- Time-Stamping stages in FPGA:

- 1. MMCM generate four-phase shifted clocks at frequency of 160 MHz

- 2. Time-to-Digital Converter, fine-time measurement.

- 3. Bunch Crossing Counter is implemented by a 15-bit Counter, coarse time measurement.

- 4. TTC Clock Latency and RPC signal propagation delay are compensated by the Latency Compensation unit.

## **Time-Stamping – TDC Transfer Function**

# **Time-Stamping – TDC Transfer Function**

CMS

### **Time-Stamping – Validation**

## **Time-Stamping – Validation**

|                       |         |           | 119,996.300 ns | 5       |             |         |                  |        |                         |       |             |               |          | 120,095.764                          | ns                                      |

|-----------------------|---------|-----------|----------------|---------|-------------|---------|------------------|--------|-------------------------|-------|-------------|---------------|----------|--------------------------------------|-----------------------------------------|

| Name                  | Value   | 119,990 r | s 120,000 :    | ns  120 | ),010 ns  1 | 120,020 |                  |        | ns <sub>1</sub> 120,050 |       |             | 0 ns  120,080 | ns  120, | .090 ns 120,10                       |                                         |

| 14 locked             | 1       |           |                |         |             |         |                  | TD     | C Clk 1                 | 60 MH | Z           |               |          |                                      |                                         |

| <sup>™</sup> clk_in_p | 0       |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

| 🖁 clk_in_n            | 1       |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

| Ъ isds_rst            | 0       |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

| Ъ glb_rst             | 1       |           | .HC Clk        |         |             | ТН      |                  |        | ub-BX                   |       |             |               |          |                                      |                                         |

| 🔓 tb_glb_rst          | 1       |           |                |         |             | -       |                  |        |                         |       |             |               |          |                                      |                                         |

| 1 tb_clk_40           | 1       |           |                |         |             |         |                  |        |                         |       |             | 1             |          |                                      |                                         |

| 🔓 tb_counter          | 4400    | 40        | 4400           |         | X           | 440     |                  |        | 4402                    |       |             | 403           |          | 4404                                 | 4405                                    |

| 🔓 sub_bx_counter      | 5       |           | <u>}</u>       |         | <u> </u>    | 5/6/7/  | <u>₽∕₽∕₽∕₽∕₽</u> |        | ৻৾৾৾৾ৼ৾৾৻৽৾৾৻ৼ৾৾৾৻ৼ৾৾৾৻ |       | 2/3/4/5/6/7 | ፞፞ጞቔ፞ጞቇጞ፼ጞ፼ጞቔ |          | 3 <b>\4)<mark>5\6\7\8\9\</mark>t</b> | Ŋ <mark>ᡚ</mark> ᡚᡚᡚᡚᡚ᠙ᡘ᠋ᢤᢓᡘᢃ᠂᠍ᡧᢄᢣᢄᠵ᠋ᢆᢓ |

| 🔓 isds_in             | 1       |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

| 🔓 tdc_in              |         |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      | TDC Output                              |

| 🕌 idly_in             | RPC II  | nput 🖊    |                |         |             |         |                  |        |                         |       |             |               |          |                                      | Sub-BX                                  |

| ₩ idly_out            | mom     | ent 📃     |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

| 🔓 new_event           | ľ       |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

| > 😽 tdc_out[3:0]      | 9       |           |                |         |             |         |                  | 9      |                         |       |             |               |          | þ                                    | 5                                       |

| 14 tdc_time           | 9       |           |                |         |             |         |                  | 9      |                         |       |             |               |          |                                      | 5                                       |

| > 😽 bc_value[14:0]    | 4395    | 4394      |                | 4395    |             | XÞ      | 4396             |        | X                       | 4397  | X           | 4398          |          | <u>,</u>                             | 4400                                    |

| 16 bc_val_integer     | 4395    | 4394      |                | 4395    |             | K       | 4396             |        | X                       | 4397  | Ж           | 4398          |          |                                      | 4400                                    |

| la dly_time           | 8800 ps | 8700 ps   |                |         |             |         |                  |        |                         |       | 8800 ps     |               |          |                                      |                                         |

| > WINLW_IDELTED[4:    | 0] 20   |           |                |         |             |         |                  |        |                         | 21    |             |               |          | TDC Out                              | put BX                                  |

|                       |         |           | -99.464 ns     |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

|                       |         | -110 ns   |                | -90 ns  | -80 ns      |         |                  | -60 ns | -50 ns                  |       | -30 ns      | -20 ns        | -10 ns   | 0 ns                                 | 10 ns 20 ns 31                          |

|                       |         |           |                |         |             |         |                  |        |                         |       |             |               |          |                                      |                                         |

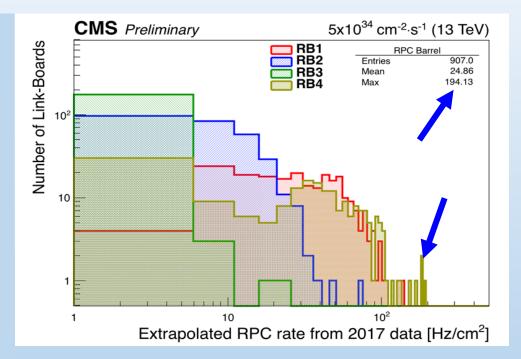

## Maximum Expected Event payload in the Barrel

- Expected Max hit rate in Barrel in HL-LHC , safety factor 3: 600 cm<sup>-2</sup>. s<sup>-1</sup>

- Biggest Strip surface area : 120 × 3 cm<sup>2</sup>

- Average cluster size: -

- Number of Strip per chamber : 96

- Max Single hit in one LB per BX : 600 x (120 x 3) x 96 x 25 X 10<sup>-9</sup>= 0.52 hit /LB x bx

- One Link covers three Link Boards

- Max Single hit on Link per bx : 0.52 × 3 = 1.56 hit /Link . BX

- Size of hit : 13 bits/hit (Yellow box)

- MLB Max. Event Payload: 13 bits/hit × 1.56 hits/Link . BX = 20.28 bits /Link . BX

•

= 20.28  $\times$  40  $\times$  10<sup>6</sup> bit/s = 0.811  $\times$  10<sup>9</sup> bit/s

- Total number of link in the Barrel : 300

- Total number of event payload in the Barrel : 6084 bits /BX = 760.5 Byte /BX

- Maximum throughput :  $20.28 \times 300 \times 40 \times 10^6$  bit/s =  $0.24336 \times 10^{12}$  bit/s

One Event = Size of the data corresponding to one bunch crossing

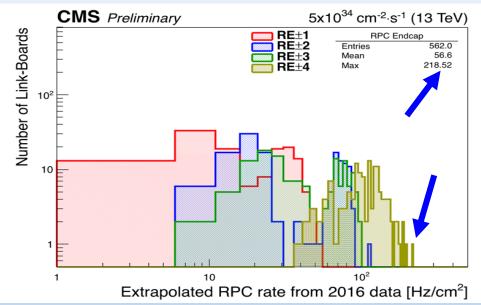

## Maximum Expected Event payload in the Endcap

• Expected Max hit rate in Endcap in HL-LHC , safety factor 3: 700 cm<sup>-2</sup>. s<sup>-1</sup>

- Biggest Strip surface area : 66 × 3.125 cm<sup>2</sup>

- Average cluster size: -

- Number of Strip per chamber : 96

- Max Single hit in one LB per BX : 700 x (66 × 3.125) × 96 × 25 × 10<sup>-9</sup> = 0.35 hit /LB . BX

- One Link covers three Link Boards

- Max Single hit on Link per bx : 0.35 × 3 = 1.05 hit /Link . BX

- Size of hit : 13 bits/hit (Yellow box)

- MLB Max. Event Payload: 13 bits/hit × 1.05 hits/Link . BX = 13.65 bit / Link . BX

=  $13.65 \times 40 \times 10^6$  bit/s =  $0.546 \times 10^9$  bit/s

- Total number of link in the Endcap : 192

- Total number of event payload in the Endcap = 2620 bit/BX = 327 Byte/BX

- Maximum throughput =  $13.65 \times 192 \times 40 \times 10^6$  bit/S =  $0.1048 \times 10^{12}$  bit/S

One Event = Size of the data corresponding to one bunch crossing

## **Radiation Consideration**

- The Link system will be installed on the Balcony of CMS, where the rates are even lower than what we have at the periphery of the detector.

- Total Irradiation Dose at most is 10 Gy @ 3000fb<sup>-1</sup>

- Neutron Flux at the CMS Balcony is 1x10<sup>4</sup> cm<sup>-2</sup>s<sup>-1</sup> @5 x 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Neutron Fluence for 10 HL-LHC years is 8x10<sup>11</sup> cm<sup>-2</sup>

- The new Link board components has been chosen from COTS which are validated for radiation at the level of **300 Gy**

- The FPGA TID KINTEX-7 (XC7K160T) is 3400-4500 Gy

- Scrub Time of entire FPGA (Real time SEU detection and Correction) : 13ms

- The Single Event upset (SEU) rate on configuration memory is 1 SEU every 413 sec. and 1 SEU every 1695 sec. at Block RAM

- <u>TMR</u> and <u>Configuration Scrubbing</u> will mitigate the SEUs

## **Radiation Consideration Estimation of SEU on the KINTEX-7 XC7K160T Configuration and BRAM Memories**

| <ul> <li>Number of Errors = 6<sub>CRAM</sub> × Flux × T<sub>irrd</sub> × N<sub>CRAM</sub></li> <li>6<sub>CRAM</sub> = Cross section of the Single Event upset of each bit at the configuration Memory (cm<sup>2</sup> bit<sup>-1</sup>)</li> </ul> | Integrated Errors due to SEU at the<br>Configuration Memory of KINTEX-7<br>XC7K160T                                                                                                                                                                                                                                           | Integrated Errors due to SEU at the<br>BLOCK RAM Memory of KINTEX-7<br>XC7K160T<br>$O_{DRAM} = 5.07 \times 10^{15} \text{ cm}^2 \text{ bit}^1$<br>Flux = 1 x 10 <sup>4</sup> cm <sup>-2</sup> s <sup>-1</sup><br>Time of Exposure = 1 sec<br>N <sub>BRAM</sub> = 11,700,000 bits<br>$E_{BRAM} = 0.00059$ at 1 second<br>$E_{BRAM} = 0.036$ at 1 minute<br>$E_{BRAM} = 2.135$ at 1 hour |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Flux = Number of Neutron pre squire centimeter per second</li> <li>T<sub>irrd</sub> = Irradiation Time</li> <li>N<sub>CRAM</sub> = number of bits at the Configuration Memory</li> </ul>                                                  | $G_{CRAM} = 4.52 \times 10^{-15} \text{ cm}^2 \text{ bit}^{-1}$<br>Flux = 1 x 10 <sup>4</sup> cm <sup>-2</sup> s <sup>-1</sup><br>Time of Exposure = 1 sec<br>N <sub>CRAM</sub> = 53,540,576 bits<br>E <sub>CRAM</sub> = 0.00242 at 1 second<br>E <sub>CRAM</sub> = 0.1452 at 1 minute<br>E <sub>CRAM</sub> = 8.712 at 1 hour |                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Scrubbing time (13 ms)                                                                                                                                                                                                                             | 1 SEU every 413 seconds         SEU Time In         Time (Second)                                                                                                                                                                                                                                                             | 1 SEU every 1694 seconds terval >> Scrubbing time                                                                                                                                                                                                                                                                                                                                      |  |  |

Benzad Bognrati, CIVIS RPC LINK System, 2nd DRD1 Collaboration Meeting, 19 June

# **RPC Link System- CHARM Irradiation result**

#### Irradiation test: 12 Oct. – 1 Nov. 2022

|                   | TID     | НеН                       | N1MeV                      | ThN                       | POT      | DD/TID                                      | Rfactor  |

|-------------------|---------|---------------------------|----------------------------|---------------------------|----------|---------------------------------------------|----------|

| 1) RUN #28 (USER) | 19.1 Gy | 5.35e+10 cm <sup>-2</sup> | -2.86e+07 cm <sup>-2</sup> | 1.17e+11 cm <sup>-2</sup> | 1.44e+16 | -1.49e+06 cm <sup>-2</sup> Gy <sup>-1</sup> | 2.189445 |

| 2) RUN #29 (USER) | 16.9 Gy | 4.89e+10 cm <sup>-2</sup> | 2.20e+11 cm <sup>-2</sup>  | 9.95e+10 cm <sup>-2</sup> | 1.42e+16 | 1.30e+10 cm <sup>-2</sup> Gy <sup>-1</sup>  | 2.033706 |

| 3) RUN #30 (USER) | 17.9 Gy | 5.05e+10 cm <sup>-2</sup> | 2.90e+11 cm <sup>-2</sup>  | 1.00e+11 cm <sup>-2</sup> | 1.46e+16 | 1.62e+10 cm <sup>-2</sup> Gy <sup>-1</sup>  | 1.980232 |

| Final value       | 54.0 Gy | 1.53e+11 cm <sup>-2</sup> | 5.11e+11 cm <sup>-2</sup>  | 3.17e+11 cm <sup>-2</sup> | 4.33e+16 | 9.74e+09 cm <sup>-2</sup> Gy <sup>-1</sup>  | 2.067794 |

# RPC Link System- Installation in Control Room at CHARM

- Two Redundant readout

- In this setup two Control Boards emulate the Backend electronics functionalities

## **CHARM Preparation Area**

#### September 2022: Dry-Run test for one week

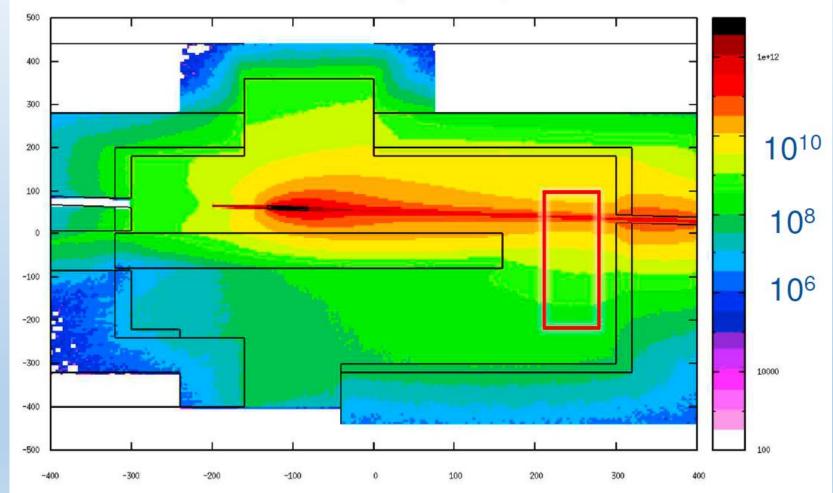

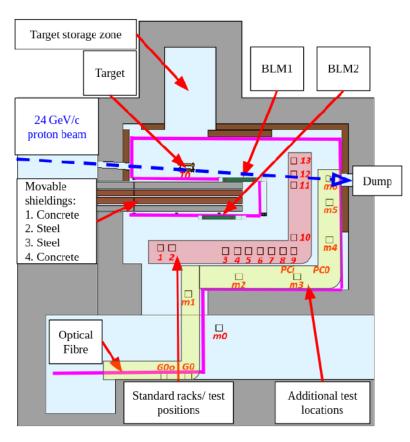

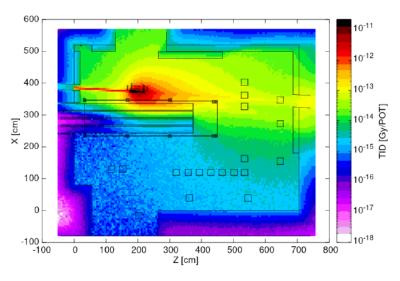

# The CHARM Radiation Environment

HEH flux (cm<sup>-2</sup>h<sup>-1</sup>)

In the downstream locations (10-13) HEH fluxes of ~10<sup>10</sup> cm<sup>-2</sup>h<sup>-1</sup> (roughly one year in the LHC tunnel) can be reached in one hour

# The CHARM Radiation Environment

of the mixed-field environment, is that of a quasi-uniform spill lasting roughly 350 ms, which is repeated every 10 seconds. Although this would indeed be a pulsed beam for

Fig. 1: Top view of FLUKA geometry of the CHARM test area. Two BLMs are installed at 1 m above beam height, one next to the target and one behind the movable shieldings. There

The simulated 2D TID distribution at beam height is shown for two configurations: CuOOOO (top) and CuCSSC (bottom). Paper Link

# The CHARM Radiation Environment

Fig. 1: Top view of FLUKA geometry of the CHARM test area. Two BLMs are installed at 1 m above beam height, one next to the target and one behind the movable shieldings. There TABLE I: Maximum and weekly maximum integrated rates at CHARM for the Total Ionizing Dose, and the thermal neutron equivalent and high-energy hadron Fluences, obtained at the R10 location based on FLUKA simulations.

| Quantity                   | Maximum<br>Rate                                 | Integrated Rate<br>(per week)        |

|----------------------------|-------------------------------------------------|--------------------------------------|

| Total Ionizing Dose        | 2.70 Gy/h                                       | 360 Gy                               |

| Thermal neutron fluence    | $3 \times 10^{6} \text{ cm}^{-2} \text{s}^{-1}$ | $1.5 \times 10^{12} \text{ cm}^{-2}$ |

| High-energy hadron fluence | $1.5 \times 10^6 \text{ cm}^{-2} \text{s}^{-1}$ | $8 \times 10^{11} { m cm}^{-2}$      |