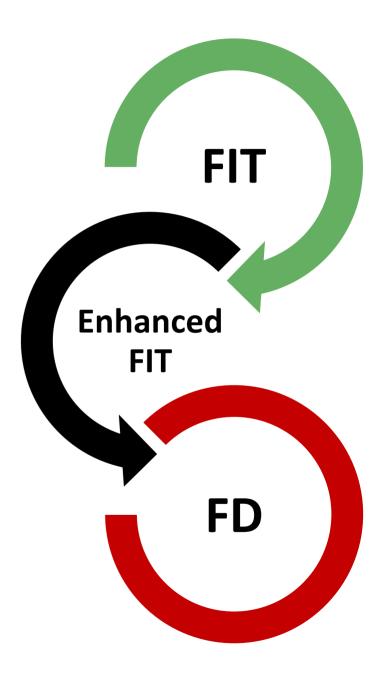

# FIT FEE upgrade for the future ALICE 3 FD detectors

at AGH University of Krakow

I. Brzozowski, M. Gąsiorowski, M. Grzegorzek, M. Jabłoński, J.Kitowski, A. Kopyto,S. Koryciak, J. Kowalewski, A. Laczewski, J. Miszczyński, J. Otwinowski, W. Pierożak, K. Płonka, Ł. Przustupa, <u>P. Russek</u>, O. Savchenko, J. Stelmach, F. Urbański, P. Wiącek, C. Worek, H. Zaśko

#### Main activities at AGH

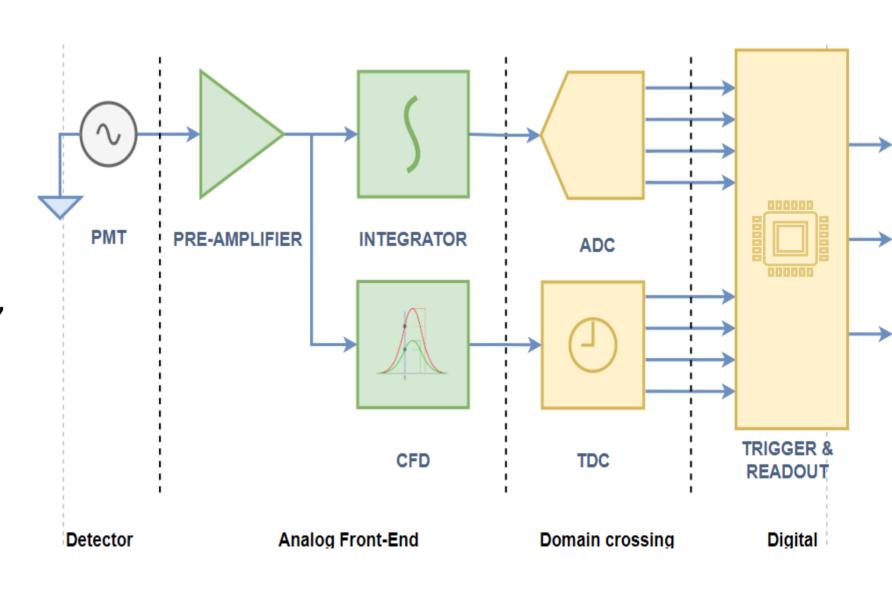

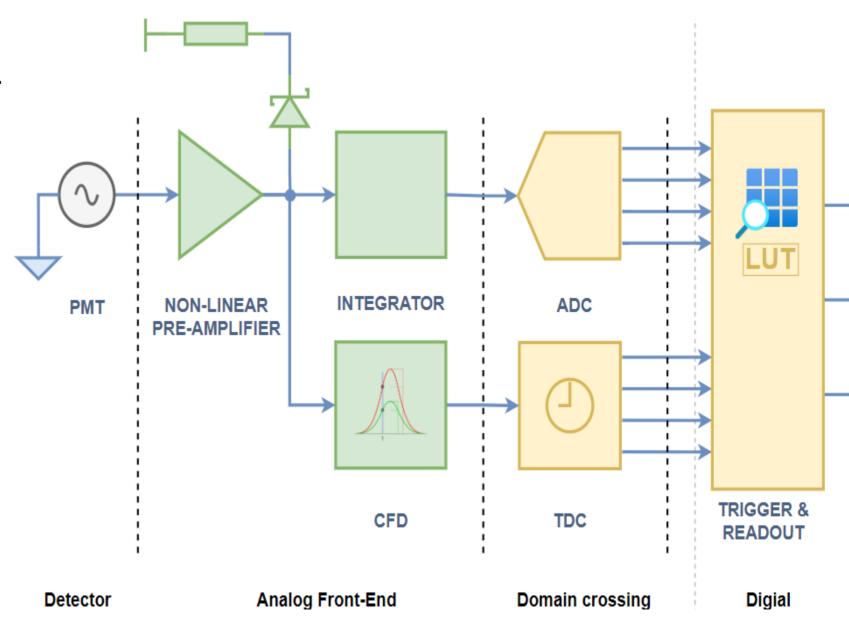

- Enhancement of analog front-end FIT readout electronics:

- goal to achieve measurments with:

- 14 bit charge resolution,

- system RMS jitter < 20 ps.</li>

- the pre-amplifier improvement for better signal dynamics

- new architecture of the charge integrator to increase precision,

- launch of the ASIC project to increase overall AFE performance.

- High frequency direct sampling of PMT signal

- AGH University group focuses on analog front-end

- Goal is to increase:

- overall system time resolution <20 ps,</li>

- detector signal range,

- Precision (14-bit)

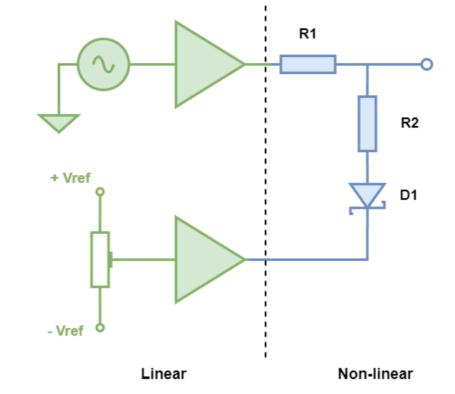

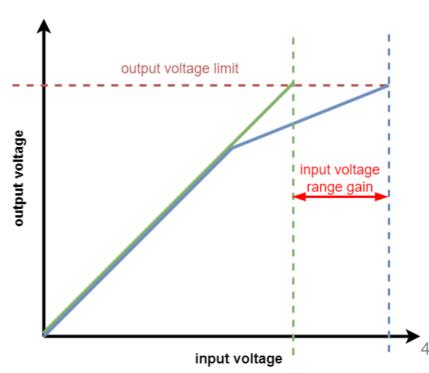

#### Non-linear pre-amplifier

Allows us to increase input signal range, while keeping sufficient measurment resolution for small signals

but

- Introduction of time measurment jitter for signals above threshold

- Diode requires temperature stabilization

- No simple propotion of measured integrator voltage to charge

- Compensation of measured charge in digital domain

- simple LUT solution in FPGA

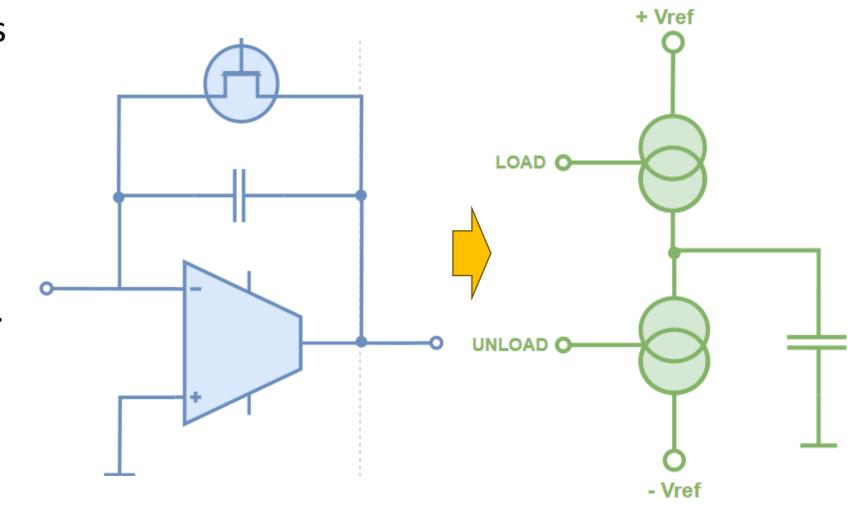

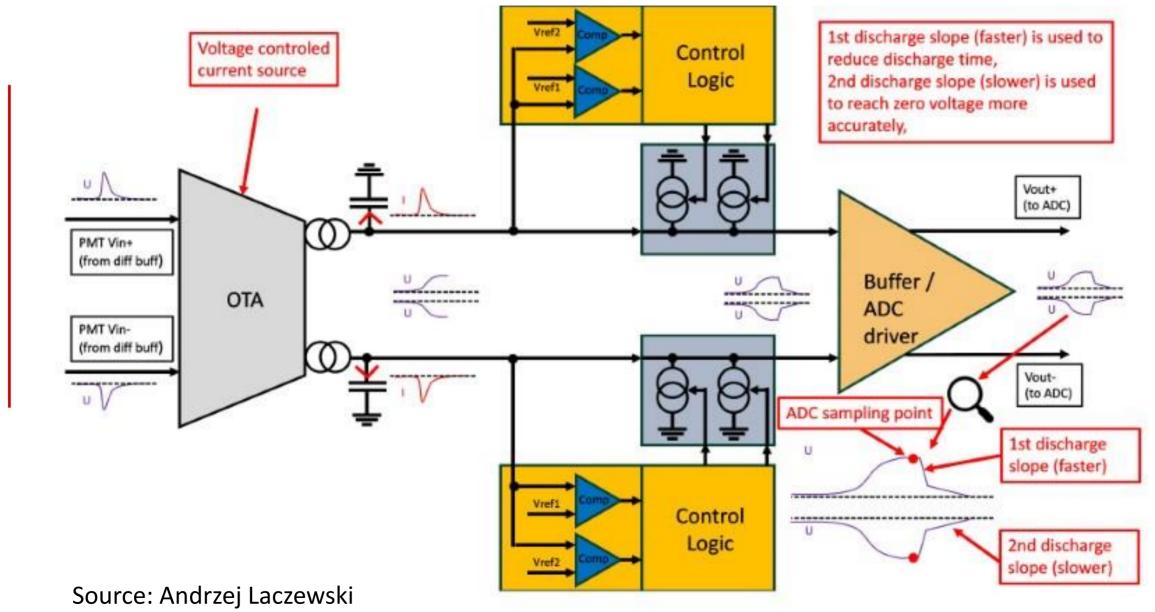

- Integrator based on current sources mitigates problems of traditional op-amp integrator

- Switching transistor downsides:

- limited keying speed,

- parasite charge injection.

10 Oct. 2024

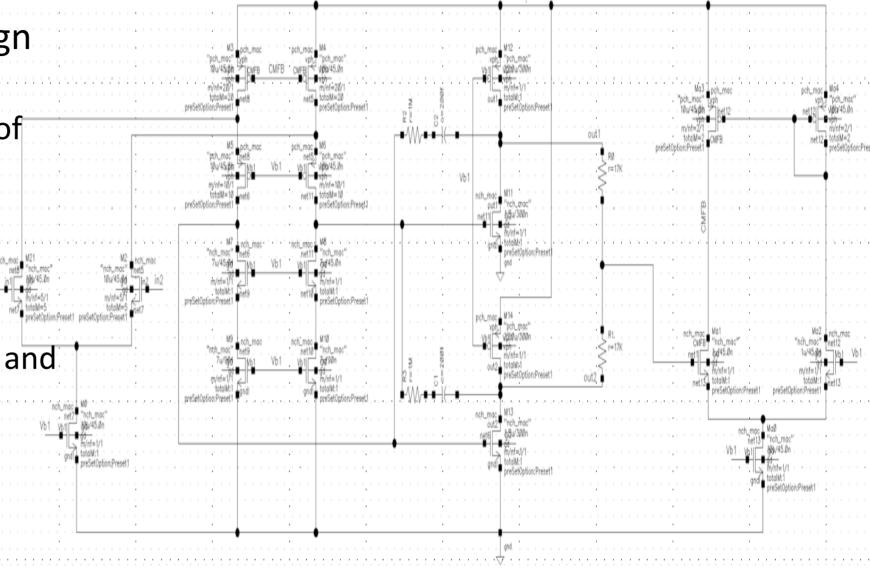

## Design of ASIC for OTA-based integrator

- Necessary to meet design constraints:

- space, energy, stability of parameters

- Selected technology is UMC\_18 CMOS:

- well known and tested

- supply domains of 1.8V and 3.3V

- Relatively low price

Cadence design. Source: Jakub Miszczyński

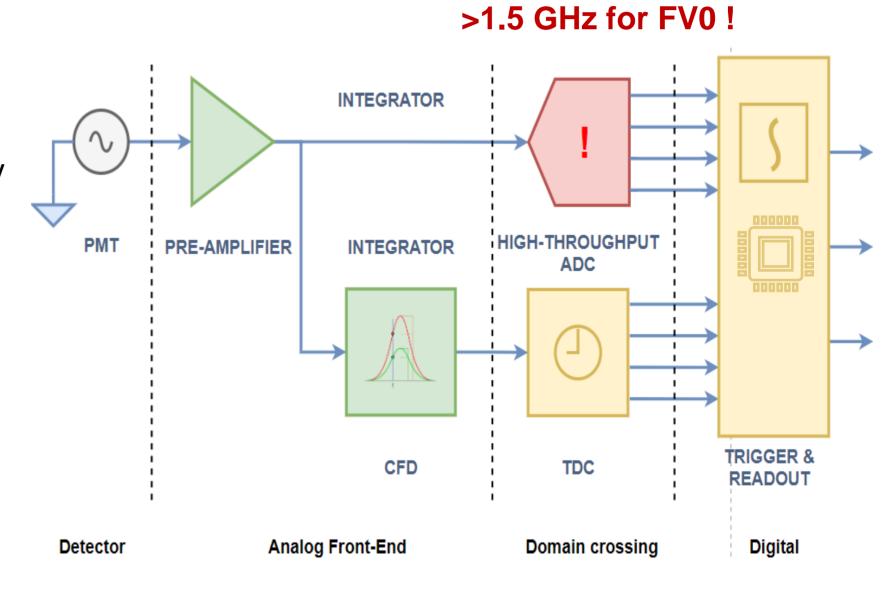

#### Direct PMT signal sampling method

- Modern approach

- Digital PMT signal processing in FPGA

- Software-like flexibility

- Difficult for high frequency signals

- lack of measurment precision

- High Energy consumption

- High latency

- FIT latency < 425 ns</li>

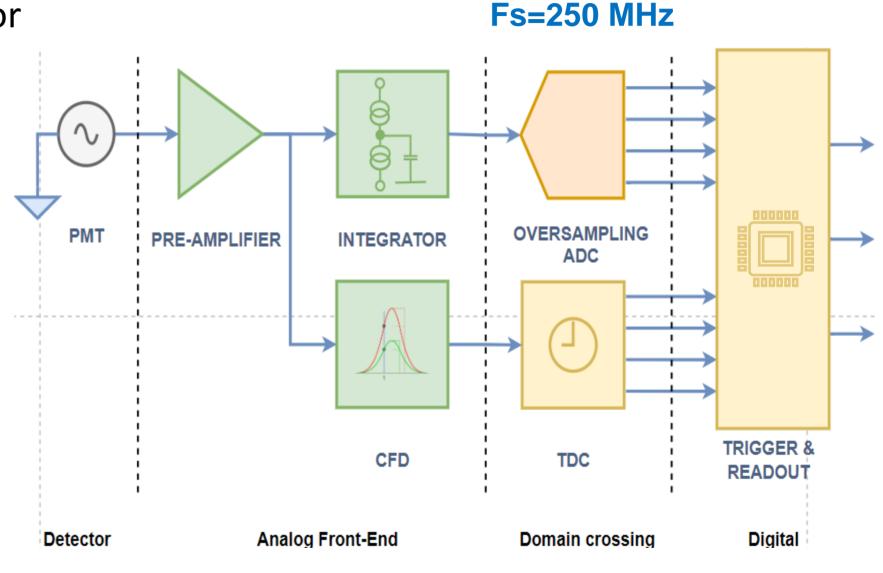

# Oversampling of analog integrator

Oversampling allows for precise detection of pile-ups

End -- Start voltage difference improves measurmant precision

ah.edu.p

## Thank You

agh.edu.p