# ATLAS Inner Tracker (ITk) modules

**Richard Bates**

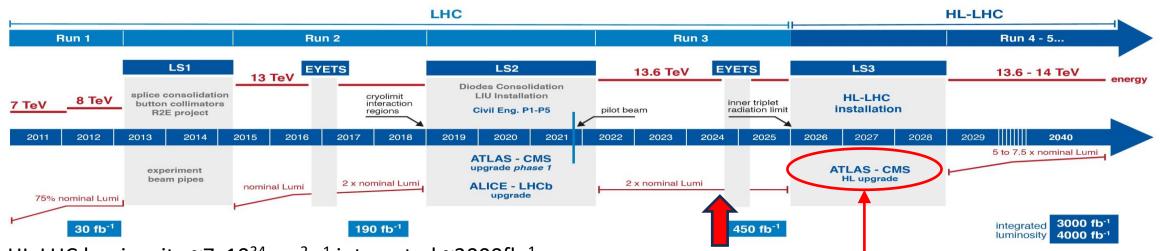

## LHC timeline

Today

- HL-LHC luminosity ~7x10<sup>34</sup>cm<sup>-2</sup>s<sup>-1</sup> integrated ~3000fb<sup>-1</sup>

- ~3.5 times Run-3 peak luminosity

- ~x5 times integrated luminosity at end of Run-3

- Increased luminosity → Increased pile-up:

- Up to 200 pile-up events expected at the HL-LHC compared to ~48 in current Run-3 data

- Increased pile-up compromises pattern recognition and requires higher granularity and higher readout rates

- Increased luminosity → Increased radiation damage

- Damage scales approximately linearly with luminosity ~x10 increase

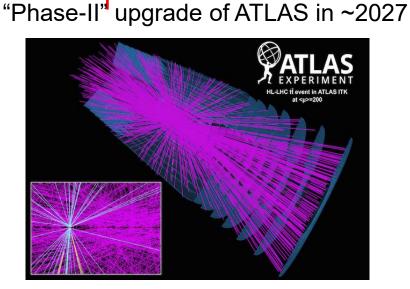

Simulated ttbar events with 200 pileup ATLAS public plot

### **ATLAS Inner Tracker (ITk)**

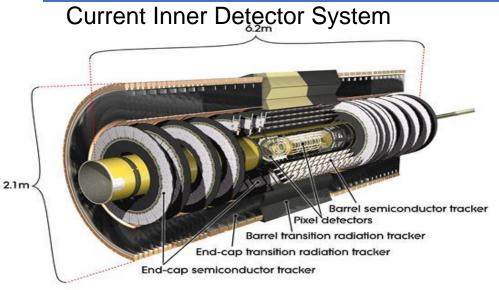

#### Phase-II Inner Tracker (ITk)

The current inner detector system will be replaced with a new all-silicon tracking system -- ITk

- New tracker

- Targeting the same or better performance than current Inner Detector

- Increased granularity to maintain occupancy <1%</li>

- Low mass mechanics, cooling and serial powering to minimize material

- Increased radiation hardness

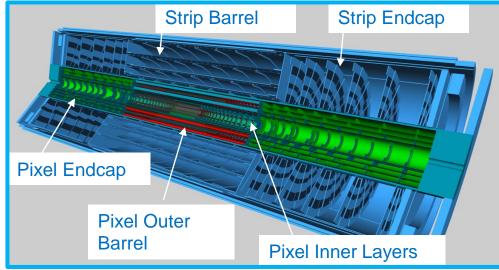

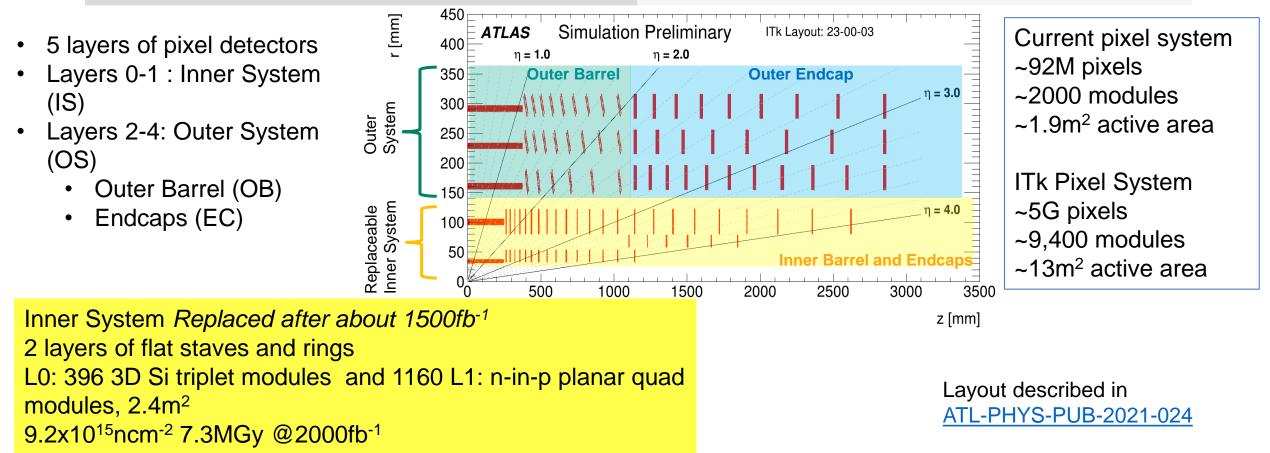

### **ITk Pixel detector layout**

Outer Barrel: 3 layers of flat staves and inclined rings Si n-in-p planar quad modules 4472 quad modules, 6.94m<sup>2</sup> 2.3x10<sup>15</sup>n/cm<sup>-2</sup> 1.7MGy @4000fb<sup>-1</sup> Endcap: 3 layers of rings Si n-in-p planar quad modules 2344 modules, 3.64m<sup>2</sup> 3.1x10<sup>15</sup>n/cm<sup>-2</sup> 3.5MGy @4000fb<sup>-1</sup>

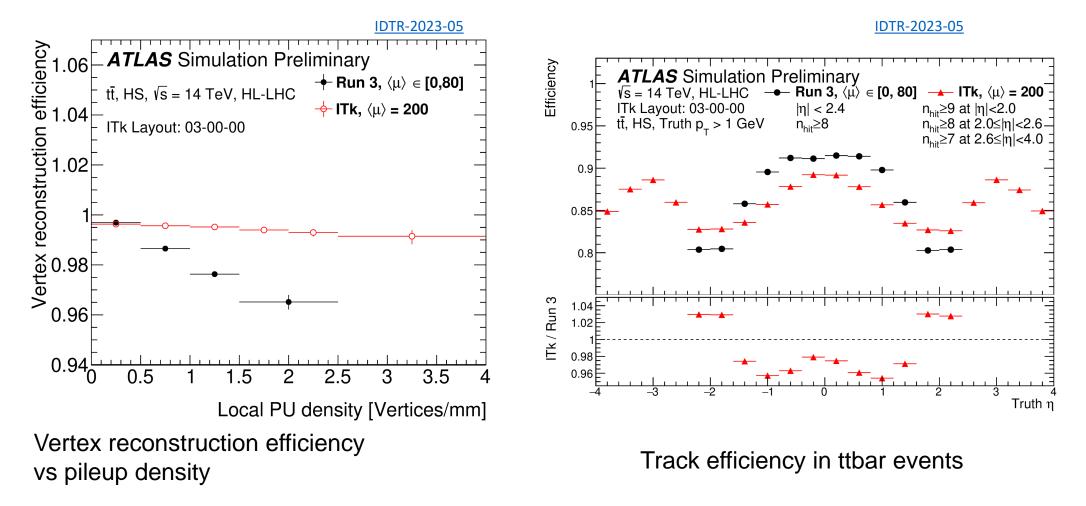

### **Simulation studies of performance**

#### Aim for a performance as good as or better than the current inner tracker

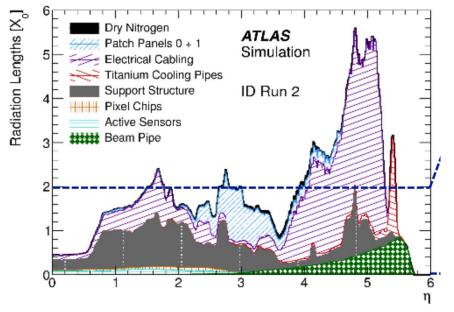

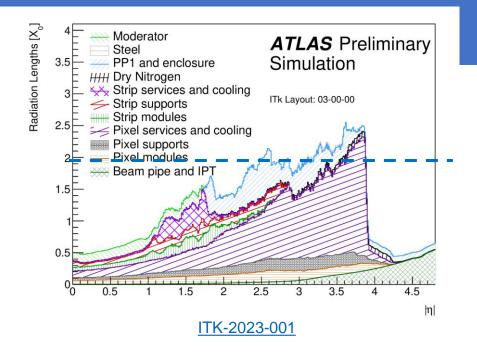

### Material

- Material impacts tracking, radiation levels, data rates and downstream detectors such as the calorimeter.

- It is important to minimize the material.

- Reduce material using

- CO<sub>2</sub> cooling with thin titanium pipes

- Modules with thin Si sensors (100-150μm) and FE-chips (150μm)

- Serial powering of pixel modules to reduce cabling

- Low-mass carbon structures for mechanical stability and mounting

- Optimize number of readout cables using data link sharing

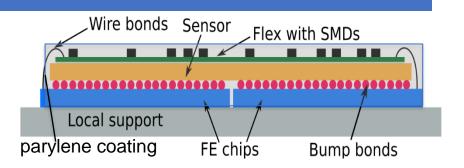

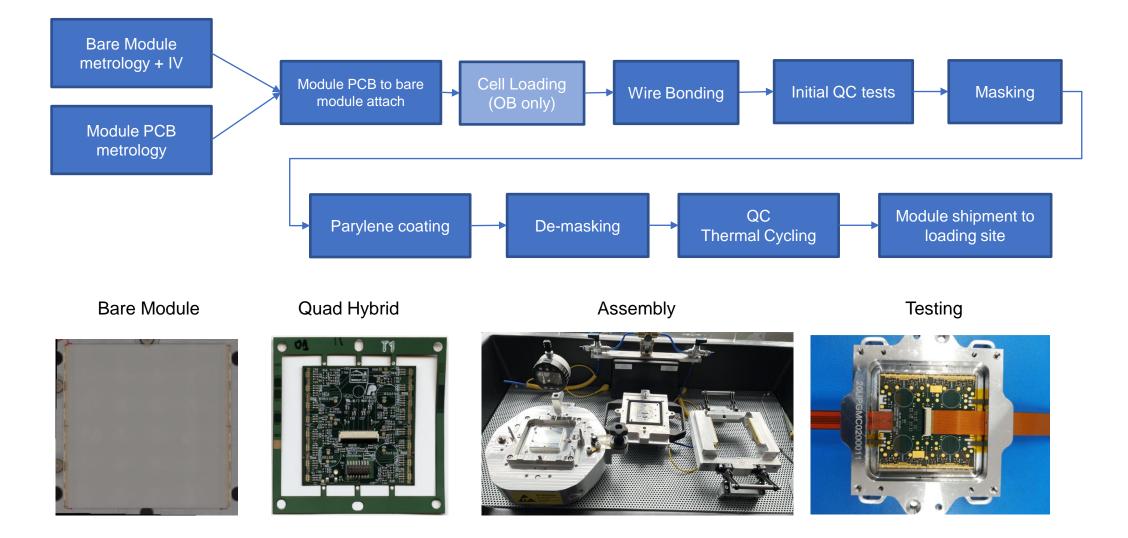

### Modules

- 1 or 4 FE chips bump-bonded to sensor

- Quad modules: 4 FE-chips bonded to 1 sensor

- Triplet module: 1 FE-chip bonded to 1 sensor

- Cu-Kapton flex hybrid glued to sensor

- Flex provides connections for power, DCS and data

- Mix of materials with different coefficients of thermal expansion make the module design challenging

- Modules assembled at. +20°C, but lowest module temperature can be -45°C in the experiments

- Difference in CTE between Cu and Si leads to thermal stress on the bumps

- Amount of Cu needs to be carefully balanced between low power requirements and thermal stress on the bumps

- Qualify bump-strength of solder-based bumps after 100 thermal cycles (-55°C +60°C) for different vendors

- Good results from qualification, being followed up in the preproduction

- Indium bumps needs further evaluation

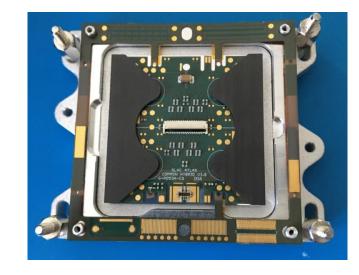

Quad module

Triplet module

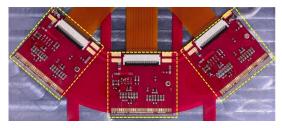

### **Module Flavors: Quads**

- Quad modules on L1-4

- L1: 100 um thick sensor

- L2-4 150 um thick sensor

- EC modules

- OB modules with wire bond protection canopy

Slightly smaller in x & y for the L1 modules

### Module Flavors: IS

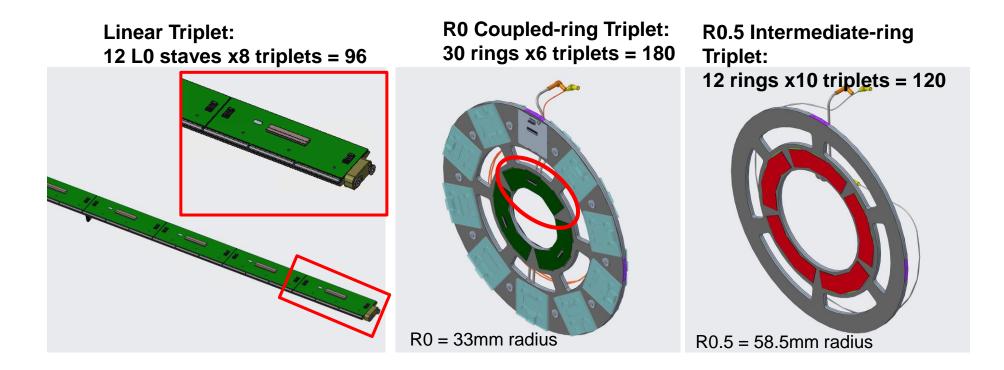

- Pseudo-triplet modules for LO

- 3 single bare modules glued to triplet hybrid

### **Module Production Numbers**

| Item                | Pre-production | Production | Installed | Yield factor |

|---------------------|----------------|------------|-----------|--------------|

| Module hybrids      | 839            | 12370      | 8372      |              |

| L0 – Stave          | 10             | 141        | 96        | 1.46         |

| L0 – Coupled Rings  | 18             | 264        | 180       | 1.46         |

| L0 – Endcap Rings   | 12             | 176        | 120       | 1.46         |

| Common Quad Hybrids | 799            | 11789      | 7976      | 1.48         |

| Assembled Modules   | 849            | 12011      | 8372      |              |

| L0 – Stave          | 10             | 141        | 96        | 1.47         |

| L0 – Coupled Rings  | 18             | 264        | 180       | 1.47         |

| L0 – Endcap Rings   | 12             | 176        | 120       | 1.47         |

| L1 Quad             | 120            | 1690       | 1160      | 1.46         |

| L2-L4               | 683            | 9740       | 6816      | 1.43         |

#### Yields from MoU/BoE document and may change

### Overview

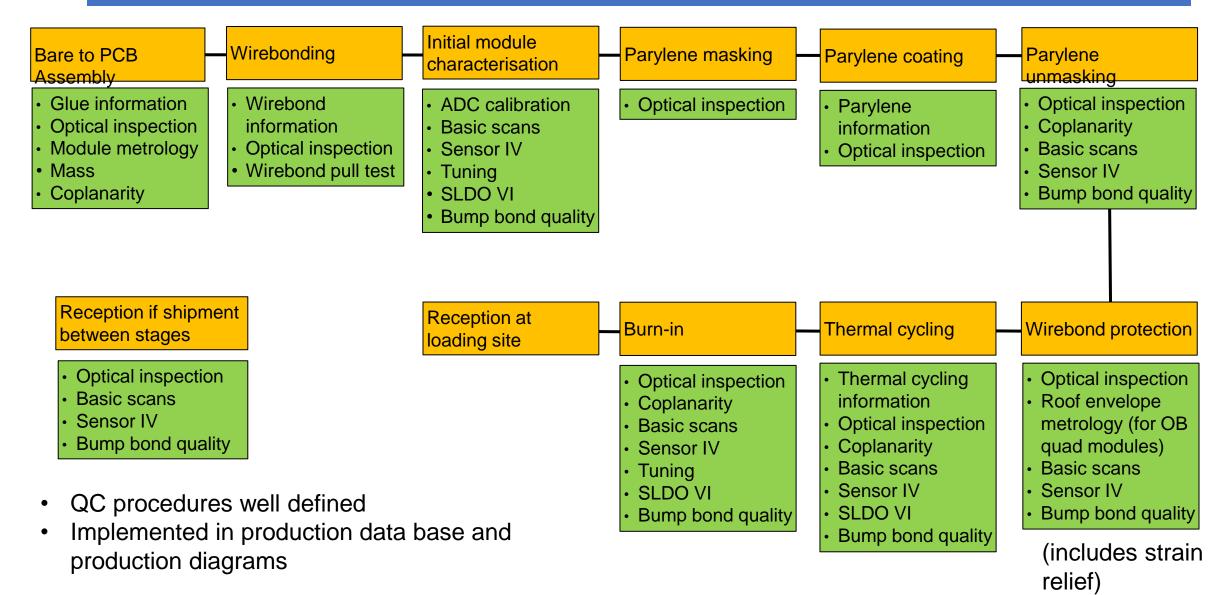

## **Quality Control**

### Sensors

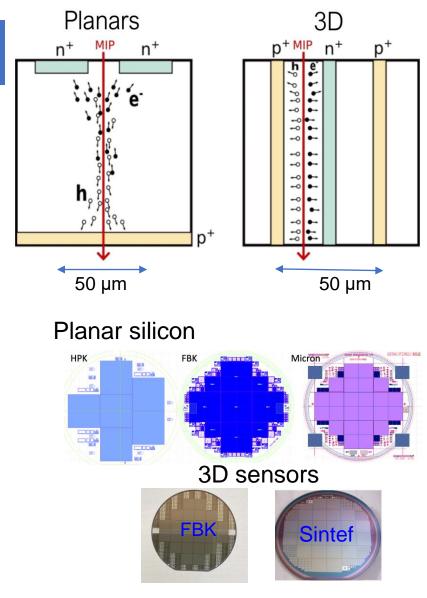

- Improve radiation hardness by:

- Using thin planar sensor 100+150µm thickness

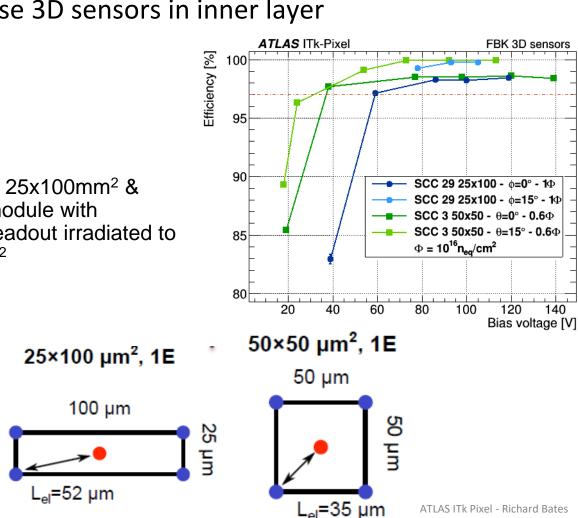

- Use 3D sensors in inner layer •

Irradiated 3D 25x100mm<sup>2</sup> &  $50x50\mu m^2$  module with ITkPixV1.1 readout irradiated to 1x10<sup>16</sup>n<sub>eq</sub>cm<sup>-2</sup>

Planar preproduction complete and 3D close to completion

150 µm

100 or

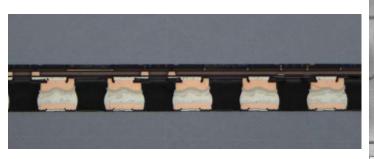

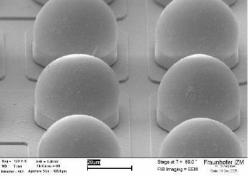

### **Hybridization**

- Number of modules requires 4 hybridization vendors to meet the needed capacity

- Technical issues

- Dicing of FE-chips can lead to chipping and debris

- flip-chip of multiple FE-chips to a sensor has caused problems for some vendors

- Handling the bow of sensors during flip-chip

- Currently, approximately 380 quad modules and 100 3D single modules delivered for technical evaluation and module pre-production

Cross-section of sensor & FE-chip connection

Solder bumps

laser pre-grooving and dicing

blade dicing

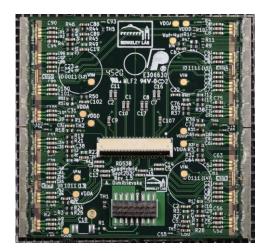

### FE-chip: ITkPixV2

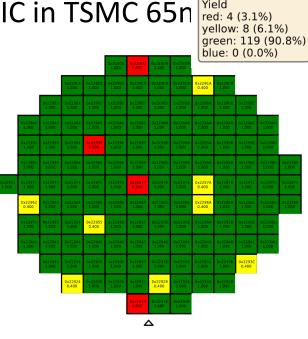

#### Wafer probing yield map

- RD53 Collaboration: joint R&D for ATLAS and CMS ASIC in TSMC 65n Field 4 (3.1%)

- Main features for ATLAS

- 65nm technology, 152800 pixels per chip, 50x50 μm<sup>2</sup> pitch

- Tracking in dense environments

- Low threshold operation

- Cluster charge readout using Time over Threshold

- Radiation environment

- Sensor leakage current compensation

- SEE hardening

- 1.28Gb/s data rates

- 4 data links per chip at 1.28 Gb/s

- data compression

- Optimization of services

- Merging of chip data in module

- Integrated shuntLDO regulator for serial powering

- Final chip ITkPixV2 submitted March 2023

- Wafer probing yield around 90% based on first 100 wafers

131 chips per waferProbing of full wafer takesabout 24hrsYield map based on test ofpower, digital and analogfunctionality

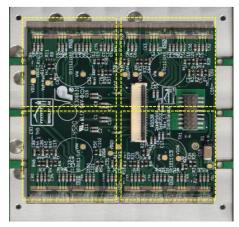

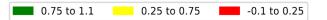

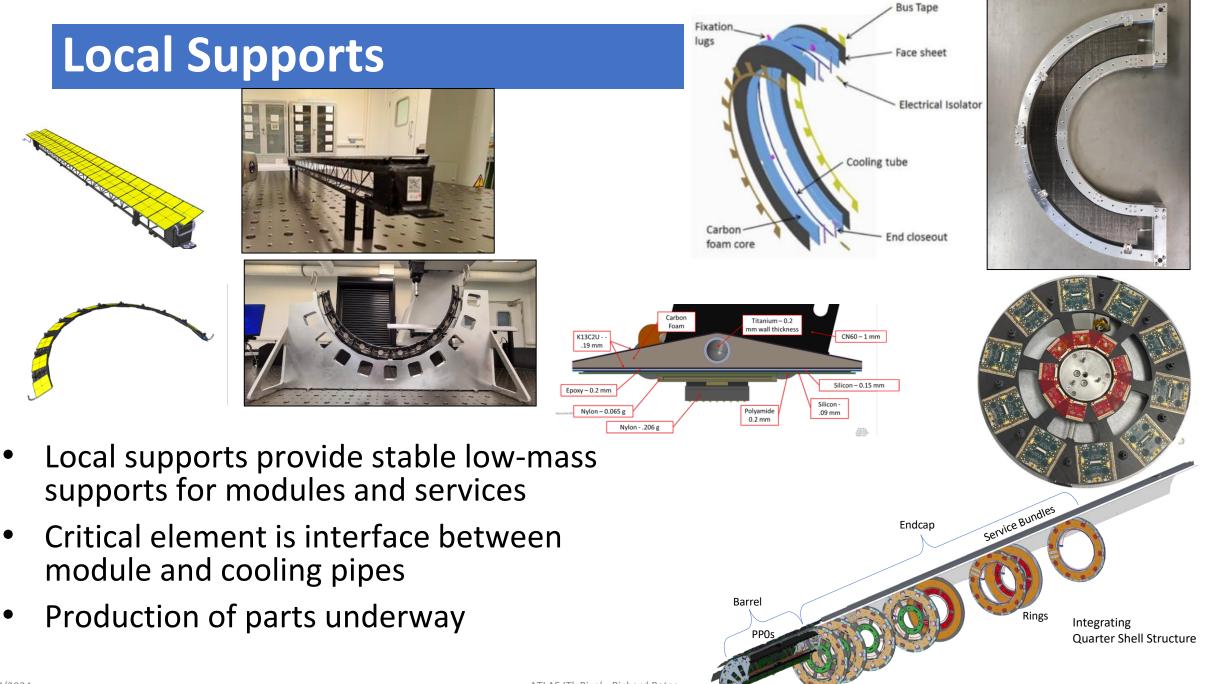

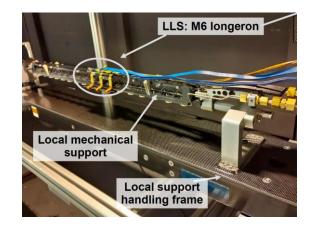

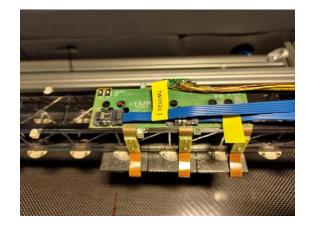

### Loaded Local Supports and System test

- Outer barrel module loading and system tests

- RD53 prototype modules loaded on to cells and thermally tested mounted onto local supports system test

- Performance of modules monitored through the loading process

- Work on system tests preproduction items in progress

### Summary

- The ATLAS ITk Pixel detector has been designed to operate in the challenging HL-LHC environment and maintain the performance of the current tracking system

- Increased radiation hardness

- Maintain pixel hit occupancy at 1% by increasing granularity

- Low mass achieved using carbon based mechanics, serial powering and data merging

- The project is now in pre-production

- Large scale production brings a new set of problems as more sensitive to rare problems

- Moving from development of individual items system level tests

- Loaded local support system tests are underway, excellent testbed for integration issues

## Thank you for your time