# Quad Module – MALTA2 V1

Marcos Vázquez Núñez

Carlos Solans Sánchez

#### Introduction

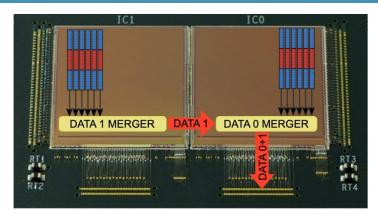

(a) IC0 Master; IC1 Slave

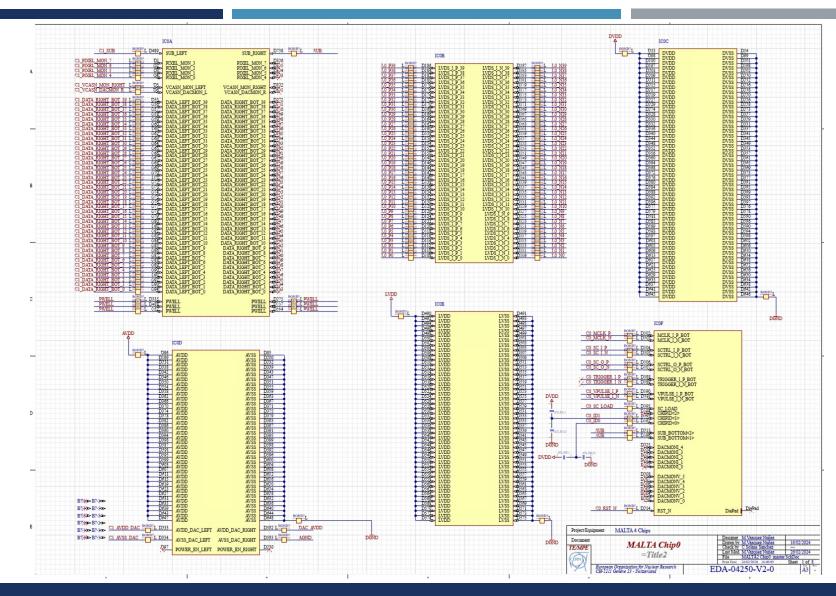

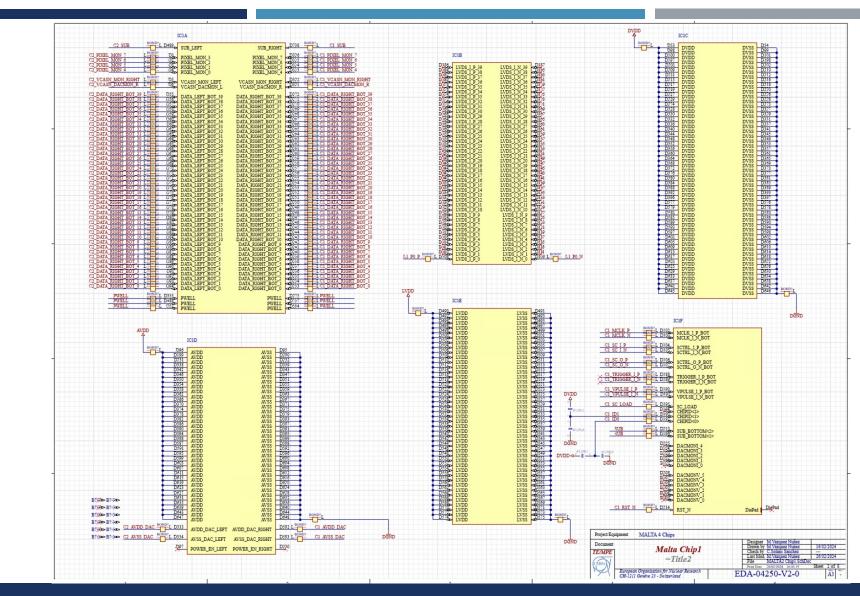

#### **CHIP 0 - MASTER**

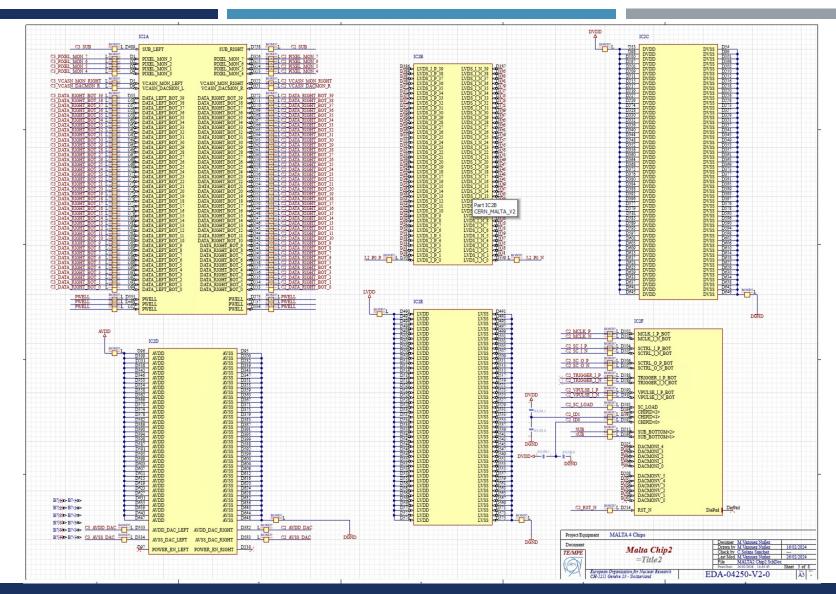

#### CHIP 1 - Slave

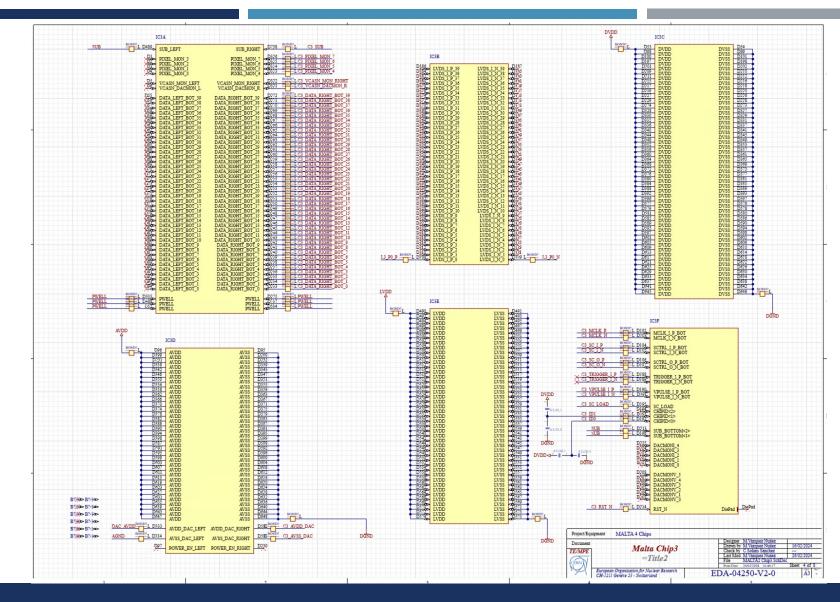

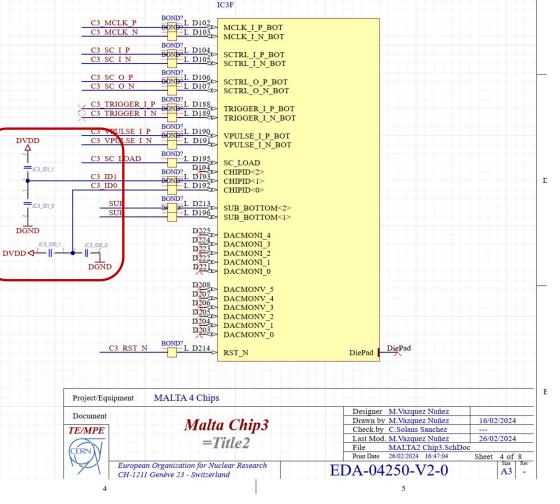

#### CHIP 2 - Slave

#### CHIP 3 - Slave

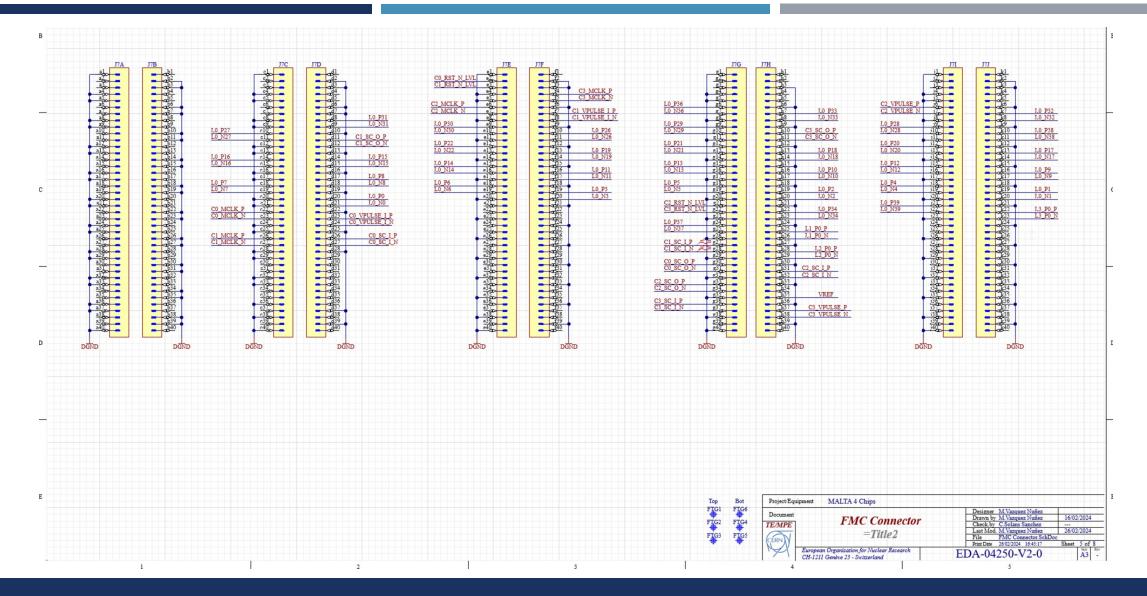

#### FMC Connector - HPC

CERN

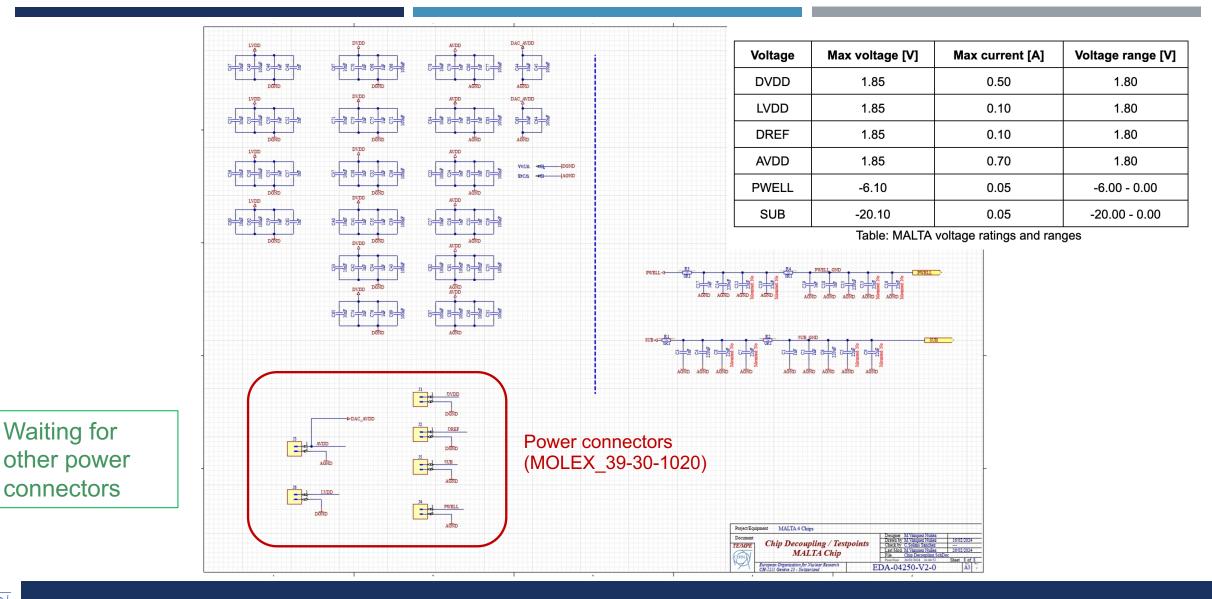

#### Power connectors & decoupling capacitors

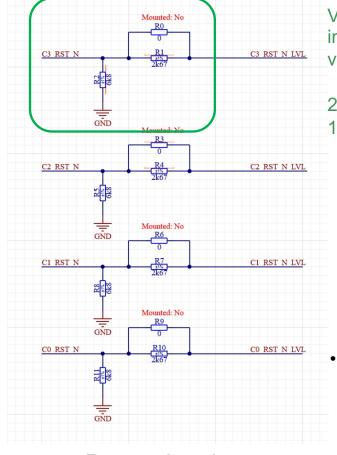

#### Reset & chip ID

**Reset signals**

Voltage dividers were implemented to reduce the voltage from 2.5V to 1.8 V.

2.5V → comes from FPGA 1.8V → goes to the chip

> Solder jumpers were implemented like switches (easier to solder and unsolder) to choose in between '1' and '0'

Chip ID has two bits, because four chips will be implemented (3 slaves

- + 1 master chips).

- "00" → CHIP 3 (slave)

- "10"  $\rightarrow$  CHIP 1 (slave)

- "11"  $\rightarrow$  CHIP 0 (master)

Chip ID (Chip 3 in this picture)

(CERN)

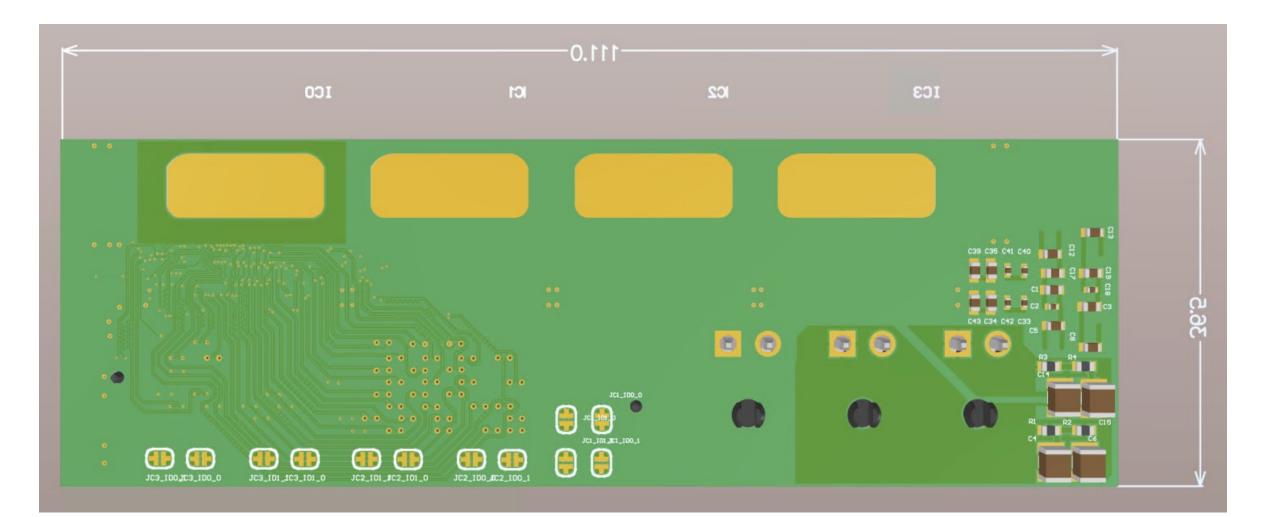

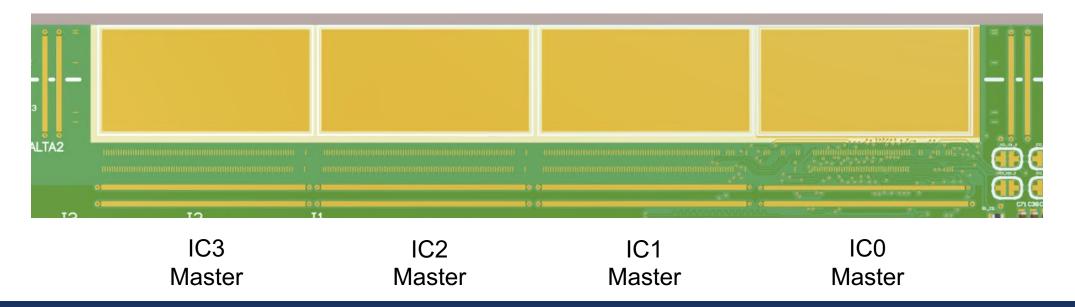

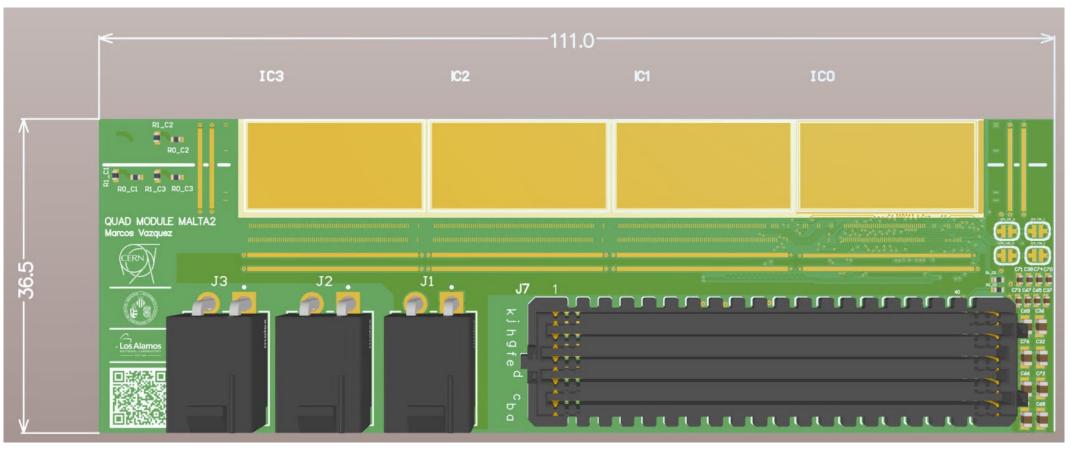

#### 3D view – Front side

- Minimal distance required from bonding lab to do wirebonding in between MALTA2 chips is at least 800 microns

- Distance in between chips will be 900  $\mu m$  for this first version

#### **PCB** details

- MALTA2 quad module PCB V1 will have the following dimensions:

- 111 mm x 36.5 mm x 0.4 mm

- Material for high-speed signals: I-Tera MT40

- <u>https://www.isola-group.com/pcb-laminates-prepreg/i-tera-mt40/</u>

- Thickness: ~ 400 µm for 4 layers in stack-up

- Advantage against MALTA QUAD module (12 layers used). Minimal thickness can be 1.3 1.5 mm

- Minimal thickness of MALTA2 QUAD module has been divided by 3 compared to MALTA QUAD, thus less dead material in the PCB.

- FMC pinout was changed for PCB routing optimisation

- HPC FMC connector used. Module cannot be tested with LPC connector, due to both banks of the connector are used (A and B).

- 460 CHF/unit

CERN

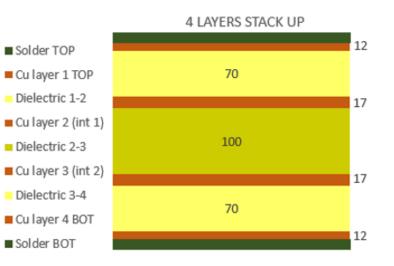

Manufacturer stack-up

#### Stack-up

- Total thickness will be ~ 400  $\mu$ m in this version (398  $\mu$ m)

- Soldermask thick  $\rightarrow$  25 µm

- Top and bottom copper layers → 12 µm

- Core → 100 µm (I-Terra MT40 material)

- Prepreg  $\rightarrow$  70 µm (1067H of I-Tera MT40 material)

- Metallisation drilled layer  $\rightarrow$  25 25 = 50 µm

| # | Name           | Material        | Туре        | Weight | Thickness | Dk   | Df     |

|---|----------------|-----------------|-------------|--------|-----------|------|--------|

|   | Top Overlay    |                 | Overlay     |        |           |      |        |

|   | Top Solder     | Solder Resist 🕮 | Solder Mask |        | 0.025mm   | 3.5  | 0      |

|   | Top Layer      |                 | Signal      | 1/2oz  | 0.012mm   |      |        |

|   | Dielectric 1   | 0               | Prepreg     |        | 0.07mm    | 3.08 | 0.002  |

| 2 | GND            |                 | Plane       | 1oz    | 0.017mm   |      |        |

|   | Dielectric 11  |                 | Core        |        | 0.1mm     | 3.26 | 0.0025 |

| 3 | Internal layer |                 | Signal      | 1oz    | 0.017mm   |      |        |

|   | Dielectric 2   |                 | Prepreg     |        | 0.07mm    | 3.08 | 0.002  |

| 4 | Bottom Layer   |                 | Signal      | 1/2oz  | 0.012mm   |      |        |

|   | Bottom Solder  | Solder Resist 🔤 | Solder Mask |        | 0.025mm   | 3.5  | 0      |

|   | Bottom Overlay |                 | Overlay     |        |           |      |        |

Altium stack-up

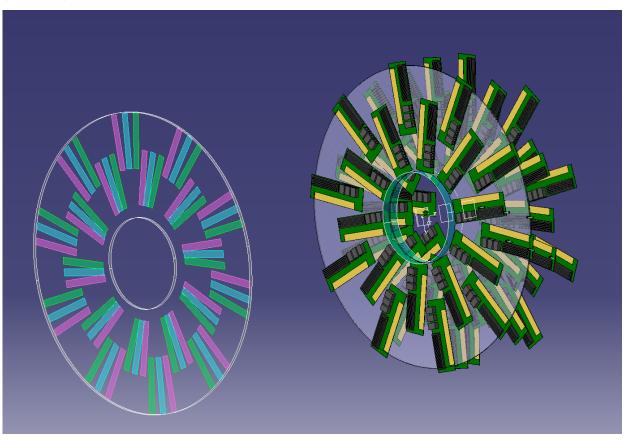

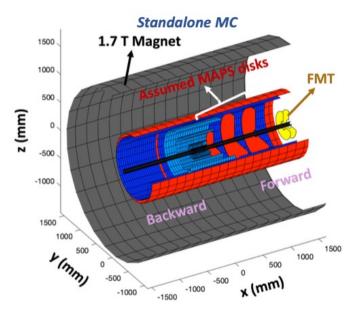

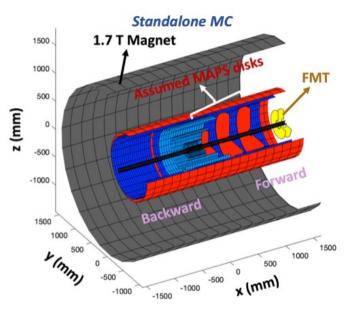

#### Mechanical studies of the detector disk for FMT

• Regarding the dimensions provided, our mechanicals engineers were simulating a disk with 3 different modules layers (pink, blue and green) to cover the dead material as efficiently as possible.

#### Hadron endcap FMT geometry (config 2)

| Parameter              | Disk 1                | Disk 2                |

|------------------------|-----------------------|-----------------------|

| Inner Radius           | 7.014 cm              | 7.014 cm              |

| Outer Radius           | 23.095 cm             | 23.095 cm             |

| z location             | 145 cm                | 165 cm                |

| Material budget        | 0.74%X/X <sub>0</sub> | 0.74%X/X <sub>0</sub> |

| Average hit efficiency | 98%                   | 98%                   |

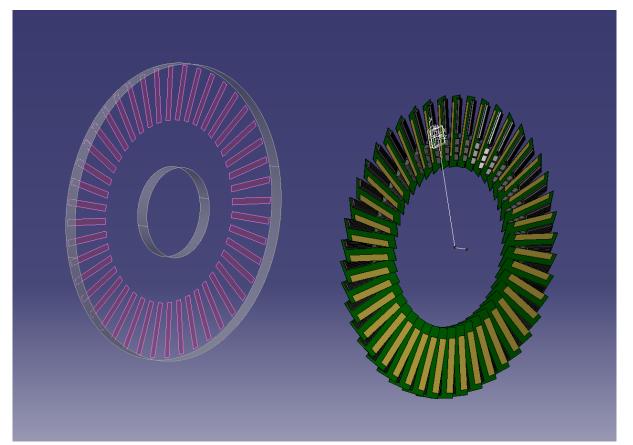

#### Mechanical studies of the detector disk for FMT

Regarding the dimensions provided, our mechanicals engineers were simulating a disk with 2 different modules layers (pink) to cover the dead material as efficiently as possible.

#### Hadron endcap FMT geometry (config 2)

| Parameter              | Disk 1                | Disk 2                |

|------------------------|-----------------------|-----------------------|

| Inner Radius           | 7.014 cm              | 7.014 cm              |

| Outer Radius           | 23.095 cm             | 23.095 cm             |

| z location             | 145 cm                | 165 cm                |

| Material budget        | 0.74%X/X <sub>0</sub> | 0.74%X/X <sub>0</sub> |

| Average hit efficiency | 98%                   | 98%                   |

# **BACKUP** 17/06/24

QUAD-Module update

1/7/24

15

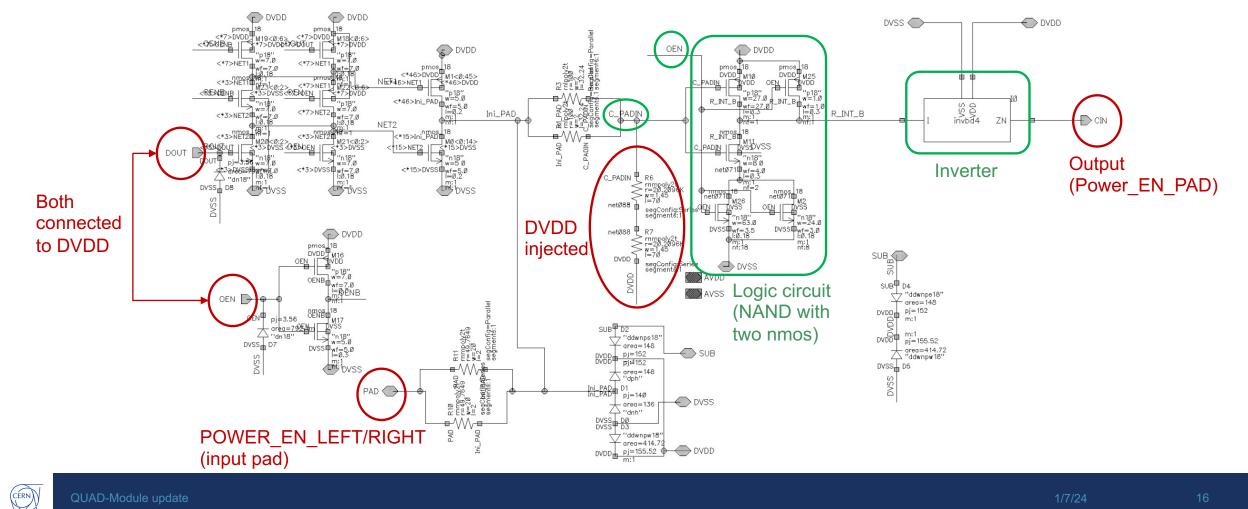

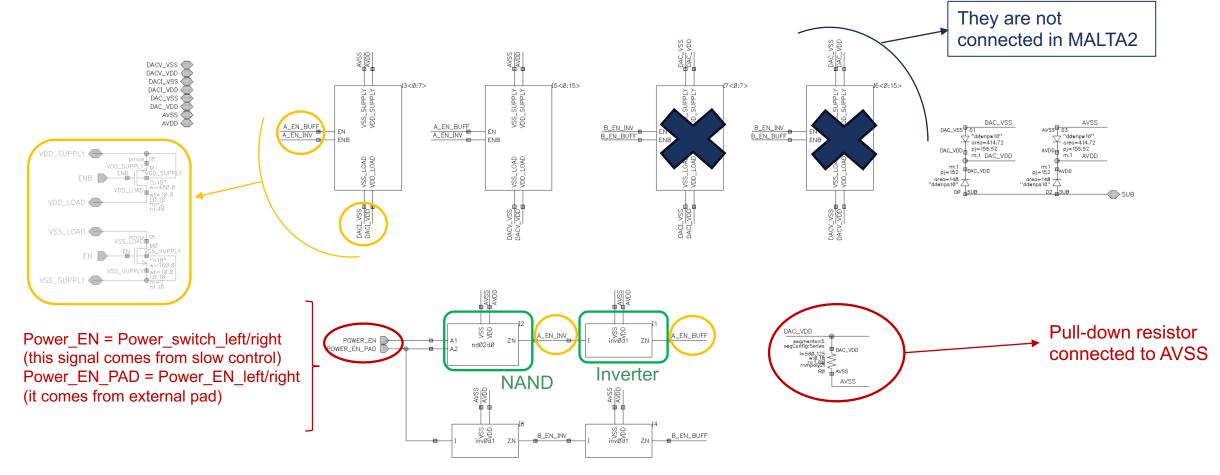

## Pull-up in POWER EN LEFT/RIGHT by default

Power\_EN signal does not need to be connected, it is configurated in '1' by default, with OEN = DVDD = '1' and C\_PADIN = '1' at the NAND input, CIN = '1' (output)

### Pull-down resistor in DAC\_VDD

Every left and right DAC power (DAC\_VDD) has a pull down resistor implemented in MALTA2 chip (AVDD\_DAC\_LEFT/RIGHT)

#### 3D view-Back side