# Towards MPGDs with embedded pixel ASICs

Lucian Scharenberg on behalf of the CERN EP-DT-DD GDD team

8<sup>th</sup> International Conference on Micro-Pattern Gaseous Detectors, USTC 14 October 2024

## **Outline**

### Motivation:

Why high-granularity readout of MPGDs? Why Timepix4?

### **1. Embedding into the amplification stage:**

Simple PCB manufacturing techniques and intrinsic discharge protection.

### 2. First steps, triple-GEM:

Before embedding, explore GEMPix with Timepix4. Testing of TSV-Timepix4.

### 3. Large-area ASICs:

Long-term perspective and ideas for ambiguity-free readout

#### Summary

# **Motivation**

## High-granularity readout of gaseous detectors

### Possibilities offered by high-granularity readout of gaseous detectors:

- → Low-material budget tracking with high spatial accuracy

- → Event-selection based on geometrical signature

- → Sensitivity to low-energetic photon interactions ( $E_{gamma}$  < 2 keV)

https://ixpe.msfc.nasa.gov/for\_scientists/papers/ 2017spie\_0829\_sgro.pdf

## Example applications:

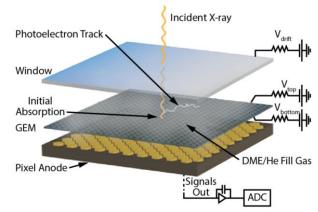

- → X-ray polarimetry (e.g. IXPE @ NASA)

- → Nuclear recoil events (e.g. MIGDAL, CYGNO)

- → Material science (e.g. MIXE @ PSI)

- → Axion helioscopes (e.g. IAXO)

- → Micro dosimetry (e.g. GEMPix)

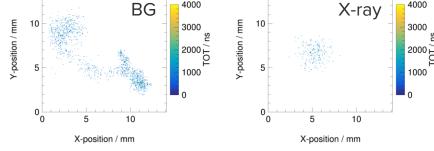

Geometry selection with GridPix data

# CERN

## Illustration for X-ray polarimetry @ IXPE

## Hybrid pixel ASICs The Timepix4

Most commonly used ASIC for this purpose: Timepix family

→ Use **bump-bond pads** for semiconductor sensor **as charge collection pads**

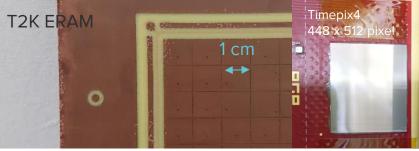

### Timepix4: latest version of the Timepix

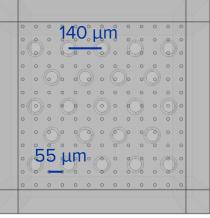

- → 2.5 x 3.0  $\approx$  7 cm<sup>2</sup> active area with **448 x 512 pixels** (55 µm square pitch)

- $\rightarrow$  700 electrons energy resolution

- → Up to 60 ps front-end time resolution

- → Up to **3 MHz/mm<sup>2</sup> hit rate (data-driven)** and up to 5 GHz/mm<sup>2</sup> (frame-based)

### Most interesting feature for us: 4-side tileable

- → Connect from the back-side, using **Through Silicon Vias (TSVs)** with Redistribution Layer (RDL)

- → No dead area, **no wire bonds!** Required for embedding process

## Backside of a TSV-Timepix4

Courtesy of Jerome Alozy

# Part 1: embedding concept and status

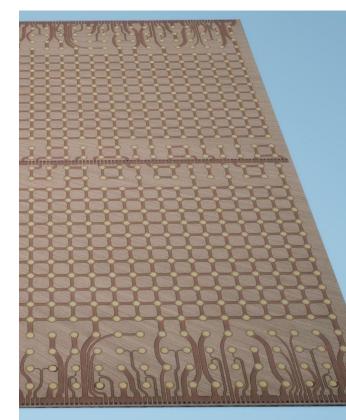

# **Embedding** approach

## New research line with CERN EP R&D Work Package 2

### **Embedding of front-end ASICs in flexible PCB, i.e. micro-pattern amplification structures**

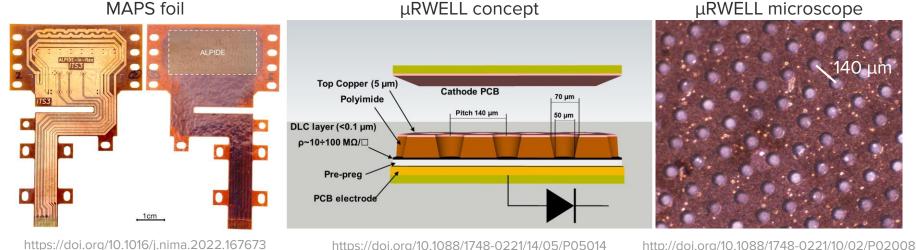

- → Possible with Micro-Resistive Well (µRWELL) structure, using standard PCB technologies

- → Conceptually inspired by "MAPS foil" (Magnus Mager and Rui de Oliveira): MPGD 2022

https://doi.org/10.1088/1748-0221/14/05/P05014

http://doi.org/10.1088/1748-0221/10/02/P02008

# Embedding approach

## New research line with CERN EP R&D Work Package 2

### Embedding of front-end ASICs in flexible PCB, i.e. micro-pattern amplification structures

- → Possible with Micro-Resistive Well (µRWELL) structure, using standard PCB technologies

- → Conceptually inspired by **"MAPS foil"** (Magnus Mager and Rui de Oliveira): <u>MPGD 2022</u>

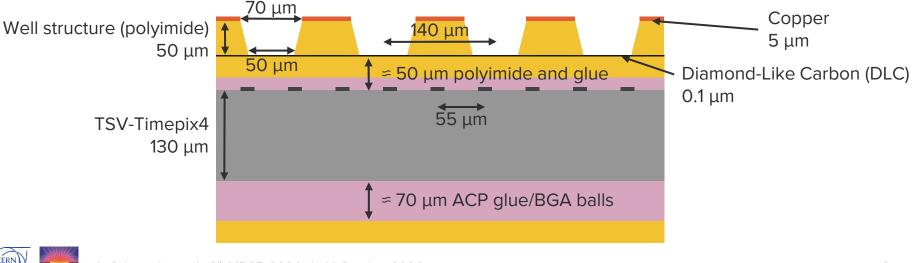

- → Embedding **only possible, because of TSVs** (wire bonds and pads interfere laminating procedure)

### Not drawn to scale!

# Embedding approach

## New research line with CERN EP R&D Work Package 2

## Embedding of front-end ASICs in flexible PCB, i.e. micro-pattern amplification structures

- → Possible with Micro-Resistive Well (µRWELL) structure, using standard PCB technologies

- → Conceptually inspired by **"MAPS foil"** (Magnus Mager and Rui de Oliveira): <u>MPGD 2022</u>

- → Embedding only possible, because of TSVs (wire bonds and pads interfere laminating procedure)

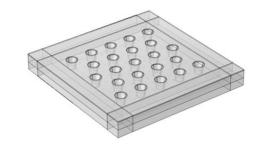

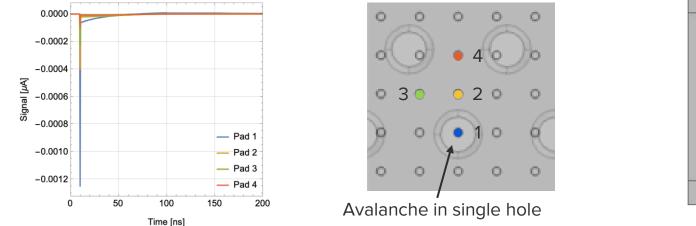

# **Signal induction simulation**

### How is the charge measurement affected?

- $\rightarrow$  Distance (up to 50  $\mu m$ ) between DLC and charge collection pads

- → Different geometry between Timepix4 pixels and  $\mu RWELL$  holes

Simulation of signal induction using **COMSOL** and **Garfield++** (Djunes Janssens)

#### Next step: include front-end response, i.e. Timepix4 transfer function

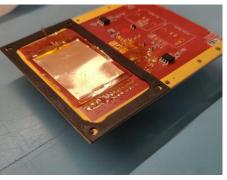

## Next steps and production status

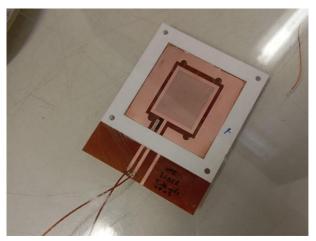

### **Designed and produced custom detector PCB** (William Billereau)

- → Based on Nikhef carrier

- → Support typical MPGD R&D detector housing

Allows **µRWELL test without embedding** and various GEM configurations

- → Electrostatic coupling between  $\mu$ RWELL foil and TSV-Timepix4

- → After low yield in first production, **new production ongoing**

## Received electrically broken TSV-Timepix4v0

→ At CERN MPT workshop for **mechanical tests of embedding**

## **Part 2: performance evaluation with GEM**

Well-known technology (GEMPix) to understand gaseous detector properties and software optimisation

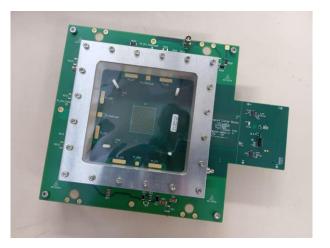

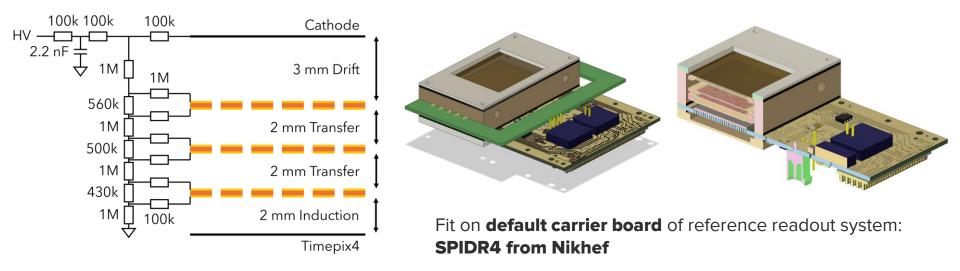

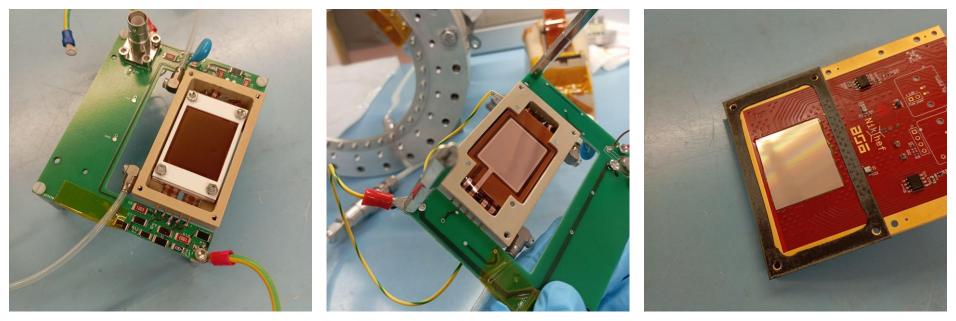

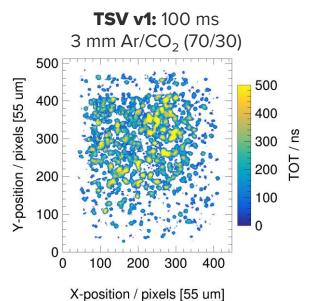

## Triple-GEM detector for TSV-Timepix4v1 Detector design

Small gas volume with 3 mm drift/interaction region, filled with Ar/CO<sub>2</sub> (70/30)

- → Triple-GEM well established with Timepix (GEMPix)

- → Reach sufficient gain while maintaining low discharge probability (bare, unprotected Timepix)

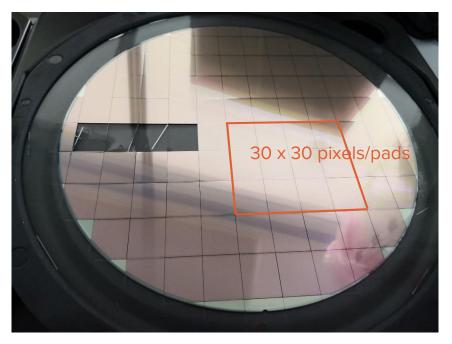

## **Triple-GEM detector for TSV-Timepix4v1** Assembly of TSV chips

**Chip assembly** through **ACP** (Anisotropic Conductive Paste) on Nikhef carrier at University of Geneva (Mateus Vicente):

# **Triple-GEM detector for TSV-Timepix4v1**

## **Detector assembly (GEMPix4)**

Detector with  $2.5 \times 3.0 \text{ cm}^2$  active area surprisingly complicated in handling and operation.

# **Triple-GEM detector for TSV-Timepix4v1**

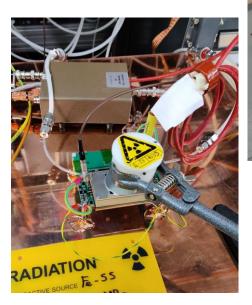

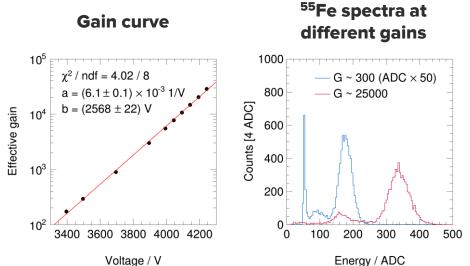

## **Single-channel characterisation**

Single-channel copper electrode, read out with NIM electronics (preamp, shaper, MCA + picoammeter for anode current)

→ Gains > 25k without discharges

→ Good energy resolution at low gains

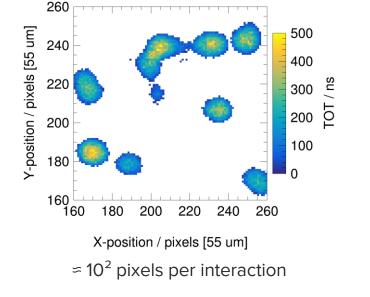

**Individual interactions**

3 mm drift is too thin for full absorption

#### Measurements with <sup>90</sup>Sr at G ≈ 5000

Zoom and 10 ms slice

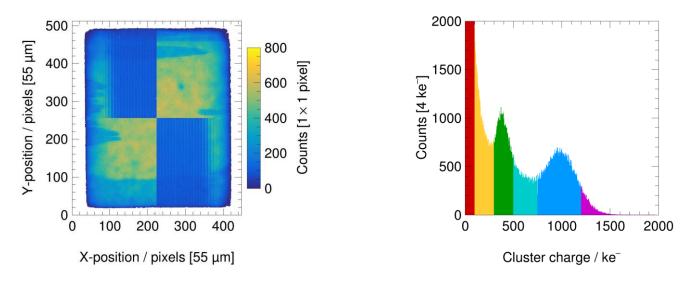

# **First results**

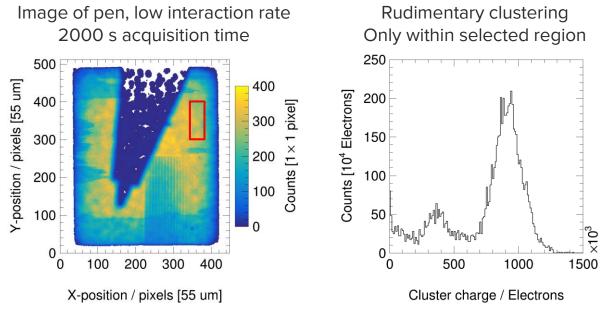

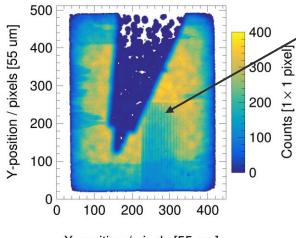

## Imaging

#### First X-ray image recorded with TSV-Timepix4

Clusters

**Hits only**

Detector gain ≈ 5000

## **Next steps with GEMPix4**

X-position / pixels [55 um]

Redo measurements with **Timepix4v2** (Fast-links work correctly) → 10 Gbps instead of 40 Mbps over slow control links

**Flat-field corrected image** and understanding of origin of image features

Explore the possibility of a **2 x 2 chip matrix and larger area** readout

Continue the work of Fabrizio Murtas with his colleagues from the **CERN RP Dosimetry team** (Pierre Carbonez, Tristan Genetay and Andrea Garcia-Tejedor)

- → Optimisation of the detector

- → Applications (e.g. micro dosimetry or part of CT in hospitals)

## **Part 3: future perspective and dreams** Other front-end ASICs and readout boards in silicon

## Large area coverage Typical gaseous detector applications

Pixel/pad readout = **ambiguity free**

Examples of pad readout:

- → ALICE Time Projection Chamber:

- → T2K Time Projection Chambers:

- → RHUM project:

- → MPGD-based DHCAL:

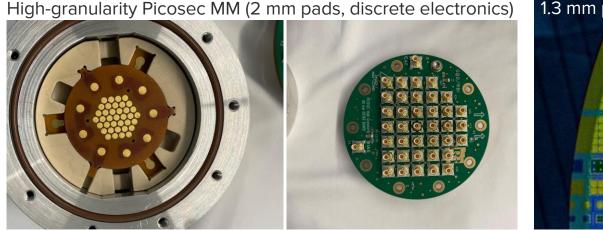

- → Picosec MicroMegas:

Compare with typical pixel ASICS:

https://indico.cern.ch/event/973503/contributions/4099220/

4 x 7 mm<sup>2</sup>, 6 x 10 mm<sup>2</sup>, 6 x 12 mm<sup>2</sup> and 6 x 15 mm<sup>2</sup> 10 x 11 mm<sup>2</sup> 1 x 3 mm<sup>2</sup>, 1 x 8 mm<sup>2</sup> and 10 x 10 mm<sup>2</sup> 10 x 10 mm<sup>2</sup> 10 x 10 mm<sup>2</sup>

0.055 x 0.055 mm<sup>2</sup>

### Large area gaseous detector applications do not require this fine granularity

→ Find a solution with e.g. 1 x 1 mm<sup>2</sup> or 3 x 3 mm<sup>2</sup> pads

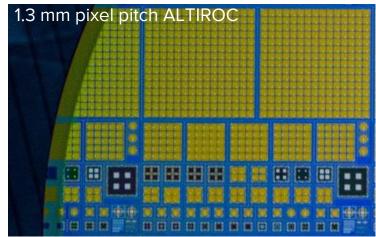

## **Other front-end ASICs**

## Establish a manufacturing technique that can be applied to other ASICs

- → Use ASICs with larger pixel pitch, e.g. ALTIROC or ETROC (both 1.3 mm pitch)

- → Could enable high-granularity Picosec MicroMegas/µRWELL with integrated front-end electronics

Courtesy of Florian Brunbauer

https://indico.cern.ch/event/1323113/contributions/5823798/

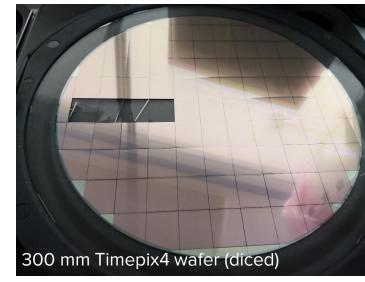

## Dreaming a bit – the silicon readout board General idea

### Go beyond the "classical" front-end ASIC

- → Timepix4 and ALTIROC < 10  $cm^2$

- $\rightarrow$  Gaseous detectors > 100 cm<sup>2</sup>

#### Go beyond the "classical" PCB

- → PCB with 30 x 30 pads of 3 x 3 mm<sup>2</sup> size very expensive (several kCHF)

- ightarrow Does not include front-end electronics

(900 channels = e.g. 8 VMM3a hybrids = several kCHF on top)

### Typical wafer costs (does not include the mask): 1 to 4 kCHF

→ Why not make a readout board from a wafer? The silicon readout board for gaseous detectors!

https://indico.cern.ch/event/1413681/contributions/5998158/

## Dreaming a bit – the silicon readout board Advantages

## Why not make a readout board from a wafer? The silicon readout board for gaseous detectors!

Example: 100 x 100 mm<sup>2</sup> ASIC with 3 x 3 mm<sup>2</sup> pixels → Ambiguity free, large-area readout

Cheap process possible (e.g. 130 nm instead of 28 nm)

### With 3 x 3 mm<sup>2</sup> pads

- → Sufficient space for redundancy and discharge protection

- $\rightarrow$  Increase reliability of electronics

## Summary and next steps

## **Summary and next steps**

New research line on embedding of high-granularity readout ASICs in micro-pattern amplification stage

- → Profit from the capabilities of **TSV-Timepix4**

- → First promising results obtained with GEMPix4, allows to study signal induction and electronics understanding and optimisation

### **Next steps with Timepix4**

- → Perform **tests with µRWELL**, first without embedding

- → Mechanical embedding tests at CERN MPT workshop

- → Target construction of **multi-chip PCB** with e.g. 2 x 2 chip matrix

Future goals and dreams

- → Test different front-end ASICs, e.g. ALTIROC or ETROC

- → Start development of silicon readout board

## Acknowledgements

## This project is only possible, because of the help and support from many people. Many thanks to all of them!

### CERN:

Jerome Alozy, William Billereau, Florian Brunbauer, Michael Campbell, Pierre Carbonez, Tristan Genetay, Djunes Janssens, Xavi Llopart, Magnus Mager, Rui de Oliveira, Eraldo Oliveri, Francisco Piernas Diaz, Miranda van Stenis

### University of Geneva:

Mateus Vicente

### Nikhef:

Martin Fransen, Kevin Heijhoff, Martin van Beuzekom, Bas van der Heijden

# Thanks for your attention :-)

Lucian.Scharenberg@cern.ch

## **Back-up slides**

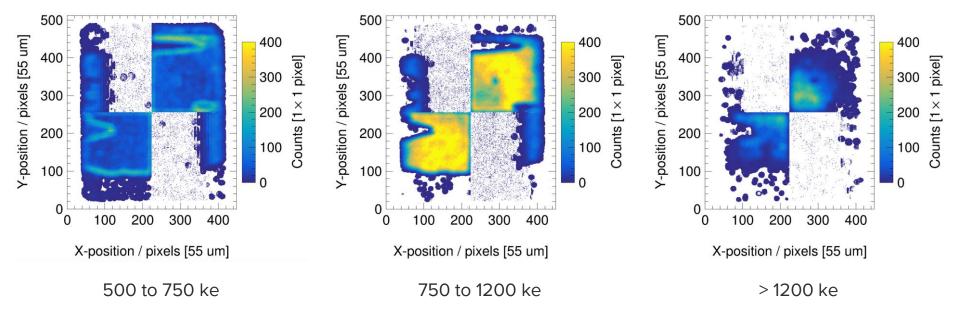

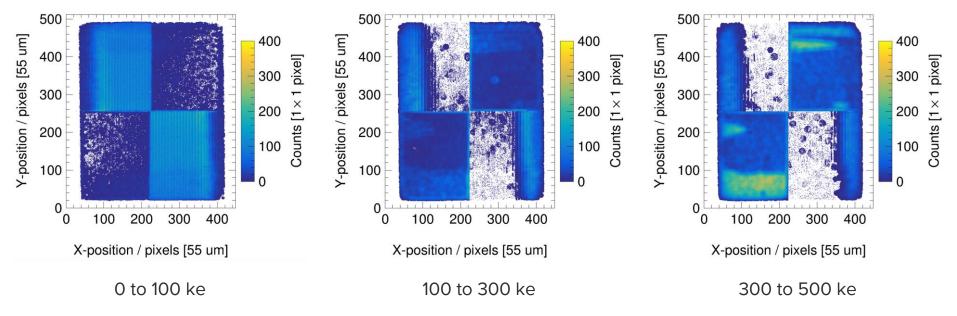

## First results Spectroscopy

X-ray **image has some structures**. Affects the quality of the <sup>55</sup>Fe spectrum.

Use the cluster information to **select the energy** and the plot the **hit positions** for each energy slice.

## First results Spectroscopy

Use the cluster information to select the energy and the plot the hit positions for each energy slice.

## First results Spectroscopy

Use the cluster information to select the energy and the plot the hit positions for each energy slice.