# Update on Flexible Printed Circuits (FPCs)

19/11/2024

M.Borri on behalf of WP3 Electrical Interfaces

### **Outline**

Low TRL OB prototypes: recap.

Status of assembly.

Test plan.

Conclusion and future work.

## Low TRL OB prototypes: time-line

- Defined requirements:

- **18/03/2024**

- Design review:

- **1**6/05/2024

- Prototypes delivery:

- **08/10/2024**

- Testing:

- To assemble to interface cards;

- To distribute and test;

Issue so far:

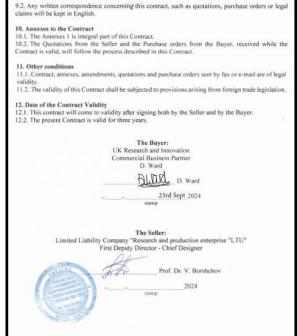

and then a Purchase Order needs to be sent by the Buyer to the Seller as a confirmation of quotatio

## Low TRL OB prototypes: delivery

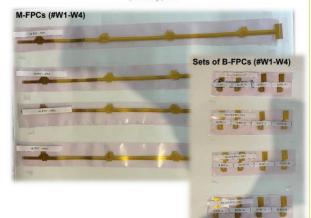

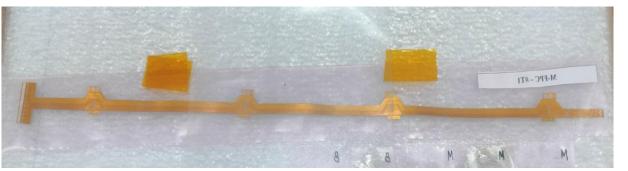

#### ePIC SVT L4 FPC prototypes and sets of FPCs shipped to STFC DIL

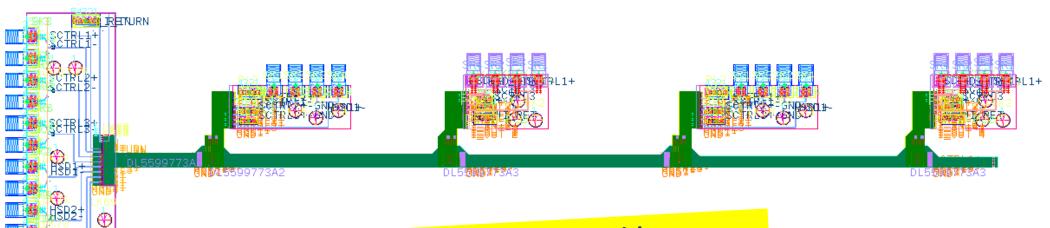

Assembled multilayered multicomponent ePIC SVT L4 FPC prototypes

L4 FPCs (#1-4)

Sets FPCs for ePIC SVT L4 FPC prototypes

#### **Delivered FPCs:**

- 4 prototypes of assembled ePIC SVT-L4 FPC

- 4 sets of FPC prototypes for ePIC SVT-L4 FPCs (4 M-FPCs+ 16 B-FPCs)

October 10, 2024

ePIC SVT WP3 Electrical Interfaces Meeting

viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

Note: all FPCs are packed in ESD protective film packages

A lot of details in the design...

#### I.Tymchuk:

30 masks in total were required for M-FPC + B-FPC-A + B-FPC-B; i.e. 10 photomasks for each FPC were required; (usually a 2 layer FPC requires up to 6 masks)

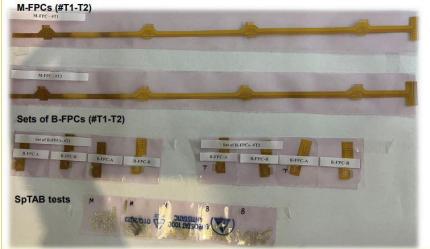

### Additional (test) FPCs shipped to STFC DIL

Additional Test FPCs delivered for SpTAB tunning, test procedure/fixture tunning etc.

#### Additionally delivered:

- ✓ M-FPC - 2pcs

- √ B-FPCs - 2 sets (4x2 B-FPCs)

- √ SpTAB test elements (~70pcs)

#### Important notes:

- ✓ M-FPC OK (only a bit imperfectness in interlayer aligning presents)

- ✓ B-FPCs 6 pcs are OK, only 2pcs are NOK (marked by letter T)

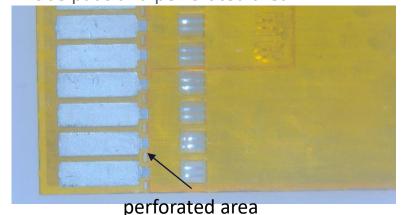

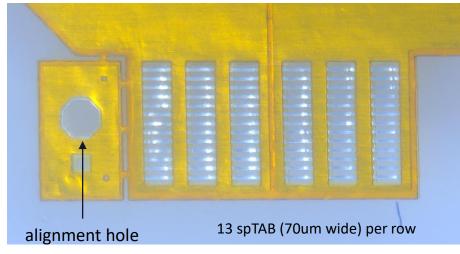

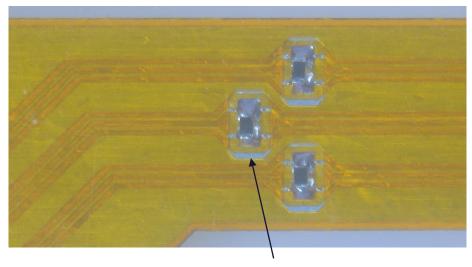

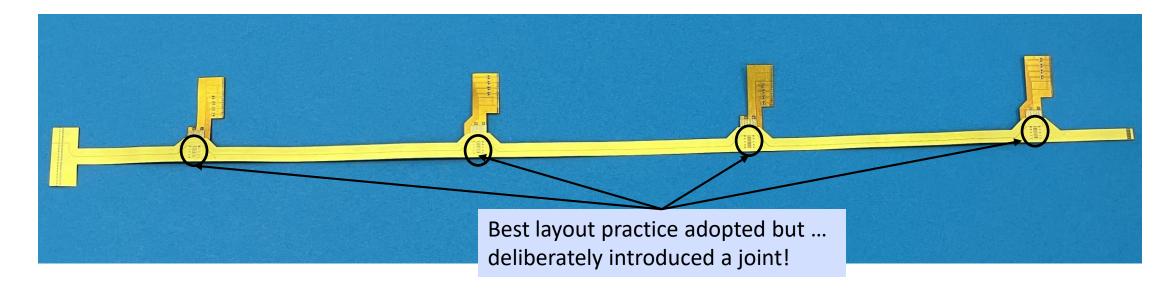

## Low TRL OB prototypes: visual inspection at DL

Alignment of FPC to interface PCB

Probe pads and perforated area

Current in/out spTABs at joint with bridge FPC

0201 components

voids?

# Low TRL OB prototypes: visual inspection at DL

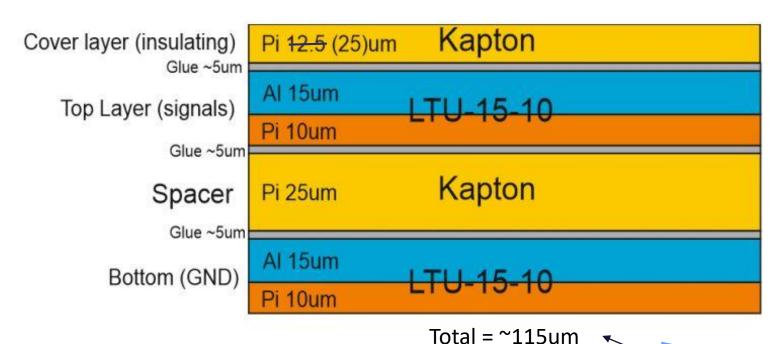

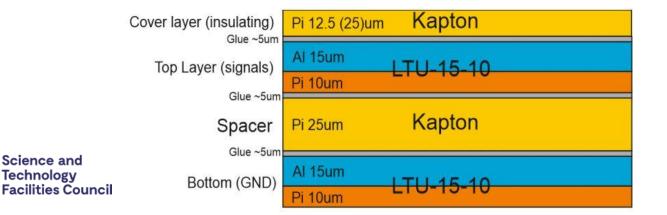

Schematic cross-section of M-FPC and B-FPC

Difference ~3.6um

Measured 111.4um

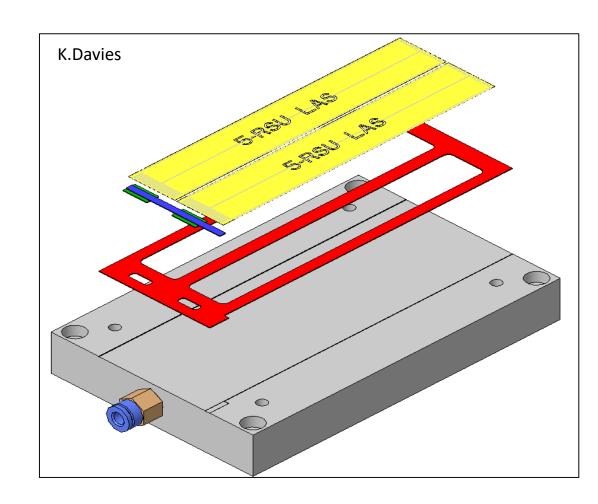

## Low TRL OB prototypes: interconnection

- Interconnection required in order to enable electrical testing;

- The FPCs are interconnected to interface cards;

- This improves signal transmission to/from the FPC;

- We start simple:

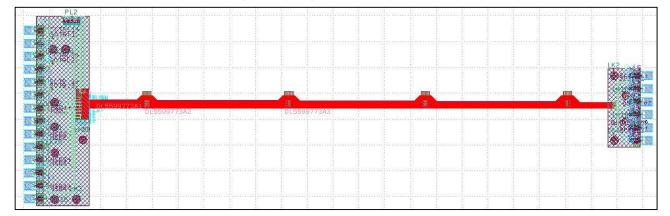

- M-FPC to interface cards;

Sketch of the main FPC (M-FPC) to interconnected to interface cards

marcello.borri@stfc.ac.uk

## Low TRL OB prototypes: interconnection

- Selection of interconnection site, options:

- RAL

- Oxford

- L'pool (only briefly)

- B'ham ✓

- From July 2024:

- Discussed details of the job;

- Visited sites;

- ... but because we could not estimate a delivery date, nothing tangible happened. (Pressure from other jobs/projects)

- Converged on the selection of the interconnection site later than expected.

Wedge required to spTAB prototypes to interface PCBs

Ordered by J.Glover, estimated delivery ~11/12/2024.

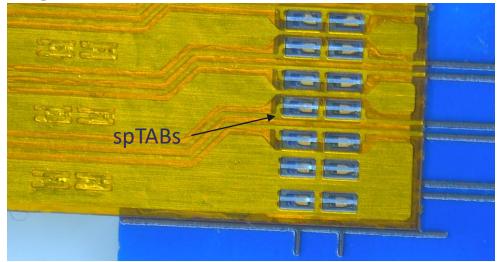

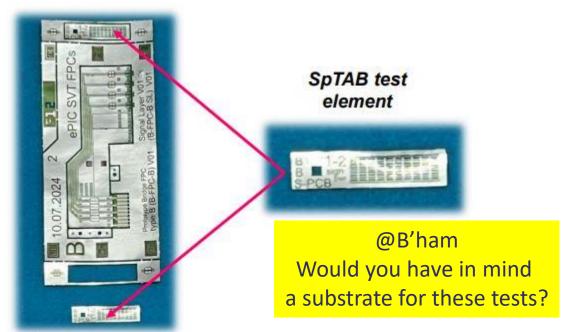

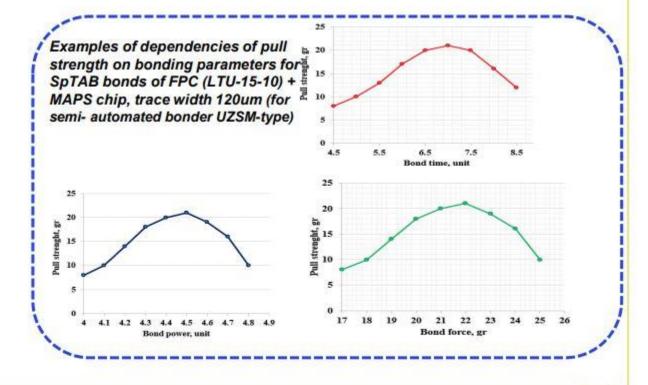

## SpTAB test elements for investigating/checking bond parameters

- For SpTAB need to be done investigating and verifying bonding parameters

- For this purpose special bond test elements are using (same trace width as in bond area)

- Bond test elements are made of same material as object for bonding (top and bottom layers of multilayered flex)

- Bond parameters need to be investigated/verified for each/different bonder

Note:

typically SpTAB test elements are delivering together with FPCs

ihor.tymchuk@cern.ch

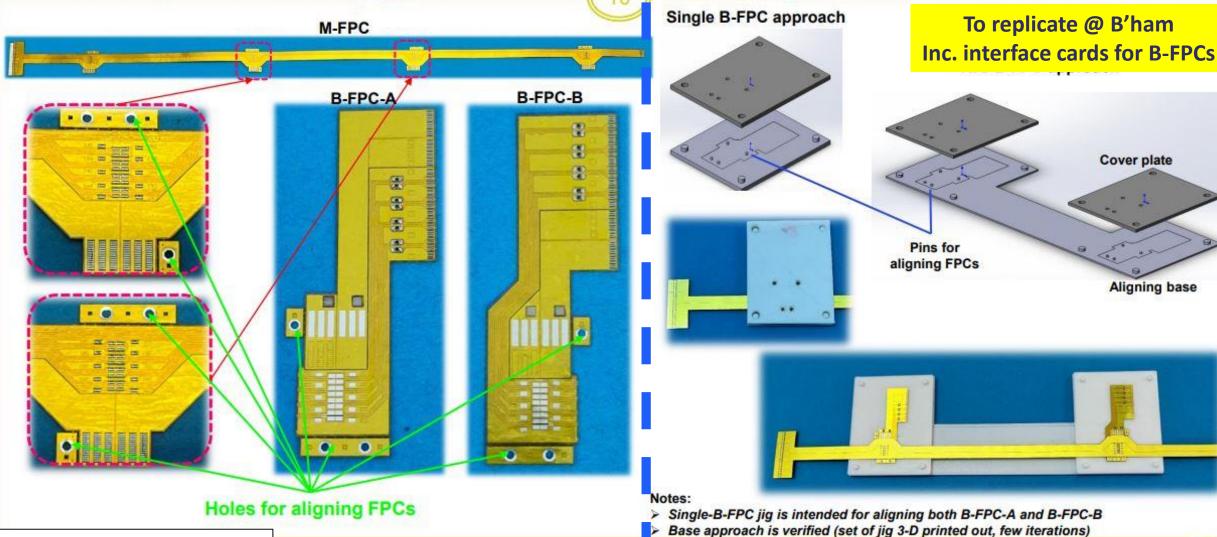

## Possible approach to aligning FPCs and 3-D printed jig for assembling ePIC SVT FPC

Further down the line to try in-house spTAB bonding of B-FPCs to M-FPCs

viatcheslav.borshchov@cern.ch,

## Low TRL OB prototypes: interconnection further steps

ToDo - difficult!

B'ham to propose assembly sequence?

Example

1- B-FPC to B-int'face-PCB 2- B-FPC to M-FPC

3- M-FPC to M-int'face-PCB

# What do we test for: signal and pwr integrity

- Signal integrity.

- The ability to propagate signals without distortions

- Factors that contribute to signal integrity degradation:

- Reflections

- Impedance discontinuities

- Cross talk

- Mutual parasitic capacitance & inductance

- Skew

- Propagation delays

- Jitter

- Non-uniform impedance, crosstalk, interference, and power supply noise

- Signal attenuation

- Losses caused by conductive and dielectric energy dissipation.

- Power integrity

- Reduced Noise pick up

- Decoupling capacitors (Equivalent Series Resistor)

- Coherent grounding strategy over the Power Distribution Network

- Acceptable IR drop (and related FPC power consumption)

## Signal integrity: layout dependent

The most important cause of signal integrity issues in a PCB is faster signal rise times.

|   | Signal name            | Type | Comment                                     | Coupling   | Standard                          | lpGBT eLink  | Rate                  |

|---|------------------------|------|---------------------------------------------|------------|-----------------------------------|--------------|-----------------------|

|   | slow ctrl clk (down)   | AC   | from lpGBT to AncASIC                       | Capacitive | CERN Low Powering Signal (CLPS)   | clock-eLink  | 80 Mb/s               |

|   | slow ctrl write (down) | AC   | from lpGBT to AncASIC                       | Capacitive | CERN Low Powering Signal (CLPS)   | output-eLink | 80 Mb/s               |

|   | slow ctrl read (up)    | AC   | from AncAsic to IpGBT                       | Capacitive | CERN Low Powering Signal (CLPS)   | input-eLink  | 160 Mb/s              |

|   | data                   | AC   | from AncAsic to VTRX+ (1 diff line/AncASIC) | Capacitive | CERN Low Powering Signal (CLPS)   | N/A          | 5.12 Gb/s (or 10Gb/s) |

| V | voltage supply         | DC   | Max: (2.5V/AncASIC) * (4 AncASIC)           | Direct     | 10% Vdrop for 2.5V/LAS, is it OK? | N/A          | N/A                   |

|   | current                | DC   | 2.5 A (total per AnASIC)                    | Direct     |                                   | N/A          | N/A                   |

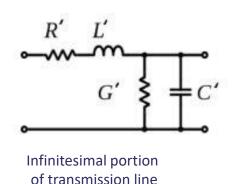

## Transmission lines – signal attenuation

Science and

**Technology**

KCL + KVL

$$\frac{\partial v(z,t)}{\partial z} = -Ri(z,t) - L\frac{\partial i(z,t)}{\partial t} \\ \frac{\partial i(z,t)}{\partial z} = -Gv(z,t) - C\frac{\partial v(z,t)}{\partial t}$$

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z}$$

$$I(z) = I_0^+ e^{-\gamma z} + I_0^- e^{\gamma z}$$

#### Schematic cross-section of M-FPC and B-FPC

Let  $y = \alpha + i\beta$  or  $\alpha + i(2\pi/\lambda)$

y = complex propagation constant

a = attenuation constant (nepers/unit length)

$\beta$  = phase constant (radians/unit length)

$\lambda = wavelength$

$\omega$  = angular frequency (radians/second)

$$\alpha = \alpha_C + \alpha_D + \alpha_G + \alpha_R$$

$\alpha_C = loss$  due to metal conductivity

$\alpha_D = loss$  due to dielectric loss tangent

$\alpha_G = loss$  due to conductivity of dielectric

$\alpha_B = loss$  due to radiation

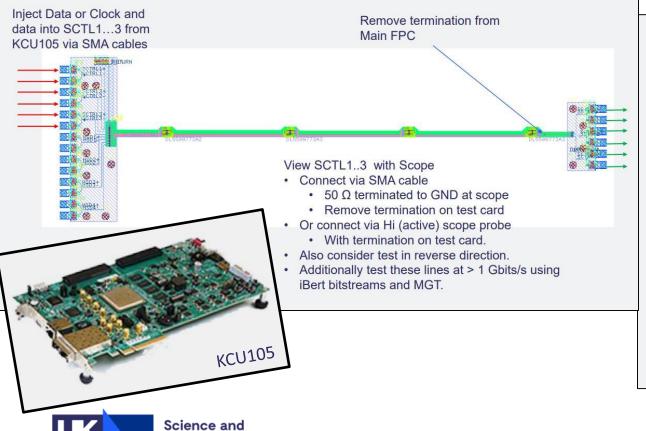

### Testing – first tests to do at DL

### Main FPC only, slow control

Technology Facilities Council

### **Equipment**

| EK-U1-KCU105-G    | https://www.digikey.co.uk/en/pro<br>ducts/detail/amd/EK-U1-<br>KCU105-G/5080514                        | KCU105             |  |

|-------------------|--------------------------------------------------------------------------------------------------------|--------------------|--|

| CCSMA-MM-SS402-24 | https://www.digikey.co.uk/en/pro<br>ducts/detail/crystek-<br>corporation/CCSMA-MM-<br>SS402-24/2137809 | 24 inch cable.     |  |

| CCSMA-MM-SS402-36 | https://www.digikey.co.uk/en/pro<br>ducts/detail/crystek-<br>corporation/CCSMA-MM-<br>SS402-36/2137810 | 36 inch cable.     |  |

| ADP-SMAF-BNCM     | https://www.digikey.co.uk/en/pro<br>ducts/detail/linx-technologies-<br>inc/ADP-SMAF-BNCM/9826665       | BNC to SMA adapter |  |

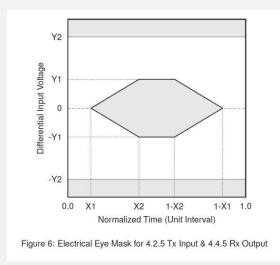

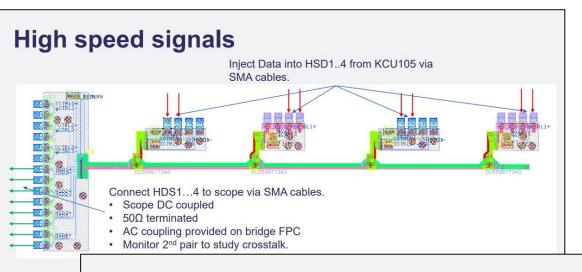

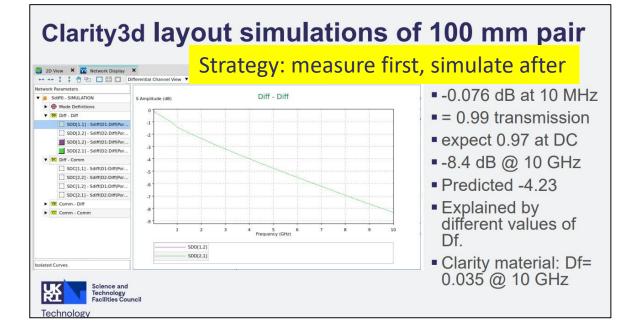

## High speed data & first tests

#### **VTRx+ TX input Eye mask**

| Specification   | Value   |

|-----------------|---------|

| X1 @ UI=97.66ps | 10.7 ps |

| X2              | 30.3 ps |

| Y1              | 95 mV   |

| Y2              | 350 mV  |

Technology

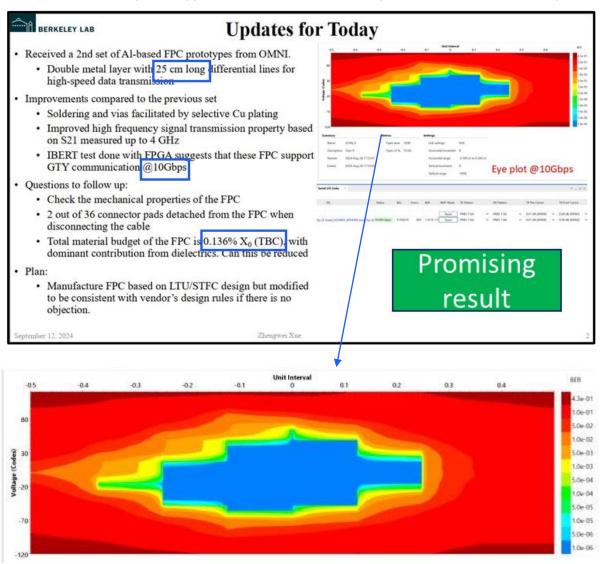

#### LBNL results w prototypes from Omni Circuits (dielectric is ArlonEmd)

... conversion to Volt and time possible.

## Further testing

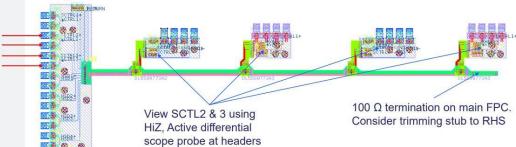

#### Slow Control Clock and TX data SCTL2 & 3

Inject Data or Clock and data into SCTL2...3 from KCU105 using SMA cables

Science and Technology Facilities County

- To rent higher spec equipment:

- Lecroy WaveMaster8330HD 33GHz scope (33 GHz, 12 bits, 160 GS/s, 200 Mpts)

- Lecroy WavePulser40iX 40GHz TDR instrument

- Discussed first month free of charge with supplier.

stfc.ac.uk

### Conclusion

- Characterization of FPCs will start in the new year.

- Valuable learning from the design and procurement stage.

- Currently learning on how to spTAB the FPCs to their interface cards.

- Starting to work on the definition stage of the next FPC iteration (module)