# White Rabbit Timing (WRT)

**Status Update**

G. Kruk on behalf of the White Rabbit Timing team

## **Outline**

- Introduction

- White Rabbit Timing Network

- WREN Boards v1

- Front-End Software

- Next Steps

- Summary

## **White Rabbit Timing**

### Physical Network

- RS-485 copper cables, GMT repeaters → fibers and WR switches (1Gb)

- Manual link delay calibration → automatic, sub nanosecond

- One directional → Possibility of many transmitters

## Central Timing Receiver (CTR) → White Rabbit Event Node (WREN)

- $8 \rightarrow 32$  counters

- More external inputs: 6+8 (VME), 2+4 (PCIe)

- More internal clocks: 1KHz, 1MHz, 10MHz, 40MHz, 1GHz, RF Frev and Bunch (LHC & SPS)

- Simpler generation of pulse trains

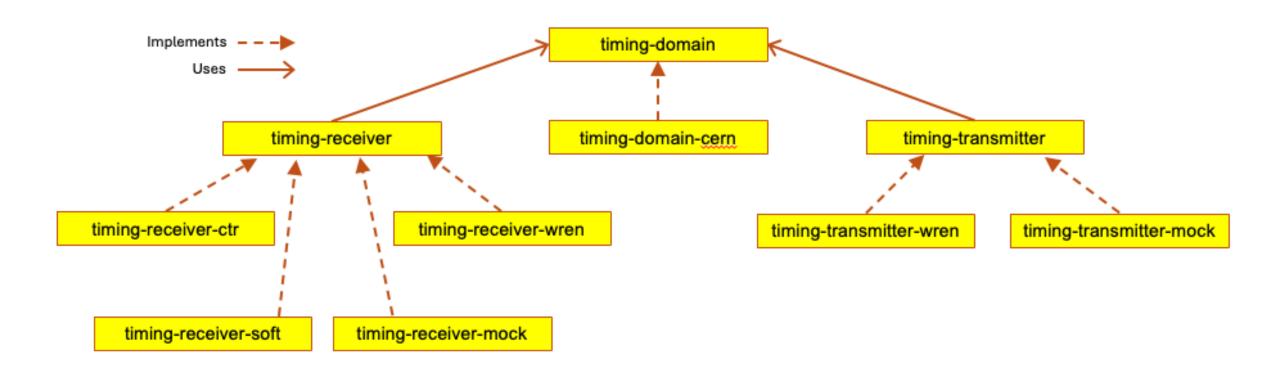

## Front-End Library

- Simpler API, C++ only

- Implemented for WREN, CTR and Mock

- No timService process on the FEC

- New LTIM FESA class

## **Beam Synchronous Timing & Safe Machine Parameters**

## Beam Synchronous Timing (BST)

- Selected timing events, along with telegram values and RF clocks

- Encoded into frames by BST Master and distributed via a dedicated BST network

- Received and decoded by dedicated BOBR modules or VFC-HD-core

## Safe Machine Parameters (SMP)

- Beam energy and intensity, safe beam flags, ...

- Data collected from various sources by the SMP arbiter module

- Today distributed:

- Via dedicated links to critical users

- Via GMT at 10Hz to FESA classes

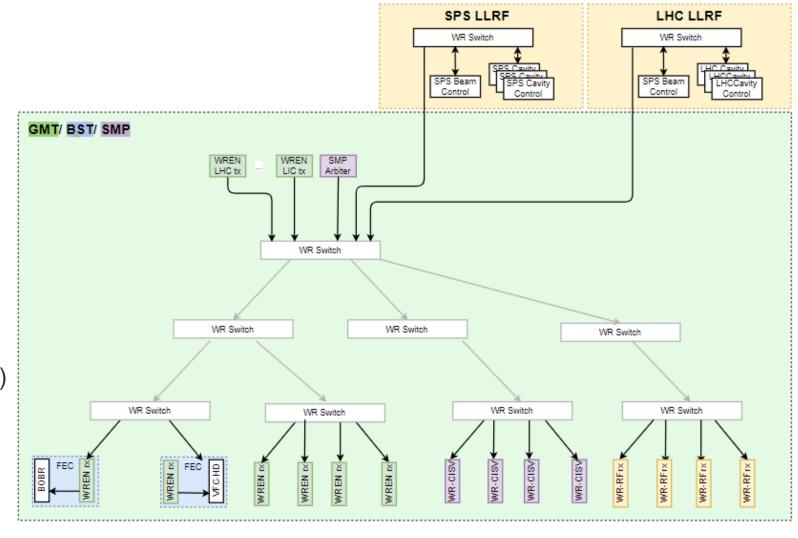

## GMT/BST/SMP/RF over WR

### GMT

Reception by WREN

### SMP

- Reception at 10Hz by WREN

- Reception at 1KHz by CISU

### RF Clocks

- Reception by WREN

- Reception by WR2RF (precision)

### BST

WREN as a local BST Master

# **High-Level Plan**

|  | When       | Milestone                                                          |

|--|------------|--------------------------------------------------------------------|

|  | Q4 2024    | Tests start by Equipment groups in labs                            |

|  | Q1-Q2 2025 | Installation of WRT on selected operational pilot FECs             |

|  | Q2 2025    | Migration of 3MeV Test Stand, SM18 and FAIR Test Facility          |

|  | LS3        | Renovation of the LHC and the SPS (Including North Area and AWAKE) |

|  |            | Aligned with the renovation of SMP and BST                         |

|  | LS4        | Renovation of the remaining machines                               |

# **Current Status**

# White Rabbit Timing Network Optical Fibers Installation

| When         | Where                                                                              |

|--------------|------------------------------------------------------------------------------------|

| Now          | Equipment groups' labs (see next slide)                                            |

| YETS 2024/25 | LHC Experiments' labs                                                              |

| YETS 2024/25 | LINAC3 / LEIR (for pilot FECs)                                                     |

| Q2 2025      | SM18 & FAIR test facilities (3MeV TS already done)                                 |

| LS3          | The entire accelerator complex (LS3 installation plans by EN-EL expected in Q4'24) |

# White Rabbit Timing Network Priority List

| Group  | Room                   | Status    |

|--------|------------------------|-----------|

| SY-ABT | 865/2-A08              | Installed |

| SY-BI  | 865/R-B05<br>866/R-D02 | TBC       |

| SY-EPC | 866/1-C04              | Installed |

| SY-RF  | 864/R-C08              | TBC       |

| TE-MPE | 272/S-008<br>30/5-040  | Installed |

| TE-MSC | 30/3-036               | Installed |

## **WREN Boards v1**

### VME

- 6 fixed inputs (In1..In6) [new]

- 8 configurable I/Os (InOut1..InOut8)

- BST Outputs (P0, P2)

- ~30 produced

## PCle

- 2 fixed inputs (In1..ln2) [new]

- 4 configurable I/Os (InOut1..InOut4)

- ~20 produced

## Patch Panel

• 32 outputs (Out1..Out32)

## **Front-End Software: Library**

## Front-End Software: LTIM and WREN (v 10.x.y)

#### LTIM

- Management of triggers (pulses, interrupts)

- Conceptually the same as old LTIM, few changes in property and field names

- e.g. OutEnable → Enabled

- New configuration options reflecting the capabilities of WREN

#### WREN

- Pin directions (for configurable pins): In, Out

- Input active edges: rising, falling

- Input labels

- Output levels (aka polarity): active high (TTL), active low (TTL\_BAR)

- Output gates: OR, AND

- Module diagnostics

# Front-End Software: CLI test program (wrtdr)

- Configuration of the WREN board

- Management of LTIMs

- Subscriptions on interrupts (Central Timing events and LTIMs)

- Diagnostics and troubleshooting

## **Front-End Software: Status**

- Integration with FESA framework done

- Not supporting yet selectors different than USER e.g. SPS.DYN\_DEST.AWAKE

- CLI test program done

- Demo on Friday

- Finishing support for fixed inputs

- Change with respect to WREN v0

- Final adjustments of the public API

- timing-domain, timing-receiver, LTIM, WREN

- Preparing a dedicated transmitter FEC

- Mirroring super cycles played by the operational LIC Central Timing

- LHC events transmission planned for Q1 2025

# **Next Steps**

- Meeting this Friday, with more technical details

- Present the APIs, tools and release procedure

- Get your feedback

- Release timing libraries and the FESA framework

- Around mid-November

- Installation of WR switches and WREN boards

- By BE-CEM-IN

- Complete WRT EDMS 2.0 document and send it for approval

- With updated milestones for 2025 and LS3

# **Summary**

- The project is moving according to the plan

- Although we do have a bit of delay

- Technical meeting this Friday to get your feedback

- We still need a few weeks to wrap it up → Aiming at mid-November

- Release of the FEC software stack

- Transmission of LIC events

- Installation of WR switches and WRENs

- LHC events to be transmitted in Q1 2025