# ERN

## Development of radiation-hard active sensors in 180 nm HV CMOS technology

Daniel Muenstermann (CERN) with most plots stolen from Ivan Peric (U Heidelberg)

Daniel Muenstermann | 19<sup>th</sup> RD50 Workshop | CERN | November 22<sup>nd</sup>, 2011

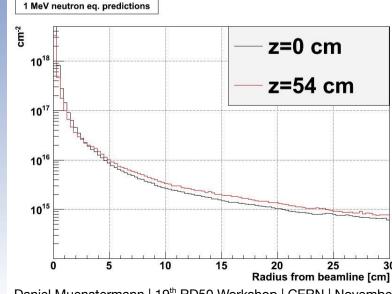

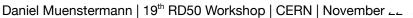

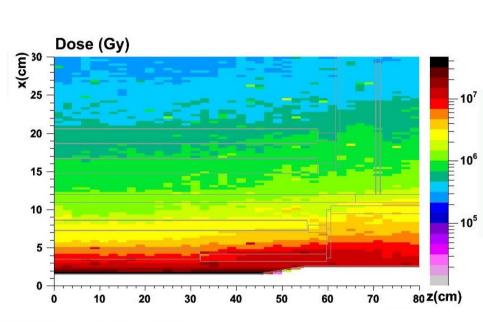

## Reminder: fluences at HL-LHC

- integrated luminosity: 3000 fb<sup>-1</sup>

- including a safety factor of 2 to account for all uncertainties this yields for ATLAS:

- at 5 cm radius:

- ~2•10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>

- ~1500 MRad

- at 25 cm radius

- up to 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup>

- ~100 MRad

- several m<sup>2</sup> of silicon

Active sensors

#### Silicon 1 MeV-equivalent flux

## **Implications**

- High fluences: trapping dominant

- reduce drift distance, increase field  $\rightarrow$  reduce drift time:

- 3D sensors

- thin silicon

- Iow depletion depth 'on purpose':

- Iow(er) resistivity silicon

- dedicated annealing to increase N<sub>eff</sub>

- Large areas: low cost of prime importance

- industrialised processes

- large wafer sizes

- cheap interconnection technologies

- Idea: explore industry standard CMOS processes as sensors

- commercially available by variety of foundries

- Iarge volumes, more than one vendor possible

- 8" to 12" wafers

- Iow cost per area: "as cheap as chips"

- (partially too) low resistivity p-type Cz silicon

- thin active layer

- wafer thinning possible

## AMS H35 and H18 HV-CMOS

- Project initiated and led by Ivan Peric (U Heidelberg)

- Austria Micro Systems offers HV-CMOS processes with 350 and 180 nm feature size, the latter one in cooperation with IBM

- biasing of substrate to ~100V possible

- substrate resistivity ~20 Ohm\*cm → N<sub>eff</sub> > 10<sup>14</sup>/cm<sup>3</sup>

- radiation induced N<sub>eff</sub> insignificant even for innermost layers

- depletion depth in the order of 10-20 µm

- on-sensor amplification possible and necessary for good S/N

- key: small pixel sizes → low capacitance → low noise

- additional circuits possible, e.g. discriminator

- beware of 'digital' crosstalk

- full-sized radiation hard drift-based MAPS feasible, but challenging

- aim for 'active sensors' in conjunction with rad-hard readout electronics first

#### Scope of the talk:

- Introduce the concept

- Present first results with test chips

- Outline a planned submission

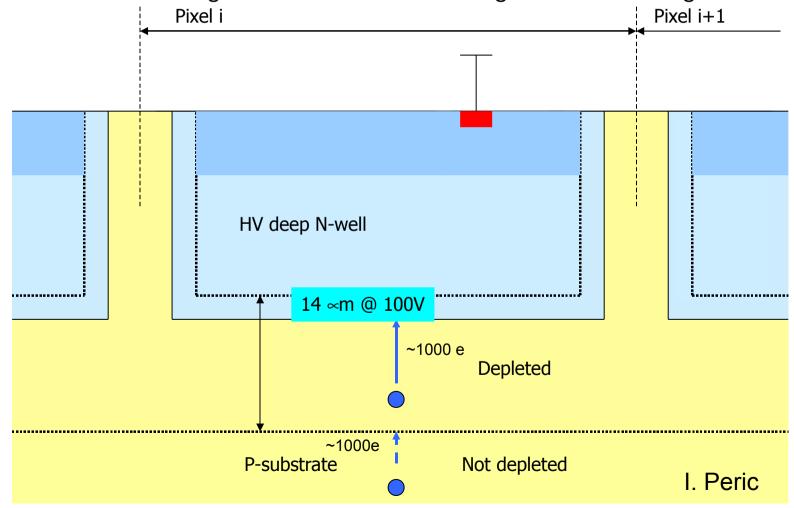

#### A HV-CMOS sensor...

- essentially a standard n-in-p sensor

- depletion zone 10-20 µm: signal in the order of 1-2ke-

- challenging for hybrid pixel readout electronics

- new ATLAS ROC FE-I4 might be able to reach this region but no margin

The depleted high-voltage diode used as sensor (n-well in p-substrate diode)

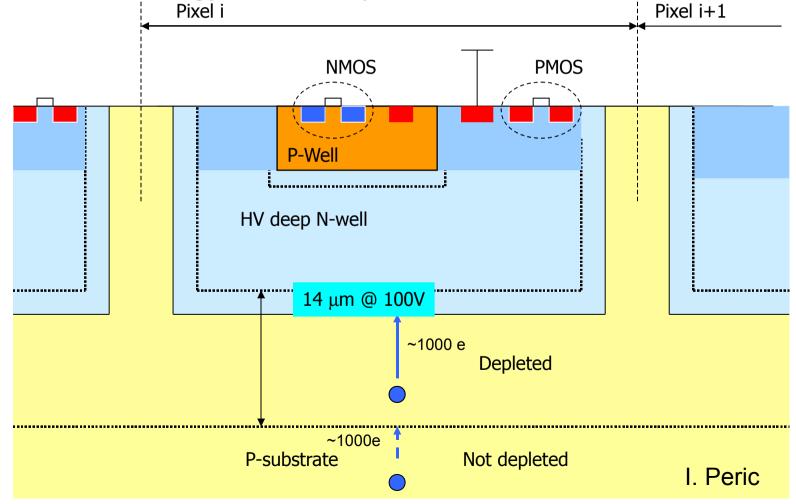

## ...including active circuits

- implementation of

- first amplifier stages

- additional cuircuits: discriminators, impedance converters, logic, ...

- deep sub-micron technology intrinsically rad-hard

CMOS electronics placed inside the diode (inside the n-well)

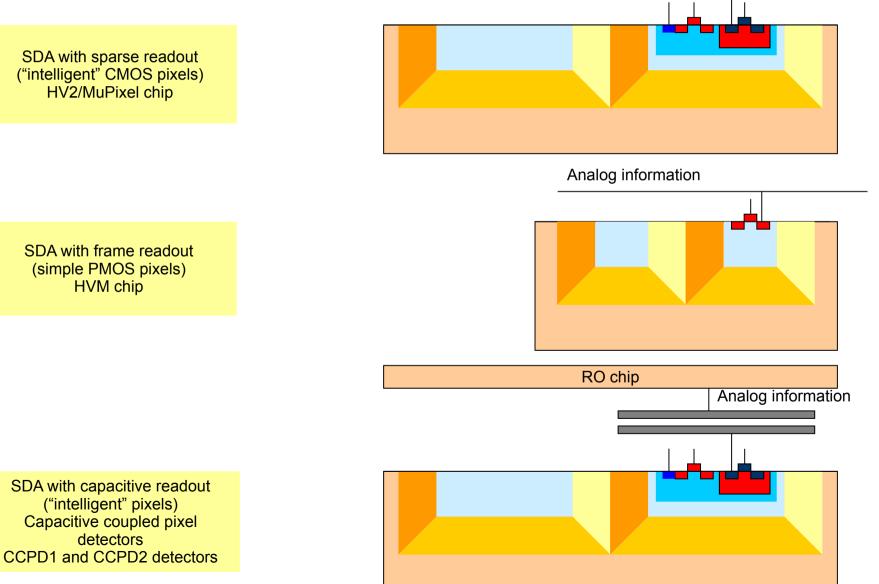

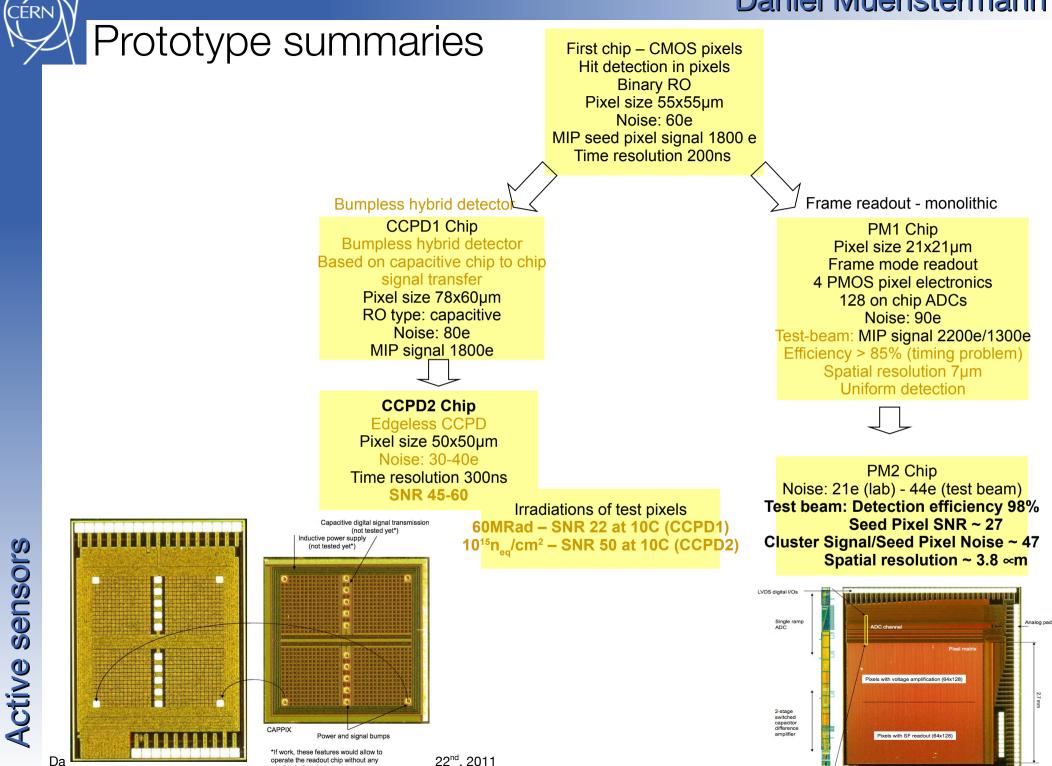

Prototypes

Several test-chips submitted in both technologies already

**Binary information**

Daniel Muenstermann | 19th RD50 Workshop | CERN | November 22nd, 2011

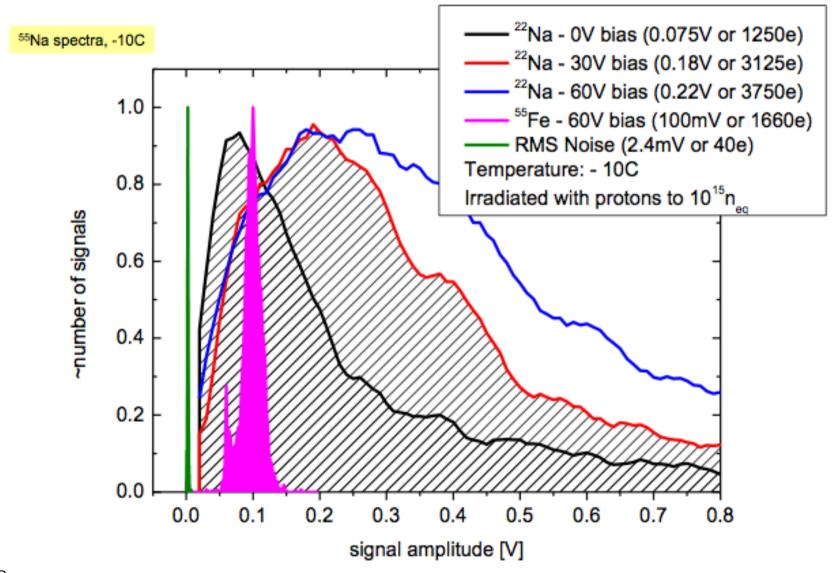

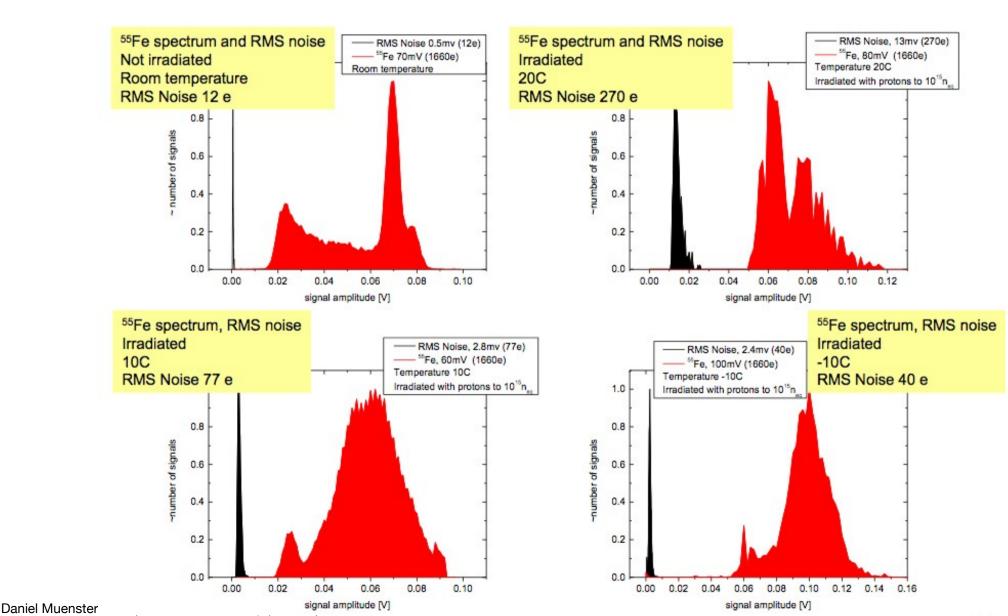

### Some irradiated prototype results

- Irradiation with 23 MeV protons: 1e15 neq/cm2, 150MRad

- generally very good S/N ratio

### Some irradiated prototype results

- Irradiation with 23 MeV protons: 1e15 neq/cm2, 150MRad

- FE-55 performance recovers after slight cooling

#### From MAPS to active sensors

- Existing prototypes would not suitable for HL-LHC, mainly because

- readout too slow

- time resolution not compatible with 40 MHz operation

- high-speed digital circuits would affect noise performance

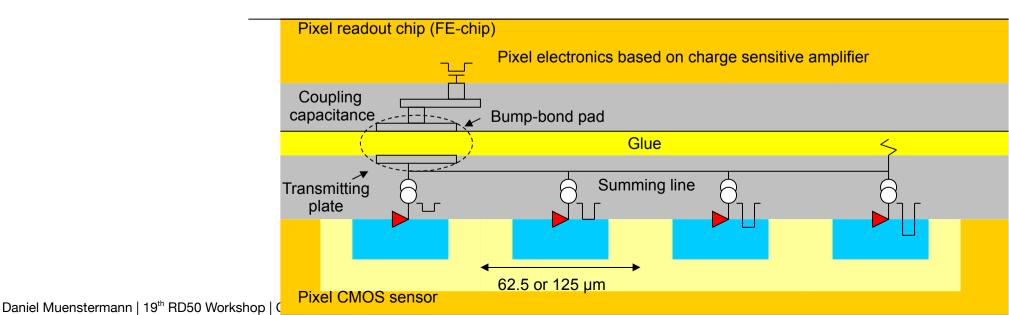

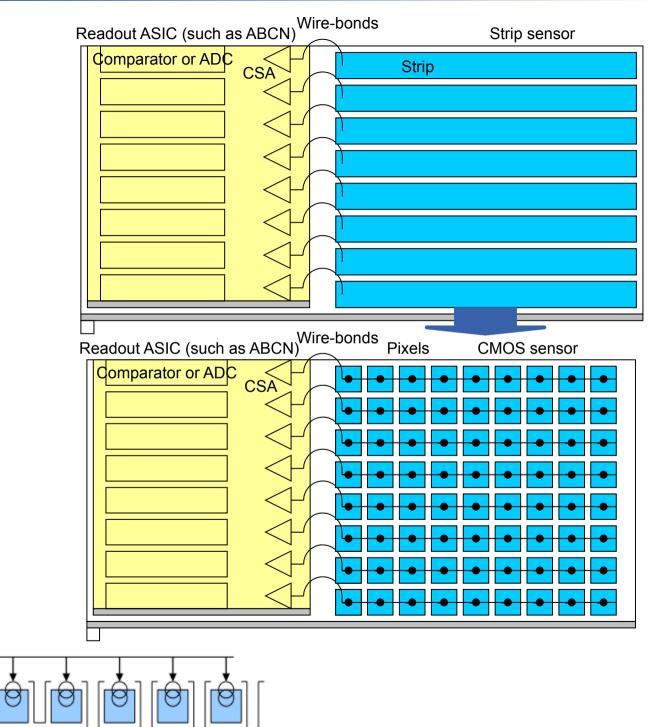

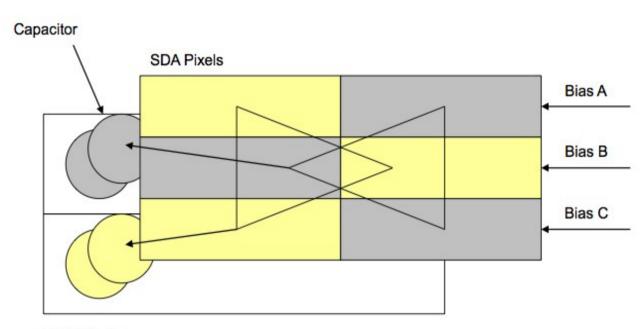

- Idea: use HV-CMOS as sensor in combination with existing readout technology

- fully transparent, can be easily compared to other sensors

- can be combined with several readout chips

- makes use of highly optimised readout circuits

- can be seen as first step towards a sensor being integrated into a 3Dstacked readout chip (not only analogue circuits but also charge collection)

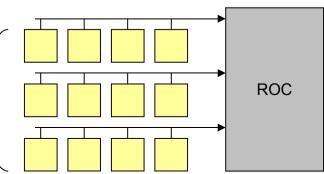

- Basic building blocks: small pixels (low capacitance, low noise)

Pixels

- can be connected in any conceivable way to match existing readout granularity, e.g.

- (larger) pixels

- strips

# Pixels

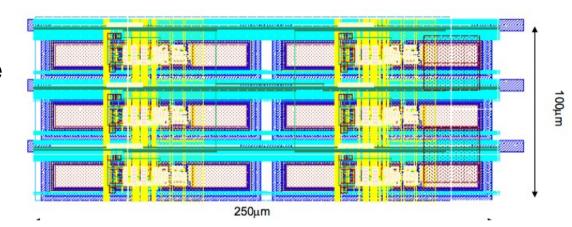

- Possible/sensible pixel sizes: 20x20 to 50x125 µm

- 50x250 µm (current ATLAS FE-I4 chip) too large

- combine several sensor "sub-pixels" to one ROC-pixel

- sub-Pixels can encode their address/position into the signal e.g. as pulseheight-information instead of signal proportional to collected charge

- routing on chip is well possible, also non-neighbour sub-pixels could be combined and more than one combination is possible

## Pixels

- Possible/sensible pixel sizes: 20x20 to 50x125 µm

- 50x250 µm (current ATLAS FE-I4 chip) too large

- combine several sensor "sub-pixels" to one ROC-pixel

- sub-Pixels can encode their address/position into the signal e.g. as pulseheight-information instead of signal proportional to collected charge

- routing on chip is well possible, also non-neighbour sub-pixels could be combined and more than one combination is possible

- Only reason not to use AC coupling with pixel sensors up to now was small coupling capacitance in association with low signal

- amplification possible, hence AC transmission not a problem at all

- would allow to get rid of costly bump-bonding

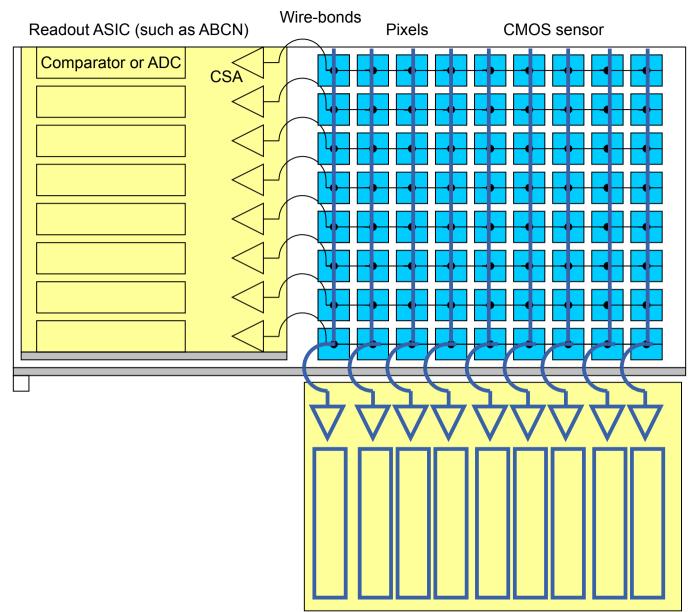

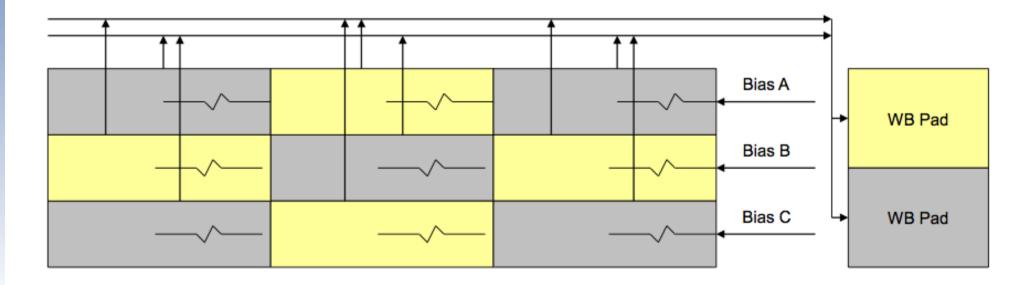

- Easiest idea would be to simply sum all pixels within a virtual strip

- Hit position along the strip could be again encoded by pulse height for analogue readout chips (e.g. Beetle)

Summing line

Active sensors

# Strips

- Signals are digital so multiple connections are possible, e.g.

- "crossed strips"

- strips with double width but only half the pitch in r-phi

#### Reticule size/stitching

- Sensor size is currently limited by reticule size of ~2x2 cm

- however, the yield should be excellent (very simple circuit, essentially no "central" parts) so it might be interesting to cut large arrays of sensors from a wafer and connect individual reticules by

- wire-bonding

- post-processing (one metal layer, large feature size)

- There are HV-CMOS processes/foundries which allow for stitching

- Very slim dicing streets

- Gaps between 1-chip modules could be rather narrow

| □<br>□<br>□<br>□<br>□<br>Chip2      |   |          |                                              | Chip2 |       |

|-------------------------------------|---|----------|----------------------------------------------|-------|-------|

| □<br>□<br>□<br>□<br>□<br>□<br>Chip1 |   |          | <ul> <li>Chip to chip connections</li> </ul> | Chip1 |       |

| Reticle1                            | C | ►<br>hip | to reticle edge distance = 80 um             | Ret   | icle2 |

| 4                                   |   | →        |                                              |       |       |

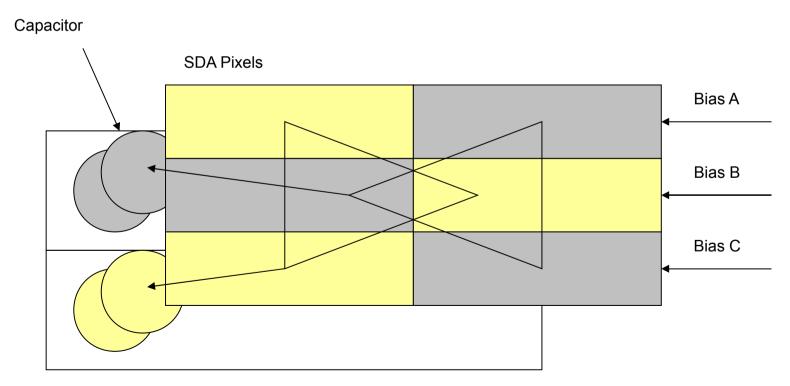

#### Current plans

- ATLAS institutes plan to submit a combined active strip/pixel sensor

- pixels match new ATLAS FE-I4 readout chip

- capacitive coupling

- bump-bonding possible

- strips should be compatible with ATLAS ABCN and LHCb/Alibava Beetle

- size: ~2x4mm

Strip Bus -> to wire bond pads

Pixel Bus -> to capacitive transmission electrodes

4-bit DAC

Daniel Mu

Active sensors

## Current plans

- Sub-pixel positions are encoded by 3-level pulses

- additive: unique pulse heights for all pixel combinations

- FE-I4's 4-bit ToT should be able to disentangle

**FEI4** Pixels

#### Conclusions

- HV-CMOS processes might yield radiation-hard, low-cost, improvedresolution, low-bias-voltage sensors

- First test chips indicate rad-hardness up to at least 1e15 neq/cm2

- Process can be used for

- drift-based MAPS chips (baseline for µ3e-Experiment at PSI)

- 'active' n-in-p sensors

- First design being submitted within ATLAS framework suited for

- capacitively coupled pixel sensors

- "virtual" strip sensors

- Irradiation and testbeam campaign planned for 2012

- up to HL-LHC fluences

Sensors

Active

- testbeam at CERN with Timepix telescope

- Hope to have raised interest in the community, will report on first "sensor" results at the next RD50 meeting

- if successful, might be sensible to also pursue an RD50-centric project to be able to include interest from all LHC experiments (and beyond)