### ATLAS Pixel Interconnects Issues

Workshop on Quality Issues in Current and **Future Silicon Detectors** 03 Nov. 2011 CERN

D. Dobos on behalf of **ATLAS Pixel**

#### Outline:

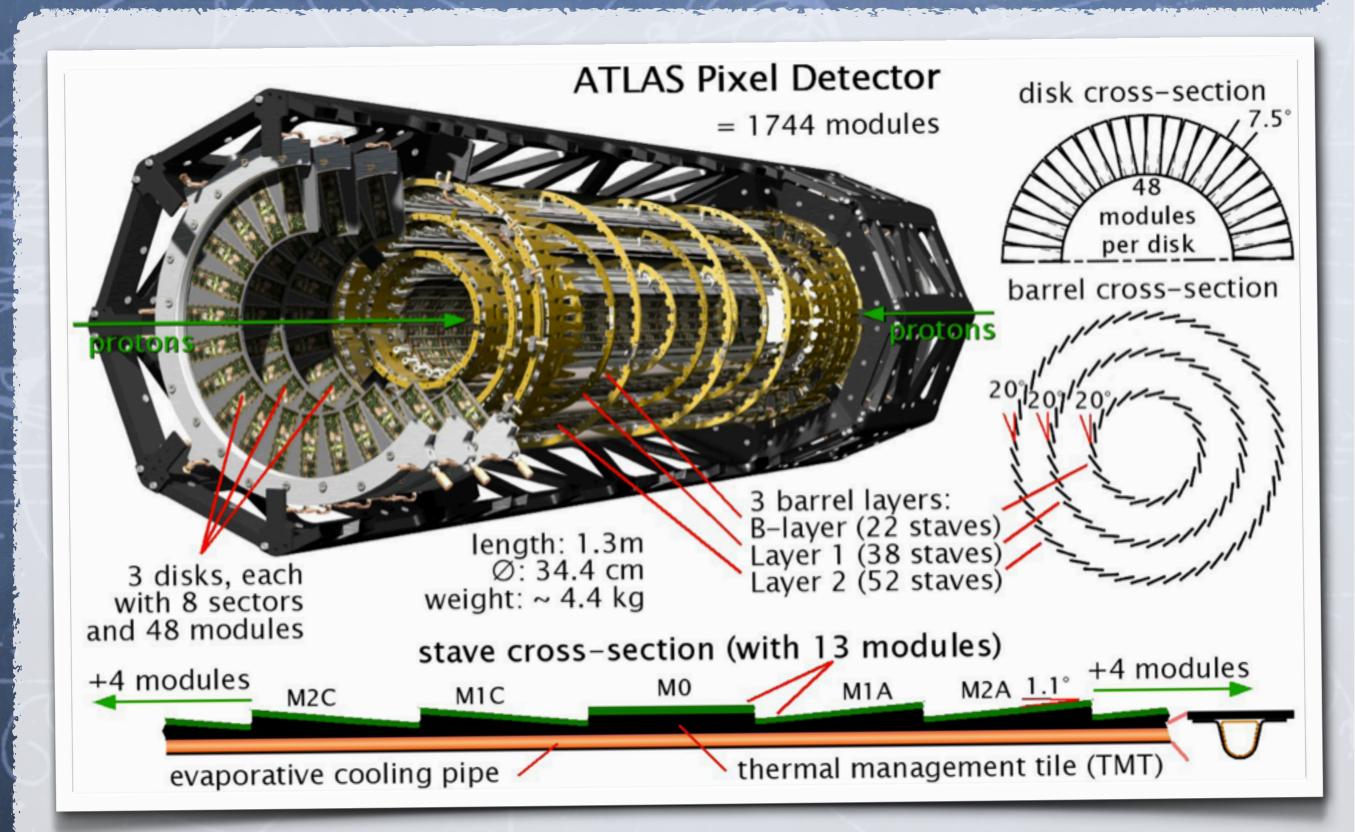

- ATLAS Pixel

- Bump Bonds

- Wire Bonds

# ATLANTSHELL OTHER OTH

# ANDTSHELL COUNTSHELL

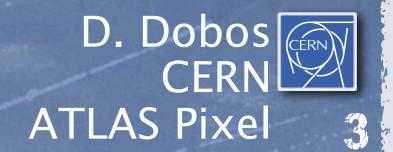

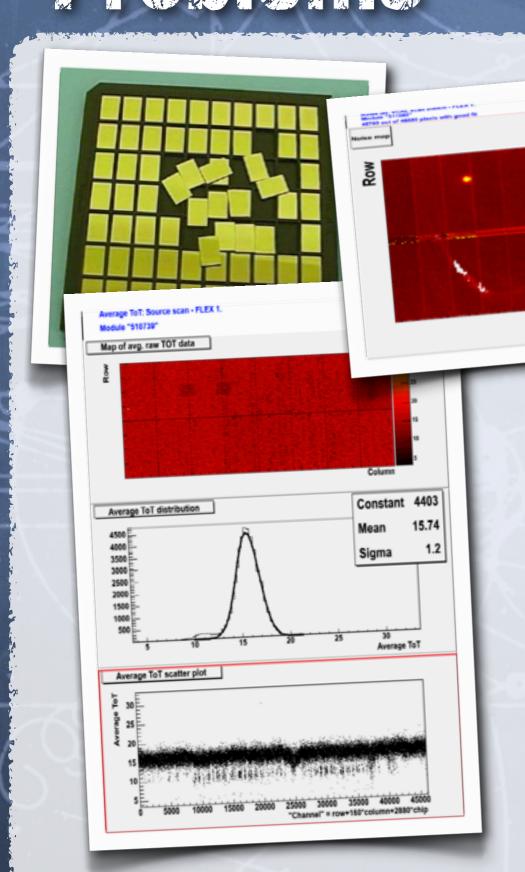

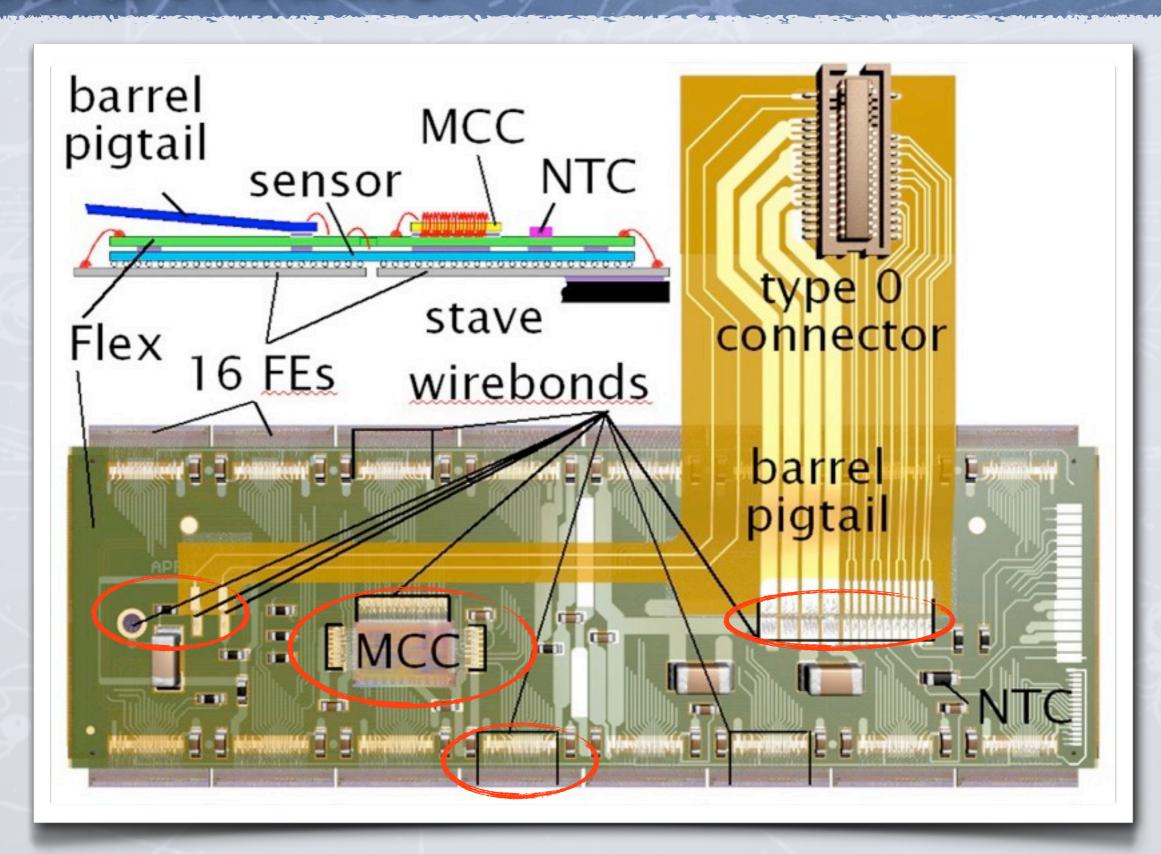

#### Pixel Module:

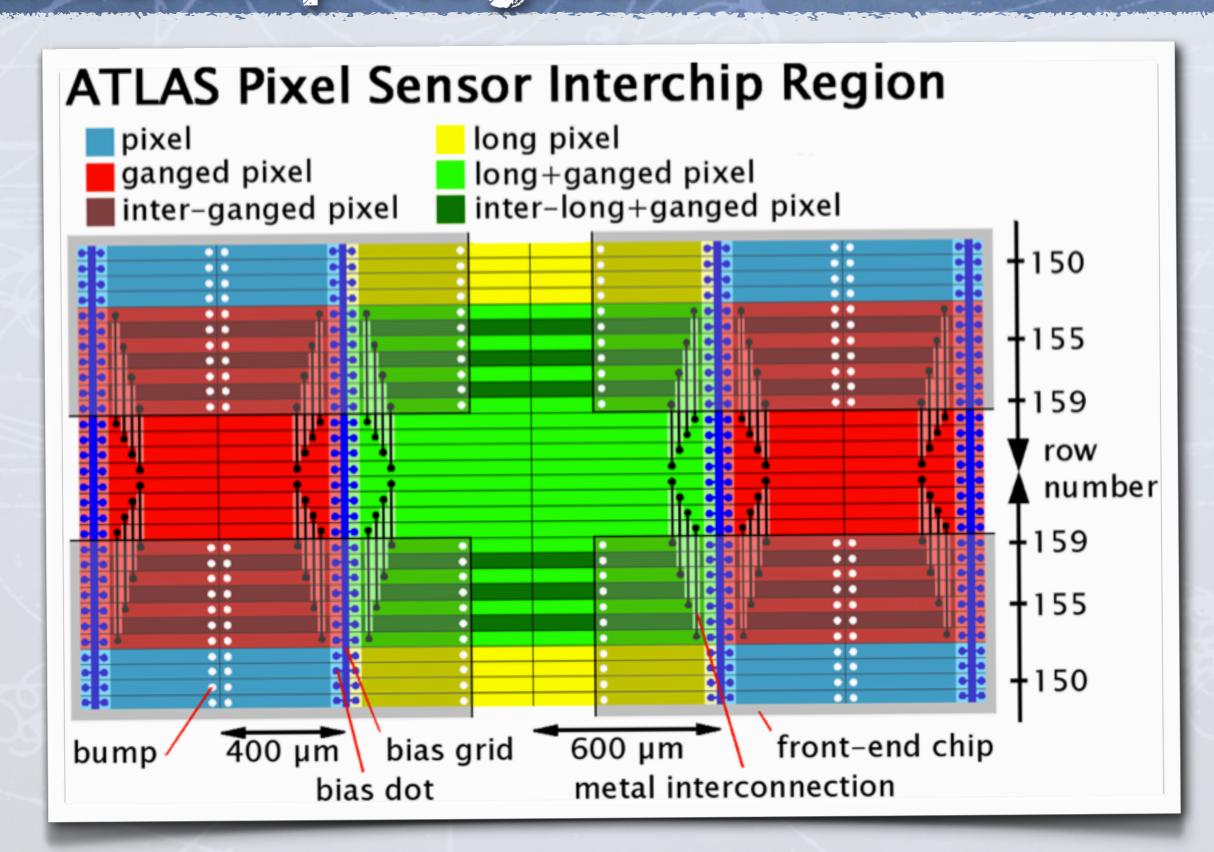

- Planar n-in-n silicon sensor (n<sup>+</sup>np<sup>+</sup>), 250 μm thick, active area: 16.4 x 60.8 mm<sup>2</sup>

- 16 FE-I3 readout chips, 180 µm thick, cover 7.2 x 10.8 mm<sup>2</sup> (2880 pixel cells) each, 3.5M transistors, 0.25 µm DSM technology

- Flexible circuit layer with Module Control Chip (MCC) and passive components

### FIXEI EUMON 5 STEPS Elonomy Frocess

More than 46k electrical connections between sensor & 16 FEs:

- Connection density: ~ 4,800 cm<sup>-2</sup>:

- Minimal pitch between two connections: 50 μm

- Only mechanical interface between the sensor and the FEs

- Challenging some years ago: high density, high yield, low pitch

- I. Deposition of a Under Bump Metallization (UBM) on the sensor and FE wafer

- 2. Deposition of bumps either only on the FE wafer or on the FE and sensor wafer

- 3. Thinning of the FE wafer down to about 180 µm

- 4. Dicing of the sensor and FE wafers and selection of good components by probing

- 5. Flip chipping of FE chips to the sensor after precision alignment and formation of electrical and mechanical connection at appropriate temperature and pressure

# FIXEI MOMINE TYPES INTERCION REGION

### Fixel Eumans Elzm Elonomo Venocrs

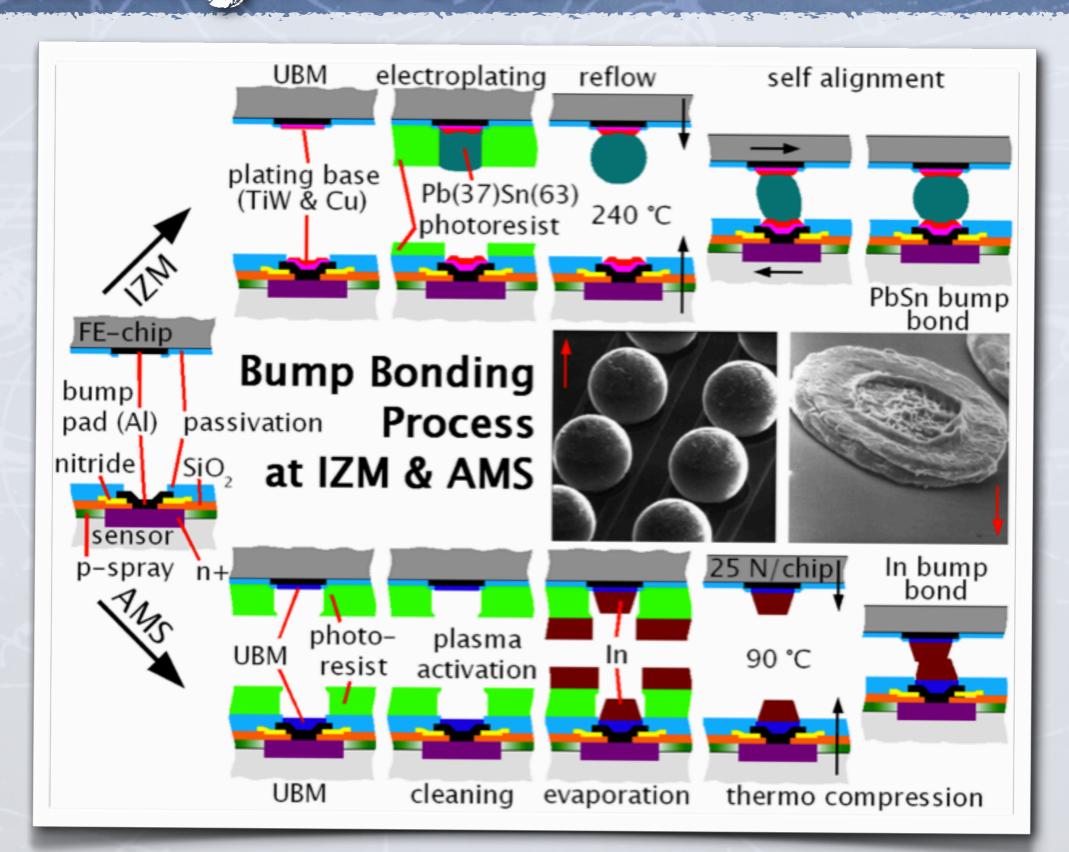

To have a technical redundancy during development and to use multiple sources to fill the needed quantities, two different

manufacturers of bare modules were used.

- IZM (Frauenhofer Institut für Zuverlässigkeit und Mikrointegration, Berlin, Germany) uses a bump bonding technique with solder bumps

- AMS (Alenia Marconi Systems, Roma, Italy) later SELEX uses indium bumps for the interconnections

Both manufacturers get the FE & sensor wafers provided with aluminum bump pads. Besides opening for bump pads, the rest of the wafer is covered with a SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> passivation layer.

# FIXEI EUMON 5 STEPS ECOMOTING FYOCESS

### SOIGER BUINDS & PBSN MOUITH BUINDS N & PBSN

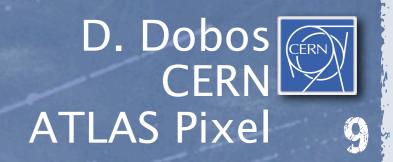

Advantage of indium bumps: lower flip-chip temperature Significant difference is interconnection electrical resistance:

- ullet Solder bumps have a constant resistance of about 0.5  $\Omega$

- Indium bumps resistance ~10  $\Omega$ . Increase up to 500 k $\Omega$  observed on ~10% indium bumps. Caused by In<sub>2</sub>O<sub>3</sub> oxidation layers on bumps can be broken by applying a 3 V bias voltage to electronics.

Bump resistances have to be kept small to avoid a significant contribution to the FE preamplifier noise.

### COMITY ECTRICAL COMITY OF AL

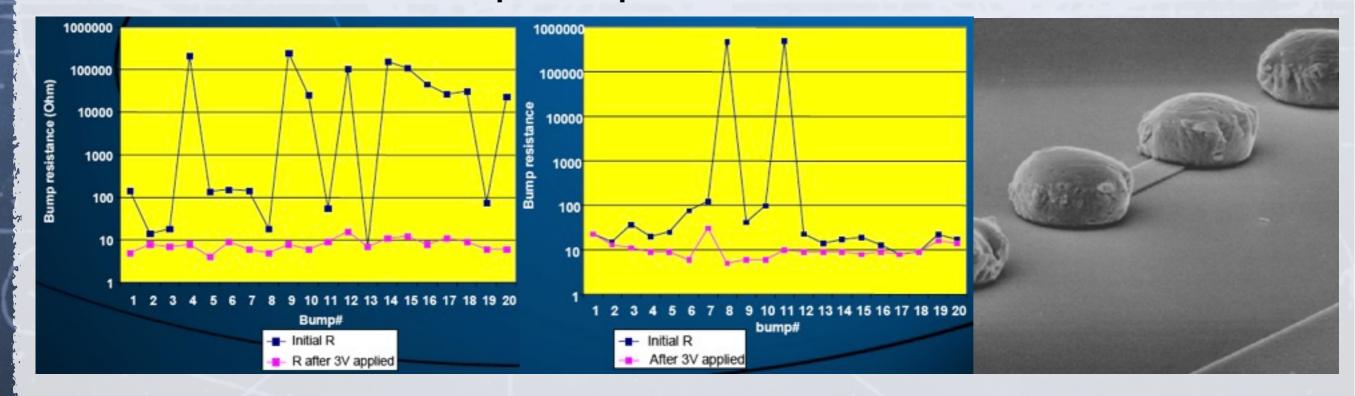

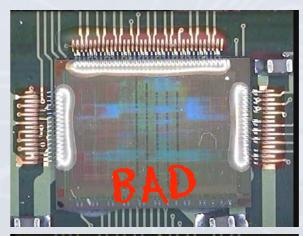

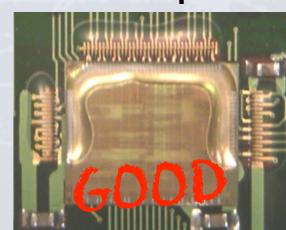

High resolution (2-5 μm) X-ray inspections with phosphor screen CCD system and pattern recognition used to detect merged and missing bumps. Results crosschecked with further electrical tests. FEs with bump defects (missing or merged bumps, residue between bumps, damaged FEs) can be reworked. Reworking FEs successfully demonstrated for both technologies.

### Fixel Eumons sizm Bonding Vendors

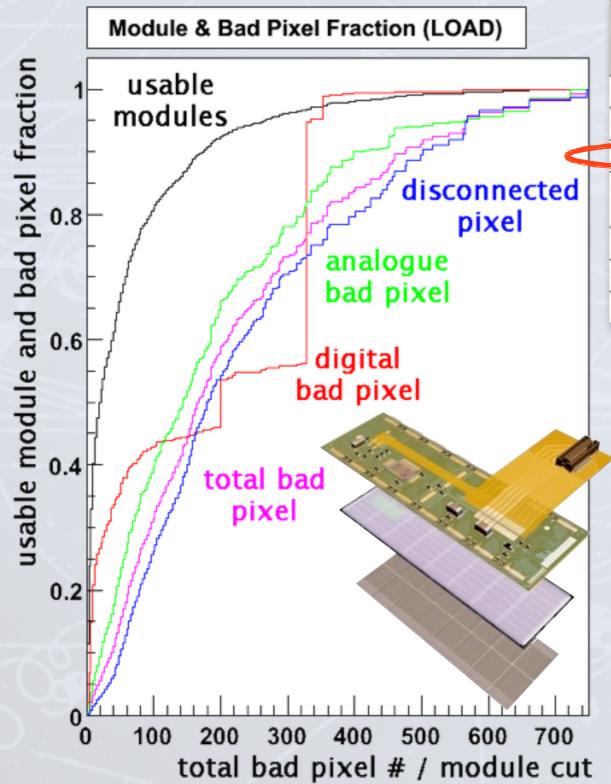

| Bad pixel type:              | LOAD bad<br>pixel amount<br>(fraction): | BIST bad<br>pixel amount<br>(fraction): | LOAD total fraction: | BIST total fraction: |

|------------------------------|-----------------------------------------|-----------------------------------------|----------------------|----------------------|

| digital injection            | 875 (0.9%)                              | 1047 (1.0%)                             | 0.013‰               | 0.016‰               |

| analogue injection           | 36542 (36.9%)                           | 40518 (37.1%)                           | 0.54‰                | 0.60‰                |

| disconnected                 | 61618 (62.2%)                           | 67760 (61.9%)                           | 0.92‰                | 1.00%                |

| barrel sum<br>(~67.1M pixel) | 99035                                   | 109325                                  | 1.5‰                 | 1.6‰                 |

| B-layer (~20%)               | 5105 (5.2%)                             | 5033 (4.6%)                             | 0.39‰                | 0.38‰                |

| Layer-1 (~34%)               | 32371 (32.7%)                           | 36850 (33.7%)                           | 1.42‰                | 1.62‰                |

| Layer-2 (~46%)               | 61559 (62.1%)                           | 67442 (61.7%)                           | 1.98%                | 2.17‰                |

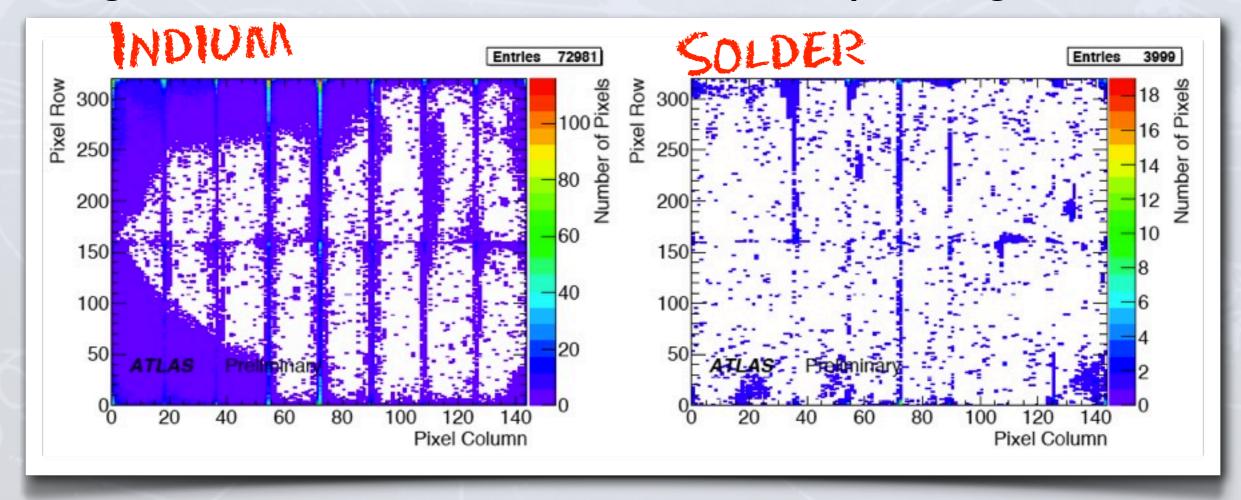

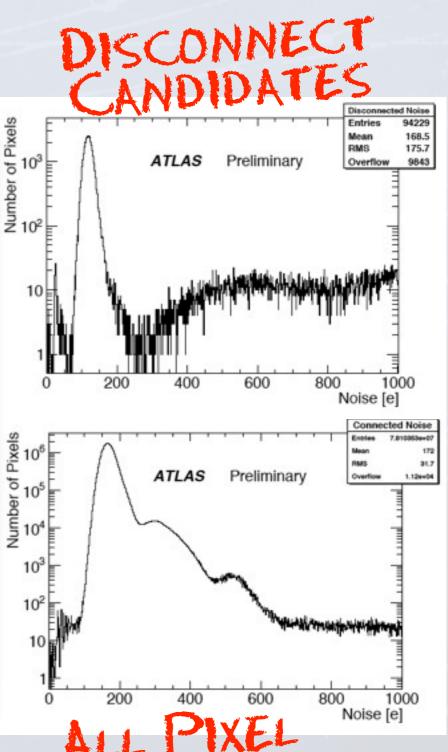

- Disconnected bumps is main reason (~1%) for bad pixels

- Can affect mechanical connection stability can provoke additional disconnected pixels increase for modules with a contiguous region of disconnected pixels is expected with mechanical stress, thermal cycling, ...

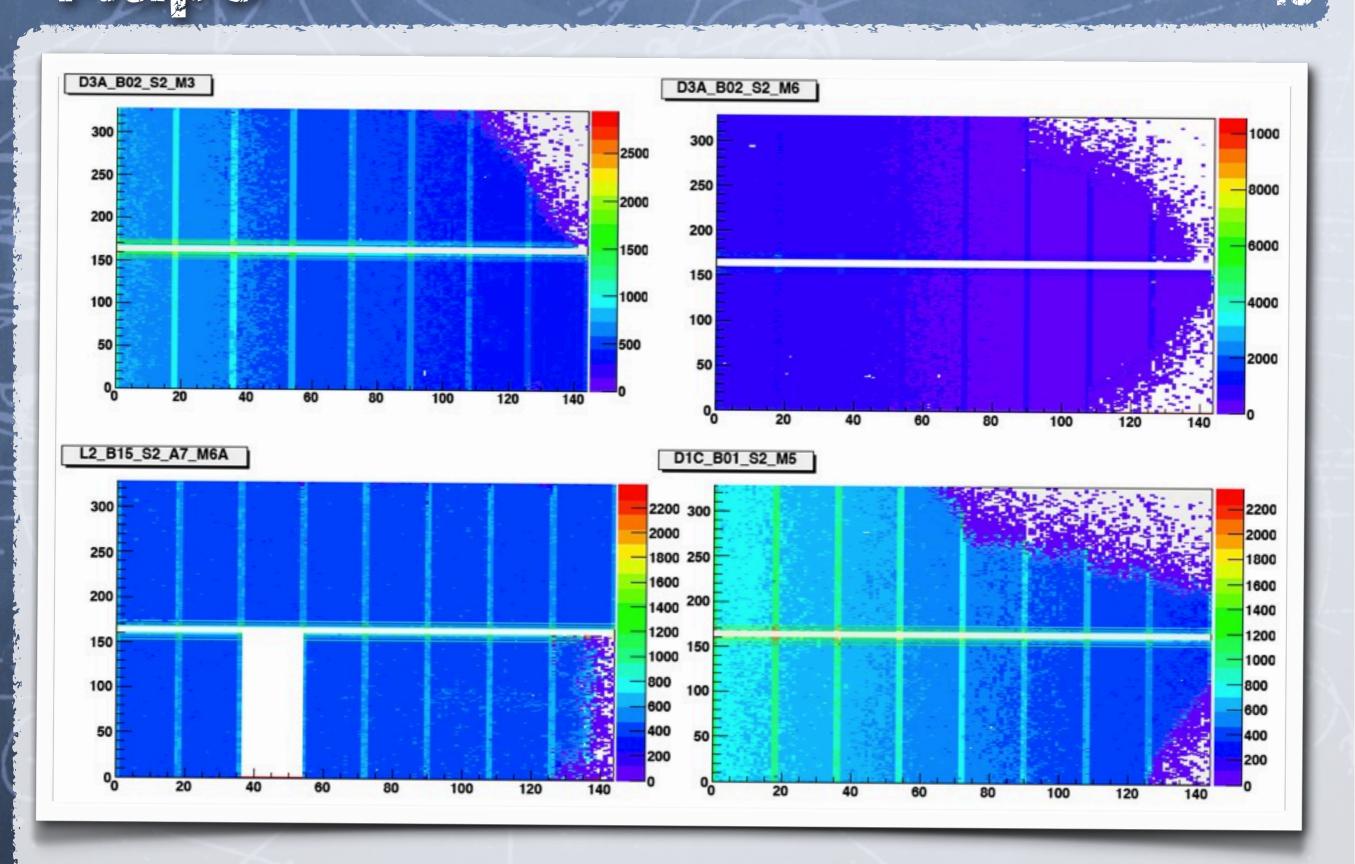

### IIISCOMMECTE MODULE PIXCIS WORST MODULE

PRODUCTION SOURCE SCAN

# DEFLINE ANALYSIS

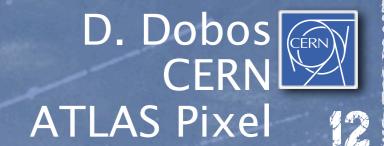

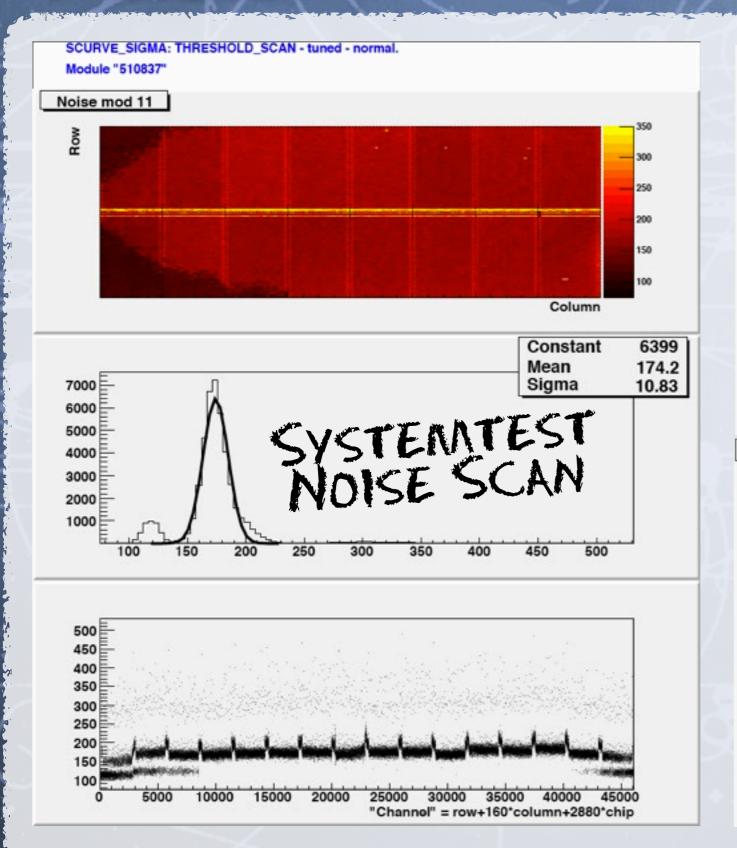

#### DISCOMBETE CROSSTALK SCAN SCAN

- Used crosstalk scan (4 ke<sup>-</sup> threshold 200 ke<sup>-</sup> injection)

- Sensor crosstalk 3.5%, low cross-talk in electronics (shielding)

- Analogue and threshold scan (noise: 160e -> 120e) verification

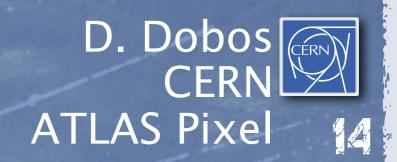

- 76980 disconnected pixels (0.1%) in 1697 modules

- 94.8% of total disconnected bumps are Indium type bumps

- Larger connected areas are from few badly damaged modules

#### DISCOMBETE CROSSTALK SCAN SCAN

### ODS EYWE OSOLDER EYCONEMOS BUNNES

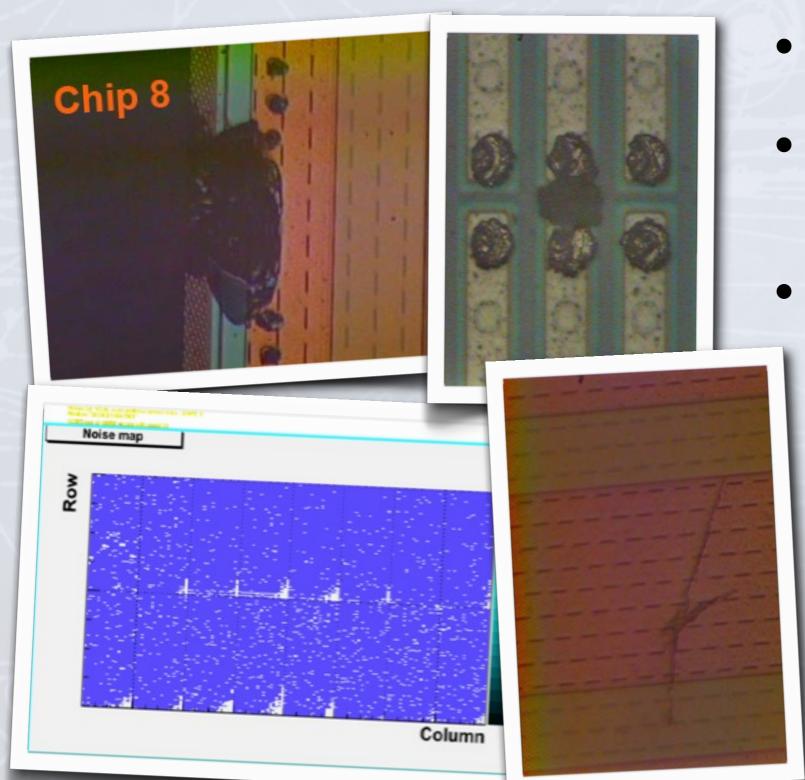

Contamination with particles (from dicing) shorts on chips and on sensor

#### FE:

- Gelpack remnants & difficult handling

- vacuum tweezer accident

- Over-thinning (only initially)

#### Sensor:

- Poor passivation openings

- Sensor Dicing problems

#### Observed after assembly:

- Low-ToT pixels: problem after UBM recycling

- Noise hot spots + high Ileak

### Observe Mount FroblemsumPs

- VDDA shorts, cleaning procedure

- Silicon fragments sandwiched between sensor and FE

- Care in cleanliness and handling, inspection

- Broken pickup tool: springs to distribute pressure along the FE

- Damage to the electronics, problem with the manipulation procedure

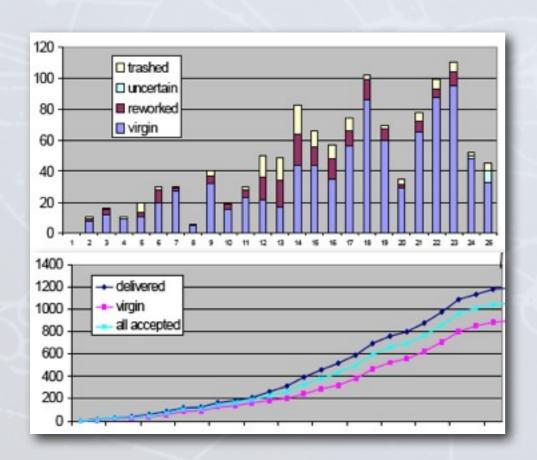

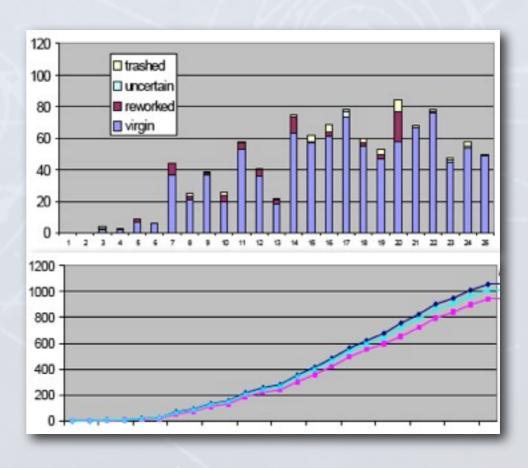

#### Production yield and timelines of 2576 modules:

#### Indium bumps:

• OK: 89%

• Virgin OK: 74%

• Reworked: 13%

• Failed: 11%

#### Solder bumps:

• OK: 97%

Virgin OK: 87%

Reworked: 7% + 3% internal

• Failed: 3%

#

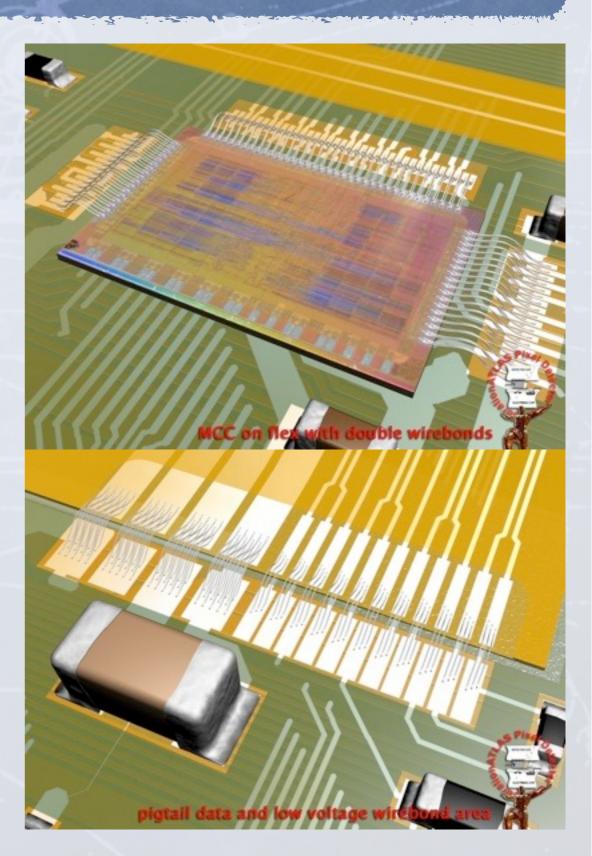

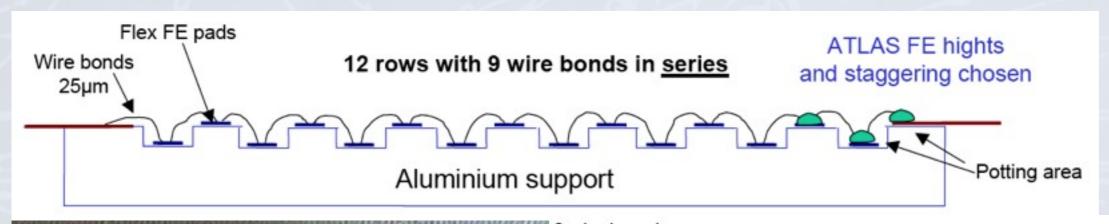

### WITCOCIOS 720 WIREBONDS ON 3 MODULE

### WIZEDOMO SPLITUP É POSITIONS STRATEGY

720 Wirebonds 25µm round Al:

- FE: I bond \* 30 \* 16 FEs = 480

- MCC: 2 bonds \* 71 = 142

- Power: I4 bonds \* 4 = 56

- Data: 3 bonds \* 11 = 33

- HV: 3 bonds \* 3 = 9

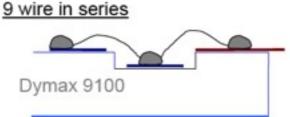

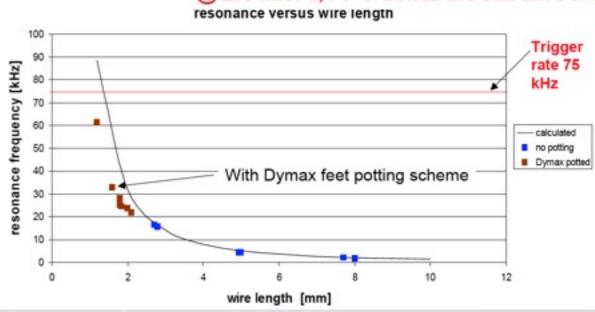

- three/two different lengths to avoid breaking by resonances, caused by Lorentz force in the solenoid field during power cycling or fixed frequency data

- FE wire bonds are potted at their bond feet

- MCC feet were potted at beginning of production

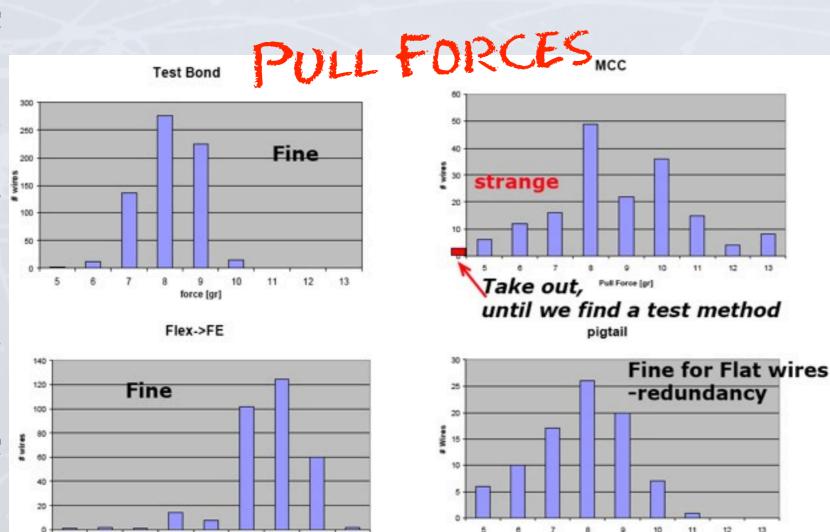

### WIYCOCHUPUL & POKE CUZITY ASSUYZMCC

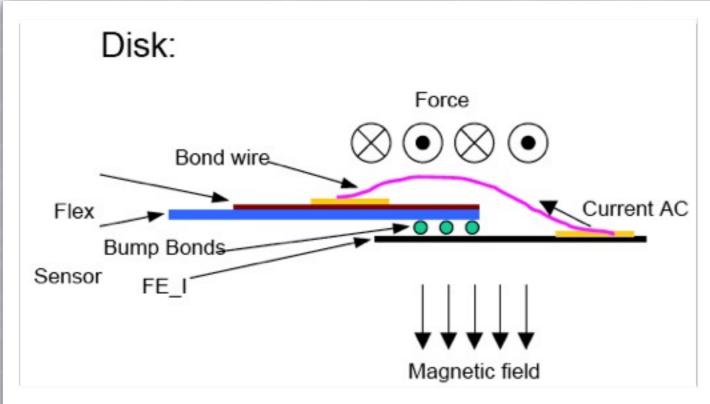

## WITCOCHOB-FIELD RESCHANCES

Barrel:

Force

Force

Current AC

Sensor Bump Bonds

FE\_I

Magnetic field

Atlas: worst case B = 2 Tesla  $\Delta$  Iddd = 38 mA  $\Delta$  Idda = 55 mA

#### Test setup:

B = 0.4 Tesla

=> chose I<sub>ac</sub>= 200 mA

# WIZEDOMOB-FIELD RESOMBIANCES

27 wire in series

20kHz - 35 kHz sweeps @ 200 mA:

After 80 sweep cycles

@ 200 mA / 0,4 T → bond <u>breaks</u>

20kHz - 100 kHz sweeps @ 200 mA:

After 15480 sweep cycles

@ 200 mA / 0,4 T → bonds are still alive !!!! resonance versus wire length

17,5 kHz

# Wirebond Condition

- For FE chips NECESSARY to avoid power bond failure due to mechanical resonance in B- field

- MCC bonds safe from this effect (much shorter and no AC currents), thought conservative to treat all bonds the same way

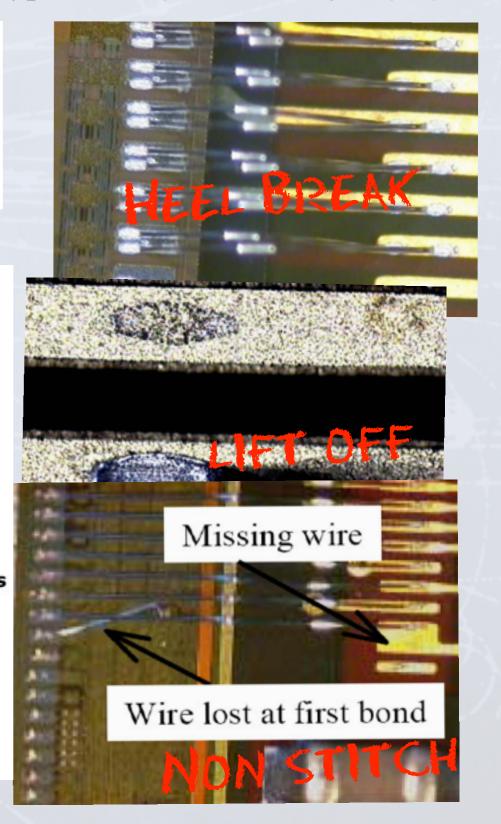

- Encapsulating detaches from the MCC surface expands and contracts 50µm with thermal cycling: CTE encapsulant = 100 x CTE silicon - sheers on the END bonds and can breaks them

- Removal of encapsulant and rebonding

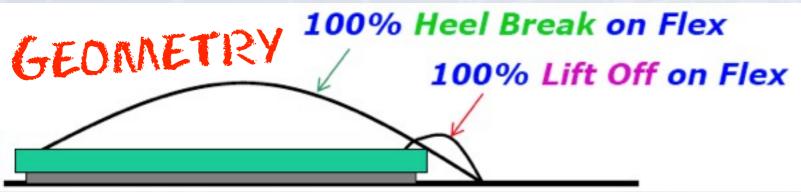

#### Influenced by:

- Geometry of bead

- MCC surface properties -SE4445 glue to attach the MCC to the flex - fine for Eccobond 45 glueing

Curing procedure. Hot UV lamp vs. cold UV lamp

### Summary & Conclusions

- 80.3M bumpbonds with 50 µm pitch

- Solder & Indium bumps different electrical resistance (noise)

- X-ray & electrical quality control

- Disconnected Bumps main reason (0.1%) for dead pixels

- Large disconnected areas grow with thermal cycling, especially for Indium bonds and FE edges

- Particle contamination (dicing) create shorts and hot-spots

- Many possibilities for mechanical stress on FEs and sensors

- Anyhow good yields, especially with rework possibility

- 1.3M wirebonds, 25 µm Al round wire

- Quality Assurance: Geometry, breaking mechanisms

- Redundancy with different wire bond lengths, feet potting

- Resonances in B-field studies show need for encapsulation

- Feet potting can cause wire bond breaking as well

###

### IZAN STEP!

To ensure good adhesion, at IZM, the wafers are sputter etched before sputtering of an adhesion layer (200 nm TiW) and the plating base (300 nm Cu) by electroplating. Photoresist is spin coated on the wafer and patterned by exposure to UV light through a high precision contact mask followed by an etching process. A wettable UBM (5  $\mu$ m Cu) is plated followed by an 100-200 nm gold oxidation protection layer.

### AMAS STEP !

At AMS photosensitive photoresist is spin coated on the wafers and patterned with the conventional photolithography process described above. A proprietary UBM is deposited.

### DECOSITIONS TEP 2

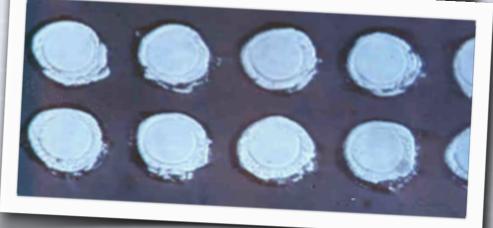

#### IZM STEP 2

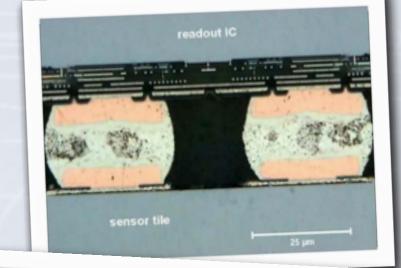

At IZM solder (37% Pb 63% Sn) is electroplated. It remains as 30 µm high cylindrical bumps after photoresist removal. The cylindrical bumps turn, caused by surface tension, into spherical bumps during a first reflow process.

#### AMS STEP 2

At AMS the UMB is cleaned with a plasma etching process immediately before the deposition of indium, obtained by electron beam evaporation of indium under vacuum ( $\sim 10^{-6}$  Torr). The photoresist is removed by a wet lift-off process and indium cylinders of about 20  $\mu$ m in diameter and  $\sim 8 \mu$ m in height remain.

# Trining and light of

### IZM & AMS STEP 3

Since many processing steps of the bump deposition are hard to carry out with thinned and fragile wafers, thinning takes place after bump deposition. The FE wafers are completely coated with a thick photoresist layer to protect the bumps. They are thinned to  $\sim$  180  $\mu$ m by backside mechanical grinding at GDSI (Grinding and Dicing Services Inc., Sunnyvale, CA, USA)

### IZM & AMS STEP 4

The fragile wafers are diced immediately after thinning to minimize the risk of braking by handling. To ensure that FE chips have not been damaged the diced and bumped single chips are held by custom carriers and tested with probe stations.

# FID CRIDOING OF FEP 5 CRIDS TO SCISOISTEP 5

#### IZM STEP 5

Photoresistive protection cover layers are removed by the described lift-off process. At IZM all 16 FEs are tacked together to the sensor UBM by solder flux using a precision pick and place bonder. The entire bare module is placed in a reflow oven. It undergoes a 4 minutes heating cycle with a maximum temperature of 240°C for a few seconds in an activated atmosphere. The bumps and the UBM are solder merged. Caused by surface tension of the bump balls the FEs align themselves.

#### AMS STEP 5

At AMS a single automated machine is used to precisely align, flip and bond the FEs one-by-one onto the sensor. The bonding process itself is a thermo compression at 90°C for a couple of minutes with an applied force of 25 N per FE. Since no self alignment happens for indium bumps, the alignment and planarity of the applied pressure have to be more accurate than for solder bumps.