UDINE

# Update from CERN and UniUD

Stefano Michelis, on behalf of the CERN power distribution team Stefano Saggini, University of Udine

07/02/2025

DRD 7.1.b meeting

#### Status of the funds

- CERN has the funds from EP RD 5.4 package, for the next 3 years. Equivalent is around 100KCHF/year + 2 Students

- UdiUD has been participating with internal funds in the framework of a collaboration in place for 15 years. UniUD is looking for funds from INFN for a PhD student.

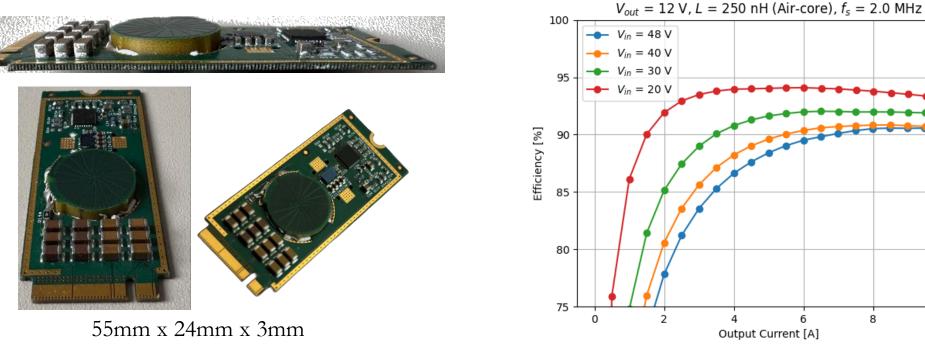

### bPOL48V: some improvements

CERN Rad-Hard Power Distribution

- Industrial testing is under development, tested chips will be available in Feb 2025

- EPC released the final version of the EPC2152, tested with TID up to 400Mrad w/o issues

- production ready modules have been presented at TWEPP, 300 modules are in production (with PCB inductor as well) 50 samples in travel to CERN this week

10

#### Double Buck Buck GaN based 48V DCDC 3-Level Buck 5-Level Buck TECHNOLOGY 🔨 TOPOLOGY - Currently using OnSemi I4T Several converter topology are - Investigation a new investigated for evaluating the best technology (BCD8s from ST) efficiency for high conversion ratio 48V Converters for radiation tolerance: 3 (48V -> 5V and 48V->0.9V) testchips submitted in Nov24 **TESTING DESIGN** - A new compact test board has been Currently on a new controller + developed to perform testing of power stage that can replace both DCDCs (functional + TID) - A more advanced board has been bPOL12V and bPOL48V

also developed for SEE testing

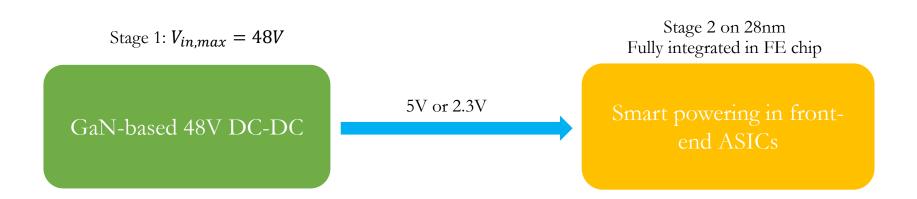

# Smart powering in 28nm front-end ASICs

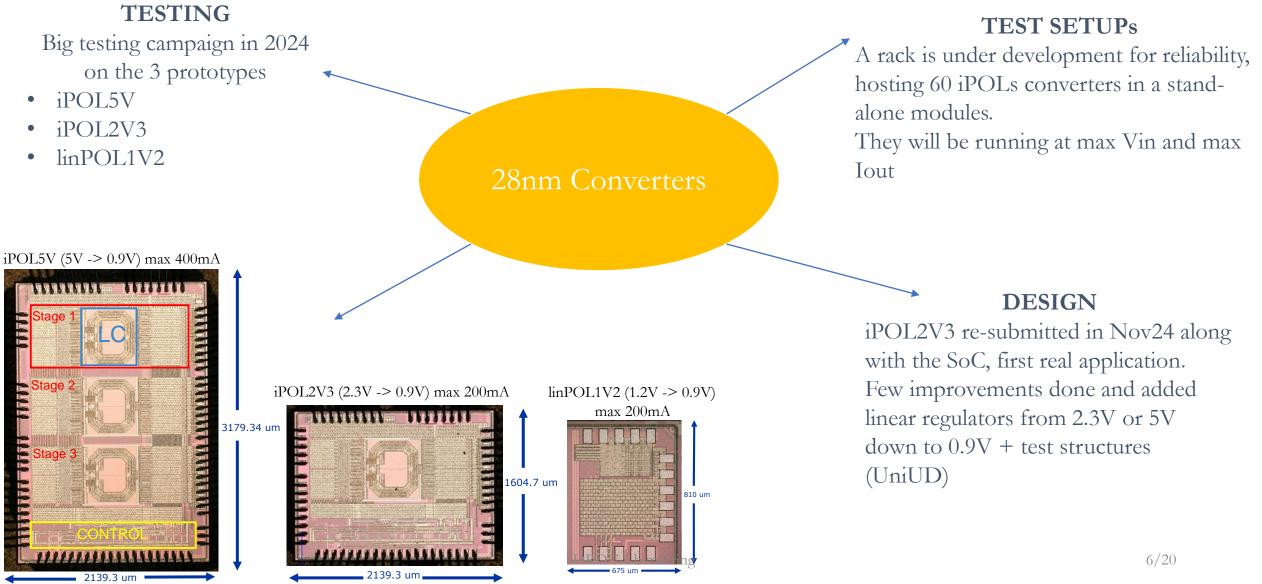

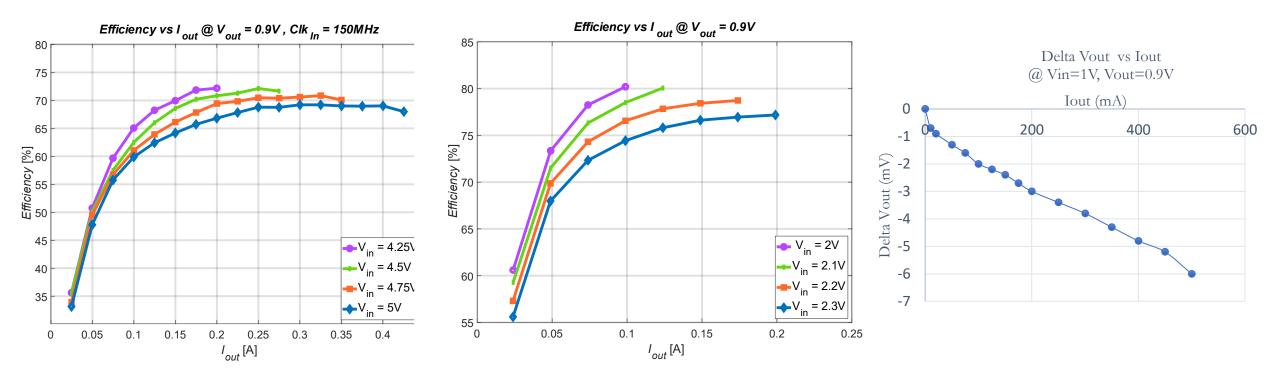

#### Electrical performance of 28nm ASICs

linPOL1V2

iPOL5V

iPOL2V3

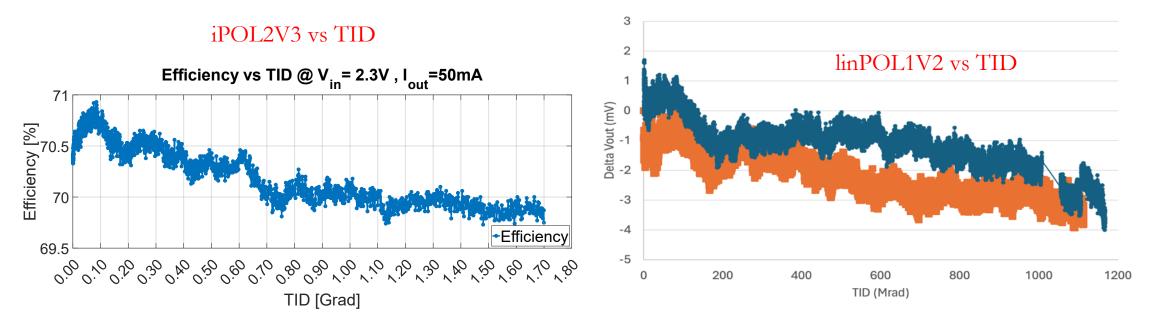

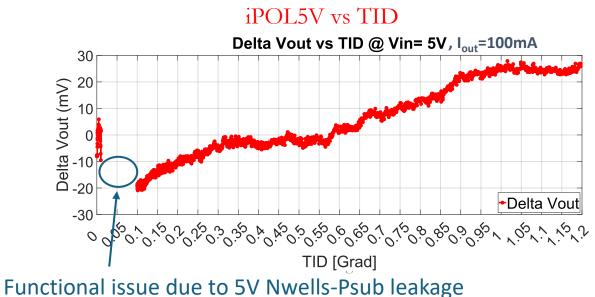

## TID testing of 28nm ASICs

## Contribution of UniUD

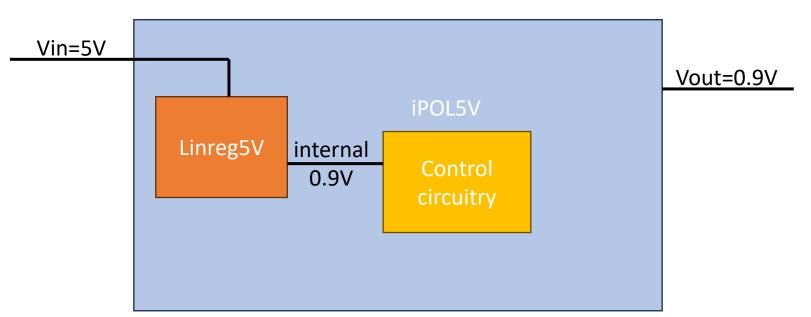

University of Udine (UniUD) contributed with the idea of the topology used for iPOL5V and iPOL2V3 and its improvement for HEP applications

In the first prototype iPOL5V and iPOL2V3 have the control circuitry supplied by an external 0.9V.

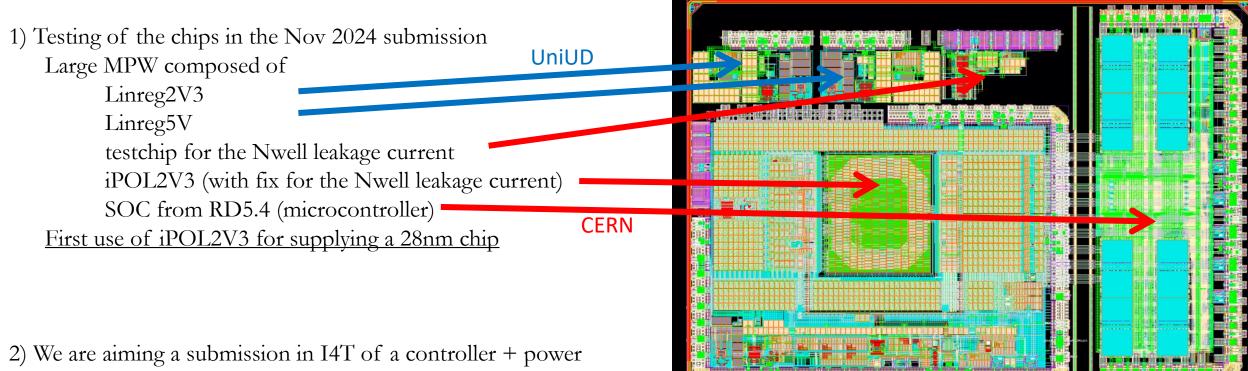

Stefano Saggini designed for this purpose two linear regulators to supply the 0.9V from the input line. from 5V to 0.9V (Linreg5V) for iPOL5V 2.3V to 0.9V (Linreg2V3) for iPOL2V3

The two designs have been integrated in the Nov 2024 submission

#### Plans for 2025

stage for replacing in long term bPOL12V and bPOL48V

# Conclusions

#### Legacy converters bPOLs:

- New modules of bPOL48V available

- Gan\_Controller for bPOL48V will be industrially tested, ASICs available on Feb 25

#### New RD on going

- 2 stage based

- 48 to 2.3V/5V under development in a new HV technology exploring new architecture as well

- 3 POL have been developed in 28nm technology: iPOL5V, iPOL2V3 and linPOL1V2. All three working fine, tested up to levels above 1Grad. We found a TID issue on iPOL5V, it has been corrected and re-submitted.

- Linear regulators for start-up have been developed and integrated in silicon, testing will happen in 2025