## **AIDA WP9**

Infrastructure for Gaseous tracking, Si-based vertex detector and tracker R&D, granular calorimetry

Marcel Vos (IFIC, U.Valencia/CSIC)

Vincent Boudry (LLR)

with help from

Klaus Desch, Hanno Perrey, Thomas Bergauer, Roman Poeschl

## WP 9.2: Advanced infrastructures for detector **R&D** Gaseous detector facilities

Subtask 9.2.1 (CEA, CERN, DESY, ULund):

Upgrade of the Large Prototype at DESY

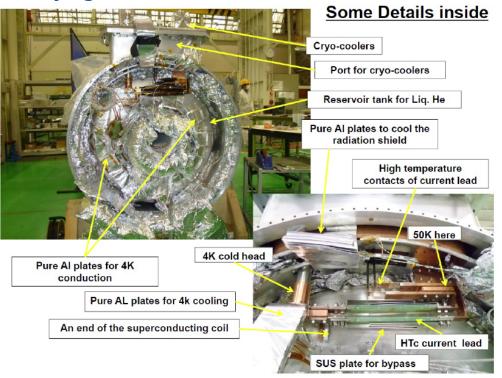

Superconducting solenoid

Endplate integration and Read-out system

**Subtask 9.2.2** (CERN):

Infrastructure for the production of large MPGDs

Subtask 9.2.3 (CEA, DESY, UBonn, NIKHEF)

Common readout systems for gaseous detectors (pixellated readout)

## Subtask 9.2.1 Large TPC prototpye upgrade at DESY

PCMAG 1T Solenoid upgrade done in Japan (waiting for re-installation at DESY)

- selfcontained cryogenics

Ralf Diener, DESY

PCMAG will be available again this summer for tests

AIDA is co-funded by the European Commission within the Framework Programme 7 Capacities Specific Programme, Grant Agreement 262025

Subtask 9.2.2 CERN MPGD workshop upgrade 9 new machines, delivery almost complete (785 kCHF payed by CERN), commissioning in progress. 2x1m<sup>2</sup> Micromegas, 2x0.5 m<sup>2</sup> GEMs.

2 years of fellow on AIDA funds (240 kCHF) for commissioning of the new equipment and redefinition of the production parameters

Lots of 'clients' for prototyping (MM Muon chambers for ATLAS upgrade and for muon tomography, GEM Muon chambers for CMS upgrade, GEMs for GSI, plus tens of smaller projects, and more to come...

Rui de Oliveira, CERN

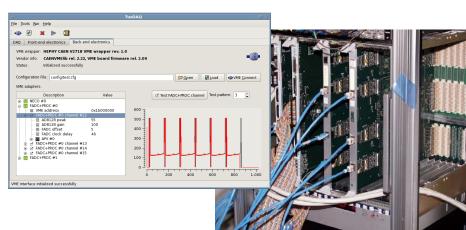

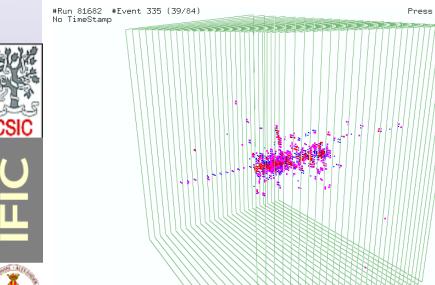

## Subtask 9.2.3 Readout pixel-gas detectors

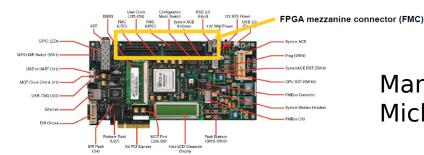

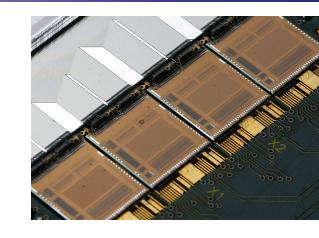

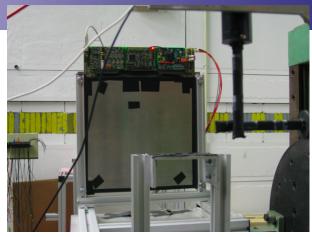

Goals: - "Large Area" module ( $\sim$ 100 chips) with InGrid-Detector for LP TPC with Timepix1- initial readout system for Timepix3 (longer time scale)

V6 board functional, firmware on SRS

Until now: VHDCI 68 pin cable (same as for MUROS), will be HDMI soon

Passive A-Type card, rooting signals

SRS FEC with Virtex 5

FPGA

Ethernet to SRU / PC

SRS-based readout system

The goal" SPiDR systen

RELAXD readout system

SPiDR system peedy Pixel Detector Readout

- Readout for Medipix3 and (later) Timepix3

- Initially 1 Gbit/s Ethernet, then migrate to 10 GBE

- Develop firmware on FPGA development boards

- At a later stage design a compact readout module like Relaxd

Martin van Beuzekom, NIKHEF Michael Lupberger, Bonn

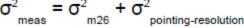

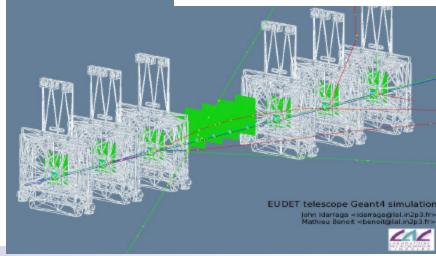

WP9.3: go to a test beam by plane and plug your prototype into a full-fledged infrastructure.

Users don't need to develop/buy and commission scintillators & trigger logic, remote-controlled mechanical support, DAQ, cooling, analysis chain. Support is crucial

Task leader: I. Gregor (also DESY contact)

No meeting this week due to clash with ATLAS upgrade meeting, but a nice overview talk by Hanno Perrey in the plenary on Wednesday Milestones in M13: design & specification of telescope & thermo-mechanical infrastructure

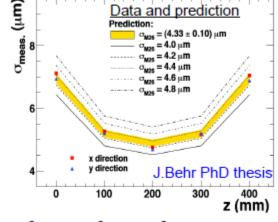

Pointing resolution in between the planes

A very complete infrastructure was developed in EUDET See: Igor Rubinsky (DESY), TIPP2011

## Beam telescope demonstrators:

MIMOSA–28 (next generation)

ATLAS FE-I4 (integrated in EUDET telescope)

TimePix (standalone)

#### Interfaces & auxiliary infrastructure:

Design and produce a mini-TLU with high speed capabilities (ongoing, see also common DAQ session in WP8) Implement FE–I4 in trigger mode (tested and found to work)

Design cooling plant

(~ existing design)

Providing Timepix infrastructure under the umbrella of AIDA (plug-compatible with MIMOSA/ATLAS arms?)

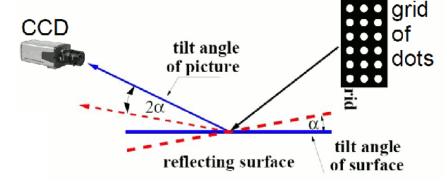

### Off-beam infrastructure

Thermal performance measurements & mechanical characterization

"monitoring minute deformations [...] in an environment that closely mimics that of the experiment.

Allow users to look at their ultra-thin ladders at a different wave-length

Monitor vibrations and deformations using Bragg fibers or

[Participating insitutes] agreed on a list of material required for the optimal design of the system [...] measurements using this infrastructure are planned for 2012" Merge elements from existing "private" infrastructure in Spain and DESY. Similar plans exist elsewhere (at CERN).

## **WP9.4 Silicon Tracking**

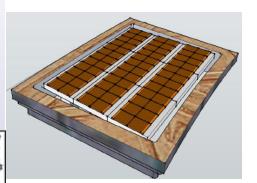

Task leader: Thomas Bergauer (HEPHY Vienna) Providing multi-layer Si  $\mu$ -strip coverage for the calorimeter stack of WP9.5

#### provide a reference for calorimeters of WP9.5

- → use TB data to understand two-particle resolution re-launching the SiLC collaboration for u-strip R&D

- → to go well beyond for AIDA deliverables

DAQ → APVDAQ (for APV25 chip used in CMS/Belle-II).... Done!!

### **Baseline sensors**

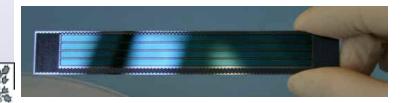

- •Large area sensor: 95 x 95 mm<sup>2</sup>

- •Very fine pitch: 50 μm

#### **Recovered SILC modules:**

careful evaluation of sensor quality needed

# New sensor design (for submission to ON u-electronics)

Large main sensor 10 x 10 cm<sup>2</sup> Small test sensors with design variations Test structures

Wafer layout made by HEPHY

Marko Dragicevic (HEPHY Vienna)

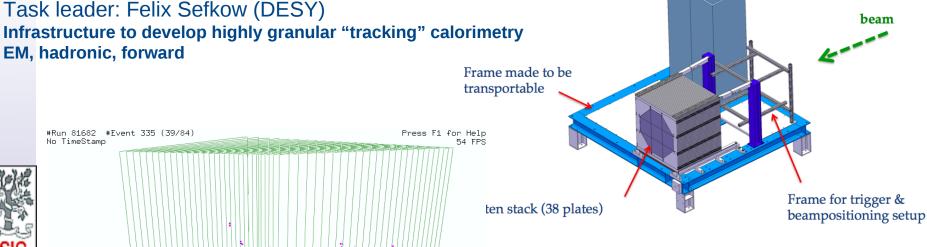

## **WP9.5** Granular calorimetry

Task leader: Felix Sefkow (DESY)

EM, hadronic, forward

For backgrounds: CALICE reports to the DESY PRC:

March 2010, http://arxiv.org/pdf/1003.1394

http://arxiv.org/pdf/1105.0511

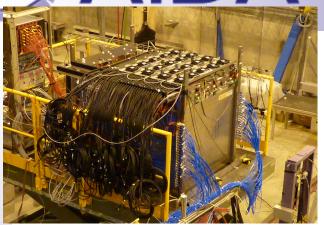

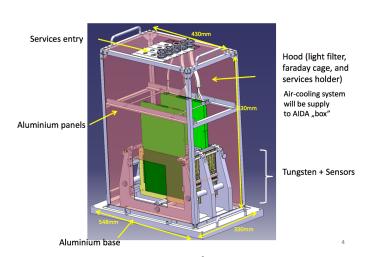

Electronics rack

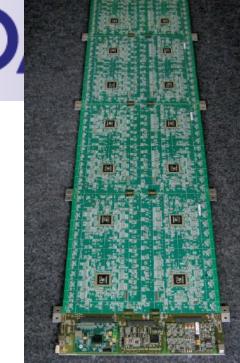

First layers of technological prototype of analoque Hcal

1m3 technological prototype of SDHCAL (commissioned in 2011, now going for beam)

First layers of technological Prototype of SiW Ecal

Towards AIDA FCAL

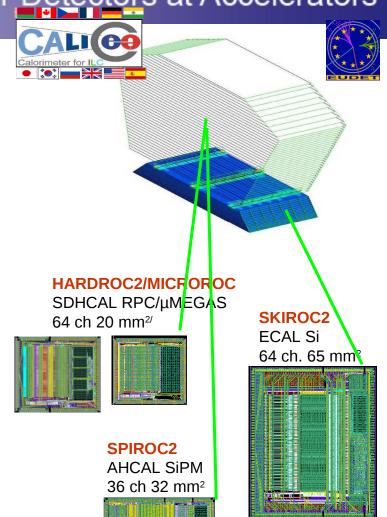

ASIC development & large-scale readout boards

**SPIROC**

# nced European Infrastructures for Detectors at Accelerators

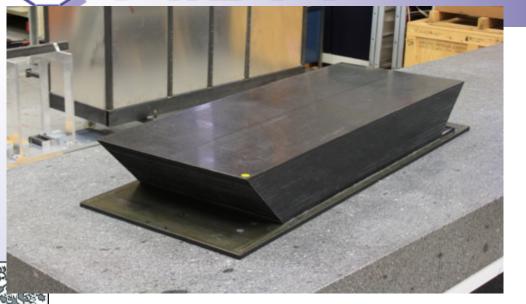

Completed alveolar structure

- Tungsten layers embedded in carbon fibre composite

- Cured in oven to form structure

Similar size as LC detector module

(Infrastructure) which can house other sensitive components (e.g. scintillator layers)

- Beam test with layer in T24 at DESY ongoing

- Large scale beam test (~ 10 layers) envisaged for July 2012

Advanced European Infrastructures

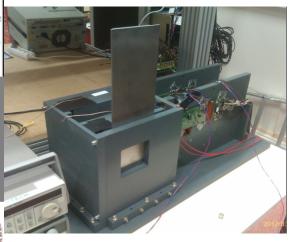

ccelerators

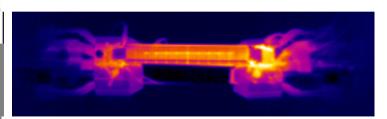

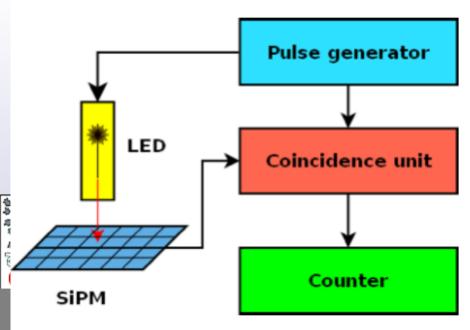

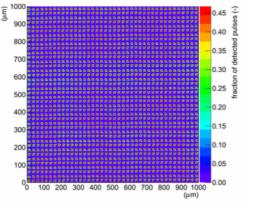

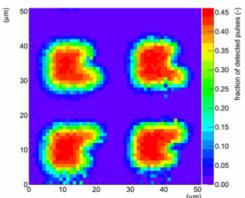

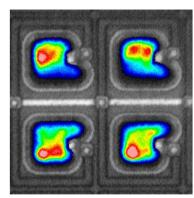

Focusing LED light to a small point Of SiPM (Diameter ~1.5mum)

- Scan with 1mum step size

Getting the details of SiPM response

Sensitive area reduced

By quenching resistor

Photo + photoemission image

Transnational access at DESY and CERN: See presentations by Ties Behnke and Horst Breuker in WP5,6,7 session on Thursday morning

CERN: 512 person days accepted by selection panel for Testbeams (600 foreseen); 200 in Irradiation facilities. The total budget is 197900 CHF.

Users include the whole spectrum: ATLAS (5x), CALICE (2x), LHC-b, TimePix, CMS, Belle-II, NA63, SPEC, fastRPC

## Special action items for M13 milestones:

#### **Common DAQ & WP9 (organized by David Cussans)**

write up a complete "specs" document for the TLU in the next two months, that's agreed upon by TimePix, CALICE, LCTPC, evaluating also a high-rate proposal

$\mu$ -strip package assumes minimal DAQ interface is sufficient to run combined tests with CALO-infrastructure

#### Silicon-CALO interface (organized by WP9.4 and WP9.5)

Specify in detail what is to be measured, how, when and where:

**ECAL/HCAL**

**CERN SPS availability**

Overlay/data-only

Solid activity throughout WP9. Very fruitful task meetings.

Annual report delivered. M13 milestones in preparation.

AIDA continues to provide infrastructure developed under EUDET and is already extending it.