Orsay Micro Electronics Group Associated

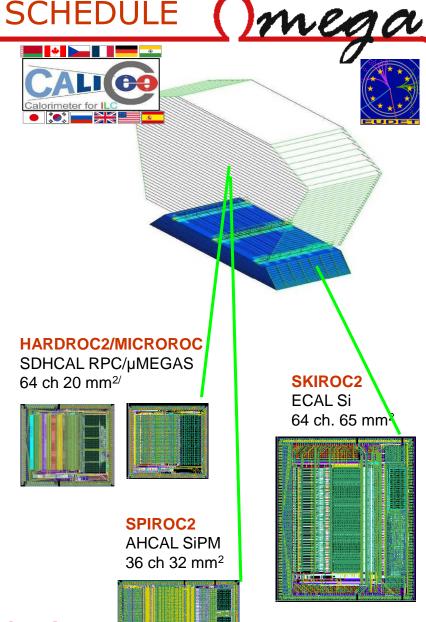

# AIDA WP9.5: MILESTONES and SCHEDULE

- Schedule presented at the AIDA Kick Off meeting

- 2011: Characterization of the 2<sup>nd</sup> generation ROC Chips

- Dedicated run produced in March 2010

- 25 wafers received in June

- 20 000 chips packaged in the US

- 2012: Submission and test of one of the 3<sup>rd</sup> generation chips

- 2013: Submission of a second 3<sup>rd</sup> generation chip

- August 2013: Report

- Budget for 3rd generation of electronics:

- 31k€ (ECAL) + 50 k€ (Hadronic Calorimeter) => 2 chip submissions

- 30 ppm

- Cost:

- Multi Project runs (MPW): 1k€/mm2

- Packaging: \$3500

- Testboard: 1500 €

0.35µm SiGe AMS technology

#### **HARDROC2** Characterisation

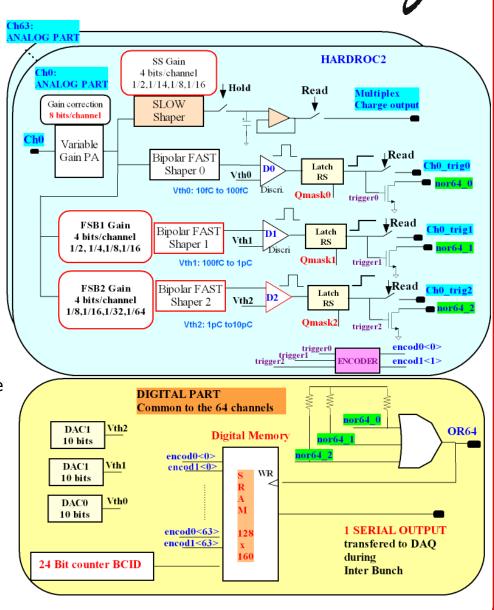

### HARDROC2: 64 channels (RPC DHCAL)

- preamp + shaper+ 3 discris (semi digital readout)

- Auto trigger on 10fC up to 20 pC

- 5 0.5 Kbytes memories to store 127 events

- Full power pulsing  $=> 7.5 \mu W/ch$

- 2010 TB: 1 m2 (144 HR2b)

- power pulsing in magnetic field successfully tested

- SDHCAL technological proto with 40 layers (5760 HR2 chips) built in 2010-2011.

- Testbeam summer 2011: pb with the DAQ2 (HDMI) + pb of cooling

- TB November 2011: 6 detectors and USB DAQ: good performance of the electronics and detector

- Next TB (April 2012) with 40 detectors and intermediate DAQ (HDMI & DCC cards for synchronization and USB for config & readout)

- HARDROC3 FE: No major modifications needed

Cosmic hadronic shower

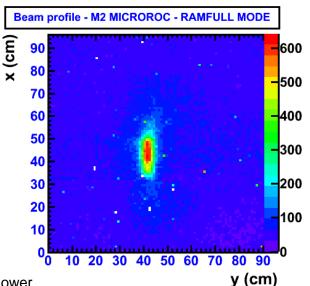

#### MICROROC Characterisation

### MICROROC: 64 channels µMegas DHCAL

- ☐ Very similar to HARDROC except for the input preamp and shapers (100-150 ns)

- Noise: 0.2fC (Cd=80 pF). Auto trigger on 1fC up to 500fC

- $\square$  Pulsed power: **10**  $\mu$ **W/ch** (0.5 % duty cycle)

- 1 m2 in TB in August and October 2011. Very good performance of the electronics and detector (Threshold set to 1fC).

- □ 2012: 4 m2 in TB

Cosmic hadronic shower

#### SPIROC2 Characterisation

mega

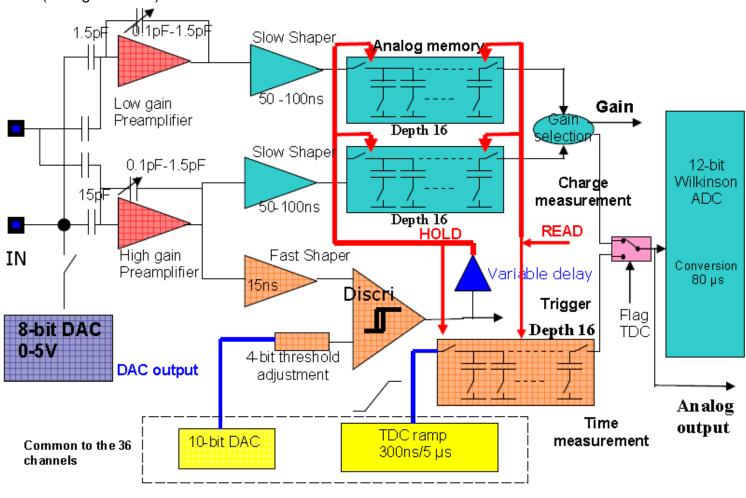

- SPIROC2: 36 channels for AHCAL (SiPM)

- □ Autotrigger on 1 spe (150 fC), 16 depth SCA for Charge measurement (up to 300 pC) and Time measurement (< 1 ns)

- □ 2 memories of 2K bytes to store Charge and Time measurements from the internal 12 bits ADC

- $\square$  Pulsed power: **25**  $\mu$ **W/ch** (1 % duty cycle)

- ☐ Testbench measurements at ORSAY and at system level at DESY show some defects

- ✓ Design of a new input preamp to solve rate dependency pb + coherent noise + Crosstalk (HG/LG)

- ✓ Building block with this new FE tested in December 2011: Very good performance

- » HG Preamplifier + Slow shaper: Vmax= 46 mV/pe, Noise RMS = 2,3mV =>SNR ~ 20

- ⇒ Submission of SPIROC2C (Feb 2012) with this new FE

- ✓ Klaus2 chip (Heidelberg University): also a good candidate for the FE of Spiroc => "KlausROC"

- □ TDC: First tests of TDC ramps in SPIROC2b show promising results. Resolution <1ns (dominated by linearity) => New tdc in SPIROC2c to minimize dead time

- ☐ HBU2 tested successfully in DESY test beam (March 2012)

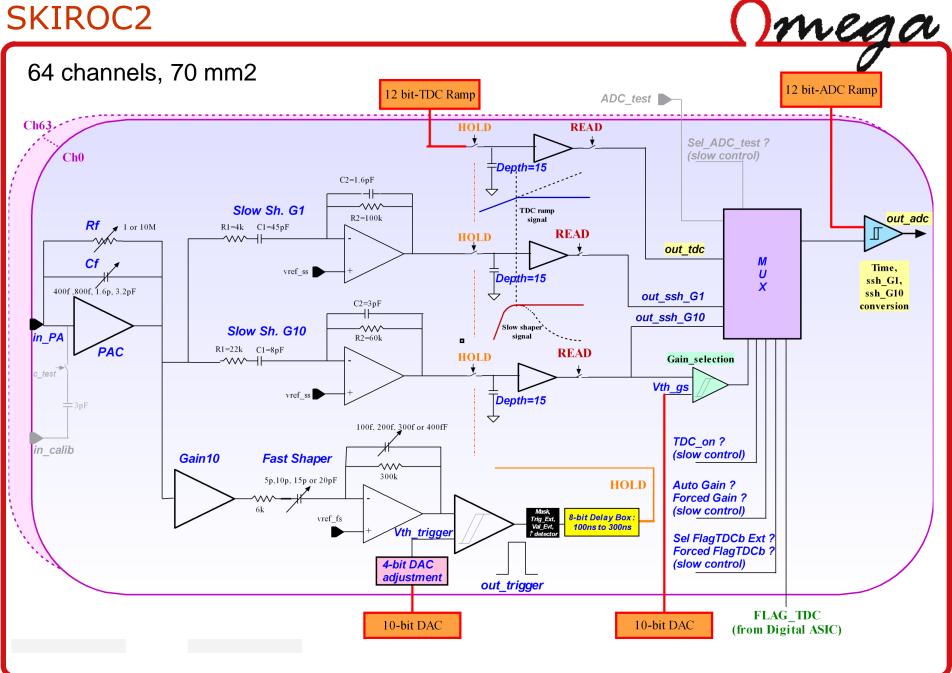

#### SKIROC2 Characterisation

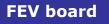

- **SKIROC2**: 64 channels for ECAL (Si pin diodes)

- □ Autotrigger on 0.5 MIP (2 fC), 15 depth SCA for Charge measurement (0-2500 MIPs) and Time measurement (< 1 ns)

- ☐ 1 memory of 4K bytes to store the digitized measurements of Charge and Time by the internal 12 bits ADC

- □ Pulsed power: **25 µW/ch** (1 % duty cycle)

- □ Similar to SPIROC2 except for the input PA => SKIROC2 benefits from SPIROC measurements

- ☐ Testbench measurements: very good performance

☐ Test beam @ DESY starting 26th March (FEV boards with sensor and 4

packaged SKIROC2)

- 2<sup>nd</sup> generation ROC chip

- Auto-trigger, analog storage, digitization and token-ring readout, common DAQ

- Power pulsing : <1 % duty cycle

- 3<sup>rd</sup> generation ROC chip

- **Independent channels (= Zero suppress)**

- 64/36 address pointers

- ReadOut, BCID, SCA (Spiroc and Skiroc) management

#### => Digital part much more complicated

- SCA depth: 8 instead of 16

- Possibility to use "Roll mode" by Slow Control: circular memory very useful for Testbeam

- New TDC with no dead time

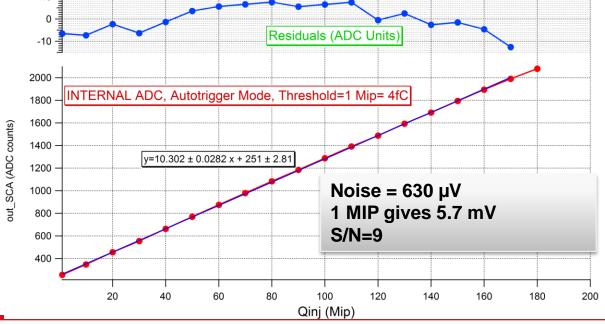

- New Slow Control (Triple voting) using I2C link (while keeping the « old SC » system)

# SUBMISSIONS SCHEDULE

- 1st submission (Feb 2012): SPIROC2C (2<sup>nd</sup> generation chip)

- new input preamp: less sensitive to coherent noise, better Signal-to-Noise ratio, no pedestal shift and no rate dependency

- SC: old one (No I2C)

- Input 8-bit DAC slope uniformity improved

- TDC : dead time decreased

- Pin to pin compatible with spiroc2b so noise measurements can be performed at the system level using the existing HBUs

- Die size: 32 mm2 => MPW run 32 k€ (CALICE/EUDET funding), 27<sup>th</sup> Feb 2012

- 2<sup>nd</sup> submission (June 2012 or September 2012): HARDROC3

- « Simple » chip compared to Spiroc3: I2C, independent channels, circular memory, one register/channel, temperature sensor

- No major modifications in the analog part

- HR3 won't be pin to pin compatible with HR2 and probably in a different package: TQFP208 instead of TQFP 160 (same size and thickness)

- ⇒ New 1 m2 RPC chamber to be built to test HR3 at the system level

- Die size should be ~30 mm2 => 30 k€ + 5K test setup (AIDA funding)

- 3<sup>rd</sup> submission (March 2013) SPIROC3: Complex chip, many parts still to be tested on test bench and at the system level

- I2C, independent channels but also new PA, TDC, SCA

- Hardroc3 and Spiroc2c test feedback necessary before submitting Spiroc3

- Size should be ~40 mm2 => 40 k€ + 5 K test setup (AIDA funding)

# Conclusion

#### 2011:

- 2<sup>nd</sup> generation ROC chip characterisation

- no money spent, 4 ppm (0.3 FTE) for the design of the digital part of the 3<sup>rd</sup> generation of ROC chip

#### • 2012:

- HR3 design and submission (June or September)

- Test of HR3 and SPIROC2C before submitting SPIROC3

- 35k€ for HR3, 16 ppm (1.3 FTE)

# **BACK UP Slides**

# 3Gen ROC chips: common features

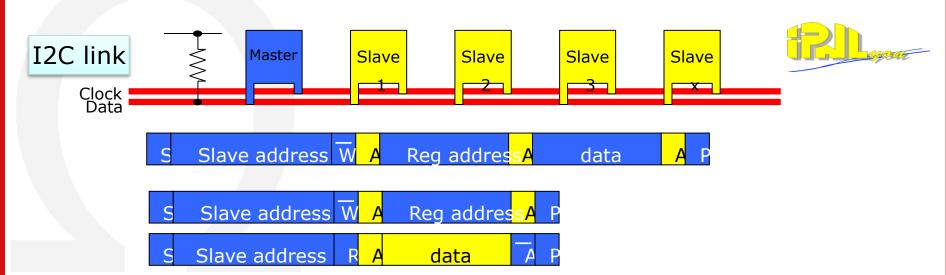

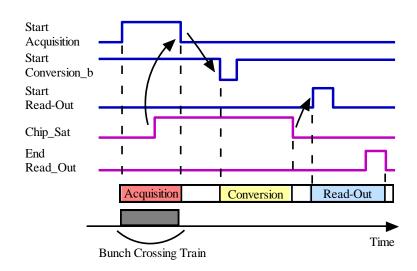

- DIF sequencing (Acq, Conv and Readout):

- Backward compatibility with 2Gen ROC chips sequencing

- Use of ChipSat signal

- Daisy chained chips for readout

- Possibility to use Roll mode by Slow Control:

- If RollMode = "0" → Backward compatibility with 2Gen ROC chips behavior

- Only the N first events are stored

- If RollMode = "1" → 3Gen ROC chips behaviour

- Use the circular memory mode

- Only the N last events are stored

# 3Gen ROC chips: common features

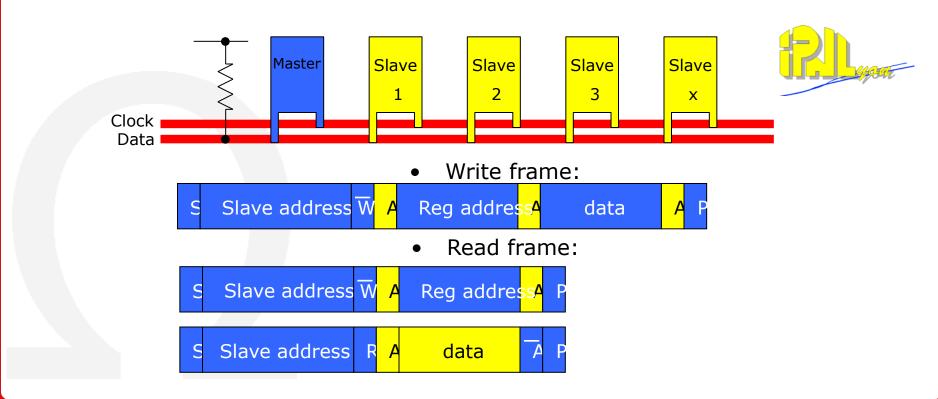

- Slow control parameters:

- Backward compatibility with 2Gen ROC chips slow control

- Use of classical shift register slow control

- Embedded I2C

- 7-bit address + 1 general call address (127 chips can be addressed)

- · Access port doubled

- Bidirectional data line with open collector (Driver will be the same as Dout)

- Read back capability of SC bits (non destructive)

# 3Gen ROC chips: common features

• Extra pin needed for I2C / SC:

| HARDROC 2    |   | HARDROC 3           |      |

|--------------|---|---------------------|------|

| ShiftReg_In  | 1 | ShiftReg_In         | 1    |

| ShiftReg_Out | 1 | ShiftReg_Out        | 1    |

| ShiftReg_Clk | 1 | ShiftReg_Clk        | 1    |

| ShiftReg_Rst | 1 | ShiftReg_Rst        | 1    |

|              |   | ShiftReg_Loadb      | 1    |

|              |   | ShiftReg_ReadBack   | 1    |

|              |   | Error_Triple_Voting | 1    |

|              |   |                     |      |

|              |   | 7-bit I2C @         | 7    |

|              |   | 2 x (SCL / SDA)     | 4    |

|              |   | Select_I2C_Port     | 1    |

|              |   | Clk_I2C_SR          | 1    |

|              |   | Rstb_I2C            | 1    |

|              |   |                     |      |

|              |   | Select_I2C_SR       | 1    |

|              |   |                     |      |

|              |   |                     |      |

| Total        | 4 | Total               | 4+18 |

Standard SC

SC with triple voting

I2C

Selection I2C or std SC

# HARDROC2b

Omega

- □ 64 channels, 20 mm2

- □ Variable gain (8bits) current preamps (50 ohm input)

- ☐ One multiplexed analog output (12bit)

- □ 3 shapers, variable Rf,Cf and gains

- □ 3 thresholds (=> 3 DACs):

- □ 10 fC, 100fC, 1pC (megas)

- □ 100fC, 1pC, 10pC (GRPC)

- □ Auto-trigger on 10fC

- □ Store all channels and BCID for every hit. Depth = 128 bits

- Data format :

128(depth)\*[2bit\*64ch+24bit(BCID)+8bit(Heade

r)] = 20kbits

- 872 SC registers, default config

- Power pulsing

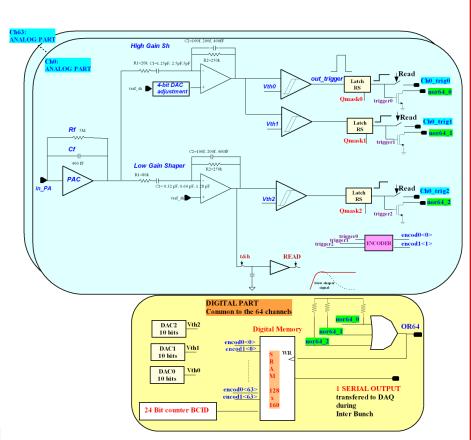

# MICROROC ~ HR2B

Omega

- Collaboration with LAPP Annecy

- ☐ 64 channels, 20 mm2

- □ Same as HARDROC but with charge preamp input stage + HV protection and slower shaping + 4bit DAC/channel

- □ Preamp optimized for Cd=80 pF, noise = 0.2 fC. Cf=0.4pF Rf=5M

- Maximum input charge : 500 fC

- ☐ Bi-gain shaper (G1-G4), peaking tunable 50-200 ns (2 bits)

- □ 3 thresholds: Lowest threshold ~2 fC

- ☐ Pin to pin compatible with HR2

- Store all channels and BCID for every hit. Depth = 128 bits

- Data format :

128(depth)\*[2bit\*64ch+24bit(BCID)+8bit(Header)]

= 20kbits

- □ 872 SC registers, default config

- Power pulsing

# SPIROC2b

Omega

- •36 channels, 32 mm2

- Bi-gain (autogain)

- Analogue Memory depth: up to 16 events can be stored (columns)

- 2 × 36 channels (Charges/Times)

# SKIROC2