# Bonn / CPPM plans for 3D integration

M. Barbero, L. Gonella, F. Hügging, H. Krüger, N. Wermes (Bonn University)

J.-C. Clemens, S. Rozanov (CPPM)

March 28<sup>th</sup> 2012

Aida 1st Annual Meeting, DESY, March 27th -30th 2012

# Bonn / CPPM project

- <u>Goal</u>: Interconnection of the ATLAS FE-I4 chip to sensors using bump bonding and post-processing TSVs from IZM.

- <u>Context</u>: Material reduction, new module concepts, new technologies for High Luminosity LHC upgrade.

- <u>1<sup>st</sup> goal at short time-scale</u>: Demonstrate two-side access (front and back) to a <u>bump-bonded sensor/FE stack</u>, using the FE-I<sub>4</sub>B.

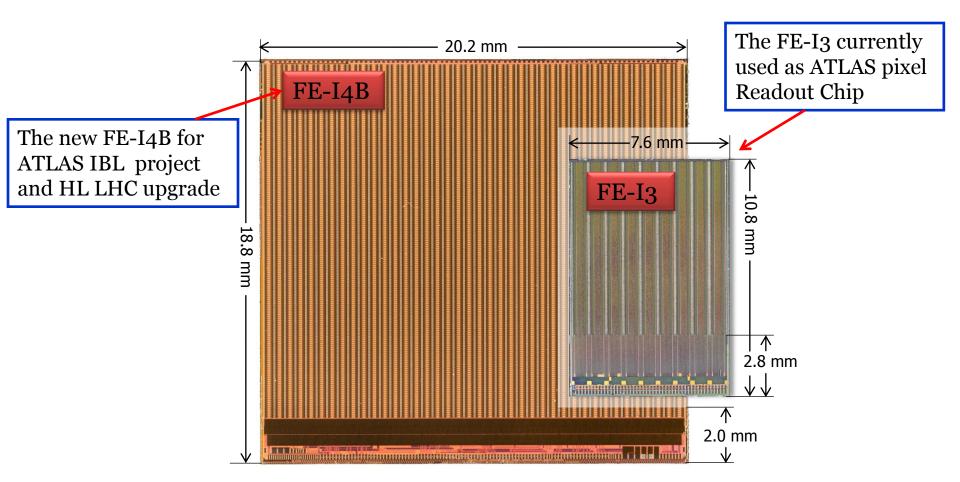

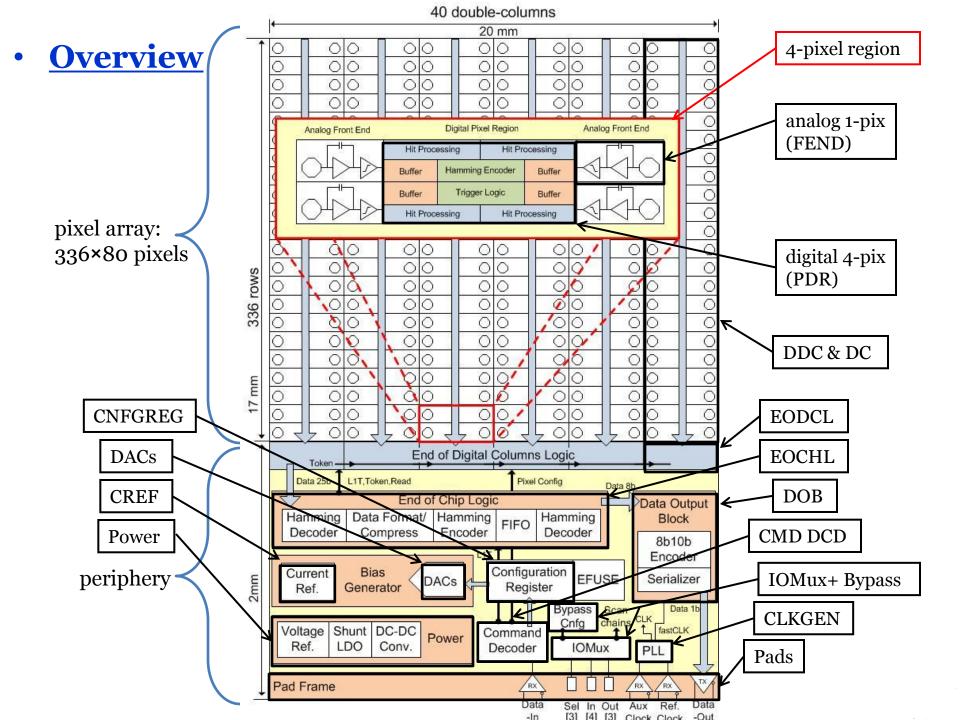

## FE-I4B

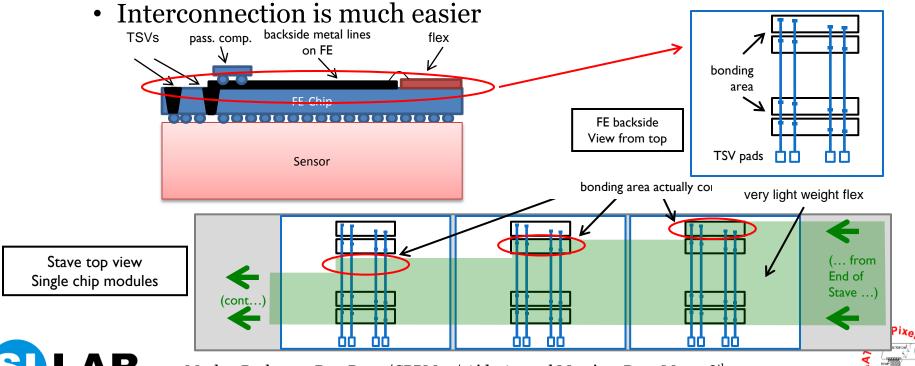

# Module concept with TSV: Sketch

- TSVs + backside metallization → Will allow the use of FE's backside for routing

- Direct connection of service lines or flex on FE backside

- Less material: no need for wings, module flex, connectors (IBL as an example: gain ~0.13%X0)

# Current project with TSV

- Long term relationship between Ubonn and IZM Berlin.

- IZM main bump bonding ATLAS pixel partner.

- Many developments for future module addressed with IZM:

Usage of different sensors, thin IC modules, low cost program...

- Started a via-last TSV development with IZM 3 years ago.

- FE-I2/I3 readout electronics.

- Tapered side wall / Straight side wall TSVs.

(both used successfully, tapered side wall TSVs a faster process, better suited to our needs)

- "Integrated" TSV / Bump Bonding process in-house at IZM.

- Profits from ultra thin flip chipping R&D (developed for FE-I4 in ATLAS IBL project).

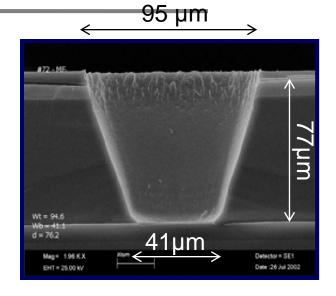

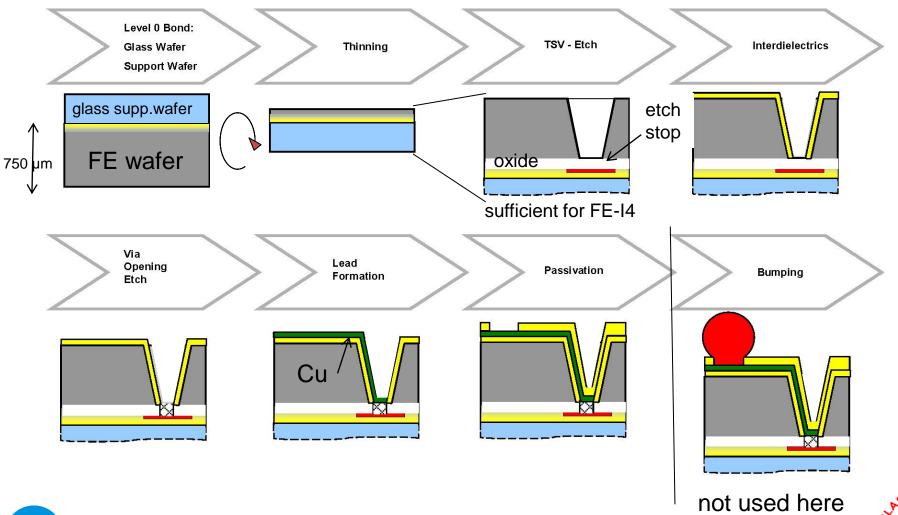

# Tapered Side Walls TSV Etching

- Tapered Side Wall TSV is a fast process

- Vias are etched in one step and oxide is deposited afterwards.

- Tapered walls

- Side wall angle 72°

- Via diameter on the bottom is 41μm

- Via diameter on the top is 95μm

- Si thickness 77μm (in this example)

- with pad pitch of 150 μm (FE-I2) →

maximum die thickness is 100μm

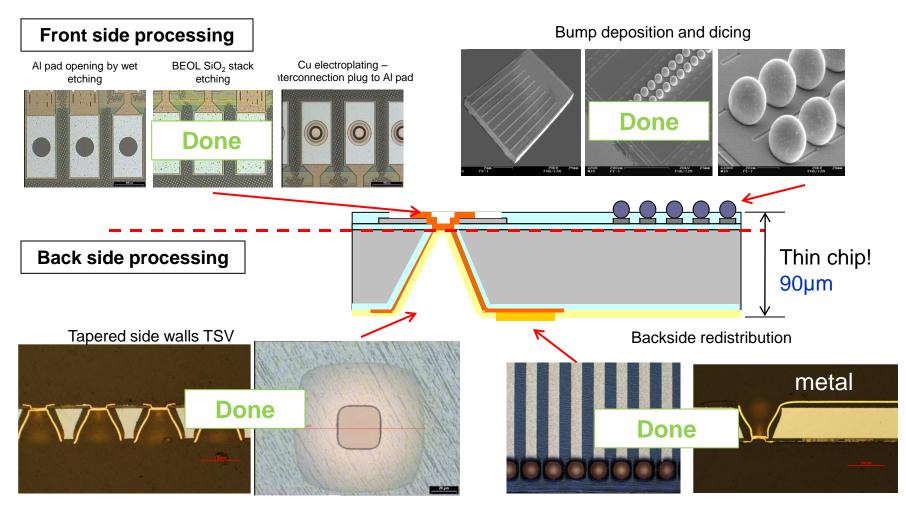

# TSV: Main process flow

# TSV prototypes with FE-I2/3

#### Frontside processing

- Cu pad to bond pad interconnect (plug)

- Bump deposition

- Dicing

#### Backside processing

- Thinning to 90μm

- Silicon Via etching

- Passivation

- Re-Distribution Layer (RDL)

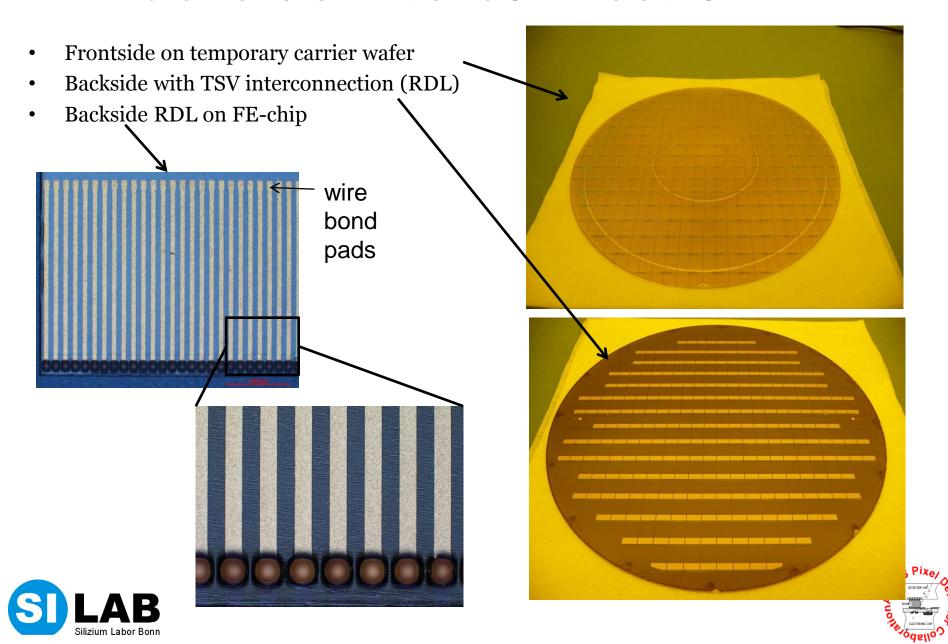

## Backside interconnection

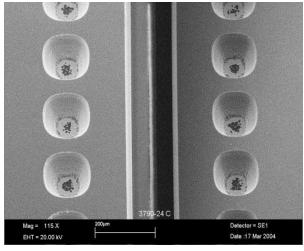

#### Tapered TSVs processing on ATLAS FE-I2 batch

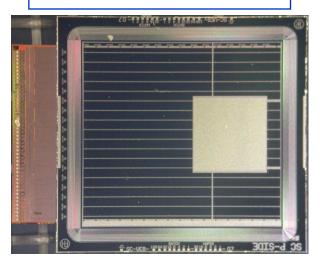

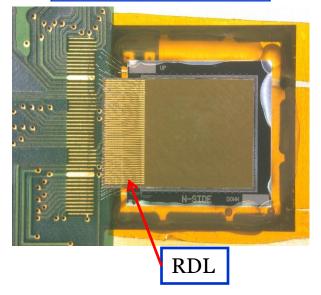

## FE-I2 module with TSV

- Received 16 modules:

- FE-I2 chips, 90μm thick, with tapered TSV and RDL

- Planar n-in-n sensor

- 2 modules mounted on boards for electrical tests

- Both modules work fine

Module front side

Module on board

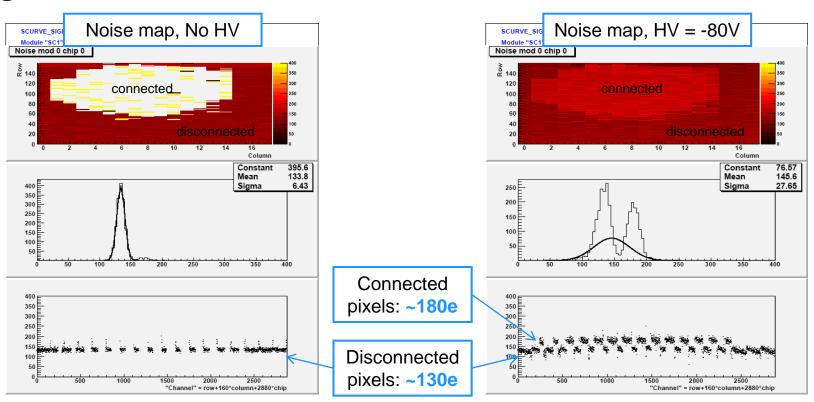

# Module test using TSVs

• Used "standard" IC handling method (no handle wafer) → gains time (but of course leads to large area of unconnected bonds).

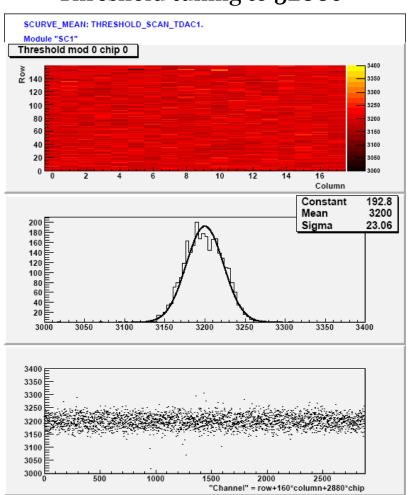

• ENC ~180e-! Module works fine & no indication of extra noise

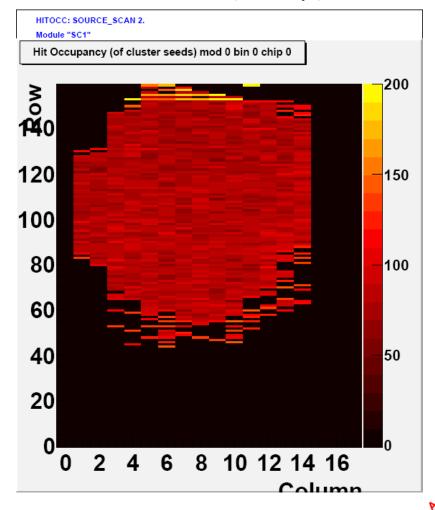

## Source scan with TSV module

#### Threshold tuning to 3200e

#### Source scan (Am 241)

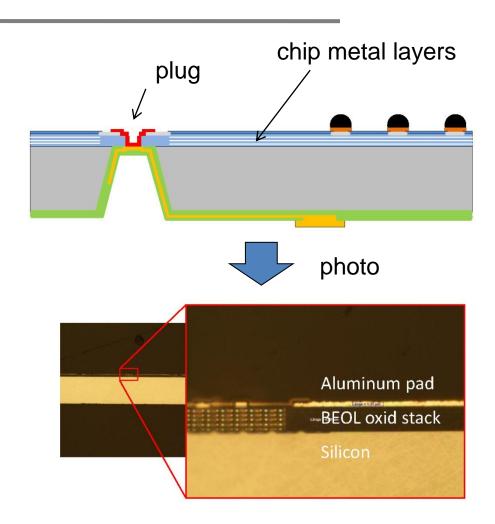

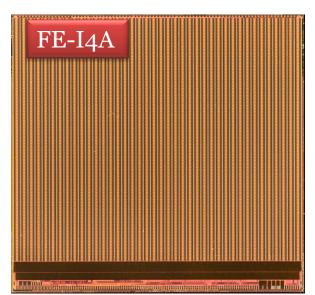

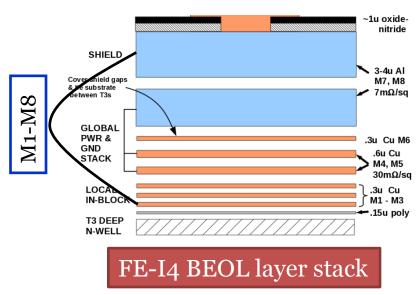

# Next immediate step: TSV FE-I4A

- Next step: Use FE-I4A IC & same process:

- 6 times larger than FE-I2/3 but thickness must be 90μm (note IBL chips are 150μm thick): Use thin flip chip method currently used for IBL modules.

- FE-I<sub>4</sub>A pads are already tuned for TSV usage (half pad area

BEOL only, complete metal stack → No frontside plug needed)

# Intermediate goal

- Usage of final version of the FE-I4 IC for IBL, FE-I4B. Tuned for TSV usage + can use the CPPM-developed GDAC to monitor more information (internal voltages, leakage currents, temperature...).

- Assess the potential for TSV of a second vendor (LETI Grenoble, France).

- Test connection to other sensor types (3D silicon, depleted HV CMOS).

#### Conclusion

- Successful 1<sup>st</sup> demonstration of usage of TSV on FE-I2 / I3 ATLAS FE.

- ICs function well when operated with TSV + backside RDL (equivalent noise, source scan performed).

- A run with FE-I4A will soon start (3 wafers reserved for that). Results expected ~fall 2012.

- TSV on FE-I4B, in-situ IC characterization.

- Developments for IBL and HL-LHC upgrades lead to:

- Integrated TSV / Bump-bonding process.

- Handling of large & thin IC.

- <u>Goal</u>: New module concepts using TSV, material reduction, technology exploration for the High Luminosity LHC upgrade.

### **BACKUP**

# • BACKUP

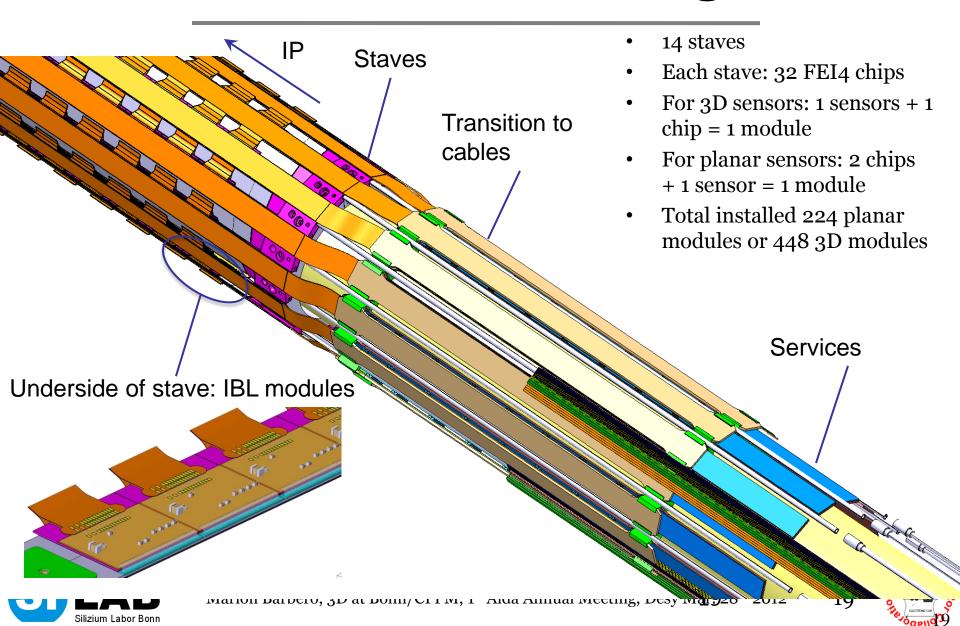

# Stave and module arrangement