# R&D towards a 3D - Via last interconnect Technologies for Pixel detectors

Atlas IN2P3 project

Abdenour Lounis, Gisèle Martin-Chassart, Damien Thienpont, Jeanne Tongbong, Benoit Lachacinski

Laboratoire de l'accélérateur Linéaire

Université Paris XI, Orsay,

Giovanni Calderini, Jean François Genat, Olivier Ledortz

Laboratoire de Physique des Hautes Energies, Paris VI

Teddy Todorov, Renault Gaglione, , Julie Prast, Fatima Lachani

Laboratoire Annecy –le-Vieux de Physique des Particules

# Why do we go for 3D technologies, for HL-LHC. Criteria to be fulfilled:

- Better granularity & 4 size abuttable devices

(Shrink pixel dimensions to decrease the form factor of the final device)

- Low material budget (Submicron technologies + thin sensors using innovative interconnect techniques: slid, microbumps...)

- Radiation hard Si detectors (Oxygenated silicon) and electronics (CMOS 130 nm and 45 nm)

- Low power dissipation systems (low noise electronics and use of TSV technology in place of wire bonds, bumps...)

## **Prospects**

In parrallel: To exploit and combine two major technology advances and evaluate potential beneficts

Use 130 nm CMOS and potential availability of 65 nm in Research laboratories in close cooperation and coordination with CERN-Mic

(process of building a 65 nm « club » or task force)

Take advantage of « open » TSV providers in Europe to demonstrate the feasability of TSVs on functional detector chips.

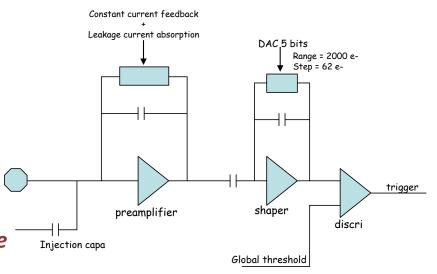

# OMEGAPIX2 project : CHIP for pixel readout (IBM 130 nm)

#### chartered-Tezzaron

#### Targets:

- Low threshold (1000 e)

- Low noise ~300 fF

- •Cope with high leakage current (up to 100 nA per channel)

- •8 bits local threshold adjustment

- Time-Over-Threshold measurement

- •3 bits

- •Clock multiplier (40Mhz to 160 Mhz) possible

- Optimized readout for maximum charge measurement accuracy and event pile-up

- On pixel memory of *up to 3* event between each Lv1 clear

- •Ambitious goal is to couple this chip to a sensor and bring it in test-beam for performance study, radiation damage studies

- •Entangled with Slim Edge sensor R&D to produce 4 side buttable device

Submitted end 2011

3 bits Range = ~ 10,000 e-Step = ~ 1250 e-

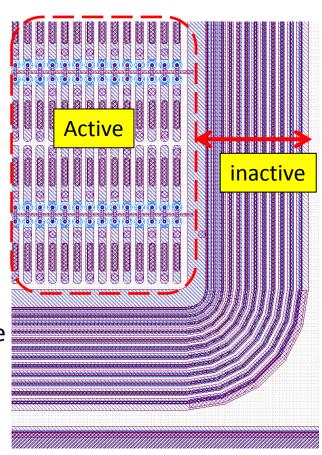

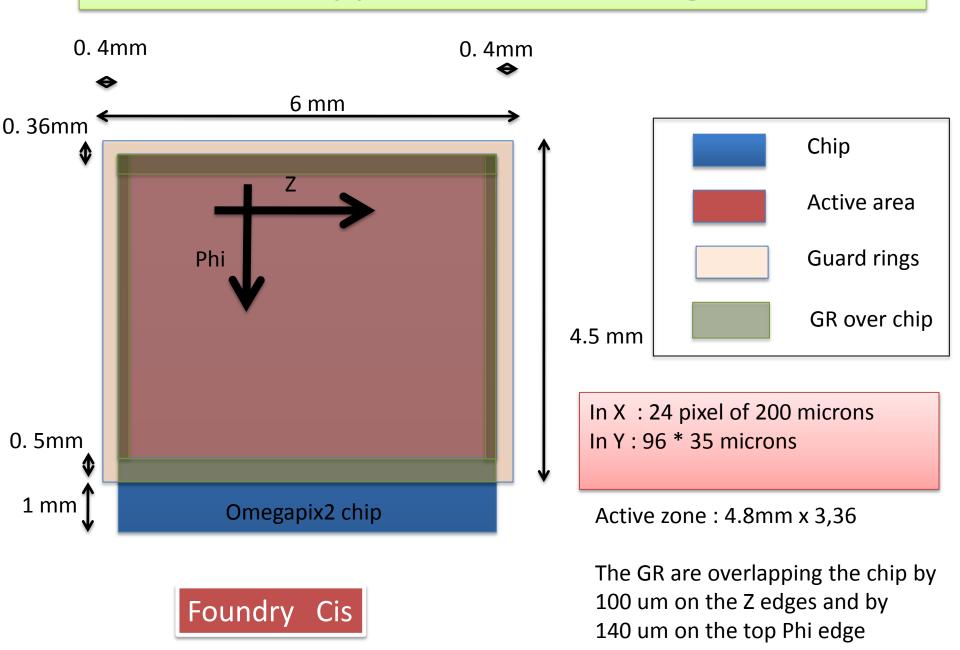

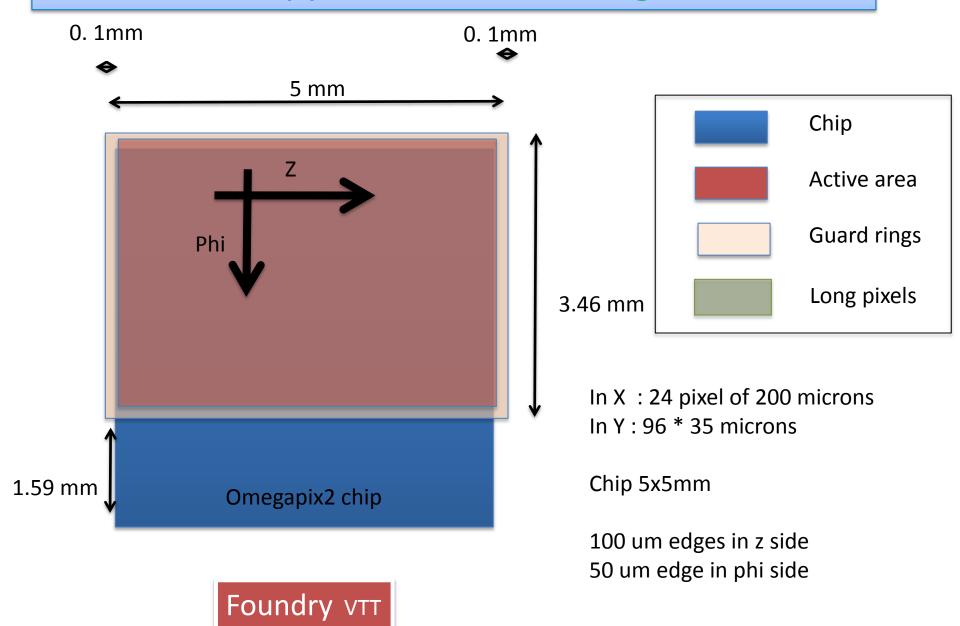

### OMEGAPIX2 sensor For ATLAS HL-LHC

- Reduction of Phi resolution has been shown to be more beneficial to ATLAS tracking performance than Z resolution -> Pixel of 35x200 um

- OMEGAPIX2 will provide a complete read-out chain usable in testbeam and other complete standalone system test

- The chip could provide spectroscopic measurements at low luminosity (ie details charge measurement) and fast operation at higher luminosity

Planar Pixel Sensor

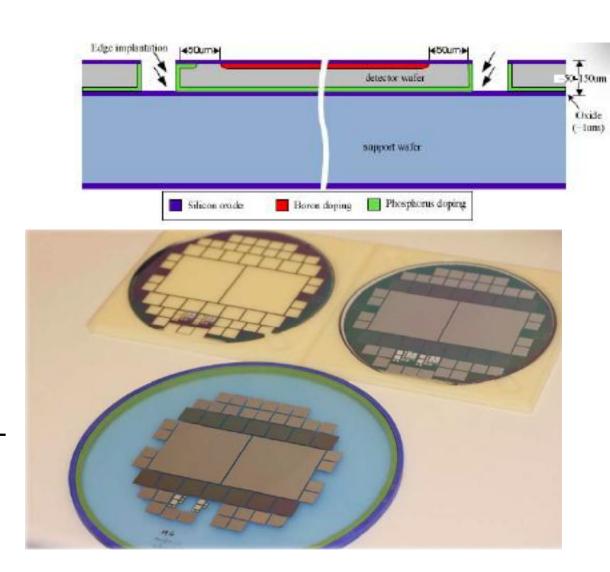

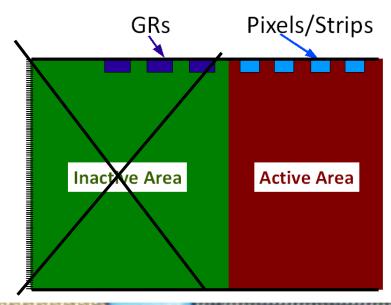

## Sensor developpement: Guard Ring Sensor

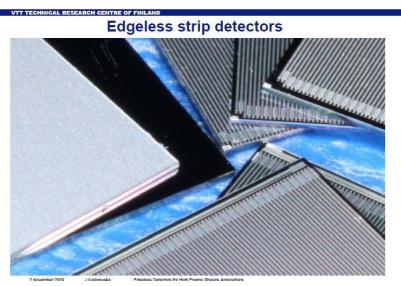

## Towards Edgless sensor technology

### Sensor developpement: Active Edge Sensor

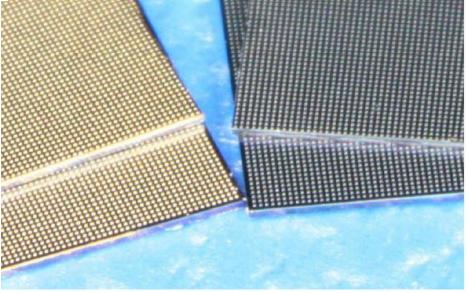

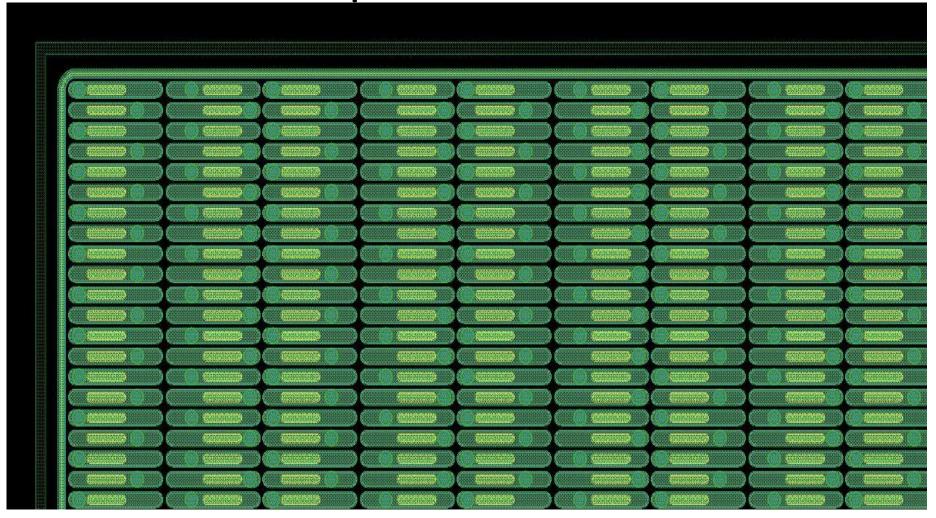

# VTT Edgless pixel matrix under production

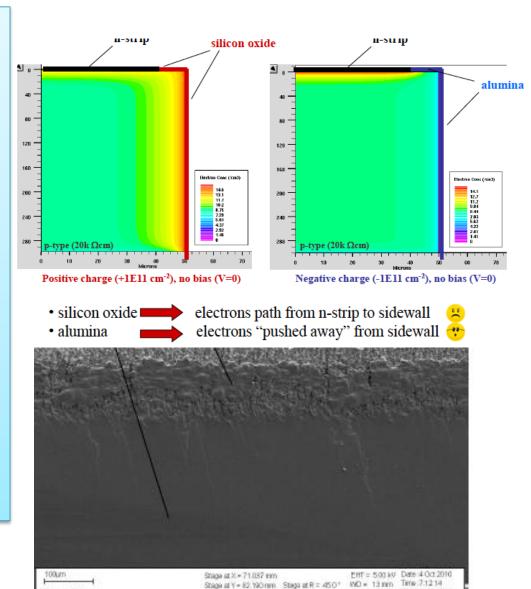

## Promising approach : RD 50 Slim Edges

Slim edge is achieved through post-processing by creating a clean cut at the edge of the sensor:

- Laser scribing

- Cleaving

Passivation of the edge using Alumina Atomic Layer Deposition can be used with new material to control oxide charge and control potential drop in the sensor.

Santa Cruz

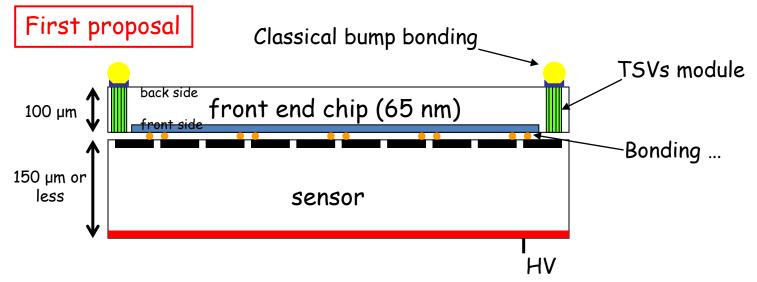

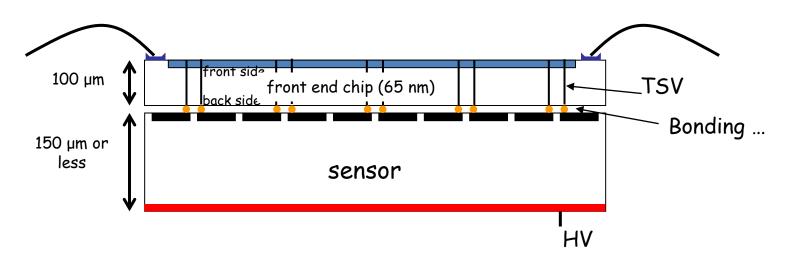

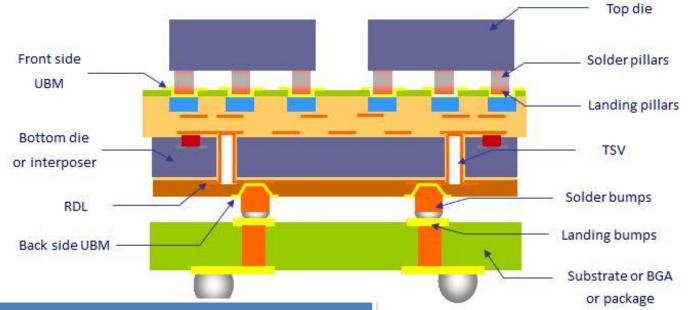

#### Bump bonding TSVs module back side front end chip (65 nm) First proposal 100 μm front side Bonding ... $150 \, \mu m \, or$ sensor less HV front sid 100 µm TSV front end chip (65 nm) back side Interconnexions 150 μm or less sensor second proposal HV

Via Last AIDA project: LAL + LPNHE+ LAPP

#### Process steps

- > Front end chip fabrication in 65 nm techno (IBM) with analog and digital signal processing and sensor fab

- ✓ no pads, only available area for futures TSVs

- > via-last post-processing

- √ I/O access by the chip's back side

- ✓ Several TSVs for one pad => better yield

- > thinning up to reach TSVs, back metallization (100 µm final thick)

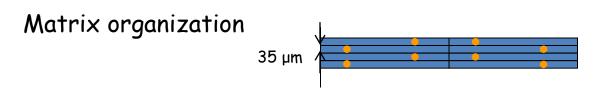

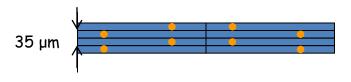

- > bonding sensor: ~ 35 µm pitch

Pixel bonding will be placed in alternance to get minimal pixel width

#### Second proposal

#### Much more ambitious!!

#### Process steps

- > Front end chip fabrication in 65 nm techno (IBM) with analog and digital signal processing and sensor fab

- > via-last post-processing

- ✓ one TSV by pixel

- > thinning up to reach TSVs, back metallization (100 µm final thick)

- > bonding sensor: ~ 35 µm pitch

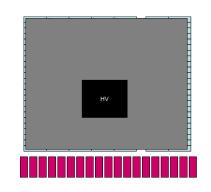

#### Matrix organization

Pixel bonding will be placed in alternance to get minimal pixel width

## Exploit industrial know how Open 3D™ Initiative (LETI-GRENOBLE)

#### General information

- → The purpose of this specification guide is to give a maximum of information to LETI in order to prepare the technical proposal

- ◆ The customer must fill the column "customer answer"

- ♦ The orange cells are mandatory to fill

- ◆ The blue cells are optional

Meeting scheduled April 20th, 2012 at Grenoble

## Industry offers

| institute | diameter aspect filling pitch type ratio/depth |                                         |                                                    | interconnection                                    |                 | wafer size   |                                               |  |

|-----------|------------------------------------------------|-----------------------------------------|----------------------------------------------------|----------------------------------------------------|-----------------|--------------|-----------------------------------------------|--|

|           |                                                |                                         |                                                    | type p                                             | itch diameter   |              |                                               |  |

| CEA Leti  | 30µm<br>40µm<br>60µm                           | 1.5:1 Cu liner<br>03:01<br>02:01        | from backside to M1<br>80μm                        | solder pillar (Cu- SnAg)<br>solder bumps (Cu SnAg) | 50μm<br>120μm   | 25μm<br>80μm | 200/300 mm<br>for TSV?                        |  |

| CMP/MOSIS | 100μm                                          | 2.5:1 (250 μm) Cu liner?                | via middle<br>400μm with 0.35 μm CMOS              |                                                    |                 |              | 2 Tier 3D by Tezzaron<br>Austria Microsystems |  |

| EMFT      | 2 μm<br>10 μm                                  | > 8:1 Tungsten<br>4:1 (40µm) Tungsten/C | 4μm apect ration: 16:1<br>20 μm                    | SLID (SnCu)                                        | < 30 μm         | 25 μm        | 200/300(?) mm                                 |  |

| IZM       | 15 μm<br>large<br>(100μm?)                     | 50 μm Cu filling<br>Cu lining           | 30 μm interposer<br>large tapered<br>(>100<br>μm?) | SnAg(Cu), CuSn, Au, In<br>Au nano porous           | 20 μm?          | 10μm         | 300 Dresden                                   |  |

| IMEC      | 25µm                                           | 2:1 (50μm) Cu filling                   | 40μm via last                                      | CuSn (in)                                          | 20μm<br>(10μm?) |              | 200                                           |  |

|           | 5μm                                            | 4:1 (20μm) Cu filling                   | via middle (with 130nm in-<br>10μm houswe CMOS)    |                                                    |                 |              | 200                                           |  |

| VTT       | 60μm (top)                                     | 2:1 (120μm) Cu lining                   | 90μm tapered (86deg)                               | SnPb, InSn, PbSn, SnAg                             | 25µm            | 50μm         | 150 μm (TSV)                                  |  |

| T-Micro   | 0.5-2.8 μm<br>(tapered)<br>2.5 μm              | < 40μm tungsten<br>< 55 μm polysilicon  | ~10 µm via last<br>small via first                 | microbumps + adhesive                              | 5μm             | 2μm          | 200mm (or<br>larger?)                         |  |

## Project forecast & Time scale

- A-operation: is to get slim edge Pixel sensors (IZM) with Omegapix2 chip- 05/2012

- B-operation is to get edgless pixel sensors (VTT) with Omegapix2 chip- 05/ 2012

- Third step is to have an Omegapix ASIC readout 130nm (end 2013)and later-on 65nm

- Deliver a 4 side abuttable monolithic edgless device where I/O signals are routed vertically through the readout chip (~2015)

## VTT slim edges sensors

Slim edge is achieved through:

- •Extreme quality of the sensor surface

- Implantation of the edges after etching

Important requirements:

- Implementation of pspray and moderated pspray implantation in VTT process

- Radiation hardness