A C-Card for Use with the BNL Peak-Finding ASIC

Ken Johns, Joel Steinberg, Jason Veatch, Venkat Kaushik (U. Arizona)

## Status

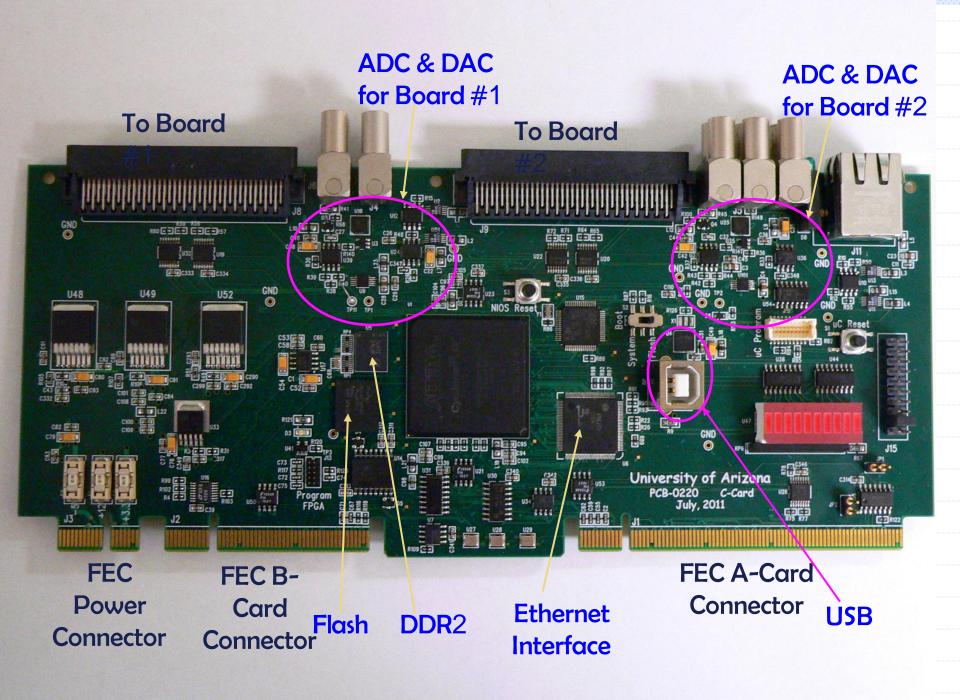

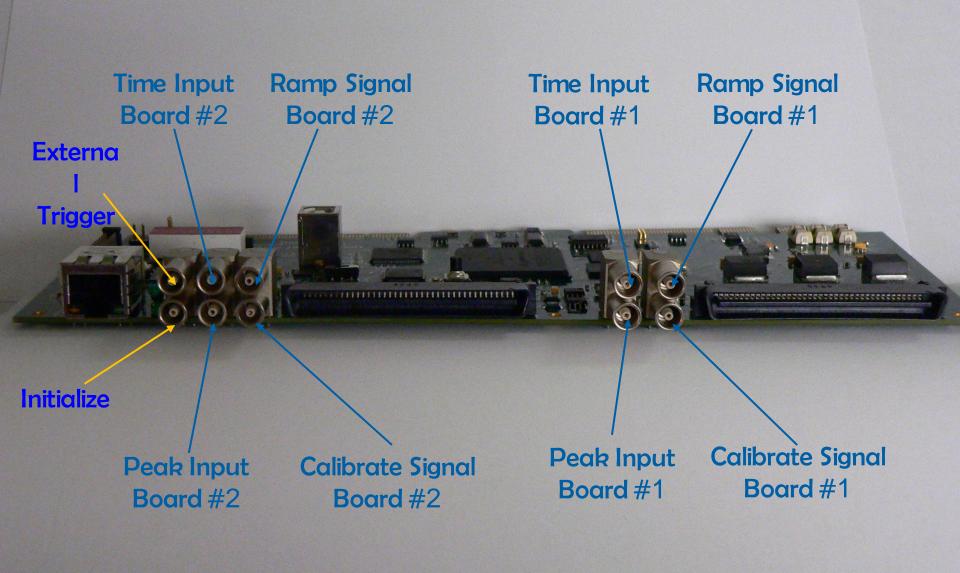

➤A C-Card has been developed for use with both versions (V1 and V2) of the BNL peak-finding ASIC

Communication with the FEC card to the MAMMA DAQ program has been successfully tested

Communication with the V1 ASIC on its present front-end card is in progress

Design of a front-end card for full-size Micromegas using V2 of the ASIC is in progress

### Features

Connections to two BNL front-end cards via 2x80 pin ribbon cables 8 LVDS inputs to C-Card 16 LVDS I/O ports Connection to FEC card via card edge connectors 4 LVDS inputs to C-Card 21 LVDS outputs 3 LVDS clocks to C-Card 2 3.125 Gbps transceivers

#### Features

$\rightarrow$  10/100 Ethernet and USB connections ≻4 12 bit ADC's ≻4 16 bit DAC's  $\geq$  2 calibration pulse generators  $\geq$  2 ramp generators 2 FPGA clock regions from on-board oscillators or FEC

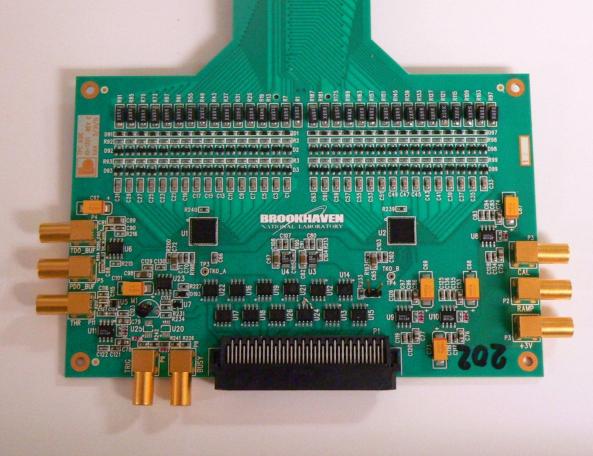

# Front-End Card with V1 BNL ASICS

. ... .

## **Testing With FEC**

## **Testing with FEC**

Preprogrammed events of varying lengths and time intervals were sent to the FEC

Sorin Martoiu wrote FEC firmware for

Sorin Martolu wrote FEC firmware for FIFO receive and UDP packet creation

Validated with MAMMA DAQ program

using simple event prints

### **Future Work**

- Continue commissioning of C-Card with V1 BNL ASIC

- Prepare for commissioning of C-Card with V2 BNL ASIC

- Continue design of front-end card for full-size MM with V2 BNL ASIC