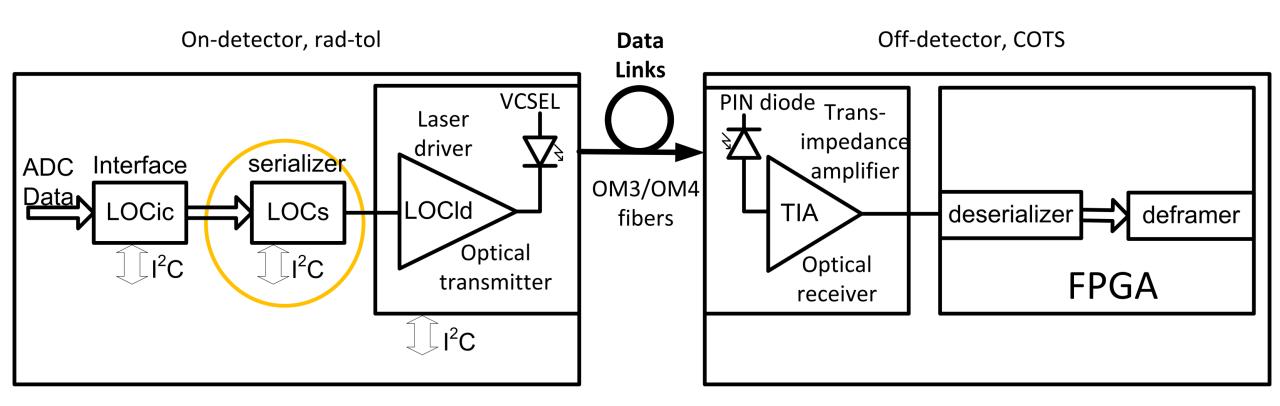

LOCs2, a 2-channel, 8 Gbps 16:1 serializer is a prototype ASIC for ATLAS liquid argon (LAr) calorimeter readout upgrade. In the proposed LAr calorimeter readout upgrade, the large volume of data from ADC, about 100Gbps each board, will be continuously transferred to back-end through optical data link<sup>[1]</sup>. A serial ASICs are demanded for optical link because of its high bandwidth, low power and radiation-tolerant requirements. Serializer is the key component to convert parallel data from ADC to high speed serial data to laser driver. LOCs2 is the second version of serializer we developed based on Silicon-on-Sapphire (SoS) CMOS process.

The upgrading ATLAS LAr calorimeter readout optical data link

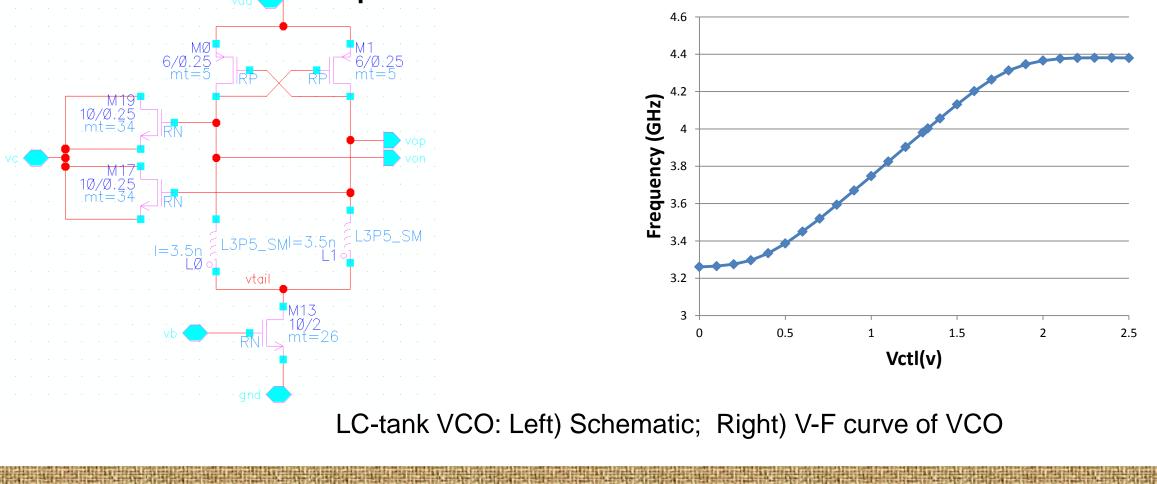

### **LC-tank PLL**

LC-tank PLL has low power and low-jitter characters, comparing to ring oscillator based PLL. The core of the LOCs2 clock generator is a LC-tank PLL inherited from previous design in 2010<sup>[3]</sup>.

- Frequency center at 4GHz with 20% tuning range

- LC VCO phase noise -110 dBC/Hz at 4GHz

- Power consumption: 100mW

### Summany

We designed a two channel, 8Gbps radiation-tolerant serializer for ATLAS liquid argon calorimeter readout optical link system upgrade. The ASIC consumes about 1.2 Watt and its total jitter is estimated to be about 39 ps.

The design has been submitted in June 2012 and will be test in October 2012.

Datao Gong<sup>1</sup>, Suen Hou<sup>2</sup>, Mengxun He<sup>4</sup>, Futian Liang<sup>1,3</sup>, Chonghan Liu<sup>1</sup>, Tiankuan Liu<sup>1</sup>, Da-Shung Su<sup>2</sup>, Ping-Kun Teng<sup>2</sup>, Annie C. Xiang<sup>1</sup>, Jingbo Ye<sup>1</sup> <sup>1</sup> Department of Physics, Southern Methodist University, Dallas TX 75275, U.S.A. <sup>2</sup> Institute of Physics, Academia Sinica, Taipei 11529, Taiwan <sup>3</sup> Department of Modern Physics, University of Science and Technology of China, Hefei Anhui 230026 China <sup>4</sup> Electrical Engineer Department, Arizona State University, Tempe, Arizona, U.S.A.

dtgong@physics.smu.edu

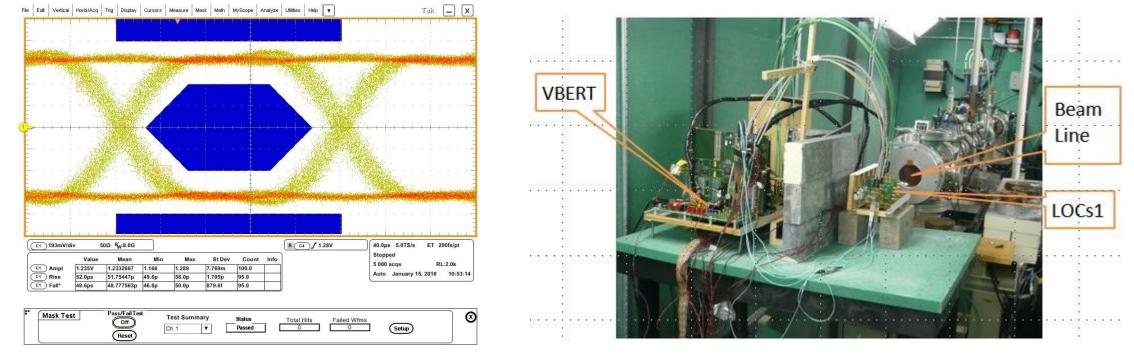

# SoS process and LOCs1 test

The SoS CMOS process, with a thin layer of silicon deposited on highly insulating sapphire substrate, reduces parasitic capacitance and Single Event Upset (SEU) cross section, making it a good technology candidate for ASIC design in detector front-end electronics in particle physics experiments.

Based on the 0.25 um SoS CMOS technology, we had developed a single channel 5 Gbps 16:1 serializer in 2010, LOCs1. LOCs1 is implemented with CMOS logical and its highspeed clock generator is a 2.5 GHz ring oscillator phase-locked loop. The prototype chip has been successfully tested in lab and proven to be radiation-tolerant in radiation test<sup>[2]</sup>.

The previous version LOCs1: Left) Eye diagram; Right) Radiation test

## High-speed differential 2:1 multiplexer stage

The serializer comprises 4 multiplexer stages in serial and only last stage is driven by the highest clock signal at 4GHz This stage is composed of two D-flip-flop, a latch and a 2:1 MUX. To achieve high speed and reduce jitter, all circuits are implemented with CML logic.

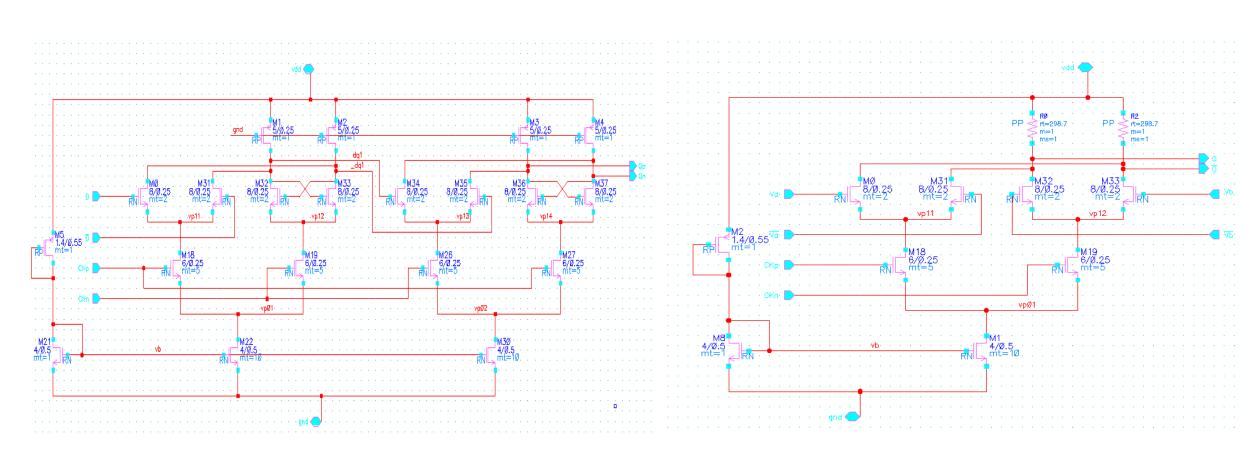

Schematic of CML circuits in last stage: Left) D-flip-flop; Right) 2:1 MUX

## Acknowledgements

• This work is supported by US-ATLAS R&D program for the upgrade of the LHC, and the US Department of Energy grant DE-FG02-04ER41299. • We are grateful to Paulo Moreira (CERN), Fukun Tang (University of Chicago), Mauro Citterio, Valentino Liberali (INFN), Carla Vacchi (University of Pavia), Christine Hu, Quan Sun (IPHC), Sachin Junnarkar (BNL), Yi Kang, Jay Clementson, John Sung, and Gary Wu (Peregrine Semiconductor Corporation). • We also would like to thank Justin Ross at Southern Methodist University for his help in setting up and maintaining the design environment.

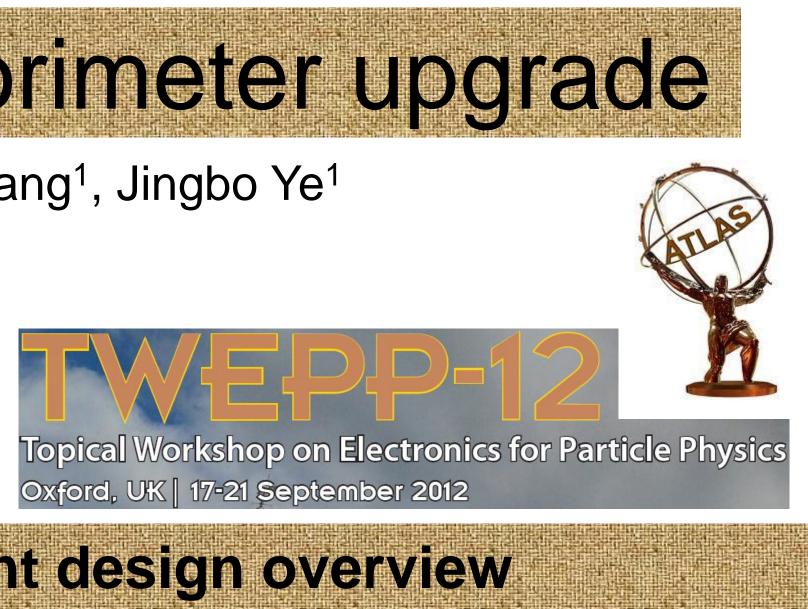

The current design inherits the structure of previous design. To improve the serializer speed, the clock generator is replaced with a 4 GHz LC-tank phase-locked loop and part of the highspeed circuits are re-designed with current mode logic (green block below). Two serializers share one PLL to save power consumption.

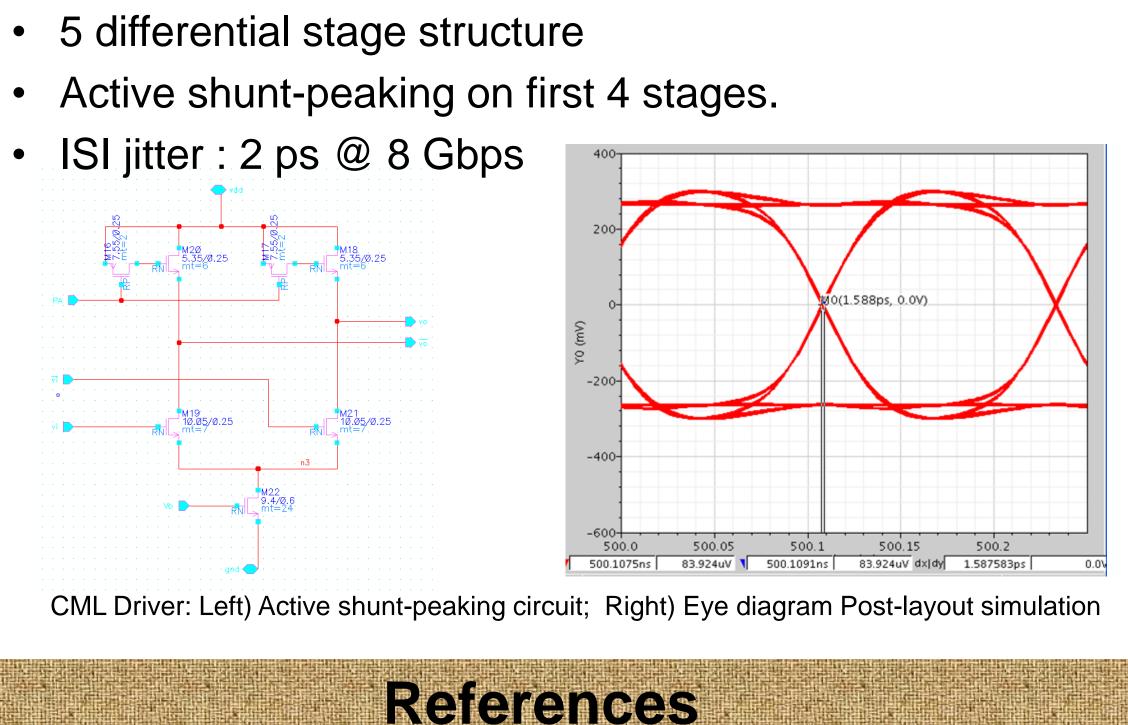

**CML** Driver The serial data is driven to output by a CML driver.

- Output impedance 50 ohm

- Power supply : 3.3 V

[1] Hucheng Chen, Readout Electronics for the ATLAS LAr Calorimeter at HL-LHC, the Technology and Instrumentation in Particle Physics (TIPP) conference, Chicago, U.S.A, June 9-14, 2011. [2] A 16:1 serializer ASIC for data transmission at 5 Gbps D Gong 2010 JINST 5 C12009 [3] T Liu, A 4.9-GHz low power, low jitter, LC phase locked loop, 2010 JINST 5

C12045

LOCs2: Left) Block diagram; Middle) Layout of the die; Right) Eye diagram of post-layout simulation